Documente Academic

Documente Profesional

Documente Cultură

Shree Chanakya Education Society's Indira College of Engineering and Management Lesson Plan for VLSI Design and Technology

Încărcat de

Harold WilsonDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Shree Chanakya Education Society's Indira College of Engineering and Management Lesson Plan for VLSI Design and Technology

Încărcat de

Harold WilsonDrepturi de autor:

Formate disponibile

SHREE CHANAKYA EDUCATION SOCIETYS

INDIRA COLLEGE OF ENGINEERING AND MANAGEMENT

Approved By AICTE New Delhi, DTE (MS) and Affiliated to Pune University ( Id-No. PU/PN/Engg/282/2007)

Department of Electronics &Telecommunication Engineering

Lesson Plan

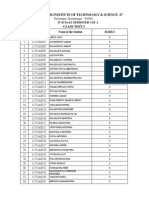

Teaching Scheme Lecturers/week: 4 hrs Practicals/week: 2 hrs VLSI DESIGN AND TECHNOLOGY (404182) Examination Scheme Paper: 100 Marks Practical: 50 Marks

Sr.No

Planned Date

Syllabus to Covered

UNIT I

1. 102/07/2012 . 2. 04/07/2012 3. 05/07/2012 4. 09/07/2012 5. 12/07/2012 6. 13/07/2012 7. 16/07/2012 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. 21. 22. 23. 24. 25. 26. 27. 17/07/2012 18/07/2012 19/07/2012 23/07/2012 24/07/2012 25/07/2012 26/07/2012 30/07/2012 31/07/2012 01/08/12 06/08/2012 07/08/2012 08/08/2012 09/08/2012 13/08/2012 14/08/2012 16/08/2012 21/08/2012 22/08/2012 23/08/2012

Enhancement MOSFET equivalent circuit parasitics, as resistor, diode. Active load, current source and push pull inverter amplifiers. Current source and sink. Common source, drain and gate amplifiers. Cascode amplifier. Differential amplifier. CMOS op-amp.

Unit II

CMOS Inverter, voltage transfer curve, body effect, hot electron effect, velocity saturation Static and dynamic dissipations. Power delay product. Noise margin. Combinational logic design, W/L calculations. Transmission gate, design using TGs. Parameter, layout, Design Rule Check. Technology scaling.

Unit III

VHDL design units, modeling styles synthesizable and non synthesizable test benches design flow, functions, procedures, attributes, test benches, configurations Finite State Machines (FSM), packages. Synchronous and asynchronous machines state diagrams and VHDL codes for FSMs.

Unit IV

Need of PLDs Comparison with ASIC general purpose processor, DSP processor, microcontroller, memories etc. Features, specifications, detail architectures,

28. 27/08/2012 29. 28/08/2012 30. 29/08/12 31. 32. 33. 34. 35. 36. 37. 38. 39. 40. 41. 42. 43. 30/08/2012 03/09/2012 04/09/2012 05/09/2012 09/09/2012 10/09/2012 11/09/2012 12/09/2012 13/09/2012 17/09/2012 18/09/2012 20/09/2012 24/09/2012

limitations of Complex Programmable Logic Device (CPLD) Field Programmable Logic Devices (FPGA). application areas

Unit V

Types of fault, stuck open, short, stuck at 1, 0 faults Fault coverage Need of Design for Testability (DFT). Controllability, predictability, testability Built In Self Test (BIST) Partial and full scan check. Need of boundary scan check JTAG, Test Access Port (TAP) controller.

Unit VI

Clock skew, Clock distribution techniques clock jitter Supply and ground bounce, power distribution techniques. Power optimization. Interconnect routing techniques wire parasitics. Design validation. Off chip connections, I/O architectures I/O architectures. Signal integrity Issues, EMI immune chip design

44. 25/09/2012

S-ar putea să vă placă și

- The Occult WorldDocument256 paginiThe Occult WorldJewell Elliott100% (1)

- Astrology MathematicsDocument34 paginiAstrology MathematicsDrFaisal ShawqeeÎncă nu există evaluări

- SolidWorks Advanced 2013 - 14Document117 paginiSolidWorks Advanced 2013 - 14Arman Pineda100% (10)

- Eye Witness TestimonyDocument32 paginiEye Witness Testimonyapi-308625760Încă nu există evaluări

- AutoCAD Electrical 2020 for Electrical Control Designers, 11th EditionDe la EverandAutoCAD Electrical 2020 for Electrical Control Designers, 11th EditionÎncă nu există evaluări

- The Trauma of Freud Controversies in Psychoanalysis PDFDocument318 paginiThe Trauma of Freud Controversies in Psychoanalysis PDFMinuxÎncă nu există evaluări

- B.tech - CSE All Year SyllabusDocument92 paginiB.tech - CSE All Year SyllabusSachin TiwaryÎncă nu există evaluări

- Digital System Designs and Practices: Using Verilog HDL and FpgasDocument14 paginiDigital System Designs and Practices: Using Verilog HDL and FpgasHarold WilsonÎncă nu există evaluări

- Competing Risks and Multistate Models With RDocument249 paginiCompeting Risks and Multistate Models With RJuanCarlosAguilarCastro100% (1)

- Microprocessors and Microcontrollers Lab ManualDocument107 paginiMicroprocessors and Microcontrollers Lab ManualRohith ShashankÎncă nu există evaluări

- 2017 I. IntroductionDocument50 pagini2017 I. IntroductionnaiyaÎncă nu există evaluări

- Trends in Linguistics - Studies and MonographsDocument550 paginiTrends in Linguistics - Studies and MonographsNelly PaniaguaÎncă nu există evaluări

- Indira College of Engineering and Management: Lesson PlanDocument2 paginiIndira College of Engineering and Management: Lesson PlanDianaAuroraÎncă nu există evaluări

- Final 2Document33 paginiFinal 2Anurag KharwarÎncă nu există evaluări

- FKE S3 1011 BUKU LOG Amalan KejuruteraanDocument80 paginiFKE S3 1011 BUKU LOG Amalan Kejuruteraanng soo keeÎncă nu există evaluări

- ECE 7995-Embedded Systems For Vehicles-Syllabus S17 - v2Document6 paginiECE 7995-Embedded Systems For Vehicles-Syllabus S17 - v2AsraButoolÎncă nu există evaluări

- Scheme - G Fifth Semester (Ej, Et, Ex, En, Is, Ic, Ed, Ei)Document42 paginiScheme - G Fifth Semester (Ej, Et, Ex, En, Is, Ic, Ed, Ei)RahulPatilÎncă nu există evaluări

- Semester 1: Effective For 2009 Intake Onwards Page 1 of 6 - CSDocument6 paginiSemester 1: Effective For 2009 Intake Onwards Page 1 of 6 - CSnjk19Încă nu există evaluări

- Advanced Help Desk Automation: A Project Report ONDocument11 paginiAdvanced Help Desk Automation: A Project Report ONRachna LalÎncă nu există evaluări

- TeachingPlan BTKR1313 SEM1 20122013Document10 paginiTeachingPlan BTKR1313 SEM1 20122013Sabikan SulaimanÎncă nu există evaluări

- Instruction Manual: Raj Kumar Goel Institute of Technology, GhaziabadDocument13 paginiInstruction Manual: Raj Kumar Goel Institute of Technology, GhaziabadunkownÎncă nu există evaluări

- Industrial Training Report (SagarGarg)Document35 paginiIndustrial Training Report (SagarGarg)kartik guptaÎncă nu există evaluări

- BE Session PlanDocument23 paginiBE Session Plananon_747680669Încă nu există evaluări

- VIIIth Semester Scheme and SyllabusDocument21 paginiVIIIth Semester Scheme and SyllabusJitesh DewanganÎncă nu există evaluări

- Unit1 OSDocument136 paginiUnit1 OSKanika RajputÎncă nu există evaluări

- Sap RPL12Document2 paginiSap RPL12Arlando HutapeangÎncă nu există evaluări

- MTechSyllabus2012 13Document243 paginiMTechSyllabus2012 13Nitin GoyalÎncă nu există evaluări

- TE Session PlanDocument13 paginiTE Session Plananon_747680669Încă nu există evaluări

- TE Session PlanDocument14 paginiTE Session Plananon_747680669Încă nu există evaluări

- HDL Programing and Eda Tools Laboratory Manual: For I / Ii M.Tech Vlsi Design (Ece) I - SemesterDocument130 paginiHDL Programing and Eda Tools Laboratory Manual: For I / Ii M.Tech Vlsi Design (Ece) I - SemesterShruti GuravÎncă nu există evaluări

- Jana Evangelisty ENGLISH Ders IçeriğiDocument24 paginiJana Evangelisty ENGLISH Ders IçeriğiMojtaba AhmadiÎncă nu există evaluări

- MPMCDocument47 paginiMPMCvaseem_ahmedÎncă nu există evaluări

- 1.PPT II Plastics Processing Technology II 20 222 wtb2654Document1 pagină1.PPT II Plastics Processing Technology II 20 222 wtb2654Raj ThakurÎncă nu există evaluări

- Mobile App. Development (22617) Subject MicroprojectDocument21 paginiMobile App. Development (22617) Subject MicroprojectKunal Shankar TherÎncă nu există evaluări

- HarshaDocument54 paginiHarshatejaswiniprathapaneniÎncă nu există evaluări

- Character RecognitionDocument13 paginiCharacter RecognitionNilax PatelÎncă nu există evaluări

- Concept of "Finishing School For Engineering Students"Document4 paginiConcept of "Finishing School For Engineering Students"Amit Kumar SrivastavaÎncă nu există evaluări

- National Training Programmes 2012 13Document4 paginiNational Training Programmes 2012 13chandussctÎncă nu există evaluări

- Venu GDocument53 paginiVenu GtejaswiniprathapaneniÎncă nu există evaluări

- Softwen ProjectDocument4 paginiSoftwen ProjectAngelique Garrido VÎncă nu există evaluări

- Monday7 VirgiawanDocument8 paginiMonday7 Virgiawankeisya hanumÎncă nu există evaluări

- Timetable Scheduling System For Ducoe: Project ProposalDocument13 paginiTimetable Scheduling System For Ducoe: Project ProposalTewodros DemelashÎncă nu există evaluări

- Pengaruh Penggunaan Software Inventor Terhadap Kemudahan Mahasiswa dalam Praktikum CAD/CAMDocument8 paginiPengaruh Penggunaan Software Inventor Terhadap Kemudahan Mahasiswa dalam Praktikum CAD/CAMM. IskandarÎncă nu există evaluări

- Staff Development Programme 2012Document3 paginiStaff Development Programme 2012gopikrishnaraoÎncă nu există evaluări

- EE 423 Embedded System Design Awais KambohDocument5 paginiEE 423 Embedded System Design Awais KambohMuhammad GulÎncă nu există evaluări

- Unit4 CNDocument173 paginiUnit4 CNShivani MauryaÎncă nu există evaluări

- 15UEC727 - Master Record-1Document70 pagini15UEC727 - Master Record-1vishnu devÎncă nu există evaluări

- SE Experiments TemplateDocument92 paginiSE Experiments TemplateRani rajpurohitÎncă nu există evaluări

- LabDocument11 paginiLabravi855885Încă nu există evaluări

- Jhala Aanal DivyanshuDocument2 paginiJhala Aanal DivyanshuadjhalaÎncă nu există evaluări

- Ec8562 DSP ManualDocument86 paginiEc8562 DSP ManualN.S.Priyanga 33Încă nu există evaluări

- Gujarat Technological University Mechanical (Cad/Cam) (08) : Computer Aided Process Planning 2720813 Semester: IiDocument3 paginiGujarat Technological University Mechanical (Cad/Cam) (08) : Computer Aided Process Planning 2720813 Semester: IiGeorge CamachoÎncă nu există evaluări

- MTechSyllabus2012 13Document243 paginiMTechSyllabus2012 13kamalkahamlaÎncă nu există evaluări

- Microprocessor FinalDocument14 paginiMicroprocessor Finalvidhatekaruna4Încă nu există evaluări

- Manvendra Jain 2.5 Years Electrical Apr 2016Document3 paginiManvendra Jain 2.5 Years Electrical Apr 2016Amit PrajapatiÎncă nu există evaluări

- Sem5 EJ5EDocument38 paginiSem5 EJ5EAjit SinghÎncă nu există evaluări

- 1.syllabus Website Autonomy CSE (1 To 17) UpdatedDocument229 pagini1.syllabus Website Autonomy CSE (1 To 17) UpdatedCSE 44 Prajwal BhajeÎncă nu există evaluări

- Final BTech MechanicalDocument31 paginiFinal BTech MechanicalAniket GaikwadÎncă nu există evaluări

- Unit3 - PPT - CSBS COA-1Document62 paginiUnit3 - PPT - CSBS COA-1mayankrajput13626Încă nu există evaluări

- Int Project CodingDocument96 paginiInt Project CodingGEETAÎncă nu există evaluări

- Digital Design Lab ManualDocument39 paginiDigital Design Lab ManualDhananjayaÎncă nu există evaluări

- Major Project Report FormatDocument2 paginiMajor Project Report FormatNiyati ShahÎncă nu există evaluări

- CAD/CAM Lab Manual for Mechanical EngineeringDocument83 paginiCAD/CAM Lab Manual for Mechanical EngineeringPasupathi KumarÎncă nu există evaluări

- ECE 365 Microprocessor Course SyllabusDocument5 paginiECE 365 Microprocessor Course SyllabusMohamad Taib MiskonÎncă nu există evaluări

- SyllabusDocument3 paginiSyllabusRon ThomasÎncă nu există evaluări

- FGDFGFDocument5 paginiFGDFGFHarold WilsonÎncă nu există evaluări

- JNTUH M.Tech academic regulationsDocument9 paginiJNTUH M.Tech academic regulationsSal ExcelÎncă nu există evaluări

- Notes 326 Set8Document16 paginiNotes 326 Set8Bakshi AmitÎncă nu există evaluări

- ECAD and VLSI Lab ManualDocument107 paginiECAD and VLSI Lab ManualHarold WilsonÎncă nu există evaluări

- STLD Bits & Exercise Problems Unit-IVDocument5 paginiSTLD Bits & Exercise Problems Unit-IVHarold WilsonÎncă nu există evaluări

- STLD QUESTION BANK Unit I and II GuideDocument16 paginiSTLD QUESTION BANK Unit I and II GuideHarold WilsonÎncă nu există evaluări

- Flip-Flops & Sequential CircuitsDocument7 paginiFlip-Flops & Sequential Circuitsmanishbhardwaj8131Încă nu există evaluări

- Question Bank Iii Semester BtechDocument18 paginiQuestion Bank Iii Semester BtechHarold WilsonÎncă nu există evaluări

- FGDFGFDocument5 paginiFGDFGFHarold WilsonÎncă nu există evaluări

- ELE2120 Digital Circuits and Systems: Tutorial Note 7Document19 paginiELE2120 Digital Circuits and Systems: Tutorial Note 7Harold Wilson100% (1)

- Karnaugh MapsDocument9 paginiKarnaugh MapsshijinbgopalÎncă nu există evaluări

- EceDocument12 paginiEcesrijha9Încă nu există evaluări

- Vlsi TD I Mtech I Sem II Mid Vlsi Es DsceDocument2 paginiVlsi TD I Mtech I Sem II Mid Vlsi Es DsceHarold WilsonÎncă nu există evaluări

- Computer Organization May 2008 Question PaperDocument4 paginiComputer Organization May 2008 Question Paperelimelek100% (1)

- Eca Lab ManualDocument56 paginiEca Lab Manualtnj_sundarÎncă nu există evaluări

- Analog CommunicationsDocument8 paginiAnalog CommunicationsHarold WilsonÎncă nu există evaluări

- Introduction To Verilog (Dr. Vu)Document183 paginiIntroduction To Verilog (Dr. Vu)htnguyen304Încă nu există evaluări

- TSGENCO Recruitment 2015Document2 paginiTSGENCO Recruitment 2015Sarepalli NaveenÎncă nu există evaluări

- Kavitha.p Ece Asst ProfDocument2 paginiKavitha.p Ece Asst ProfHarold WilsonÎncă nu există evaluări

- Nominal Rolls Cse A & B 3 Class TestDocument4 paginiNominal Rolls Cse A & B 3 Class TestHarold WilsonÎncă nu există evaluări

- Antennas and Wave PropagationDocument2 paginiAntennas and Wave PropagationHarold WilsonÎncă nu există evaluări

- Batch-3 First Contact PGMDocument58 paginiBatch-3 First Contact PGMHarold WilsonÎncă nu există evaluări

- Kavitha.p Ece Asst ProfDocument2 paginiKavitha.p Ece Asst ProfHarold WilsonÎncă nu există evaluări

- Veltech PG Vlsi RegCDocument43 paginiVeltech PG Vlsi RegCtiitumaÎncă nu există evaluări

- ECE 4514 Lecture 21 Functions and TasksDocument27 paginiECE 4514 Lecture 21 Functions and TasksHarold WilsonÎncă nu există evaluări

- ECE 4514 Digital Design II Spring 2008 Timing Analysis and Timed SimulationDocument49 paginiECE 4514 Digital Design II Spring 2008 Timing Analysis and Timed SimulationHarold WilsonÎncă nu există evaluări

- List of Helpline Centers: S.No Name of The Help Line CentreDocument1 paginăList of Helpline Centers: S.No Name of The Help Line CentreHarold WilsonÎncă nu există evaluări

- Phase-I Admissions: Admission Schedule PGECET-2014Document1 paginăPhase-I Admissions: Admission Schedule PGECET-2014Harold WilsonÎncă nu există evaluări

- Frequently Asked Questions On PGEC/PGECET AdmissionsDocument1 paginăFrequently Asked Questions On PGEC/PGECET AdmissionsHarold WilsonÎncă nu există evaluări

- Q4-Hinge Theorem-ActivityDocument2 paginiQ4-Hinge Theorem-ActivityEmelie HernandezÎncă nu există evaluări

- Munsat, S. - ProcessDocument6 paginiMunsat, S. - ProcessBen FortisÎncă nu există evaluări

- My Journey in PharmacologyDocument30 paginiMy Journey in PharmacologysureshÎncă nu există evaluări

- Mikhail Murashov: 2110 Applebrook Drive Commerce Township, MI 48382 (386) 569-8665 Personal Website: Mmurashov@adrian - EduDocument2 paginiMikhail Murashov: 2110 Applebrook Drive Commerce Township, MI 48382 (386) 569-8665 Personal Website: Mmurashov@adrian - Eduapi-242945986Încă nu există evaluări

- USA Mathematical Talent Search Solutions To Problem 5/4/18Document3 paginiUSA Mathematical Talent Search Solutions To Problem 5/4/18สฮาบูดีน สาและÎncă nu există evaluări

- SOLVED NUMERICALS EXAMPLES in Machine LearningDocument59 paginiSOLVED NUMERICALS EXAMPLES in Machine LearningYash SinhaÎncă nu există evaluări

- Itp 8Document5 paginiItp 8Arung IdÎncă nu există evaluări

- Chapter 3Document62 paginiChapter 3Matthew AloÎncă nu există evaluări

- DOO OBR Usage v3Document73 paginiDOO OBR Usage v3Kirti ThakurÎncă nu există evaluări

- High School 9-12 Reading Curriculum GuideDocument23 paginiHigh School 9-12 Reading Curriculum GuidemrsfoxÎncă nu există evaluări

- What's in The Light: Bel Air Family Investment Awarded Silver Spoon AwardDocument14 paginiWhat's in The Light: Bel Air Family Investment Awarded Silver Spoon AwardlrbrennanÎncă nu există evaluări

- NetAct Plan Editor 4.9-4 CNDocument4 paginiNetAct Plan Editor 4.9-4 CNAshraf JarjeesÎncă nu există evaluări

- IB Source AnalysisDocument8 paginiIB Source AnalysisRita LimÎncă nu există evaluări

- Resume SasDocument3 paginiResume Saslubasoft0% (1)

- Nueva Vida Outreach Specialist Job DescriptionDocument2 paginiNueva Vida Outreach Specialist Job DescriptionOffice on Latino Affairs (OLA)Încă nu există evaluări

- Resume Michal SzalonekDocument2 paginiResume Michal Szalonekszalonek4330Încă nu există evaluări

- Real and IdealDocument2 paginiReal and Idealapi-373490764Încă nu există evaluări

- Project Vetting Worksheet-9472538Document4 paginiProject Vetting Worksheet-9472538kovzsanÎncă nu există evaluări

- Axiomatic Product Development LifecycleDocument4 paginiAxiomatic Product Development LifecyclegschiroÎncă nu există evaluări

- FGD on Preparing Learning Materials at Old Cabalan Integrated SchoolDocument3 paginiFGD on Preparing Learning Materials at Old Cabalan Integrated SchoolRAQUEL TORRESÎncă nu există evaluări

- Aristotle On Practical WisdomDocument3 paginiAristotle On Practical Wisdoma4Încă nu există evaluări

- Food Chemistry: Analytical MethodsDocument7 paginiFood Chemistry: Analytical Methodswildan ariefÎncă nu există evaluări

- Inventor of 4G OFDM Technology Inspired by Dragon BallDocument7 paginiInventor of 4G OFDM Technology Inspired by Dragon BallTria RahmawatiÎncă nu există evaluări

- Bhaskar Agarwal CVDocument1 paginăBhaskar Agarwal CVbhaskaraglÎncă nu există evaluări