Documente Academic

Documente Profesional

Documente Cultură

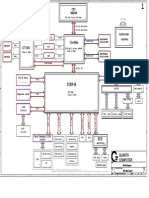

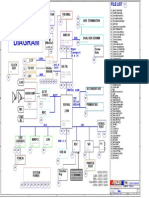

Sony-Mx2 - 1207 - For - Netin - 1208 SCHEMATIC

Încărcat de

videosonTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Sony-Mx2 - 1207 - For - Netin - 1208 SCHEMATIC

Încărcat de

videosonDrepturi de autor:

Formate disponibile

A

P264: MXM-II, G3, 256MB, 128-bit, 4/8Mx32DDR LVDS,DVI_A, DVI_B,TV_OUT,VGA

HISTORY:

A00: INITIAL VERSION 600-10264-00xx-000

3/18/04 - Started P264 from P263 design

SKU

VARIANT BASE SKU000 SKU001 SKU002 <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED>

NVPN 600-10264-xxxx-vvv 600-10264-0000-000 600-10264-0001-000 600-10264-0002-000 <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED>

ASSEMBLY BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT 256MB(128bit) FINAL NV41M 400/350 DDR1 8Mx32 144BGA, LVDS + DVI_A/DVI_B + TV_OUT + VGA NV41M 400/350 128MB(128bit) DDR1 8Mx32 144BGA, LVDS + DVI_A/DVI_B + TV_OUT + VGA NV41M 400/350 128MB(128bit) DDR1 4Mx32 144BGA, LVDS + DVI_A/DVI_B + TV_OUT + VGA <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> <UNDEFINED> 5

B 1 2 3 4 5 6 7 8 9 10 5 11 12 13 14 15

ASSEMBLY

PAGE DETAIL ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED IS'. THE MATERIALS MAY OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS CONTAIN KNOWN 'AS AND UNKNOWN VIOLATIONS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS. C E A B D

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL <edit here to insert page detail>

2701 SAN TOMAS EXPRESSWAY SANTA CLARA, CA 95050, USA

NVIDIA CORPORATION

NV_PN

600-10264-xxxx-vvv

PAGE

ID NAME F G

<XR_PAGE_TITLE>

H

DATE 7-MAY-2004

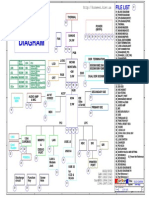

U9B

FBAD[63..0] BI FBAD0 0 1 2 3 4 5 FBAD1 FBAD2 FBAD3 FBAD4 FBAD5 FBAD6 FBAD7 FBAD8 FBAD9 FBAD10 FBAD11 FBAD12 FBAD13 FBAD14 FBAD15 FBAD16 FBAD17 FBAD18 FBAD19 FBAD20 FBAD21 FBAD22 FBAD23 FBAD24 FBAD25 FBAD26 FBAD27 FBAD28 FBAD29 FBAD30 FBAD31 FBAD32 FBAD33 FBAD34 FBAD35 FBAD36 FBAD37 FBAD38 FBAD39 FBAD40 FBAD41 FBAD42 FBAD43 FBAD44 FBAD45 FBAD46 FBAD47 FBAD48 FBAD49 FBAD50 FBAD51 FBAD52 FBAD53 FBAD54 FBAD55 FBAD56 FBAD57 FBAD58 FBAD59 FBAD60 FBAD61 FBAD62 FBAD63 BGA820_P10_33X33MM COMMON

7<>

6<>

FBCD[63..0] BI

FBVTT U9C

BGA820_P10_33X33MM COMMON

5<>

4<>

FBVDD FBVDD FBVDD FBVDD FBVDD FBVDD FBVDD FBVDD FBVDD FBVDD FBVDD FBVDD FBVDD FBVDD FBVDD FBVDD FBVDD FBVDD FBVDD FBVDD FBVDD

A12 A15 A18 A21 A24 A27 A3 A30 A6 A9 AA32 AD32 AG32 AK32 C32 F32 J32 M32 R32 V32

2/14 FBA

N27 M27 N28 L29 K27 K28 J29 J28 P30 N31 N30 N32 L31 L30 J30 L32 H30 K30 H31 F30 H32 E31 D30 E30 H28 H29 E29 J27 F27 E27 E28 F28 AD29 AE29 AD28 AC28 AB29 AA30 Y28 AB30 AM30 AF30 AJ31 AJ30 AJ32 AK29 AM31 AL30 AE32 AE30 AE31 AD30 AC31 AC32 AB32 AB31 AG27 AF28 AH28 AG28 AG29 AD27 AF27 AE28

6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34

35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 5< 4< 4<> FBADQM[7..0] OUT 0 1 2 3 4 5 6 7 5<> 4<> FBADQS[7..0] BI 0 1 2 3 4 5 6 7

FBAD0 FBAD1 FBAD2 FBAD3 FBAD4 FBAD5 FBAD6 FBAD7 FBAD8 FBAD9 FBAD10 FBAD11 FBAD12 FBAD13 FBAD14 FBAD15 FBAD16 FBAD17 FBAD18 FBAD19 FBAD20 FBAD21 FBAD22 FBAD23 FBAD24 FBAD25 FBAD26 FBAD27 FBAD28 FBAD29 FBAD30 FBAD31 FBAD32 FBAD33 FBAD34 FBAD35 FBAD36 FBAD37 FBAD38 FBAD39 FBAD40 FBAD41 FBAD42 FBAD43 FBAD44 FBAD45 FBAD46 FBAD47 FBAD48 FBAD49 FBAD50 FBAD51 FBAD52 FBAD53 FBAD54 FBAD55 FBAD56 FBAD57 FBAD58 FBAD59 FBAD60 FBAD61 FBAD62 FBAD63

3/14 FBC

FBCD0

C592 4700P 25V

C588 0.022U 16V

C587 0.022U 16V

C582 0.022U 16V

C596 0.1U 10V

0 1 2 3 4 5 6

FBCD1 FBCD2 FBCD3 FBCD4 FBCD5 FBCD6 FBCD7 FBCD8 FBCD9 FBCD10 FBCD11 FBCD12 FBCD13 FBCD14 FBCD15 FBCD16 FBCD17 FBCD18 FBCD19 FBCD20 FBCD21 FBCD22 FBCD23 FBCD24 FBCD25 FBCD26 FBCD27 FBCD28 FBCD29 FBCD30 FBCD31 FBCD32 FBCD33 FBCD34 FBCD35 FBCD36 FBCD37 FBCD38 FBCD39 FBCD40 FBCD41 FBCD42 FBCD43 FBCD44 FBCD45 FBCD46 FBCD47 FBCD48 FBCD49 FBCD50 FBCD51 FBCD52 FBCD53 FBCD54 FBCD55 FBCD56 FBCD57 FBCD58 FBCD59 FBCD60 FBCD61 FBCD62 FBCD63

GND C623 0.022U 16V C616 0.022U 16V C622 0.022U 16V C668 0.1U 10V C667 0.1U 10V

7 8 9 10 11 12 13

GND C620 0.022U 16V C695 0.022U 16V C607 0.022U 16V C567 0.1U 10V C572 0.1U 10V

14 15 16 17 18 19 20 21

FBVDDQ FBVDDQ FBVDDQ FBVDDQ FBVDDQ FBVDDQ FBVDDQ FBVDDQ FBVDDQ FBVDDQ FBVDDQ FBVDDQ FBVDDQ FBVDDQ FBVDDQ FBVDDQ FBVDDQ FBVDDQ FBVDDQ FBVDDQ FBVDDQ FBVDDQ FBVDDQ FBVDDQ

AA25 AA26 AB25 AB26 G11 G12 G15 G18 G21 G22 H11 H12 H15 H18 H21 H22 L25 L26 M25 M26 R25 R26 V25 V26

GND C677 4700P 25V C670 0.022U 16V C570 0.022U 16V C568 0.022U 16V C559 0.1U 10V C569 0.1U 10V

22 23 24 25 26 27 28 29

GND C669 1U 10V 0603 C651 1U 10V 0603 C571 0.022U 16V

30 31 32 33 34 35 36 37 38

GND

39 40 41 42 43 44 45

FBA_CMD[26..0] OUT

46 4<> 4< 5< 47 48

FBADQM0 FBADQM1 FBADQM2 FBADQM3 FBADQM4 FBADQM5 FBADQM6 FBADQM7

M29 M30 G30 F29 AA29 AK30 AC30 AG30

FBADQM0 FBADQM1 FBADQM2 FBADQM3 FBADQM4 FBADQM5 FBADQM6 FBADQM7

FBADQS0 FBADQS1 FBADQS2 FBADQS3 FBADQS4 FBADQS5 FBADQS6 FBADQS7

L28 K31 G32 G28 AB28 AL32 AF32 AH30

FBADQS_WP0 FBADQS_WP1 FBADQS_WP2 FBADQS_WP3 FBADQS_WP4 FBADQS_WP5 FBADQS_WP6 FBADQS_WP7

FBA_CMD0 P32 FBA_CMD1 U27 FBA_CMD2 P31 FBA_CMD3 U30 FBA_CMD4 Y31 FBA_CMD5 W32 FBA_CMD6 W31 FBA_CMD7 T32 FBA_CMD8 V27 FBA_CMD9 T28 FBA_CMD10 T31 FBA_CMD11 U32 FBA_CMD12 W29 FBA_CMD13 W30 FBA_CMD14 T27 FBA_CMD15 V28 FBA_CMD16 V30 FBA_CMD17 U31 FBA_CMD18 R27 FBA_CMD19 V29 FBA_CMD20 T30 FBA_CMD21 W28 FBA_CMD22 R29 FBA_CMD23 R30 FBA_CMD24 P29 FBA_CMD25 U28 FBA_CMD26 Y32

FBA_CMD0 FBA_CMD1 FBA_CMD2 FBA_CMD3 FBA_CMD4 FBA_CMD5 FBA_CMD6 FBACS1* FBACS0* FBAWE* FBA_CMD10 FBACKE 10 OUT FBA_CMD13 FBA_CMD14 FBARAS* FBA_CMD16 FBA_CMD17 FBA_CMD18 FBA_CMD19 FBA_CMD20 FBA_CMD21 FBA_CMD22 FBA_CMD23 FBA_CMD24 FBACAS* 16 17 18 19 20 21 22 23 24 OUT 4< 4<> 5< 7<> 6<> BI FBCDQS[7..0] 13 14 OUT 4< 4<> 5< 7< 6< 6<> OUT FBCDQM[7..0] 4< 4<> 5< 0 1 2 3 4 5 6 OUT OUT OUT 4< 4<> 4< 4<> 4< 4<> 5<

49 50 51 52 53 54 55 56 57 58 59 60 61 62 63

B7 A7 C7 A2 B2 C4 A5 B5 F9 F10 D12 D9 E12 D11 E8 D8 E7 F7 D6 D5 D3 E4 C3 B4 C10 B10 C8 A10 C11 C12 A11 B11 B28 C27 C26 B26 C30 B31 C29 A31 D28 D27 F26 D24 E23 E26 E24 F23 B23 A23 C25 C23 A22 C22 C21 B22 E22 D22 D21 E21 E18 D19 D18 E19

FBCD0 FBCD1 FBCD2 FBCD3 FBCD4 FBCD5 FBCD6 FBCD7 FBCD8 FBCD9 FBCD10 FBCD11 FBCD12 FBCD13 FBCD14 FBCD15 FBCD16 FBCD17 FBCD18 FBCD19 FBCD20 FBCD21 FBCD22 FBCD23 FBCD24 FBCD25 FBCD26 FBCD27 FBCD28 FBCD29 FBCD30 FBCD31 FBCD32 FBCD33 FBCD34 FBCD35 FBCD36 FBCD37 FBCD38 FBCD39 FBCD40 FBCD41 FBCD42 FBCD43 FBCD44 FBCD45 FBCD46 FBCD47 FBCD48 FBCD49 FBCD50 FBCD51 FBCD52 FBCD53 FBCD54 FBCD55 FBCD56 FBCD57 FBCD58 FBCD59 FBCD60 FBCD61 FBCD62 FBCD63

FBVTT FBVTT FBVTT FBVTT FBVTT FBVTT FBVTT FBVTT FBVTT FBVTT FBVTT FBVTT FBVTT FBVTT FBVTT FBVTT FBVTT FBVTT

AA23 AB23 H16 H17 J10 J23 J24 J9 K11 K12 K21 K22 K24 K9 L23 M23 T25 U25

C601 4700P 25V

C598 4700P 25V

C658 0.1U 10V

C632 0.1U 10V

C586 4.7U 6.3V 0603

1

GND

GND

GND

GND

GND

C600 4700P 25V

C599 4700P 25V

C603 0.1U 10V

C597 0.1U 10V

C652 4.7U 6.3V 0603

GND

GND

GND

GND

GND

C678 4700P 25V

C605 0.1U 10V

GND

GND

FBC_CMD[26..0] OUT

6< 7<

6<>

FBCDQM0 0 1 2 3 4 5 6 7 FBCDQM1 FBCDQM2 FBCDQM3 FBCDQM4 FBCDQM5 FBCDQM6 FBCDQM7

A4 E11 F5 C9 C28 F24 C24 E20

FBCDQM0 FBCDQM1 FBCDQM2 FBCDQM3 FBCDQM4 FBCDQM5 FBCDQM6 FBCDQM7

FBCDQS0 0 FBCDQS1 FBCDQS2 FBCDQS3 FBCDQS4 FBCDQS5 FBCDQS6 FBCDQS7 1 2

NET_NAME

NET_SPACING_TYPE 10MIL_G2G_20MIL 10MIL_G2G_20MIL 10MIL_G2G_20MIL 10MIL_G2G_20MIL NET_PHYSICAL_TYPE TMDS/PCIE/CLK TMDS/PCIE/CLK TMDS/PCIE/CLK TMDS/PCIE/CLK OUT OUT OUT OUT 4< 4< 4< 4< 5< 5< 5< 5<

FBA_CLK0 P28 FBA_CLK0 R28 FBA_CLK1 Y27 FBA_CLK1 AA27

FBACLK0 FBACLK0* FBACLK1 FBACLK1*

DIFF_PAIR FBACLK0 FBACLK0 FBACLK1 FBACLK1

3 4 5 6 7

C5 E10 E5 B8 A29 D25 B25 F20

FBCDQS_WP0 FBCDQS_WP1 FBCDQS_WP2 FBCDQS_WP3 FBCDQS_WP4 FBCDQS_WP5 FBCDQS_WP6 FBCDQS_WP7

FBC_CMD0 C13 FBC_CMD1 A16 FBC_CMD2 A13 FBC_CMD3 B17 FBC_CMD4 B20 FBC_CMD5 A19 FBC_CMD6 B19 FBC_CMD7 B14 FBC_CMD8 E16 FBC_CMD9 A14 FBC_CMD10 C15 FBC_CMD11 B16 FBC_CMD12 F17 FBC_CMD13 C19 FBC_CMD14 D15 FBC_CMD15 C17 FBC_CMD16 A17 FBC_CMD17 C16 FBC_CMD18 D14 FBC_CMD19 F16 FBC_CMD20 C14 FBC_CMD21 C18 FBC_CMD22 E14 FBC_CMD23 B13 FBC_CMD24 E15 FBC_CMD25 F15 FBC_CMD26 A20

FBC_CMD0 FBC_CMD1 FBC_CMD2 FBC_CMD3 FBC_CMD4 FBC_CMD5 FBC_CMD6 FBCCS1* FBCCS0* FBCWE* FBC_CMD10 FBCCKE 10 OUT FBC_CMD13 FBC_CMD14 FBCRAS* FBC_CMD16 FBC_CMD17 FBC_CMD18 FBC_CMD19 FBC_CMD20 FBC_CMD21 FBC_CMD22 FBC_CMD23 FBC_CMD24 FBCCAS* 16 17 18 19 20 21 22 23 24 OUT 6< 6<> 7< 13 14 OUT 6< 6<> 7< 6< 6<> 7< 0 1 2 3 4 5 6 OUT OUT OUT 6< 6< 6< 6<> 6<> 6<> 7<

NET_NAME

NET_SPACING_TYPE 10MIL_G2G_20MIL 10MIL_G2G_20MIL 10MIL_G2G_20MIL 10MIL_G2G_20MIL NET_PHYSICAL_TYPE TMDS/PCIE/CLK OUT TMDS/PCIE/CLK OUT TMDS/PCIE/CLK TMDS/PCIE/CLK OUT OUT 6< 6< 6< 6< 7< 7< 7< 7<

M28 K32 G31 G27 AA28 AL31 AF31 AH29

FBADQS_RN0 FBADQS_RN1 FBADQS_RN2 FBADQS_RN3 FBADQS_RN4 FBADQS_RN5 FBADQS_RN6 FBADQS_RN7 RFU RFU

Y30 AC26

FBC_CLK0 E13 FBC_CLK0 F13 FBC_CLK1 F18 FBC_CLK1 E17

FBCCLK0 FBCCLK0* FBCCLK1 FBCCLK1*

DIFF_PAIR FBCCLK0 FBCCLK0 FBCCLK1 FBCCLK1

C6 E9 E6 A8 B29 E25 A25 F21

FBCDQS_RN0 FBCDQS_RN1 FBCDQS_RN2 FBCDQS_RN3 FBCDQS_RN4 FBCDQS_RN5 FBCDQS_RN6 FBCDQS_RN7 RFU RFU

C20 D1

3V3RUN

LB503 BLM18PG181SN1D 0603 C591 470P 50V C581 0.022U 16V C554 1U 10V 0603

4

FBA_DEBUGAC27 FBA_REFCLKD32 FBA_REFCLKD31 3V3RUN FBVDD FBA_PLLVDD G23

G25 FBA_PLLAVDD

FBA_PLLVDD 12_mil

FBC_DEBUGF12 FBC_REFCLKB1 FBC_REFCLKC1

GND

GND

GND

NVVDD

FBA_PLLAVDD

LB501 BLM18PG181SN1D 0603 C589 0.022U 16V C552 1U 10V 0603

FBVDD FBC_PLLVDD G8

G10 FBC_PLLAVDD

FBC_PLLVDD 12_mil FBC_PLLAVDD 12_mil

LB502 BLM18PG181SN1D 0603 C580 470P 50V C585 0.022U 16V C560 1U 10V 0603

C583 *0.022U 16V

R554 10K 1%

12_mil FBVREF1

FBA_PLLGNDG24

C590 470P 50V GND

C558 *0.022U 16V

NVVDD

E32

FB_VREF1

R530 10K 1%

12_mil FB_VREF2

FBC_PLLGNDG9

GND GND

A28

GND R563 R553 37.4 1%

GND

FBVDD

GND

12_mil

GND

GND LB504 BLM18PG181SN1D 0603

C579 *0.022U 16V

FB_VREF2

K26 FBCAL_PD_VDDQ H26 FBCAL_PU_GND

FBCAL_PD_VDDQ

12_mil

37.4 1%

R541 10K 1% C595 470P 50V C584 0.022U 16V C638 1U 10V 0603

FBCAL_PU_GND

12_mil

C557 *0.022U 16V

R529 10K 1%

J26 FBCAL_TERM_GND

FBCAL_TERM_GND 12_mil

R565

GND GND GND

5

GND

GND

GND

GND

ASSEMBLY

PAGE DETAIL ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED IS'. THE MATERIALS MAY OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS CONTAIN KNOWN 'AS AND UNKNOWN VIOLATIONS OR OTHERWISE, AND EXPRESSLY ALL IMPLIED WARRANTIES INCLUDING, DISCLAIMS WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS. A B D C E

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL <edit here to insert page detail>

2701 SAN TOMAS EXPRESSWAY SANTA CLARA, CA 95050, USA

NVIDIA CORPORATION

NV_PN

600-10264-xxxx-vvv

PAGE

ID NAME F G

<CON_PAGE_NUM> OF <CON_TOTAL_PAGES>

H

DATE 7-MAY-2004

MEMORY 128/256MB, 8Mx32DDR, PARTITION A, BANK 0 PLACE ALL DISCRETE COMPONENTS AS NEAR AS POSSIBLE TO MEMORY

1

NET

Diffpair

NET_SPACING_RULE

5<>

4<> 5< 4<

3<> 3> 3<>

FBAD[63..0] BI BI BI FBADQM[7..0] FBADQS[7..0]

10MIL 10MIL 10MIL

5<>

4<>

5< Stuff for stacked die 4<> 3> FBACS1* IN

4<

3>

FBA_CMD[26..0] BI FBARAS* BI BI BI BI BI FBACAS* FBAWE* FBACS0* FBACS1*

10MIL

R576 R574

*0 0

FBA_B0_CS1* OUT FBA_B1_CS1* OUT

4<

4<>

U7B

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON 5< 4<> 4<> 4<> 4<> 4<> FBA_CMD[26..0] IN 1 3 2 0 24 22 21 23 19 3> 3> 3> 3> 4> FBARAS* IN IN IN IN IN FBA_CMD1 FBA_CMD3 FBA_CMD2 FBA_CMD0 FBA_CMD24 FBA_CMD22 FBA_CMD21 FBA_CMD23 FBA_CMD19 FBA_CMD20 FBA_CMD17 FBA_CMD16 FBA_CMD14 FBACAS* FBAWE* FBACS0* FBA_B0_CS1*

U10B FBVDD

FBARAS* FBACAS* FBAWE* FBACS0* FBA_B0_CS1* 4< 4<> 3> 5< FBA_CMD[26..0] IN 1 3 13 FBA_CMD1 FBA_CMD3 FBA_CMD13 FBA_CMD4 FBA_CMD5 FBA_CMD6 FBA_CMD21 FBA_CMD23 FBA_CMD19 FBA_CMD20 FBA_CMD17 FBA_CMD16 FBA_CMD14 BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON

5< 5<

4< 4< 4< 4< 4<

3> 3> 3> 3> 3>

10MIL 10MIL 10MIL 10MIL 10MIL

FBVDD

5<

4<>

5<

Stuff for monolithic die

5< 5<

M2 L2 L3 N2 M4 N5 N6 M6 N7 N8 M9 N9 N10 N11 M8 L6 M7 L9 N4 M5 M10

RAS 2/4/8MX32 CAS WE CS<0> CS<1>/TBD. A<0> A<1> A<2> A<3> A<4> A<5> A<6> A<7> A/AP<8> A<9> A<10> A<11> A<12>/TBD. BA<0> BA<1> BA<2>/TBD.

5<

4<

4<>

3>

VDD D7 VDD D8 VDD E4 VDD E11 VDD L4 VDD L7 VDD L8 VDD L11

C3 VDDQ C5 VDDQ C7 VDDQ C8 VDDQ C10 VDDQ C12 VDDQ E3 VDDQ E12 VDDQ F4 VDDQ F11 VDDQ G4 VDDQ G11 VDDQ J4 VDDQ J11 VDDQ K4 VDDQ K11 VDDQ B4 VSSQ B11 VSSQ D4 VSSQ D5 VSSQ D6 VSSQ D9 VSSQ D10 VSSQ D11 VSSQ E6 VSSQ E9 VSSQ F5 VSSQ F10 VSSQ G5 VSSQ G10 VSSQ H5 VSSQ H10 VSSQ J5 VSSQ J10 VSSQ K5 VSSQ K10 VSSQ

M2 L2 L3 N2 M4 N5 N6 M6 N7 N8 M9 N9 N10 N11 M8 L6 M7 L9 N4 M5 M10

RAS 2/4/8MX32 CAS WE CS<0> CS<1>/TBD. A<0> A<1> A<2> A<3> A<4> A<5> A<6> A<7> A/AP<8> A<9> A<10> A<11> A<12>/TBD. BA<0> BA<1> BA<2>/TBD.

FBVDD

VDDD7 VDDD8 VDDE4 VDDE11 VDDL4 VDDL7 VDDL8 VDDL11

C3 VDDQ C5 VDDQ C7 VDDQ C8 VDDQ C10 VDDQ C12 VDDQ E3 VDDQ E12 VDDQ F4 VDDQ F11 VDDQ G4 VDDQ G11 VDDQ J4 VDDQ J11 VDDQ K4 VDDQ K11 VDDQ B4 VSSQ B11 VSSQ D4 VSSQ D5 VSSQ D6 VSSQ D9 VSSQ D10 VSSQ D11 VSSQ E6 VSSQ E9 VSSQ F5 VSSQ F10 VSSQ G5 VSSQ G10 VSSQ H5 VSSQ H10 VSSQ J5 VSSQ J10 VSSQ K5 VSSQ K10 VSSQ

5<

4< 4< 5<

3> 4> 4>

FBACKE BI BI BI FBA_B0_CS1* FBA_B1_CS1*

10MIL 10MIL 10MIL

FBVDD

4 5 6 21 23 19 20 17 16 14

Decoupling for left MEMORY

FBVDD

FBVDD 2

20 17

Place around the MEM

2

R62

120

16 14

R63

120

10 FBACLK1 18

FBA_CMD10 FBA_CMD18

10 18

FBA_CMD10 FBA_CMD18

C77 0.1U 10V

C104 0.1U 10V

C80 0.1U 10V

C75 0.1U 10V

C91 0.01U 25V

C68 0.01U 25V

C70 0.01U 25V

R57

120

R60 619 1%

FBACLK1*

5<

4<> 5< 5<

3> 3> 3>

FBACKE IN IN IN FBACLK0 FBACLK0*

N12 M11 M12

R58 R527

120 120

CKE CLK CLK

FBACKE 5< 5< 3> 3> FBACLK1 IN IN FBACLK1*

N12 M11 M12

CKE CLK CLK

GND

R573 10K R525 120

FBACLK0

FBVDD

R526

120

R17 619 1%

FBACLK0*

GND

R524

120

C66 4.7U 6.3V 0603

C76 0.1U 10V

C81 0.1U 10V

C85 0.1U 10V

C84 0.01U 25V

C78 0.1U 10V

C89 0.1U 10V

C88 0.1U 10V

C93 0.1U 10V

C71 0.1U 10V

C72 0.1U 10V

C90 0.1U 10V

GND

F6 F7 F8 F9 G6 G7 G8 G9 H6 H7 H8 H9 J6 J7 J8 J9 M13

THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM Must be GND

NC NC NC NC NC NC NC NC

VSS E5 VSS E7 VSS E8 VSS E10 VSS K6 VSS K7 VSS K8 VSS K9 VSS L5 VSS L10 Vref

N13

FBAREF1 12_mil

FBVDD

R23 10K 1%

F6 F7 F8 F9 G6 G7 G8 G9 H6 H7 H8 H9 J6 J7 J8 J9 M13

THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM Must be GND

NC NC NC NC NC NC NC NC

GND C87 0.1U 10V C82 0.01U 25V C73 0.1U 10V C69 0.01U 25V C92 0.01U 25V C94 0.1U 10V

VSS E5 VSS E7 VSS E8 VSS E10 VSS K6 VSS K7 VSS K8 VSS K9 VSS L5 VSS L10 Vref

N13

FBAREF0 12_mil

FBVDD

R47 10K 1%

GND

Decoupling for right MEMORY

Place around the MEM

C100 0.1U 10V R44 6.81K 1%

FBVDD

C4 C11 H4 H11 L12 L13 M3 N3

C4 C11 H4 H11 L12 L13 M3 N3

GND

C79 0.1U 10V

R25 6.81K 1%

GND

GND

GND

GND

GND

C127 4.7U 6.3V 0603

C124 0.1U 10V

C118 0.1U 10V

C120 0.01U 25V

C121 0.1U 10V

C106 0.1U 10V

C117 0.1U 10V

C107 0.1U 10V

C96 0.01U 25V

5< 5< 5< 5< 5<

4<> 4<> 4<> 4<> 4<> 4<> 4<> 4<>

3> 3> 3> 3> 3> 3> 3> 3>

FBADQM0 IN IN IN IN IN IN IN IN FBADQM1 FBADQM2 FBADQM3 FBADQM4 FBADQM5 FBADQM6 FBADQM7

5<>

4<>

3<>

FBAD[63..0] BI

GND

U7A

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON 6 7 5 4 2 3 1 0 FBAD6 FBAD7 FBAD5 FBAD4 FBAD2 FBAD3 FBAD1 FBAD0 FBADQM0 FBADQS0

U7D

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON

U10A

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON FBAD39 39 37 38 36 35 33 34 32 FBADQM4 FBADQS4 FBAD37 FBAD38 FBAD36 FBAD35 FBAD33 FBAD34 FBAD32

U10D

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON

5< 5< 5<

B5 C6 B6 B7 D2 D3 C2 E2 B3 B2

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

22 23 20 21 19 18 16 17

FBAD22 FBAD23 FBAD20 FBAD21 FBAD19 FBAD18 FBAD16 FBAD17 FBADQM2 FBADQS2

K13 G13 G12 J13 F13 K12 F12 J12 H12 H13

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

D13 C13 E13 D12 B8 C9 B10 B9 B12 B13

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

FBAD55 55 53 54 52 51 49 50 48 FBADQM6 FBADQS6 FBAD53 FBAD54 FBAD52 FBAD51 FBAD49 FBAD50 FBAD48

G13 F13 K13 J13 F12 J12 K12 G12 H12 H13

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

FBVDD

C125 0.1U 10V

C114 0.1U 10V

C102 0.1U 10V

C101 0.1U 10V

C98 0.01U 25V

C112 0.01U 25V

C99 0.1U 10V

C97 0.1U 10V

C122 0.01U 25V

GND

FBAD[63..0]

U7E

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON FBADQS0 BI BI BI BI BI BI BI BI FBADQS1 FBADQS2 FBADQS3 FBADQS4 FBADQS5 FBADQS6 FBADQS7 15 13 14 12 11 9 10 8 FBAD15 FBAD13 FBAD14 FBAD12 FBAD11 FBAD9 FBAD10 FBAD8 FBADQM1 FBADQS1

U7C

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON

U10E

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON FBAD46 46 47 45 44 42 43 41 40 FBADQM5 FBADQS5 FBAD47 FBAD45 FBAD44 FBAD42 FBAD43 FBAD41 FBAD40

U10C

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON

C113 0.1U 10V

C108 0.01U 25V

C123 0.01U 25V

C116 0.1U 10V

C95 0.1U 10V

5<> 5<> 5<> 5<> 5<> 5<> 5<> 5<>

4<> 4<> 4<> 4<> 4<> 4<> 4<> 4<>

3<> 3<> 3<> 3<> 3<> 3<> 3<> 3<>

G3 K3 J3 F3 J2 G2 F2 K2 H3 H2

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

31 29 30 28 27 25 26 24

FBAD31 FBAD29 FBAD30 FBAD28 FBAD27 FBAD25 FBAD26 FBAD24 FBADQM3 FBADQS3

D12 D13 E13 C9 B10 B8 C13 B9 B12 B13

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

G2 J2 F2 G3 K3 F3 J3 K2 H3 H2

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

FBAD62 62 63 60 61 59 58 56 57 FBADQM7 FBADQS7 FBAD63 FBAD60 FBAD61 FBAD59 FBAD58 FBAD56 FBAD57

B5 B7 C6 B6 D2 D3 E2 C2 B3 B2

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

GND

ASSEMBLY

PAGE DETAIL ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED IS'. THE MATERIALS MAY OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS CONTAIN KNOWN 'AS AND UNKNOWN VIOLATIONS OR OTHERWISE, AND EXPRESSLY ALL IMPLIED WARRANTIES INCLUDING, DISCLAIMS WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS. A B D C E

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL <edit here to insert page detail>

2701 SAN TOMAS EXPRESSWAY SANTA CLARA, CA 95050, USA

NVIDIA CORPORATION

NV_PN

600-10264-xxxx-vvv

PAGE

ID NAME F G

<CON_PAGE_NUM> OF <CON_TOTAL_PAGES>

H

DATE 7-MAY-2004

MEMORY 128/256MB, 8Mx32DDR, PARTITION A, BANK 1 PLACE ALL DISCRETE COMPONENTS AS NEAR AS POSSIBLE TO MEMORY

need to hook up bank 1 signal

U504B

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON 4<> 4<> 4<> 4< 4< 4< 4<> 3> 3> 3> 4> FBARAS* IN IN IN IN FBACAS* FBAWE* FBA_B1_CS1*

U505B FBVDD

FBARAS* FBACAS* FBAWE* FBA_B1_CS1* 4<> 5< 3> 4< FBA_CMD[26..0] IN 23 21 6 5 4 13 3 1 16 17 20 19 14 18 10 FBA_CMD23 FBA_CMD21 FBA_CMD6 FBA_CMD5 FBA_CMD4 FBA_CMD13 FBA_CMD3 FBA_CMD1 FBA_CMD16 FBA_CMD17 FBA_CMD20 FBA_CMD19 FBA_CMD14 FBA_CMD18 FBA_CMD10 BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON

FBVDD

M2 L2 L3 N2 M4 N5 N6 M6 N7 N8 M9 N9 N10 N11 M8 L6 M7 L9 N4 M5 M10

RAS 2/4/8MX32 CAS WE CS<0> CS<1>/TBD. A<0> A<1> A<2> A<3> A<4> A<5> A<6> A<7> A/AP<8> A<9> A<10> A<11> A<12>/TBD. BA<0> BA<1> BA<2>/TBD.

5<

4<

4<>

3>

FBA_CMD[26..0] IN 23 21 22 24 0 2 3 1 16 17 20 19 14 18 10

FBA_CMD23 FBA_CMD21 FBA_CMD22 FBA_CMD24 FBA_CMD0 FBA_CMD2 FBA_CMD3 FBA_CMD1 FBA_CMD16 FBA_CMD17 FBA_CMD20 FBA_CMD19 FBA_CMD14 FBA_CMD18 FBA_CMD10

VDD D7 VDD D8 VDD E4 VDD E11 VDD L4 VDD L7 VDD L8 VDD L11

C3 VDDQ C5 VDDQ C7 VDDQ C8 VDDQ C10 VDDQ C12 VDDQ E3 VDDQ E12 VDDQ F4 VDDQ F11 VDDQ G4 VDDQ G11 VDDQ J4 VDDQ J11 VDDQ K4 VDDQ K11 VDDQ

M2 L2 L3 N2 M4 N5 N6 M6 N7 N8 M9 N9 N10 N11 M8 L6 M7 L9 N4 M5 M10

RAS 2/4/8MX32 CAS WE CS<0> CS<1>/TBD. A<0> A<1> A<2> A<3> A<4> A<5> A<6> A<7> A/AP<8> A<9> A<10> A<11> A<12>/TBD. BA<0> BA<1> BA<2>/TBD.

FBVDD

VDD D7 VDD D8 VDD E4 VDD E11 VDD L4 VDD L7 VDD L8 VDD L11

C3 VDDQ C5 VDDQ C7 VDDQ C8 VDDQ C10 VDDQ C12 VDDQ E3 VDDQ E12 VDDQ F4 VDDQ F11 VDDQ G4 VDDQ G11 VDDQ J4 VDDQ J11 VDDQ K4 VDDQ K11 VDDQ

FBVDD

Decoupling for left MEMORY

FBVDD

Place around the MEM

2

C726 0.1U 10V

C604 0.1U 10V

C732 0.1U 10V

C729 0.1U 10V

C736 0.01U 25V

C731 0.1U 10V

C657 0.1U 10V

C655 0.1U 10V

4<>

4< 4< 4<

3> 3> 3>

FBACKE IN IN IN FBACLK0 FBACLK0*

N12 M11 M12

CKE CLK CLK

FBACKE 4< 4< 3> 3> FBACLK1 IN IN FBACLK1*

F6 F7 F8 F9 G6 G7 G8 G9 H6 H7 H8 H9 J6 J7 J8 J9 M13

THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM Must be GND

NC NC NC NC NC NC NC NC

VSSQB4 VSSQB11 VSSQD4 VSSQD5 VSSQD6 VSSQD9 VSSQD10 VSSQD11 VSSQE6 VSSQE9 VSSQF5 VSSQF10 VSSQG5 VSSQG10 VSSQH5 VSSQH10 VSSQJ5 VSSQJ10 VSSQK5 VSSQK10 VSS E5 VSS E7 VSS E8 VSS E10 VSS K6 VSS K7 VSS K8 VSS K9 VSS L5 VSS L10 Vref

N13

FBAREF3 12_mil

N12 M11 M12

CKE CLK CLK

FBVDD

R564 10K 1%

F6 F7 F8 F9 G6 G7 G8 G9 H6 H7 H8 H9 J6 J7 J8 J9 M13

THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM Must be GND

NC NC NC NC NC NC NC NC

VSSQB4 VSSQB11 VSSQD4 VSSQD5 VSSQD6 VSSQD9 VSSQD10 VSSQD11 VSSQE6 VSSQE9 VSSQF5 VSSQF10 VSSQG5 VSSQG10 VSSQH5 VSSQH10 VSSQJ5 VSSQJ10 VSSQK5 VSSQK10 VSS E5 VSS E7 VSS E8 VSS E10 VSS K6 VSS K7 VSS K8 VSS K9 VSS L5 VSS L10 Vref

N13

FBAREF4 12_mil

GND

FBVDD

C733 0.01U 25V

C730 0.1U 10V

C725 0.1U 10V

C735 0.1U 10V

C738 0.1U 10V

C734 0.1U 10V

C737 0.01U 25V

C653 0.1U 10V

C724 0.01U 25V

GND C699 0.01U 25V

FBVDD

C654 0.01U 25V

C656 0.01U 25V

C681 0.1U 10V

3

GND R594 10K 1%

Decoupling for right MEMORY

Place around the MEM

FBVDD

C4 C11 H4 H11 L12 L13 M3 N3

C4 C11 H4 H11 L12 L13 M3 N3

GND

C615 0.1U 10V

R568 6.81K 1%

GND

C728 0.1U 10V

R588 6.81K 1%

GND

GND

GND

GND

C610 0.1U 10V

C573 0.1U 10V

C574 0.1U 10V

C575 0.1U 10V

C637 0.1U 10V

C636 0.01U 25V

C565 0.1U 10V

4< 4< 4< 4< 4< 4< 4< 4<

4<> 4<> 4<> 4<> 4<> 4<> 4<> 4<>

3> 3> 3> 3> 3> 3> 3> 3>

FBADQM0 IN IN IN IN IN IN IN IN FBADQM1 FBADQM2 FBADQM3 FBADQM4 FBADQM5 FBADQM6 FBADQM7

4<>

3<>

FBAD[63..0] BI

U504A

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON 6 7 5 4 2 3 1 0 FBAD6 FBAD7 FBAD5 FBAD4 FBAD2 FBAD3 FBAD1 FBAD0 FBADQM0 FBADQS0

U504D

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON

U505A

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON FBAD55 DQ<0> 55 FBAD53 DQ<1> 53 FBAD54 DQ<2> 54 FBAD52 DQ<3> 52 FBAD51 DQ<4> 51 FBAD49 DQ<5> 49 FBAD50 DQ<6> 50 FBAD48 DQ<7> 48

U505D

GND

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON FBVDD

B10 C9 B9 B8 D13 D12 C13 E13 B12 B13

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

22 23 20 21 19 18 16 17

FBAD22 FBAD23 FBAD20 FBAD21 FBAD19 FBAD18 FBAD16 FBAD17 FBADQM2 FBADQS2

K2 G2 G3 J2 F2 K3 F3 J3 H3 H2

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

FBAD39 39 37 38 36 35 33 34 32 FBADQM4 FBADQS4 FBAD37 FBAD38 FBAD36 FBAD35 FBAD33 FBAD34 FBAD32

D2 C2 E2 D3 B7 C6 B5 B6 B3 B2

G2 F2 K2 J2 F3 J3 K3 G3 H3 H2

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

C556 4.7U 6.3V 0603

C578 0.01U 25V

C576 0.1U 10V

C577 0.1U 10V

C566 0.01U 25V

C635 0.1U 10V

C634 0.01U 25V

C561 0.1U 10V

DQM DQS

FBADQM6 FBADQS6

GND

FBAD[63..0]

U504E

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON FBADQS0 BI BI BI BI BI BI BI BI FBADQS1 FBADQS2 FBADQS3 FBADQS4 FBADQS5 FBADQS6 FBADQS7 15 13 14 12 11 9 10 8 FBAD15 FBAD13 FBAD14 FBAD12 FBAD11 FBAD9 FBAD10 FBAD8 FBADQM1 FBADQS1

U504C

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON

U505E

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON FBAD62 DQ<0> 62 FBAD63 DQ<1> 63 FBAD60 DQ<2> 60 FBAD61 DQ<3> 61 FBAD59 DQ<4> 59 FBAD58 DQ<5> 58 FBAD56 DQ<6> 56 FBAD57 DQ<7> 57

U505C

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON

C593 0.01U 25V

C564 0.01U 25V

C562 0.1U 10V

C633 0.1U 10V

C563 0.01U 25V

4<> 4<> 4<> 4<> 4<> 4<> 4<> 4<>

3<> 3<> 3<> 3<> 3<> 3<> 3<> 3<>

G12 K12 J12 F12 J13 G13 F13 K13 H12 H13

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

31 29 30 28 27 25 26 24

FBAD31 FBAD29 FBAD30 FBAD28 FBAD27 FBAD25 FBAD26 FBAD24 FBADQM3 FBADQS3

D3 D2 E2 C6 B5 B7 C2 B6 B3 B2

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

FBAD46 46 47 45 44 42 43 41 40 FBADQM5 FBADQS5 FBAD47 FBAD45 FBAD44 FBAD42 FBAD43 FBAD41 FBAD40

G13 J13 F13 G12 K12 F12 J12 K13 H12 H13

B10 B8 C9 B9 D13 D12 E13 C13 B12 B13

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

GND

DQM DQS

FBADQM7 FBADQS7

ASSEMBLY

PAGE DETAIL ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED IS'. THE MATERIALS MAY OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS CONTAIN KNOWN 'AS AND UNKNOWN VIOLATIONS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS. C E A B D

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL <edit here to insert page detail>

2701 SAN TOMAS EXPRESSWAY SANTA CLARA, CA 95050, USA

NVIDIA CORPORATION

NV_PN

600-10264-xxxx-vvv

PAGE

ID NAME F G

<XR_PAGE_TITLE>

H

DATE 7-MAY-2004

MEMORY 128/256MB, 8Mx32DDR, PARTITION C, BANK 0 PLACE ALL DISCRETE COMPONENTS AS NEAR AS POSSIBLE TO MEMORY

1

stuff for stacked die 6<> 3> FBCCS1* IN

NET

Diffpair

NET_SPACING_RULE

7<>

6<> 7< 6<

3<> 3> 3<>

FBCD[63..0] BI BI BI FBCDQM[7..0] FBCDQS[7..0]

10MIL 10MIL 10MIL

7<>

6<>

U2B

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON FBC_B0_CS0* OUT 6< 6<> 7< 7< 7< 6<> 6<> 6<> 6<> 6<> stuff for monolithic die FBC_CMD[26..0] IN 1 3 2 0 24 22 21 23 19 3> 3> 3> 3> 6> FBCRAS* IN IN IN IN IN FBC_CMD1 FBC_CMD3 FBC_CMD2 FBC_CMD0 FBC_CMD24 FBC_CMD22 FBC_CMD21 FBC_CMD23 FBC_CMD19 FBC_CMD20 FBC_CMD17 FBC_CMD16 FBC_CMD14 FBCCAS* FBCWE* FBCCS0* FBC_B0_CS0*

U3B FBVDD

FBCRAS* FBCCAS* FBCWE* FBCCS0* FBC_B0_CS0* 6<> 6< 3> 7< FBC_CMD[26..0] IN 1 3 13 FBC_CMD1 FBC_CMD3 FBC_CMD13 FBC_CMD4 FBC_CMD5 FBC_CMD6 FBC_CMD21 FBC_CMD23 FBC_CMD19 FBC_CMD20 FBC_CMD17 FBC_CMD16 FBC_CMD14 BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON

1 FBVDD

R506

*0

R507

FBC_B1_CS1* OUT

7<

M2 L2 L3 N2 M4 N5 N6 M6 N7 N8 M9 N9 N10 N11 M8 L6 M7 L9 N4 M5 M10

RAS 2/4/8MX32 CAS WE CS<0> CS<1>/TBD. A<0> A<1> A<2> A<3> A<4> A<5> A<6> A<7> A/AP<8> A<9> A<10> A<11> A<12>/TBD. BA<0> BA<1> BA<2>/TBD.

7<

6<>

6<

3>

VDDD7 VDDD8 VDDE4 VDDE11 VDDL4 VDDL7 VDDL8 VDDL11

C3 VDDQ C5 VDDQ C7 VDDQ C8 VDDQ C10 VDDQ C12 VDDQ E3 VDDQ E12 VDDQ F4 VDDQ F11 VDDQ G4 VDDQ G11 VDDQ J4 VDDQ J11 VDDQ K4 VDDQ K11 VDDQ B4 VSSQ B11 VSSQ D4 VSSQ D5 VSSQ D6 VSSQ D9 VSSQ D10 VSSQ D11 VSSQ E6 VSSQ E9 VSSQ F5 VSSQ F10 VSSQ G5 VSSQ G10 VSSQ H5 VSSQ H10 VSSQ J5 VSSQ J10 VSSQ K5 VSSQ K10 VSSQ

M2 L2 L3 N2 M4 N5 N6 M6 N7 N8 M9 N9 N10 N11 M8 L6 M7 L9 N4 M5 M10

RAS 2/4/8MX32 CAS WE CS<0> CS<1>/TBD. A<0> A<1> A<2> A<3> A<4> A<5> A<6> A<7> A/AP<8> A<9> A<10> A<11> A<12>/TBD. BA<0> BA<1> BA<2>/TBD.

FBVDD

VDD D7 VDD D8 VDD E4 VDD E11 VDD L4 VDD L7 VDD L8 VDD L11

C3 VDDQ C5 VDDQ C7 VDDQ C8 VDDQ C10 VDDQ C12 VDDQ E3 VDDQ E12 VDDQ F4 VDDQ F11 VDDQ G4 VDDQ G11 VDDQ J4 VDDQ J11 VDDQ K4 VDDQ K11 VDDQ B4 VSSQ B11 VSSQ D4 VSSQ D5 VSSQ D6 VSSQ D9 VSSQ D10 VSSQ D11 VSSQ E6 VSSQ E9 VSSQ F5 VSSQ F10 VSSQ G5 VSSQ G10 VSSQ H5 VSSQ H10 VSSQ J5 VSSQ J10 VSSQ K5 VSSQ K10 VSSQ

7<

6<

3>

FBC_CMD[26..0] BI FBCRAS* BI BI BI BI BI FBCCAS* FBCWE* FBCCS0* FBCCS1*

10MIL

7< 7< 7<

6< 6< 6< 6<

3> 3> 3> 3> 3>

10MIL 10MIL 10MIL 10MIL 10MIL

FBVDD

6<

4 5 6 21 23 19 20 17 16 14

7<

6< 6>

3> 6<

FBCCKE BI BI FBC_B0_CS0*

10MIL 10MIL

FBVDD

20 17

R514

120

16 14

R513

120

FBCCLK1

10 18

FBC_CMD10 FBC_CMD18

10 18

FBC_CMD10 FBC_CMD18

Decoupling for left MEMORY

FBVDD

Place around the MEM

R509

120

R511 619 1%

FBCCLK1*

7<

6<> 7< 7<

3> 3> 3>

FBCCKE IN IN IN FBCCLK0 FBCCLK0*

N12 M11 M12

R508 R515

120 120

CKE CLK CLK

FBCCKE 7< 7< 3> 3> FBCCLK1 IN IN FBCCLK1*

N12 M11 M12

CKE CLK CLK

C59 0.01U 25V

C22 0.1U 10V

C25 0.1U 10V

C11 0.1U 10V

C58 0.01U 25V

C44 0.1U 10V

C49 0.01U 25V

C26 0.1U 10V

C36 0.01U 25V

R501 10K R516 120

FBCCLK0

GND

R512

120

R6 619 1%

FBCCLK0*

GND

FBVDD

R510

120

GND

F6 F7 F8 F9 G6 G7 G8 G9 H6 H7 H8 H9 J6 J7 J8 J9 M13

THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM Must be GND

NC NC NC NC NC NC NC NC

FBVDD

VSS E5 VSS E7 VSS E8 VSS E10 VSS K6 VSS K7 VSS K8 VSS K9 VSS L5 VSS L10 Vref

N13

FBCVREF1 12_mil

R1 10K 1%

F6 F7 F8 F9 G6 G7 G8 G9 H6 H7 H8 H9 J6 J7 J8 J9 M13

THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM Must be GND

NC NC NC NC NC NC NC NC

FBVDD

VSS E5 VSS E7 VSS E8 VSS E10 VSS K6 VSS K7 VSS K8 VSS K9 VSS L5 VSS L10 Vref

N13

FBCVREF0 12_mil

C47 4.7U 6.3V 0603

C3 0.1U 10V

C57 0.1U 10V

C4 0.1U 10V

C2 0.1U 10V

C10 0.1U 10V

C9 0.1U 10V

C8 0.1U 10V

C20 0.1U 10V

C48 0.1U 10V

C28 0.1U 10V

GND R4 10K 1% C60 0.1U 10V C34 0.1U 10V C31 0.01U 25V C55 0.01U 25V C41 0.01U 25V

C4 C11 H4 H11 L12 L13 M3 N3

C4 C11 H4 H11 L12 L13 M3 N3

GND

C23 0.1U 10V

R2 6.81K 1%

GND

C24 0.1U 10V

R3 6.81K 1%

GND

Decoupling for left MEMORY

FBVDD

7< 7< 7< 7< 7< 7< 7< 7<

6<> 6<> 6<> 6<> 6<> 6<> 6<> 6<>

3> 3> 3> 3> 3> 3> 3> 3>

FBCDQM0 IN IN IN IN IN IN IN IN FBCDQM1 FBCDQM2 FBCDQM3 FBCDQM4 FBCDQM5 FBCDQM6 FBCDQM7 7<> 6<> 3<> FBCD[63..0] BI

Place around the MEM

GND

GND

GND

GND

U2A

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON FBCD6 6 7 5 4 2 3 1 FBCD7 FBCD5 FBCD4 FBCD2 FBCD3 FBCD1 FBCD0

U2D

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON

U3A

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON FBCD39 39 37 38 36 35 33 34 32 FBCDQM4 FBCDQS4 FBCD37 FBCD38 FBCD36 FBCD35 FBCD33 FBCD34 FBCD32

U3D

C53 4.7U

6.3V BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON 0603

J13 F13 K13 G13 K12 G12 J12 F12 H12 H13

C37 0.01U 25V

C7 0.1U 10V

C27 0.1U 10V

C35 0.1U 10V

C63 0.01U 25V

C62 0.01U 25V

C13 0.1U 10V

C45 0.1U 10V

C56 0.01U 25V

0 FBCDQM0 FBCDQS0

F13 F12 J13 G13 K12 K13 G12 J12 H12 H13

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

FBCD22 22 23 20 21 19 18 16 17 FBCDQM2 FBCDQS2 FBCD23 FBCD20 FBCD21 FBCD19 FBCD18 FBCD16 FBCD17

D12 C13 D13 E13 C9 B10 B8 B9 B12 B13

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

G2 K2 F2 J2 J3 F3 K3 G3 H3 H2

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

FBCD55 55 53 54 52 51 49 50 48 FBCDQM6 FBCDQS6 FBCD53 FBCD54 FBCD52 FBCD51 FBCD49 FBCD50 FBCD48

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

GND

FBVDD 4

FBCD[63..0]

C21 0.1U 10V

U2E

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON

C5 0.1U 10V

C51 0.01U 25V

C6 0.1U 10V

C12 0.1U 10V

C14 0.1U 10V

C15 0.1U 10V

C42 0.01U 25V

C50 0.01U 25V

U2C

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON

U3E

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON FBCD46 46 47 45 44 42 43 41 40 FBCDQM5 FBCDQS5 FBCD47 FBCD45 FBCD44 FBCD42 FBCD43 FBCD41 FBCD40

U3C

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON

FBCD15 7<> 7<> 7<> 7<> 7<> 7<> 7<> 7<> 6<> 6<> 6<> 6<> 6<> 6<> 6<> 6<> 3<> 3<> 3<> 3<> 3<> 3<> 3<> 3<> FBCDQS0 BI BI BI BI BI BI BI BI FBCDQS1 FBCDQS2 FBCDQS3 FBCDQS4 FBCDQS5 FBCDQS6 FBCDQS7 15 13 14 12 11 9 10 8 FBCDQM1 FBCDQS1 FBCD13 FBCD14 FBCD12 FBCD11 FBCD9 FBCD10 FBCD8

B6 D2 B5 C2 B7 D3 E2 C6 B3 B2

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

FBCD31 31 29 30 28 27 25 26 24 FBCDQM3 FBCDQS3 FBCD29 FBCD30 FBCD28 FBCD27 FBCD25 FBCD26 FBCD24

G2 K2 J2 F2 G3 K3 J3 F3 H3 H2

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

C6 D2 B5 B7 E2 B6 C2 D3 B3 B2

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

FBCD62 62 63 60 61 59 58 56 57 FBCDQM7 FBCDQS7 FBCD63 FBCD60 FBCD61 FBCD59 FBCD58 FBCD56 FBCD57

E13 B10 C9 C13 B9 D13 B8 D12 B12 B13

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

GND C61 0.1U 10V C29 0.1U 10V C32 0.01U 25V C64 0.01U 25V

GND

ASSEMBLY

PAGE DETAIL ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED IS'. THE MATERIALS MAY OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS CONTAIN KNOWN 'AS AND UNKNOWN VIOLATIONS OR OTHERWISE, AND EXPRESSLY ALL IMPLIED WARRANTIES INCLUDING, DISCLAIMS WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS. A B D C E

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL <edit here to insert page detail>

2701 SAN TOMAS EXPRESSWAY SANTA CLARA, CA 95050, USA

NVIDIA CORPORATION

NV_PN

600-10264-xxxx-vvv

PAGE

ID NAME F G

<CON_PAGE_NUM> OF <CON_TOTAL_PAGES>

H

DATE 7-MAY-2004

MEMORY 128/256MB, 8Mx32DDR, PARTITION C, BANK 1 PLACE ALL DISCRETE COMPONENTS AS NEAR AS POSSIBLE TO MEMORY

1 1

U502B

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON 6<> 6<> 6<> 6< 6< 6< 3> 3> 3> 6> FBCRAS* IN IN IN IN FBCCAS* FBCWE* FBC_B1_CS1*

U501B FBVDD

FBCRAS* FBCCAS* FBCWE* FBC_B1_CS1* 7< 6< 3> 6<> FBC_CMD[26..0] IN 23 21 6 5 4 13 3 1 16 17 20 19 14 18 10 FBC_CMD23 FBC_CMD21 FBC_CMD6 FBC_CMD5 FBC_CMD4 FBC_CMD13 FBC_CMD3 FBC_CMD1 FBC_CMD16 FBC_CMD17 FBC_CMD20 FBC_CMD19 FBC_CMD14 FBC_CMD18 FBC_CMD10 BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON

FBVDD

M2 L2 L3 N2 M4 N5 N6 M6 N7 N8 M9 N9 N10 N11 M8 L6 M7 L9 N4 M5 M10

RAS 2/4/8MX32 CAS WE CS<0> CS<1>/TBD. A<0> A<1> A<2> A<3> A<4> A<5> A<6> A<7> A/AP<8> A<9> A<10> A<11> A<12>/TBD. BA<0> BA<1> BA<2>/TBD.

7<

6<>

6<

3>

FBC_CMD[26..0] IN 23 21 22 24 0 2 3 1 16 17 20 19 14 18 10

FBC_CMD23 FBC_CMD21 FBC_CMD22 FBC_CMD24 FBC_CMD0 FBC_CMD2 FBC_CMD3 FBC_CMD1 FBC_CMD16 FBC_CMD17 FBC_CMD20 FBC_CMD19 FBC_CMD14 FBC_CMD18 FBC_CMD10

VDD D7 VDD D8 VDD E4 VDD E11 VDD L4 VDD L7 VDD L8 VDD L11

C3 VDDQ C5 VDDQ C7 VDDQ C8 VDDQ C10 VDDQ C12 VDDQ E3 VDDQ E12 VDDQ F4 VDDQ F11 VDDQ G4 VDDQ G11 VDDQ J4 VDDQ J11 VDDQ K4 VDDQ K11 VDDQ B4 VSSQ B11 VSSQ D4 VSSQ D5 VSSQ D6 VSSQ D9 VSSQ D10 VSSQ D11 VSSQ E6 VSSQ E9 VSSQ F5 VSSQ F10 VSSQ G5 VSSQ G10 VSSQ H5 VSSQ H10 VSSQ J5 VSSQ J10 VSSQ K5 VSSQ K10 VSSQ

M2 L2 L3 N2 M4 N5 N6 M6 N7 N8 M9 N9 N10 N11 M8 L6 M7 L9 N4 M5 M10

RAS 2/4/8MX32 CAS WE CS<0> CS<1>/TBD. A<0> A<1> A<2> A<3> A<4> A<5> A<6> A<7> A/AP<8> A<9> A<10> A<11> A<12>/TBD. BA<0> BA<1> BA<2>/TBD.

FBVDD

VDD D7 VDD D8 VDD E4 VDD E11 VDD L4 VDD L7 VDD L8 VDD L11

C3 VDDQ C5 VDDQ C7 VDDQ C8 VDDQ C10 VDDQ C12 VDDQ E3 VDDQ E12 VDDQ F4 VDDQ F11 VDDQ G4 VDDQ G11 VDDQ J4 VDDQ J11 VDDQ K4 VDDQ K11 VDDQ B4 VSSQ B11 VSSQ D4 VSSQ D5 VSSQ D6 VSSQ D9 VSSQ D10 VSSQ D11 VSSQ E6 VSSQ E9 VSSQ F5 VSSQ F10 VSSQ G5 VSSQ G10 VSSQ H5 VSSQ H10 VSSQ J5 VSSQ J10 VSSQ K5 VSSQ K10 VSSQ

FBVDD

Decoupling for left MEMORY

FBVDD

Place around the MEM

2

2

FBCCKE IN IN IN FBCCLK0 FBCCLK0*

6<>

6< 6< 6<

3> 3> 3>

N12 M11 M12

CKE CLK CLK

FBCCKE 6< 6< 3> 3> FBCCLK1 IN IN FBCCLK1*

N12 M11 M12

CKE CLK CLK

C529 0.1U 10V

C512 0.1U 10V

C506 0.1U 10V

C523 0.01U 25V

C546 0.1U 10V

C516 0.1U 10V

C527 0.01U 25V

C547 0.01U 25V

C531 0.1U 10V

C525 0.01U 25V

GND

FBVDD

F6 F7 F8 F9 G6 G7 G8 G9 H6 H7 H8 H9 J6 J7 J8 J9 M13

THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM Must be GND

NC NC NC NC NC NC NC NC

FBVDD

VSS E5 VSS E7 VSS E8 VSS E10 VSS K6 VSS K7 VSS K8 VSS K9 VSS L5 VSS L10 Vref

N13

FBCVREF3 12_mil

R503 10K 1%

F6 F7 F8 F9 G6 G7 G8 G9 H6 H7 H8 H9 J6 J7 J8 J9 M13

THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM THERM Must be GND

NC NC NC NC NC NC NC NC

C502 4.7U 6.3V 0603

FBVDD

C505 0.1U 10V

C510 0.1U 10V

C548 0.01U 25V

C685 0.1U 10V

C538 0.01U 25V

C537 0.01U 25V

VSS E5 VSS E7 VSS E8 VSS E10 VSS K6 VSS K7 VSS K8 VSS K9 VSS L5 VSS L10 Vref

N13

FBCVREF4 12_mil

GND C509 0.1U 10V R504 10K 1% C519 0.1U 10V C549 0.1U 10V C540 0.1U 10V C515 0.1U 10V C521 0.1U 10V

GND R505 6.81K 1%

FBVDD

C4 C11 H4 H11 L12 L13 M3 N3

C4 C11 H4 H11 L12 L13 M3 N3

GND

C511 0.1U 10V

R502 6.81K 1%

GND

C517 0.1U 10V

Decoupling for left MEMORY

Place around the MEM

6< 6< 6< 6< 6< 6< 6< 6<

6<> 6<> 6<> 6<> 6<> 6<> 6<> 6<>

3> 3> 3> 3> 3> 3> 3> 3>

FBCDQM0 IN IN IN IN IN IN IN IN FBCDQM1 FBCDQM2 FBCDQM3 FBCDQM4 FBCDQM5 FBCDQM6 FBCDQM7 6<> 3<> FBCD[63..0] BI

GND

GND

GND

GND C518 0.1U 10V C508 0.1U 10V C535 0.01U 25V C536 0.01U 25V C507 0.1U 10V C543 0.01U 25V

U502A

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON FBCD22 DQ<0> 22 FBCD23 DQ<1> 23 FBCD20 DQ<2> 20 FBCD21 DQ<3> 21 FBCD19 DQ<4> 19 FBCD18 DQ<5> 18 FBCD16 DQ<6> 16 FBCD17 DQ<7> 17

U502D

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON

U501A

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON FBCD55 DQ<0> 55 FBCD53 DQ<1> 53 FBCD54 DQ<2> 54 FBCD52 DQ<3> 52 FBCD51 DQ<4> 51 FBCD49 DQ<5> 49 FBCD50 DQ<6> 50 FBCD48 DQ<7> 48

U501D

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON

FBCD6 6 7 5 4 2 3 1 0 FBCDQM0 FBCDQS0 FBCD7 FBCD5 FBCD4 FBCD2 FBCD3 FBCD1 FBCD0

F2 F3 J2 G2 K3 K2 G3 J3 H3 H2

D3 C2 D2 E2 C6 B5 B7 B6 B3 B2

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

FBCD39 39 37 38 36 35 33 34 32 FBCDQM4 FBCDQS4 FBCD37 FBCD38 FBCD36 FBCD35 FBCD33 FBCD34 FBCD32

G13 K13 F13 J13 J12 F12 K12 G12 H12 H13

J2 F2 K2 G2 K3 G3 J3 F3 H3 H2

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

GND

FBVDD 4

DQM DQS

FBCDQM2 FBCDQS2

DQM DQS

FBCDQM6 FBCDQS6

C513 4.7U 6.3V 0603

C504 0.1U 10V

C503 0.1U 10V

C526 0.01U 25V

C542 0.1U 10V

C514 0.1U 10V

C530 0.1U 10V

C528 0.1U 10V

C520 0.1U 10V

FBCD[63..0]

U502E

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON FBCD15 6<> 6<> 6<> 6<> 6<> 6<> 6<> 6<> 3<> 3<> 3<> 3<> 3<> 3<> 3<> 3<> FBCDQS0 BI BI BI BI BI BI BI BI FBCDQS1 FBCDQS2 FBCDQS3 FBCDQS4 FBCDQS5 FBCDQS6 FBCDQS7 15 13 14 12 11 9 10 8 FBCDQM1 FBCDQS1 FBCD13 FBCD14 FBCD12 FBCD11 FBCD9 FBCD10 FBCD8

U502C

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON

U501E

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON FBCD46 46 47 45 44 42 43 41 40 FBCDQM5 FBCDQS5 FBCD47 FBCD45 FBCD44 FBCD42 FBCD43 FBCD41 FBCD40

U501C

GND C544 0.01U 25V C522 0.01U 25V C524 0.01U 25V C545 0.1U 10V C539 0.1U 10V

BGA_DIAMOND144_P08_DDR_12MM_B2 COMMON

B9 D13 B10 C13 B8 D12 E13 C9 B12 B13

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

FBCD31 31 29 30 28 27 25 26 24 FBCDQM3 FBCDQS3 FBCD29 FBCD30 FBCD28 FBCD27 FBCD25 FBCD26 FBCD24

G13 K13 J13 F13 G12 K12 J12 F12 H12 H13

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

C9 D13 B10 B8 E13 B9 C13 D12 B12 B13

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

FBCD62 62 63 60 61 59 58 56 57 FBCDQM7 FBCDQS7 FBCD63 FBCD60 FBCD61 FBCD59 FBCD58 FBCD56 FBCD57

E2 B5 C6 C2 B6 D2 B7 D3 B3 B2

DQ<0> DQ<1> DQ<2> DQ<3> DQ<4> DQ<5> DQ<6> DQ<7> DQM DQS

GND

ASSEMBLY

PAGE DETAIL ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED IS'. THE MATERIALS MAY OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS CONTAIN KNOWN 'AS AND UNKNOWN VIOLATIONS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS. C E A B D

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL <edit here to insert page detail>

2701 SAN TOMAS EXPRESSWAY SANTA CLARA, CA 95050, USA

NVIDIA CORPORATION

NV_PN

600-10264-xxxx-vvv

PAGE

ID NAME F G

<XR_PAGE_TITLE>

H

DATE 7-MAY-2004

3V3RUN 3V3RUN

U9D 1 3V3RUN

BGA820_P10_33X33MM COMMON

R550 2.2K

I2CA_SCL I2CA_SDA

R549 2.2K

1

10< 10<>

4/14 DACA

LB512 BLM18PG181SN1D 0603

12_mil

10MIL_TRACE

DACA_VDD

AD10 AH10 AH9

DACA_VDD DACA_VREF DACA_RSET

DACA_VREF

I2CA_SCLK2 J3 I2CA_SDA

R548 R551 33

33

I2CA_SCL_R I2CA_SDA_R OUT BI

DACA_RSET

AF10 DACA_HSYNC AK10 DACA_VSYNC

DACA_HSYNC DACA_VSYNC

OUT OUT

10< 10<

C692 4.7U 6.3V 0603

C698 4700P 25V

C697 470P 50V

C723 0.01U 16V

R592 137 1%

R589 10K 1%

AH11 DACA_RED AJ12 DACA_GREEN AH12 DACA_BLUE

IMPEDANCE_RULE

DACA_RED DACA_GREEN DACA_BLUE ::37.5 ::37.5 ::37.5

NET_SPACING_TYPE

20MIL_G2G_30MIL

OUT

10<

20MIL_G2G_30MIL 20MIL_G2G_30MIL

OUT

10<

OUT

10<

AG9 DACA_IDUMP

GND

GND

R591 150 1%

R590 150 1%

R585 150 1%

3V3RUN 2

U9G

BGA820_P10_33X33MM COMMON

GND

GND

GND

LB506 BLM18PG181SN1D 0603

12_mil

10MIL_TRACE

DACB_VDD DACB_VREF

5/14 DACB(TV)

V8 R5 R7

DACB_VDD DACB_VREF DACB_RSET IMPEDANCE_RULE NET_SPACING_TYPE

20MIL_G2G_30MIL 20MIL_G2G_30MIL 20MIL_G2G_30MIL

OUT 10<

C644 4.7U 6.3V 0603

C648 4700P 25V

C647 470P 50V

C650 0.01U 16V

R86 365 1%

3

R571 90.9 1%

R570 1.78K 1%

R6 DACB_RED T5 DACB_GREEN T6 DACB_BLUE

DACB_RED DACB_GREEN DACB_BLUE

::37.5 ::37.5 ::37.5

OUT

10<

OUT

10<

Q3

GND

SEL_SDTV_HDTV IN

G 1 S

IRLML2502

2

20V 3A 0.080R 20A 0.5W@70C +/-8V

GND

V7 DACB_IDUMP

GND

R85 10K

SOT23

R578 150 1%

R579 150 1%

R577 150 1%

3V3RUN 3V3RUN

BAM25020Z08 GND

3

GND

U9F

BGA820_P10_33X33MM COMMON

GND

GND

GND R557 2.2K R540 2.2K

I2CB_SCL_R I2CB_SDA_R OUT BI 10< 10<>

6/14 DACC

R584

1K 1%

DACC_VDD

AD7 AH4 AF5

DACC_VDD DACC_VREF DACC_RSET

I2CB_SCLH4 J4 I2CB_SDA

I2CB_SCL I2CB_SDA

R539 R556 33

33

AG7 DACC_HSYNC AG5 DACC_VSYNC

AF6 DACC_RED

GND

AG6 DACC_GREEN AE5 DACC_BLUE

AG4 DACC_IDUMP

GND

U9E 3V3RUN 4

BGA820_P10_33X33MM COMMON

13/14 XTAL_PLL

LB505 BLM18PG181SN1D 0603 C673 4.7U 6.3V 0603 C617 1U 10V 0603 C621 4700P 25V

12_mil 10MIL_TRACE

PLLVDD

T9 T10 U10

PLLVDD VID_PLLVDD PLLGND

C631 470P 50V

13>

SSFOUT

IN

GND

T1

GND

XTALSSIN

T2 XTALOUTBUFF

BXTALOUT

R38

22

XTALOUTBUFF

OUT

13<

U1

XTALIN

U2 XTALOUT

XTALOUT

R39 *10K

SPACING

13MIL_G2G

SPACING

Y1 3

1 27 MHZ

13MIL_G2G

XTALIN

XTAL_4_SMT_LP_H10S 10 PPM 85C COMMON

GND

C103 22P

C109 22P

GND

GND

ASSEMBLY

PAGE DETAIL ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED IS'. THE MATERIALS MAY OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS CONTAIN KNOWN 'AS AND UNKNOWN VIOLATIONS OR OTHERWISE, AND EXPRESSLY ALL IMPLIED WARRANTIES INCLUDING, DISCLAIMS WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS. A B D C E

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL <edit here to insert page detail>

2701 SAN TOMAS EXPRESSWAY SANTA CLARA, CA 95050, USA

NVIDIA CORPORATION

NV_PN

600-10264-xxxx-vvv

PAGE

ID NAME F G

<CON_PAGE_NUM> OF <CON_TOTAL_PAGES>

H

DATE 7-MAY-2004

U9I

BGA820_P10_33X33MM COMMON

7/14 IFPAB

AM4

NET NAME

IFPA_TXC IFPA_TXC

AJ9 AK9

IFPATXC* IFPATXC

DIFFPAIR

IFPATXC IFPATXC

NET_SPACING_RULE

25MIL 25MIL

NET_PHYSICAL_TYPE

TMDS/PCIE/CLK TMDS/PCIE/CLK

OUT OUT 10< 10<

IFPAB_VPROBE

R596

1 3V3RUN

1K 1%

IFPABRSET

AL5

IFPAB_RSET IFPA_TXD0 AJ6 IFPA_TXD0 AH6

IFPATXD0* IFPATXD0

IFPATXD0 IFPATXD0

25MIL 25MIL

TMDS/PCIE/CLK TMDS/PCIE/CLK

OUT OUT

10< 10<

GND LB513 BLM18PG181SN1D 0603 C555 4.7U 6.3V 0603

12_mil IFPABPLLVDD

AC9

IFPAB_PLLVDD

IFPA_TXD1 AH7 IFPA_TXD1 AH8

IFPATXD1* IFPATXD1

IFPATXD1 IFPATXD1

25MIL 25MIL

TMDS/PCIE/CLK TMDS/PCIE/CLK

OUT OUT

10< 10<

C693 4.7U 6.3V 0603

C676 4700P 25V

C682 470P 50V

AD9

IFPA_TXD2 AK8 IFPA_TXD2 AJ8 IFPAB_PLLGND IFPA_TXD3 AH5 IFPA_TXD3 AJ5

IFPATXD2* IFPATXD2

IFPATXD2 IFPATXD2

25MIL 25MIL

TMDS/PCIE/CLK TMDS/PCIE/CLK

OUT OUT

10< 10<

IFPATXD3* IFPATXD3

IFPATXD3 IFPATXD3

25MIL 25MIL

TMDS/PCIE/CLK TMDS/PCIE/CLK

GND GND

OUT OUT

10< 10<

LVDSIOVDD

IFPB_TXC IFPB_TXC

AL4 AK4

IFPBTXC* IFPBTXC

IFPBTXC IFPBTXC

25MIL 25MIL

TMDS/PCIE/CLK TMDS/PCIE/CLK

OUT OUT

10< 10<

LB515 BLM18PG181SN1D 0603 C717 4.7U 6.3V 0603 C716 4.7U 6.3V 0603 C721 0.1U 10V

12_mil

IFPAIOVDD

AF9 AF8

IFPA_IOVDD IFPB_IOVDD

IFPB_TXD4 AM5 IFPB_TXD4 AM6

IFPBTXD4* IFPBTXD4

IFPBTXD4 IFPBTXD4

25MIL 25MIL

TMDS/PCIE/CLK TMDS/PCIE/CLK

OUT OUT

10< 10<

C720 0.022U 16V

C711 4700P 25V

C719 470P 50V

IFPB_TXD5 AL7 IFPB_TXD5 AM7

IFPBTXD5* IFPBTXD5

IFPBTXD5 IFPBTXD5

25MIL 25MIL

TMDS/PCIE/CLK TMDS/PCIE/CLK

OUT OUT

10< 10<

IFPB_TXD6 IFPB_TXD6 2

AK5 AK6

IFPBTXD6* IFPBTXD6

IFPBTXD6 IFPBTXD6

25MIL 25MIL

TMDS/PCIE/CLK TMDS/PCIE/CLK

OUT OUT

10< 10<

GND

GND

IFPB_TXD7 AL8 IFPB_TXD7 AK7

IFPBTXD7* IFPBTXD7

2

IFPBTXD7 IFPBTXD7 25MIL 25MIL TMDS/PCIE/CLK TMDS/PCIE/CLK

OUT OUT 10< 10<

IFPCTXC

IFPCTXD1

IFPDTXC

IFPDTXD4

R64 49.9 1%

IFPCDIOVDD

R50 49.9 1%

IFPCDIOVDD

R71 49.9 1%

IFPCDIOVDD

R61 49.9 1%

IFPCDIOVDD

R65 49.9 1%

IFPCTXC* IFPCTXD1*

R51 49.9 1%

IFPDTXC*

R70 49.9 1%

IFPDTXD4*

R59 49.9 1%

IFPCTXD0

IFPCTXD2

IFPDTXD3

IFPDTXD5

R48 49.9 1%

R52 49.9 1%

R56 49.9 1%

R68 49.9 1%

TMDSPLLVDD

R49 49.9 1% LB507 BLM18PG181SN1D 0603

IFPCTXD0*

C111 0.1U 10V

IFPCTXD2*

R54 49.9 1%

C129 0.1U 10V

IFPDTXD3*

R55 49.9 1%

C115 0.1U 10V

IFPDTXD5*

R69 49.9 1%

C119 0.1U 10V

C105 0.1U 10V

C128 0.1U 10V

GND

GND

GND

GND

GND

GND

C671 4.7U 6.3V 0603

U9H

BGA820_P10_33X33MM COMMON

8/14 IFPCD

AK3

NET NAME

IFPC_TXC IFPC_TXC

AM3 AM2

IFPCTXC* IFPCTXC

DIFFPAIR

IFPCTXC IFPCTXC

NET_SPACING_RULE

25MIL 25MIL

NET_PHYSICAL_TYPE

TMDS/PCIE/CLK TMDS/PCIE/CLK

OUT OUT 10< 10<

GND R587 1K 1%

IFPCBRSET

IFPCD_VPROBE

AH3

IFPCD_RSET IFPC_TXD0 AE1 IFPC_TXD0 AE2

IFPCTXD0* IFPCTXD0

IFPCTXD0 IFPCTXD0

25MIL 25MIL

TMDS/PCIE/CLK TMDS/PCIE/CLK

OUT OUT

10< 10<

3V3RUN 4

GND LB508 BLM18PG181SN1D 0603 C672 4.7U 6.3V 0603

3

12_mil IFPCPLLVDD

AA10

IFPCD_PLLVDD

IFPC_TXD1 AF2 IFPC_TXD1 AF1

IFPCTXD1* IFPCTXD1

IFPCTXD1 IFPCTXD1

25MIL 25MIL

TMDS/PCIE/CLK TMDS/PCIE/CLK

OUT OUT

10< 10<

C664 4700P 25V

C659 470P 50V

AB10

Q5 SI2305DS

3

IFPC_TXD2 AH1 IFPC_TXD2 AG1 IFPCD_PLLGND

IFPCTXD2* IFPCTXD2

IFPCTXD2 IFPCTXD2

25MIL 25MIL

TMDS/PCIE/CLK TMDS/PCIE/CLK

OUT OUT

10< 10<

TMDS_RUNPWORK* Q4 2N7002E

IN

RUNPWROK

R19 10K

GND

IFPCDIOVDD IFPD_TXC IFPD_TXC

AH2 AG3

IFPDTXC* IFPDTXC

IFPDTXC IFPDTXC

25MIL 25MIL

TMDS/PCIE/CLK TMDS/PCIE/CLK

OUT OUT

10< 10<

TMDSIOVDD

LB516 BLM18PG181SN1D 0603 C727 4.7U 6.3V 0603

12_mil

AD6 AE7

IFPC_IOVDD IFPD_IOVDD

IFPD_TXD4 AJ1 IFPD_TXD4 AK1

IFPDTXD3* IFPDTXD3

IFPDTXD3 IFPDTXD3

25MIL 25MIL

TMDS/PCIE/CLK TMDS/PCIE/CLK

OUT OUT

10< 10<

C696 0.1U 10V

C713 4700P 25V

C712 470P 50V

IFPD_TXD5 AL1 IFPD_TXD5 AL2

IFPDTXD4* IFPDTXD4

IFPDTXD4 IFPDTXD4

25MIL 25MIL

TMDS/PCIE/CLK TMDS/PCIE/CLK

OUT OUT

10< 10<

GND

C618 4.7U 6.3V 0603

IFPD_TXD6 AJ3 IFPD_TXD6 AJ2

IFPDTXD5* IFPDTXD5

IFPDTXD5 IFPDTXD5

25MIL 25MIL

TMDS/PCIE/CLK TMDS/PCIE/CLK

OUT OUT

10< 10<

GND

GND

5

GND

ASSEMBLY

PAGE DETAIL ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED IS'. THE MATERIALS MAY OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS CONTAIN KNOWN 'AS AND UNKNOWN VIOLATIONS OR OTHERWISE, AND EXPRESSLY ALL IMPLIED WARRANTIES INCLUDING, DISCLAIMS WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS. A B D C E

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL <edit here to insert page detail>

2701 SAN TOMAS EXPRESSWAY SANTA CLARA, CA 95050, USA

NVIDIA CORPORATION

NV_PN

600-10264-xxxx-vvv

PAGE

ID NAME F G

<CON_PAGE_NUM> OF <CON_TOTAL_PAGES>

H

DATE 7-MAY-2004

CN1B

(NON)PHY-X16 CON_MXM_230_FINGER_P0_5MM COMMON 2/2 11< 10< 8<> DVI_A_HPD OUT I2CB_SCL_R IN BI I2CB_SDA_R IO - LVDS,DVI,VGA,TV

217 232 230

DVI_A_HPD DDCB_SCLK DDCB_SDATA

DVI_A_CLK DVI_A_CLK DVI_A_TX0 DVI_A_TX0 DVI_A_TX1 DVI_A_TX1 DVI_A_TX2 DVI_A_TX2

219 221 237 239 231 233 225 227

IFPCTXC* IFPCTXC IFPCTXD0* IFPCTXD0 IFPCTXD1* IFPCTXD1 IFPCTXD2* IFPCTXD2 IN IN IN IN IN IN IN IN

9> 9> 9> 9> 9> 9> 9> 9>

IGP LVDS

11< DVI_B_HPD OUT

MXM DVI-B

DVI_B_CLK DVI_B_CLK

189 191 195 197

IFPDTXC* IFPDTXC IN IN 9> 9>

193

DVI_B_HPD

IGP_LCLK IGP_LCLK RSVD RSVD

SDTV

8> 8> 8> DACB_GREEN IN DACB_RED IN DACB_BLUE IN

HDTV

HDTV_Y HDTV_Pr HDTV_Pb

IGP_LTX2 IGP_LTX2 IGP_LTX1 IGP_LTX1 IGP_LTX0 IGP_LTX0

DVI_B_TX2 DVI_B_TX2 DVI_B_TX1 DVI_B_TX1 DVI_B_TX0 DVI_B_TX0

201 203 207 209 213 215

IFPDTXD5* IFPDTXD5 IFPDTXD4* IFPDTXD4 IFPDTXD3* IFPDTXD3 IN IN IN IN IN IN

9> 9> 9> 9> 9> 9>

140 136 144

TV_Y TV_C TV_CVBS

8> 8> 8> 8> 8>

DACA_VSYNC IN IN DACA_RED IN DACA_GREEN IN DACA_BLUE IN I2CA_SCL_R IN BI I2CA_SDA_R DACA_HSYNC

153 151 148 152 156 155 157

VSYNC HSYNC VGA_RED VGA_GRN VGA_BLU DDCA_SCLK DDCA_SDATA

IGP_UCLK IGP_UCLK RSVD RSVD IGP_UTX2 IGP_UTX2 IGP_UTX1 IGP_UTX1 IGP_UTX0 IGP_UTX0

159 161 165 167 171 173 177 179 183 185

NTP_JTAG_TRST_C OUT NTP_JTAG_TDO_C NTP_JTAG_TMS_C NTP_JTAG_TDI_C NTP_JTAG_TCLK_C OUT OUT IN OUT

11< 11> 11< 11< 11<

8> 8<>

11> 11> 11> 13< 11> 11<

GPIO3_PPEN IN IN IN I2CC_SCL_R IN BI I2CC_SDA_R GPIO4_BLEN GPIO2_BL_PWM

224 228 226 222 220

LVDS_PPEN LVDS_BLEN LVDS_BL_BRGHT DDCC_SCLK DDCC_SDATA

LVDS_UTX0 LVDS_UTX0 LVDS_UTX1 LVDS_UTX1 LVDS_UTX2 LVDS_UTX2 LVDS_UTX3 LVDS_UTX3

186 184 180 178 174 172 168 166

IFPBTXD4 IFPBTXD4* IFPBTXD5 IFPBTXD5* IFPBTXD6 IFPBTXD6* IFPBTXD7 IFPBTXD7* IFPBTXC IFPBTXC* IN IN IN IN IN IN IN IN IN IN

9> 9> 9> 9> 9> 9> 9> 9> 9> 9>

13<>

11<>

11<> 11<

SMB_DAT IN BI SMB_CLK

145 147

SMB_DAT SMB_CLK

LVDS_UCLK 162 LVDS_UCLK 160

11>

THERM_ALERT* IN RUNPWROK OUT

149 16

THERM RUNPWROK

LVDS_LTX0 LVDS_LTX0 LVDS_LTX1 LVDS_LTX1

216 214 210 208 204 202 198 196 192 190

IFPATXD0 IFPATXD0* IFPATXD1 IFPATXD1* IFPATXD2 IFPATXD2* IFPATXD3 IFPATXD3* IFPATXC IFPATXC* IN IN IN IN IN IN IN IN IN IN

9> 9> 9> 9> 9> 9> 9> 9> 9> 9>

15<

14<

13<

10< 10< 11>

MXM_RSVD1 IN IN IN MXM_RSVD2 MXM_RSVD3

141 169 143

RSVD RSVD RSVD

LVDS_LTX2 LVDS_LTX2 LVDS_LTX3 LVDS_LTX3 LVDS_LCLK LVDS_LCLK

ASSEMBLY

PAGE DETAIL ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED IS'. THE MATERIALS MAY OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS CONTAIN KNOWN 'AS AND UNKNOWN VIOLATIONS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS. C E A B D

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL <edit here to insert page detail>

2701 SAN TOMAS EXPRESSWAY SANTA CLARA, CA 95050, USA

NVIDIA CORPORATION

NV_PN

600-10264-xxxx-vvv

PAGE

ID NAME F G

<XR_PAGE_TITLE>

H

DATE 7-MAY-2004

3V3RUN

R33 200

THERM_VDD

I2C ADDRESS: 0x98H

U6

13<> 11<> 10<> I2CC_SDA_R BI I2CC_SCL_R IN

12_mil

C86 0.1U 16V

3V3RUN 3V3RUN

R31 R30

0 0

10MIL 10MIL

SO8_122MIL COMMON

GND

VDD

1

13<

11>

10<

2 3

D+ D-

R545 10K

THERM_ALERT*

OUT

R534 10K

2

THERM_SCL THERM_SDA

THERM 4 ALERT 6

8 7

SCL SDA

GND

3V3RUN

10<>

SMB_CLK IN SMB_DAT BI

R29 R32

*0 *0

10<

C83 2200P 50V

GND

U9J 3V3RUN 3V3RUN 3V3RUN

BGA820_P10_33X33MM COMMON

3V3RUN

R567 2.2K

CLAMPF6

R559 2.2K

9/14 MISC1

I2CC_SCL_R

R618 180

R601 10K

R603 10K

THERM*

J1 K1

THERMDN THERMDP

THERM

I2CC_SCLG2 G1 I2CC_SDA

I2CC_SCL I2CC_SDA

R26 R27 33

33

I2CC_SDA_R

I2CC_SCL_R I2CC_SDA_R OUT BI

10<

11<

13< 13<>

10<>

11<>

10> 10> 10> 10< 10>

NTP_JTAG_TCLK_C IN IN IN OUT IN NTP_JTAG_TMS_C NTP_JTAG_TDI_C NTP_JTAG_TDO_C NTP_JTAG_TRST_C

R617 R613 R615 *0 R616 *0 R614

*0 *0 *0

JTAG_TCLK JTAG_TMS JTAG_TDI JTAG_TDO JTAG_TRST

AJ11 AK11 AK12 AL12 AL13

JTAG_TCK JTAG_TMS JTAG_TDI JTAG_TDO JTAG_TRST

R595 270

R599 10K

GPIO0 K3 GPIO1 H1 GPIO2 K5 GPIO3 G5 GPIO4 E2 GPIO5 J5 GPIO6 G6 GPIO7 K6 GPIO8 E1 GPIO9 D2 GPIO10 H5 GPIO11 F4 GPIO12 E3

GPIO0_DVI_A_HPD GPIO1_DVI_B_HPD GPIO2_BL_PWM GPIO3_PPEN GPIO4_BLEN GPIO5_NVVDDCTL0 GPIO6_NVVDDCTL1 GPIO7_FBVDDCTL0 GPIO8_SLOWDOWN* GPIO9_MXM_RSVD2 GPIO10_MXM_RSVD1 SEL_SDTV_HDTV GPIO12_BATT_DISABLE* OUT OUT OUT OUT OUT OUT 10< 10< 10< 14< 14> 15>

R620

10K R619 10K

DVI_A_HPD DVI_B_HPD IN IN

10> 10>

D506

3V3RUN

2

D505

3V3RUN

2

R22 R552 0

MXM_RSVD2 OUT MXM_RSVD1 OUT OUT

GND

10< 10<

GND

BAV99

BAV99

GND

GND

R621 10K

R609 10K

R24 10K R612 100K R611 100K

R84

3V3RUN

*0

GND

5

GND

GND

GND

GND

U14 NC7S02P5X

4

Q2 2N7002E

AC_BATT_DRIVE

1

AC_BATT* IN

R82

AC_BATT_IN

R83 10K GND GND

GND

ASSEMBLY

PAGE DETAIL ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED IS'. THE MATERIALS MAY OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS CONTAIN KNOWN 'AS AND UNKNOWN VIOLATIONS OR OTHERWISE, AND EXPRESSLY ALL IMPLIED WARRANTIES INCLUDING, DISCLAIMS WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS. A B D C E

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL <edit here to insert page detail>

2701 SAN TOMAS EXPRESSWAY SANTA CLARA, CA 95050, USA

NVIDIA CORPORATION

NV_PN

600-10264-xxxx-vvv

PAGE

ID NAME F G

<CON_PAGE_NUM> OF <CON_TOTAL_PAGES>

H

DATE 7-MAY-2004

3V3RUN 1

U9L

BGA820_P10_33X33MM COMMON

MIOBD[11..0] IN

16>

12/14 MIOB

1 MIOBD0 MIOBD1 MIOBD2 MIOBD3 MIOBD4 MIOBD5 MIOBD6 MIOBD7 MIOBD8 MIOBD9 MIOBD10 MIOBD11 RFU RFU RFU RFU

AC3 AC1 AC2 AB2 AB1 AA1 AB3 AA3 AC5 AB5 AB4 AA5 W3 V1 Y5 W1

R583

10

12_mil

MIOBVDDQ

C684 0.1U 10V

AA8 AB7 AB8 AC6 AC7

U9M

BGA820_P10_33X33MM COMMON MIOBD3 MIOBD4 MIOBD5 3 4 5

MIOB_VDDQ MIOB_VDDQ MIOB_VDDQ MIOB_VDDQ MIOB_VDDQ

14/14 _GND_

AA12 AA2 AA21 AA31 AB27 AB6 AC10 AC23 AC29 AC4 AD16 AD17 AD2 AD31 AE17 AE27 AE6 AF11 AF26 AF29 AF4 AF7 AG10 AG11 AG14 AG15 AG19 AG2 AG22 AG31 AG8 AH24 AJ10 AJ13 AJ16 AJ17 AJ20 AJ23 AJ26 AJ29 AJ4 AJ7 AK2 AK28 AK31 AL11 AL14 AL19 AL22 AL25 AL3 AL6 AL9 AM13 AM16 AM17 AM20 AM23 AM26 AM29

GND

Y1 Y3

MIOBD10 MIOBD11 10 11

MIOBCAL_PD_VDDQ MIOBCAL_PU_GND

Y2

MIOB_VREF RFU RFU RFU RFU

W4 W5 V5 Y6

GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND

GND K10 GND K23 GND K29 GND K4 GND L27 GND L6 GND M12 GND M2 GND M31 GND N15 GND N18 GND N29 GND N4 GND P15 GND P18 GND P27 GND P6 GND R13 GND R14 GND R15 GND R18 GND R19 GND R2 GND R20 GND R31 GND T16 GND T17 GND T24 GND T29 GND T4 GND U16 GND U17 GND U24 GND U29 GND U8 GND V13 GND V14 GND V15 GND V18 GND V19 GND V2 GND V20 GND V31 GND W15 GND W18 GND W27 GND W6 GND Y15 GND Y18 GND Y29 GND Y4 GND AL10 GND AM10 GND AG13

MIOB_VSYNCAE3 AF3 MIOB_HSYNC MIOB_DE AD1 MIOB_CTL3 AD3

AD4 MIOB_CLKOUT AD5 MIOB_CLKOUT MIOB_CLKIN AE4

MIOB_CLKIN

R602 10K

GND

3V3RUN U11 U9K

BGA820_P10_33X33MM COMMON

3V3RUN

SO8_150MIL SO8 ROM_AT

3V3RUN

B12 B15 B18 B21 B24 B27 B3 B30 B6 B9 C2 C31 D10 D13 D16 D17 D20 D23 D26 D29 D4 D7 F11 F14 F19 F2 F22 F25 F31 F8 G26 G29 G4 G7 H27 H6 J16 J17 J2 J31

R53 10K

ROMCS AA4

ROMCS*

10/14 MISC2

F1 AE26 AD26 AH31 AH32

7 3 1 5 2 6

HOLD WP CS SI SO SCK

VCC

STRAP MEMSTRAPSEL0 MEMSTRAPSEL1 MEMSTRAPSEL2 MEMSTRAPSEL3 ROM_SI W2 ROM_SO AA6 ROM_SCLK AA7

ROM_SO ROM_SI ROM_SCLK

C110 0.1U 10V

GND 4

I2CH_SCL G3 I2CH_SDA H3

I2CH_SCL I2CH_SDA

GND

3V3RUN

U3 V3 U6 U5 U4 V4 V6

RFU RFU RFU RFU RFU RFU RFU

R535 *10K

BUFRST F3 STEREO T3

M6 SWAPRDY_A A26 TESTMEMCLK TESTMODEH2

TP_SWAPRDY_A

R569 10K

3V3RUN

GND R536 *2.2K

U5

SO8_150MIL COMMON

4 GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND

3V3RUN

TESTMCLK TESTMODE

6 5 3 2

SCL SDA SDA NC

VCC8 VCC7

R555 10K

R533 10K

4 GND 1 GND

C74 *0.1U 10V

*U_MEM_EE_CRYPT_8X128 GND GND GND GND

GND

5

GND

5

ASSEMBLY

PAGE DETAIL ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED IS'. THE MATERIALS MAY OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS CONTAIN KNOWN 'AS AND UNKNOWN VIOLATIONS OR OTHERWISE, AND EXPRESSLY ALL IMPLIED WARRANTIES INCLUDING, DISCLAIMS WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS. A B D C E

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL <edit here to insert page detail>

2701 SAN TOMAS EXPRESSWAY SANTA CLARA, CA 95050, USA

NVIDIA CORPORATION

NV_PN

600-10264-xxxx-vvv

PAGE

ID NAME F G

<CON_PAGE_NUM> OF <CON_TOTAL_PAGES>

H

DATE 7-MAY-2004

3V3RUN 1

R42 R40 10K

U8

SO8_150MIL COMMON 15< 14< 10> RUNPWROK IN XTALOUTBUFF IN

22

SSFOUT OUT

8<

Place close to ICS91720 3V3RUN

8 1

PD

VDD

2

SS_OUT

12_mil CLK_VDD

3.3V

R575

4.7

8>

CLKIN

CLKOUT/ 4 FS_IN0 REFOUT/ 5 FS_IN1

SS_REF

11>

11<

10<

I2CC_SCL_R IN BI I2CC_SDA_R

11<>

10<>

7 6

SCLK SDATA GND

R41 10K

C645 4.7U 6.3V 0603

C646 4.7U 6.3V 0603

C629 0.1U 10V

C619 470P 50V

I2C ADDRESS: 0xD4H

2

GND

3V3RUN U9N

BGA820_P10_33X33MM COMMON MIOAD[11..0] IN 16>

11/14 MIOA

R572

10

MIOAVDDQ

12_mil

C624 0.1U 10V

M7 M8 R8 T8 U9

MIOA_VDDQ MIOA_VDDQ MIOA_VDDQ MIOA_VDDQ MIOA_VDDQ

GND

L1 L3

MIOACAL_PD_VDDQ MIOACAL_PU_GND

MIOAD0 MIOAD1 MIOAD2 MIOAD3 MIOAD4 MIOAD5 MIOAD6 MIOAD7 MIOAD8 MIOAD9 MIOAD10 MIOAD11

P2 N2 N1 N3 M1 M3 P5 N6 N5 M4 L4 L5

MIOAD0 MIOAD1 MIOAD2 MIOAD3 MIOAD4 MIOAD5 MIOAD6 MIOAD8 MIOAD9

0 1 2 3 4 5 6

8 9

L2

MIOA_VREF

R3 MIOA_HSYNC MIOA_VSYNCR1 MIOA_DE P1 MIOA_CTL3 P3

MIOA_HSYNC

OUT

16>

R4 MIOA_CLKOUT P4 MIOA_CLKOUT MIOA_CLKIN M5

MIOACLKIN

R566 10K

GND

ASSEMBLY

PAGE DETAIL ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED IS'. THE MATERIALS MAY OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS CONTAIN KNOWN 'AS AND UNKNOWN VIOLATIONS OR OTHERWISE, AND EXPRESSLY ALL IMPLIED WARRANTIES INCLUDING, DISCLAIMS WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS. A B D C E

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL <edit here to insert page detail>

2701 SAN TOMAS EXPRESSWAY SANTA CLARA, CA 95050, USA

NVIDIA CORPORATION

NV_PN

600-10264-xxxx-vvv

PAGE

ID NAME F G

<CON_PAGE_NUM> OF <CON_TOTAL_PAGES>

H

DATE 7-MAY-2004

12<

OUT

MIOBD[11..0]

13<

OUT

MIOAD[11..0]

STRAP BIT

1

LOGIC 0

LOGIC 1

REG: NV_STRAP_0

3V3RUN

PCI_AD_SWAP

0: REVERSED 1: NORMAL DEFAULT

SUB_VENDOR NV4x

MIOAD1

0: SYSTEM BIOS 1: ADAPTER BIOS DEFAULT

R28

2.2K

RAM_CFG[3:0]

R546 *10K

MIOAD2

R547

2.2K

RAM_CFG_0 RAM_CFG_1 RAM_CFG_2 RAM_CFG_3

MS_0001: 8Mx32 DDR SDRAM, DQS PER 8 BITS, Monolithic MS_0011: 8Mx32 DDR SDRAM, DQS PER 8 BITS, Stacked MS_0110: 4Mx32 DDR SDRAM, DQS PER 8 BITS, Monolithic

R537

2.2K

MIOAD3

R532

*10K

3

R36 2.2K

MIOAD4

R37

*10K

4

R560 2.2K

MIOAD5

R561

*10K

5

2

6 22 7 8 9 10 11 12

3

CRYSTAL_0 CRYSTAL_1 TV_MODE_0 TV_MODE_1 AGP8x/4x AGP_SIDEBAND AGP_FASTWRITE

R581 2.2K

MIOBD4

MS_00: 13.5MHz MS_01: 14.318MHz MS_10: 27MHz MS_11: RESERVED MS_00: SECAM MS_01: NTSC MS_10: PAL MS_11: VGA 0: 8x 1: 4x 0: ENABLE 1: DISABLE 0: ENABLE 1: DISABLE MS_0100: NV34M MS_0110: NV18M MS_0111: NV18MPRO MS_1010: NV31M MS_1011: NV31MPRO MS_1100: NV31GLM MS_1101: NV33M MS_1110: NV31GLMPRO

3 1

DEFAULT

DEFAULT

DEFAULT

DEFAULT

DEFAULT

MEC2-1

MECH_MXM_BACKPLATE COMMON

R46

*10K

PCI_DEVID_0 PCI_DEVID_1 PCI_DEVID_2 PCI_DEVID_3 BUS_TYPE

MEC2-2

13 20

13> MIOA_HSYNC OUT

R43

2.2K

MIOBD5

R45

*10K

DEFAULT

2

MECH_MXM_BACKPLATE COMMON

R598

2.2K

MIOBD3

R597

*10K

MEC2-3

MECH_MXM_BACKPLATE COMMON

21 14 29 30

R580

*10K

MIOA_HSYNC

R582

2.2K

MEC2-4

0: PCI 1: AGP MS_00: MS_01: MS_10: MS_11:

DEFAULT PARALLEL SERIAL AT25F SERIAL SST45VF RESERVED

4

MECH_MXM_BACKPLATE COMMON

MIOBD10

R586

2.2K

ROM_TYPE_0 ROM_TYPE_1

MEC1-1

DEFAULT

1

MECH_MXM_II_HOLES COMMON

MEC1-2

MECH_MXM_II_HOLES COMMON

REG: NV_STRAP_1

4

GND

11 12 13 14

R35

*10K

MIOAD0

R34

*10K

PEX_PLL_EN_TERM100 3GIO_PADCFG_LUT_ADR[0] 3GIO_PADCFG_LUT_ADR[1] 3GIO_PADCFG_LUT_ADR[2]

R562

*10K

MIOAD6

R558

*10K

R538

*10K

MIOAD8

R531

*10K

R543

*10K

MIOAD9

R544

*10K

GND

ASSEMBLY

PAGE DETAIL ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED IS'. THE MATERIALS MAY OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS CONTAIN KNOWN 'AS AND UNKNOWN VIOLATIONS OR OTHERWISE, AND EXPRESSLY ALL IMPLIED WARRANTIES INCLUDING, DISCLAIMS WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS. A B D C E

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL <edit here to insert page detail>

2701 SAN TOMAS EXPRESSWAY SANTA CLARA, CA 95050, USA

NVIDIA CORPORATION

NV_PN

600-10264-xxxx-vvv

PAGE

ID NAME F G

<CON_PAGE_NUM> OF <CON_TOTAL_PAGES>

H

DATE 7-MAY-2004

*** Signal Cross-Reference for the entire design ***

FBA_B1_CS1* FBA_CMD<0>

4.1B> 4.2G<> 5.1D 5.2B< 3.3C 4.2B 5.2C 3.2E> 4.1G<> 4.2B< 4.2D< 5.2B<

FBCDQM<0> FBCDQM<7..0> FBCDQM<1> FBCDQM<2> FBCDQM<3> FBCDQM<4> FBCDQM<5> FBCDQM<6> FBCDQM<7> FBCDQS<0> FBCDQS<7..0> FBCDQS<1> FBCDQS<2> FBCDQS<3> FBCDQS<4> FBCDQS<5> FBCDQS<6> FBCDQS<7> FBCRAS*

3.3F 6.3A< 6.4B 7.4A< 7.4B 3.3E> 6.1G<> 3.3F 6.3A< 6.5B 7.4A< 7.5B 3.3F 6.3A< 6.4C 7.4A< 7.4C 3.3F 6.4A< 6.5C 7.4A< 7.5C 3.3F 6.4A< 6.4D 7.4A< 7.4D 3.3F 6.4A< 6.5D 7.4A< 7.5D 3.3F 6.4A< 6.4E 7.4A< 7.4E 3.3F 6.4A< 6.5E 7.4A< 7.5E 3.3F 6.4A<> 6.4B 7.4B 7.5A<> 3.3E<> 6.1G<> 3.3F 6.4A<> 6.5B 7.5A<> 7.5B 3.3F 6.4C 6.5A<> 7.4C 7.5A<> 3.4F 6.5A<> 6.5C 7.5A<> 7.5C 3.4F 6.4D 6.5A<> 7.4D 7.5A<> 3.4F 6.5A<> 6.5D 7.5A<> 7.5D 3.4F 6.4E 6.5A<> 7.4E 7.5A<> 3.4F 6.5A<> 6.5E 7.5A<> 7.5E 3.3H> 6.1B< 6.1D 6.1G<> 7.1B< 7.1D

MXM_RSVD1 MXM_RSVD2 MXM_RSVD3

10.4A< 11.3F> 10.4A< 11.3F> 10.4A< 11.3F> 10.3G> 11.3A<

DACA_BLUE DACA_GREEN DACA_HSYNC DACA_RED DACA_VSYNC

8.2F> 10.3A< 8.1F> 10.3A< 8.1F> 10.3A< 8.1F> 10.3A< 8.1F> 10.3A< 8.3E> 10.3A< 8.2E> 10.2A< 8.2E> 10.3A< 10.2A> 11.3H< 10.2A> 11.3H< 3.3D> 4.1B< 4.1D 4.1G<> 5.1B< 5.1D

FBA_CMD<26..0>

5.2D< FBA_CMD<1> FBA_CMD<2> FBA_CMD<3> FBA_CMD<4> FBA_CMD<5> FBA_CMD<6> FBA_CMD<10> FBA_CMD<13> FBA_CMD<14> FBA_CMD<16> 3.3C 4.2B 4.2D 5.2C 5.2D 3.3C 4.2B 5.2C 3.3C 4.2B 4.2D 5.2C 5.2D 3.3C 4.2D 5.2D 3.3C 4.2D 5.2D 3.3C 4.2D 5.2D 3.3C 4.2B 4.2D 5.2C 5.2D 3.3C 4.2D 5.2D 3.3C 4.2B 4.2D 5.2C 5.2D 3.3C 4.2B 4.2D 5.2C 5.2D 3.3C 4.2B 4.2D 5.2C 5.2D 3.3C 4.2B 4.2D 5.2C 5.2D 3.3C 4.2B 4.2D 5.2C 5.2D 3.3C 4.2B 4.2D 5.2C 5.2D 3.3C 4.2B 4.2D 5.2C 5.2D 3.3C 4.2B 5.2C 3.3C 4.2B 4.2D 5.2C 5.2D 3.3C 4.2B 5.2C 3.4F 3.4E> 3.4F 3.4F 3.4F 3.4F 3.4F 3.4F 3.4F 3.4F 3.4F 3.4F 3.4F 3.3H> 6.1B< 6.1D 6.1G<> 7.1B< 7.1D

NTP_JTAG_TCLK_C NTP_JTAG_TDI_C NTP_JTAG_TDO_C NTP_JTAG_TMS_C NTP_JTAG_TRST_C NVPWROK NVVDD_SENSE RUNPWROK

10.3G> 11.3A< 10.3G< 11.3A> 10.3G> 11.3A< 10.3G> 11.3A<

DACB_BLUE DACB_GREEN DACB_RED DVI_A_HPD DVI_B_HPD FBACAS*

14.2A> 15.2B< 2.3H> 14.4D< 10.4A> 13.1A< 14.2A< 15.1A< 15.1A<

SMB_CLK SMB_DAT SSFOUT

10.4A<> 11.2A< 10.4A< 11.2A<> 8.4B< 13.1D> 10.4A< 11.3F> 8.4E> 13.1A<

FBACKE

3.3D> 4.2B< 4.2D 4.2G<> 5.2B< 5.2D

FBA_CMD<17> FBA_CMD<18>

THERM_ALERT* XTALOUTBUFF

FBACLK0 FBACLK0* FBACLK1 FBACLK1* FBACS0* FBACS1* FBAD<0> FBAD<63..0>

3.4E> 4.2B< 4.3A 5.2B< 3.4E> 4.2B< 4.3A 5.2B< 3.4E> 4.2A 4.2D< 5.2D< 3.4E> 4.2A 4.2D< 5.2D< 3.3D> 4.1D 4.1G<> 4.2B< 3.3D> 4.1A< 4.1G<> 3.1B 4.4B 5.4C 3.1A<> 4.1G<> 4.4B 4.4B<> 5.4B<> 5.4C

FBA_CMD<19> FBA_CMD<20> FBA_CMD<21> FBA_CMD<22> FBA_CMD<23> FBA_CMD<24> FBCA<0> FBCA<11..0> FBCA<1> FBCA<2> FBCA<3> FBCA<4> FBCA<5> FBCA<6> FBCA<7> FBCA<8> FBCA<9> FBCA<10> FBCA<11> FBCCAS*

FBCWE*

3.3H> 6.1B< 6.1D 6.1G<> 7.1B< 7.1D

FBC_B0_CS0* FBC_B1_CS0* FBC_B1_CS1* FBC_CMD<0> FBC_CMD<26..0>

6.1B> 6.1B< 6.1D 6.2G<> 6.2G<> 6.1B> 7.1B< 7.1D 3.3G 6.1C 7.2C 3.3H> 6.1B< 6.1D< 6.1G<> 7.1B<

FBAD<1> FBAD<2> FBAD<3> FBAD<4> FBAD<5> FBAD<6>

3.1B 4.4B 5.4C 3.1B 4.4B 5.4C 3.1B 4.4B 5.4C 3.1B 4.4B 5.4C 3.1B 4.4B 5.4C 3.1B 4.4B 5.4C 3.1B 4.4B 5.4C 3.1B 4.5B 5.5C 3.1B 4.5B 5.5C 3.1B 4.5B 5.5C 3.1B 4.5B 5.5C 3.1B 4.5B 5.5C 3.1B 4.5B 5.5C 3.1B 4.5B 5.5C 3.1B 4.5B 5.5C 3.1B 4.4C 5.4C 3.1B 4.4C 5.4C 3.1B 4.4C 5.4C 3.1B 4.4C 5.4C 3.1B 4.4C 5.4C 3.2B 4.4C 5.4C 3.2B 4.4C 5.4C 3.2B 4.4C 5.4C 3.2B 4.5C 5.5C 3.2B 4.5C 5.5C 3.2B 4.5C 5.5C 3.2B 4.5C 5.5C 3.2B 4.5C 5.5C 3.2B 4.5C 5.5C 3.2B 4.5C 5.5C 3.2B 4.5C 5.5C 3.2B 4.4D 5.4D 3.2B 4.4D 5.4D 3.2B 4.4D 5.4D 3.2B 4.4D 5.4D 3.2B 4.4D 5.4D 3.2B 4.4D 5.4D 3.2B 4.4D 5.4D 3.2B 4.4D 5.4D 3.2B 4.5D 5.5D 3.2B 4.5D 5.5D 3.2B 4.5D 5.5D 3.2B 4.5D 5.5D 3.2B 4.5D 5.5D 3.2B 4.5D 5.5D 3.2B 4.5D 5.5D 3.2B 4.5D 5.5D 3.2B 4.4E 5.4E 3.2B 4.4E 5.4E 3.2B 4.4E 5.4E 3.3B 4.4E 5.4E 3.3B 4.4E 5.4E 3.3B 4.4E 5.4E 3.3B 4.4E 5.4E 3.3B 4.4E 5.4E 3.3B 4.5E 5.5E 3.3B 4.5E 5.5E 3.3B 4.5E 5.5E 3.3B 4.5E 5.5E 3.3B 4.5E 5.5E 3.3B 4.5E 5.5E 3.3B 4.5E 5.5E 3.3B 4.5E 5.5E 3.3B 4.4A< 4.4B 5.4A< 5.4C 3.3A> 4.1G<> 3.3B 4.4A< 4.5B 5.4A< 5.5C 3.3B 4.4A< 4.4C 5.4A< 5.4C 3.3B 4.4A< 4.5C 5.4A< 5.5C 3.3B 4.4A< 4.4D 5.4A< 5.4D 3.3B 4.4A< 4.5D 5.4A< 5.5D 3.3B 4.4A< 4.4E 5.4A< 5.4E 3.3B 4.4A< 4.5E 5.4A< 5.5E 3.3B 4.4B 4.5A<> 5.4C 5.5A<> 3.3A<> 4.1G<> 3.3B 4.5A<> 4.5B 5.5A<> 5.5C 3.3B 4.4C 4.5A<> 5.4C 5.5A<> 3.3B 4.5A<> 4.5C 5.5A<> 5.5C 3.3B 4.4D 4.5A<> 5.4D 5.5A<> 3.4B 4.5A<> 4.5D 5.5A<> 5.5D 3.4B 4.4E 4.5A<> 5.4E 5.5A<> 3.4B 4.5A<> 4.5E 5.5A<> 5.5E 3.3D> 4.1B< 4.1D 4.1G<> 5.1B< 5.1D