Documente Academic

Documente Profesional

Documente Cultură

9A04306 Digital Logic Design

Încărcat de

sivabharathamurthyDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

9A04306 Digital Logic Design

Încărcat de

sivabharathamurthyDrepturi de autor:

Formate disponibile

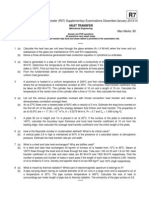

Code: 9A04306

1

DIGITAL LOGIC DESIGN

(Computer Science and Engineering)

B.Tech II Year I Semester (R09) Regular & Supplementary Examinations December/January 2013/14

Time: 3 hours Answer any FIVE questions All questions carry equal marks *****

1 (a) Convert the following numbers: (i) (41. 6875)10 to hexadecimal number. (ii) (11001101. 0101)2 to base -8 and base 4. (iii) (4567)8 to base 10. Add and multiply the following numbers without converting them to decimal: (i) Binary numbers 1011 and 101. (ii) Hexadecimal numbers 2E and 34. Simply the following Boolean expressions to minimum number of literals: + + . ( + )( + )( + + ). + + . ) ( + )( + ) ( + ) ( +

Max Marks: 70

(b)

2 (a) (b) (c) (d) (e) 3 (a) (b) 4 (a) (b)

Simplify and implement the following SOP using NOR gates f(A, B, C, D) = (0, 1, 4, 5, 10, 11, 14, 15). Reduce the following function using K-map technique f (A, B, C, D) = (0, 2, 3, 8, 9, 12, 13, 15).

5 (a) (b) 6 (a) (b) 7 (a) (b)

Implement BCD to 7-segment decoder for common anode using 4:16 decoder. + + + Implement the following Boolean function using 8:1 multiplexers F(A, B, C, D) = .

Draw the circuit diagram of clocked D-flip flop with NAND gates and explain its operation using truth table. Give its timing diagram. Draw the logic diagram of a JK flip flop and explain. Explain synchronous and ripple counters. Compare their merits and demerits. Design Mod-10 counter using T-Flip flop. Give the comparison between PROM, PLA and PAL. A combinational circuit is defined by the functions 1 (, , ) = (3, 5, 6,7) 2 (, , ) = (0, 2, 4, 7) Implement the circuit with a PLA having three inputs, four product terms and two outputs. Explain the salient features of ASM chart. Draw the ASM chart for weighing machine and explain.

8 (a) (b)

*****

Code: 9A04306 B.Tech II Year I Semester (R09) Regular & Supplementary Examinations December/January 2013/14

DIGITAL LOGIC DESIGN

(Computer Science and Engineering)

Time: 3 hours Answer any FIVE questions All questions carry equal marks *****

1 (a) (b) Subtract (111001)2 from (101011) using is complement. Convert the following numbers: (i) (2 C6B. F2)16 to octal. (ii) (26153. 7406)8 to binary (iii) (1001001. 011)2 to decimal. Simplify the following Boolean expressions to minimum number of literals: + + . (ii) ( + ) ( + ) (A+B+ ). (iii) ( (i) + ) ( + ). (iv) + ( ). Simplify the following Boolean function in SOP form ( , , , ) = + + + + .

Max Marks: 70

(a) (b)

(a) (b)

(a) (b)

Reduce the following function using K-map in SOP form ( , , , ) =(0, 1, 2, 4, 5, 8, 9, 12, 13, 14). Simplify the Boolean function using K-map. + + + Implement with NAND gates. (, , , ) = Design and implement a 4-bit combinational circuit of binary to gray code.

Implement the full adder with a decoder and two OR-gates.

(a)

(b)

Determine a minimal state table equivalent to the state table given below. PS NS Z J1 J2 1 2, 0 4, 1 2 7, 0 1, 0 3 4, 0 2, 1 4 7, 0 1, 0 5 4, 0 1, 1 6 5, 1 6, 1 7 4, 1 4, 1 Design a sequential circuit specified by the state diagram in figure using JK-flip flop.

oo

o o

6 (a) (b) 7 (a) (b) 8 (a) (b)

o

1

Design a 4-bit binary synchronous counter with D-flip flop. Design a converter with the following repeated binary sequence: 0, 1, 2, 4, 6. Use D-flip flops. Implement the following using PLA: ( , , ) = (1, 2, 4, 6), ( , , ) = (0, 1, 6,7), ( , , ) = (2, 6). Obtain the 15-bit hamming code word for the 11-bit data word 11001001010. Obtain the ASM chart for the following state transactions if = 0, control goes from state 1 to state 2 . If = 1 generate a conditional operation and go from 1 2 . How do you indicate moore outputs and Melay outputs in an ASM?

*****

Code: 9A04306

3

DIGITAL LOGIC DESIGN

(Computer Science and Engineering)

B.Tech II Year I Semester (R09) Regular & Supplementary Examinations December/January 2013/14

Time: 3 hours Answer any FIVE questions All questions carry equal marks *****

1 (a) (b) (c) 2 (a) (b) Convert the following numbers in decimal: (i) (10110. 0101)2 (ii) (16. 5)16 (iii) (26. 24)8. Perform (15)10- (28)10 in complement representation. Find the 16s complements of AF3B and convert AF3B to binary.

Max Marks: 70

Convert the following to the other canonical form: (i) F(x, y, z) = (1, 3, 7) (ii) F (A, B, C, D) = (0, 1, 2, 3, 4, 6,12). State and prove the following theorems: (i) Demorgans theorem. (ii) Conserver theorem. (iii) Shanons expansion and reduction theorem. Simplify the following Boolean function for minimal POS form using K-map: (, , , ) = (4, 5, 6, 7, 8, 12) + (1, 2, 3, 9, 11, 14) implement with NOR gates. Reduce the following function using K-map in SOP form. F(w, x, y, z) = (0, 1, 2, 4, 5, 6, 8, 9, 12, 13, 14). Realize the following Boolean expression using a 8 1 multiplexer: + + + . = Construct a 5 to 32 line decoder with four 3-to-8 line decoders with enable and a 2 to -4 line decoder. Use block diagrams for the components. A sequential circuit with two D-flip flops, A and B, two inputs , and one output z, is specified by the following next state and output equations: ( + 1) = 1 + ( + 1) = 1 + = . Draw the logic diagram of the circuit. List the state table for the sequential circuit. Draw the corresponding state diagram. Design a serial 2s complementor with a shift register and a flip flop. The binary number is shifted out from one side and its 2s complement shifted in to the other side of the shift register. Show that a BCD ripple counter can be constructed using a 4-bit binary ripple converter with asynchronous clear and a NAND gate that detects the occurrence of count 1010. Tabulate the truth table for an 8 4 ROM that implements the Boolean functions: (, , ) = (1, 2, 4, 6), ( , , ) = (0, 1, 6, 7), (, , ) = (2,6), (, , ) = (1, 2, 3, 5, 7). Considering now the ROM as a memory, specify the memory contents at addresses 1 and 4. Tabulate the PLA programming table for the four Boolean functions listed in above problem. Draw an ASM chart and stage table for a 2-bit up-down can be having mode control input, M= 1: up counting , M = 0 down counting: The circuit should generate an output 1 whenever count becomes minimum or maximum. Draw the ASM chart for weighing machine and explain.

3 (a) (b)

4 (a) (b)

(a) (b) (c) 6 (a) (b)

7 (a)

(b) 8 (a) (b)

*****

Code: 9A04306

4

DIGITAL LOGIC DESIGN

(Computer Science and Engineering)

B.Tech II Year I Semester (R09) Regular & Supplementary Examinations December/January 2013/14

Time: 3 hours Answer any FIVE questions All questions carry equal marks *****

1 (a)

Max Marks: 70

(b)

The state of a 12-bit register is 100010010111. What is its content if it represents: (i) Three decimal digits in BCD. (ii) Three decimal digits in the excess -3 code. (iii) Three decimal digits in the 8421 code. (iv) A binary number. Convert decimal 9126 to both BCD and ASCII codes. For ASCII, an add parity bit is to be appended at the left. Given the Boolean function = + 1 1 + 1 : (i) Implement it with AND. OR and inverter gates. (ii) Implement it with OR and inverter gates. (iii) Implement it with AND and inverter gates. Obtain the dual of the following Boolean expressions: . + + (ii) + + (i) A

2 (a)

(b)

3 (a) (b) 4 (a) (b) 5

Simplify the following Boolean function by using a Quline-McCluskey method: (, , , ) = (0, 2, 3, 6, 7, 8, 10, 12, 13). Find the reduced SOP form of the following function F (A, B, C, D) = m (1, 3, 7, 11, 15) + d (0, 2, 4). Design and implement a 4-bit combinational circuit of binary to gray code. Implement the full adder with a decoder and two OR-gates. A sequential circuit has two JK flip-flops A and B two inputs , and one output 2. The flip flops input equations and circuit output equation are = +1 1 = 1 1 1 = = + 1 . Draw the logic diagram of the circuit. Tabulate the state table. Derive the state equations for A and B. Design a counter with the following repeated binary sequence: 0, 1, 2, 3, 4, 5, 6. Use JK-flip flops. What is the difference between serial and parallel transfer? Explain how to converter serial data to parallel and parallel data to serial. What type of register is needed? Design a combinational circuit using a ROM. The circuit accepts a 3- bit number and generates an output binary number equal to the square of the input number. Implement the following two Boolean functions with a PLA: 1 (, , ) = (0, 1, 2, 4), 2 (, , ) = (0, 5, 6, 7).

(a) (b) (c) 6 (a) (b)

7 (a) (b)

8 (a) (b)

Explain how the ASM chart differs from a conventional flow chart. Show the difference in interpretation using one example. Obtain ASM chart for the following state transitions if = 0. Control goes from state 1 to state 2 , if = 1 generate a conditional operation and go from 1 2 . *****

S-ar putea să vă placă și

- Summary of The Types of FlipDocument1 paginăSummary of The Types of FlipPola RismaÎncă nu există evaluări

- Digital Design Mid-Sem Question PaperDocument2 paginiDigital Design Mid-Sem Question PaperAbhinav MishraÎncă nu există evaluări

- Digital Electronics Ec 1201Document34 paginiDigital Electronics Ec 1201ainugiri100% (1)

- Module 4 - Number Systems and Boolean AlgebraDocument8 paginiModule 4 - Number Systems and Boolean AlgebraSuyog ChavanÎncă nu există evaluări

- Question Bank Digital ElectronicsDocument12 paginiQuestion Bank Digital ElectronicsUrvin MistryÎncă nu există evaluări

- Exercises Logic Gates 2Document2 paginiExercises Logic Gates 2Jamewel BaneÎncă nu există evaluări

- CS302 2005 2010 Midterm - Solved - MEGA FILEDocument91 paginiCS302 2005 2010 Midterm - Solved - MEGA FILEattiqueÎncă nu există evaluări

- Unit 4: Vestigial Side Band ModulationDocument9 paginiUnit 4: Vestigial Side Band ModulationSeela Balaji KumarÎncă nu există evaluări

- NPTEL Online Course: Control Engineering: Assignment 1Document4 paginiNPTEL Online Course: Control Engineering: Assignment 1udayÎncă nu există evaluări

- Digital Electronics Assignment 1Document2 paginiDigital Electronics Assignment 1Liyanshu patelÎncă nu există evaluări

- CS302 - Lab Manual - Week No PDFDocument5 paginiCS302 - Lab Manual - Week No PDFattiqueÎncă nu există evaluări

- Digital ElectronicsDocument102 paginiDigital Electronicsdurga0% (1)

- Assgn1 PDFDocument2 paginiAssgn1 PDFfuckitÎncă nu există evaluări

- Karnaugh Maps - Rules of Simplification: Grouping OnesDocument14 paginiKarnaugh Maps - Rules of Simplification: Grouping OnesProfessor RajputÎncă nu există evaluări

- Assignment 2021-22Document2 paginiAssignment 2021-22Dan Ojwang100% (2)

- Examples of Boolean algebra simplificationDocument7 paginiExamples of Boolean algebra simplificationShabir AliÎncă nu există evaluări

- Combinational Logic Circuits and AnalysisDocument35 paginiCombinational Logic Circuits and Analysisjnax101Încă nu există evaluări

- Full Adder Using MultiplexerDocument4 paginiFull Adder Using Multiplexermohiuddin_vu67% (3)

- 3 Digits Digital AmmeterDocument3 pagini3 Digits Digital AmmeterSingam SridharÎncă nu există evaluări

- ECE-223, Solutions For Assignment #1: Chapter 1, Digital Design, M. Mano, 3 EditionDocument3 paginiECE-223, Solutions For Assignment #1: Chapter 1, Digital Design, M. Mano, 3 EditionGajula SureshÎncă nu există evaluări

- Exercise 1Document3 paginiExercise 1Kaka Hiếu100% (1)

- BOOL AL ProblemsDocument9 paginiBOOL AL ProblemsSayan GayenÎncă nu există evaluări

- RP Jain Adc DacDocument27 paginiRP Jain Adc DacAnand SinghÎncă nu există evaluări

- VHDL DOCUMENTATIONDocument41 paginiVHDL DOCUMENTATIONB. MeenakshiÎncă nu există evaluări

- Cse III Logic Design 10cs33 Notes PDFDocument80 paginiCse III Logic Design 10cs33 Notes PDFtrupti.kodinariya98100% (1)

- Trapezoidal Rule for Numerical IntegrationDocument8 paginiTrapezoidal Rule for Numerical IntegrationGian SanchezÎncă nu există evaluări

- GOVT. ENGG. COLLEGE, BHUJ BRANCH: MECH (6th Sem) DIV: A SUBJECT: Computer Aided Design TOPIC: Beizer Curves & SplinesDocument22 paginiGOVT. ENGG. COLLEGE, BHUJ BRANCH: MECH (6th Sem) DIV: A SUBJECT: Computer Aided Design TOPIC: Beizer Curves & SplinesSAGAR GOSWAMIÎncă nu există evaluări

- Python University Question PaperDocument3 paginiPython University Question Papersanika GandhiÎncă nu există evaluări

- Digital Logic Circuits and Sequential ModulesDocument10 paginiDigital Logic Circuits and Sequential Modulessara35Încă nu există evaluări

- Computer Servicing 4: Introduction To Logic Gates Boolean AlgebraDocument13 paginiComputer Servicing 4: Introduction To Logic Gates Boolean AlgebraJhon Keneth NamiasÎncă nu există evaluări

- Sequential Logic Circuits ExplainedDocument56 paginiSequential Logic Circuits ExplainedBonsa100% (1)

- Digital Electronics Multiple Choice QuestionsDocument22 paginiDigital Electronics Multiple Choice QuestionsSenthilkumar KrishnamoorthyÎncă nu există evaluări

- Digital Design-Digital Electronics Question BankDocument1 paginăDigital Design-Digital Electronics Question BankPaweceÎncă nu există evaluări

- Cs302 Mid Term Solved by AliDocument10 paginiCs302 Mid Term Solved by AliMuheet Ali0% (1)

- Question Bank for Digital Logic DesignDocument11 paginiQuestion Bank for Digital Logic DesignSatish BojjawarÎncă nu există evaluări

- Deld Mcqs 1Document25 paginiDeld Mcqs 1hertzberg 1Încă nu există evaluări

- Digital System Design QuestionsDocument5 paginiDigital System Design Questionsvijay4u4allÎncă nu există evaluări

- Exercise 7 - Register Transfer Level (RTL) LogicDocument4 paginiExercise 7 - Register Transfer Level (RTL) LogicdureÎncă nu există evaluări

- Assignment 1 DSDDocument2 paginiAssignment 1 DSDsarala tÎncă nu există evaluări

- Single Source Shortest Path Unit-3Document43 paginiSingle Source Shortest Path Unit-3Phani Kumar100% (1)

- H..Cnje.... : S-/ - "F-'-..R.TDocument2 paginiH..Cnje.... : S-/ - "F-'-..R.TYashasvi VermaÎncă nu există evaluări

- Chapter 4: Combinational Logic Solutions To Problems: (1, 5, 9, 12, 19, 23, 30, 33)Document14 paginiChapter 4: Combinational Logic Solutions To Problems: (1, 5, 9, 12, 19, 23, 30, 33)Gabriel FernandoÎncă nu există evaluări

- Notes On Counters (Digital Electronics)Document44 paginiNotes On Counters (Digital Electronics)wooDefyÎncă nu există evaluări

- MCQ FunctionDocument13 paginiMCQ FunctionMahesh Chandra UpadhyayÎncă nu există evaluări

- CA Assignment IIDocument9 paginiCA Assignment IISomesh ThakurÎncă nu există evaluări

- K-Map Method for Logic MinimizationDocument57 paginiK-Map Method for Logic MinimizationHugh100% (1)

- MICROPROCESSORS AND 8085 INSTRUCTIONSDocument7 paginiMICROPROCESSORS AND 8085 INSTRUCTIONSyoloÎncă nu există evaluări

- Logic Gate and CircuitDocument16 paginiLogic Gate and CircuitMd Naimur Rahaman SakibÎncă nu există evaluări

- STLD BitsDocument18 paginiSTLD BitsKornepati SureshÎncă nu există evaluări

- 9A04401 Switching Theory & Logic DesignDocument4 pagini9A04401 Switching Theory & Logic DesignsivabharathamurthyÎncă nu există evaluări

- 9A04401 Switching Theory and Logic DesignDocument4 pagini9A04401 Switching Theory and Logic DesignsivabharathamurthyÎncă nu există evaluări

- 9A04306 Digital Logic DesignDocument4 pagini9A04306 Digital Logic DesignsivabharathamurthyÎncă nu există evaluări

- Switching Theory and Logic Design Exam QuestionsDocument4 paginiSwitching Theory and Logic Design Exam QuestionsrangerÎncă nu există evaluări

- 9A04401 Switching Theory & Logic DesignDocument4 pagini9A04401 Switching Theory & Logic DesignsivabharathamurthyÎncă nu există evaluări

- 9A04306 Digital Logic Design4Document4 pagini9A04306 Digital Logic Design4Mahaboob SubahanÎncă nu există evaluări

- 9a04306-Digital Logic DesignDocument1 pagină9a04306-Digital Logic DesignSheikh Noor MohammadÎncă nu există evaluări

- 9A04306 Digital Logic DesignDocument4 pagini9A04306 Digital Logic DesignsivabharathamurthyÎncă nu există evaluări

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsDe la EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsEvaluare: 5 din 5 stele5/5 (1)

- Digital Communications 1: Source and Channel CodingDe la EverandDigital Communications 1: Source and Channel CodingÎncă nu există evaluări

- Linear Programming and Resource Allocation ModelingDe la EverandLinear Programming and Resource Allocation ModelingÎncă nu există evaluări

- Control Systems (CS) Notes As Per JntuaDocument203 paginiControl Systems (CS) Notes As Per Jntuasivabharathamurthy100% (3)

- SSC Telugu (FL) (AP)Document232 paginiSSC Telugu (FL) (AP)sivabharathamurthyÎncă nu există evaluări

- SSC Social Textbook (AP)Document100 paginiSSC Social Textbook (AP)sivabharathamurthyÎncă nu există evaluări

- R7312301 Transport Phenomena in BioprocessesDocument1 paginăR7312301 Transport Phenomena in BioprocessessivabharathamurthyÎncă nu există evaluări

- R7311205 Distributed DatabasesDocument1 paginăR7311205 Distributed DatabasessivabharathamurthyÎncă nu există evaluări

- 07A4EC01 Environmental StudiesDocument1 pagină07A4EC01 Environmental StudiessivabharathamurthyÎncă nu există evaluări

- R7410506 Mobile ComputingDocument1 paginăR7410506 Mobile ComputingsivabharathamurthyÎncă nu există evaluări

- 9A05707 Software Project ManagementDocument4 pagini9A05707 Software Project ManagementsivabharathamurthyÎncă nu există evaluări

- R7410407 Operating SystemsDocument1 paginăR7410407 Operating SystemssivabharathamurthyÎncă nu există evaluări

- R5410201 Neural Networks & Fuzzy LogicDocument1 paginăR5410201 Neural Networks & Fuzzy LogicsivabharathamurthyÎncă nu există evaluări

- 9A13701 Robotics and AutomationDocument4 pagini9A13701 Robotics and AutomationsivabharathamurthyÎncă nu există evaluări

- R7311506 Operating SystemsDocument1 paginăR7311506 Operating SystemssivabharathamurthyÎncă nu există evaluări

- R7310106 Engineering GeologyDocument1 paginăR7310106 Engineering GeologysivabharathamurthyÎncă nu există evaluări

- R7310506 Design & Analysis of AlgorithmsDocument1 paginăR7310506 Design & Analysis of AlgorithmssivabharathamurthyÎncă nu există evaluări

- Code: R7311306: (Electronics & Control Engineering)Document1 paginăCode: R7311306: (Electronics & Control Engineering)sivabharathamurthyÎncă nu există evaluări

- 9A10505 Principles of CommunicationsDocument4 pagini9A10505 Principles of CommunicationssivabharathamurthyÎncă nu există evaluări

- R7311006 Process Control InstrumentationDocument1 paginăR7311006 Process Control InstrumentationsivabharathamurthyÎncă nu există evaluări

- R7310406 Digital CommunicationsDocument1 paginăR7310406 Digital CommunicationssivabharathamurthyÎncă nu există evaluări

- 9A15502 Digital System DesignDocument4 pagini9A15502 Digital System Designsivabharathamurthy100% (1)

- R7310206 Linear Systems AnalysisDocument1 paginăR7310206 Linear Systems AnalysissivabharathamurthyÎncă nu există evaluări

- R5310406 Digital CommunicationsDocument1 paginăR5310406 Digital CommunicationssivabharathamurthyÎncă nu există evaluări

- R7310306 Heat TransferDocument1 paginăR7310306 Heat Transfersivabharathamurthy100% (1)

- R5310204 Power ElectronicsDocument1 paginăR5310204 Power ElectronicssivabharathamurthyÎncă nu există evaluări

- 9A14503 Principles of Machine DesignDocument8 pagini9A14503 Principles of Machine DesignsivabharathamurthyÎncă nu există evaluări

- 9A23501 Heat Transfer in BioprocessesDocument4 pagini9A23501 Heat Transfer in BioprocessessivabharathamurthyÎncă nu există evaluări

- 9A04504 Digital IC ApplicationsDocument4 pagini9A04504 Digital IC ApplicationssivabharathamurthyÎncă nu există evaluări

- 9A21506 Mechanisms & Mechanical DesignDocument8 pagini9A21506 Mechanisms & Mechanical DesignsivabharathamurthyÎncă nu există evaluări

- 9A03505 Heat TransferDocument4 pagini9A03505 Heat TransfersivabharathamurthyÎncă nu există evaluări

- 9A05505 Operating SystemsDocument4 pagini9A05505 Operating SystemssivabharathamurthyÎncă nu există evaluări

- 9A02505 Electrical Machines-IIIDocument4 pagini9A02505 Electrical Machines-IIIsivabharathamurthyÎncă nu există evaluări

- PAPTAC-FW Quality ExcursionsDocument5 paginiPAPTAC-FW Quality ExcursionsGarth110Încă nu există evaluări

- Four Ball EPDocument5 paginiFour Ball EPu4sachinÎncă nu există evaluări

- Regulation of AlternatorDocument6 paginiRegulation of Alternatorkudupudinagesh100% (1)

- Audit ComplianceDocument1 paginăAudit ComplianceAbhijit JanaÎncă nu există evaluări

- WINTER 2021 SYLLABUS All Lab Classes - Docx-2Document7 paginiWINTER 2021 SYLLABUS All Lab Classes - Docx-2Sushi M.SÎncă nu există evaluări

- Educ 61 Module 5 ActivityDocument4 paginiEduc 61 Module 5 ActivityMitchille GetizoÎncă nu există evaluări

- Unit 1 Question AnswerDocument5 paginiUnit 1 Question AnswerSubhankar BiswalÎncă nu există evaluări

- Noam Text ליגר טסקט םעֹנDocument20 paginiNoam Text ליגר טסקט םעֹנGemma gladeÎncă nu există evaluări

- Industrial Wire Cutting Machine: A Senior Capstone Design ProjectDocument17 paginiIndustrial Wire Cutting Machine: A Senior Capstone Design ProjectTruta IonutÎncă nu există evaluări

- Muhammad Ajmal: Electrical EngineerDocument1 paginăMuhammad Ajmal: Electrical EngineerMuhammad AbrarÎncă nu există evaluări

- Generate power from solar roof tilesDocument4 paginiGenerate power from solar roof tilesshalinthÎncă nu există evaluări

- Mahusay Module 4 Acc3110Document2 paginiMahusay Module 4 Acc3110Jeth MahusayÎncă nu există evaluări

- Rom, Eprom, & Eeprom Technology: Figure 9-1. Read Only Memory SchematicDocument14 paginiRom, Eprom, & Eeprom Technology: Figure 9-1. Read Only Memory SchematicVu LeÎncă nu există evaluări

- Animated Film Techniques for Phrasing Action and DialogueDocument10 paginiAnimated Film Techniques for Phrasing Action and Dialoguevall-eÎncă nu există evaluări

- Probability Sampling Guide for Health ResearchDocument5 paginiProbability Sampling Guide for Health ResearchNicole AleriaÎncă nu există evaluări

- Viavi: Variable Optical Attenuators (mVOA-C1)Document6 paginiViavi: Variable Optical Attenuators (mVOA-C1)gwÎncă nu există evaluări

- 2219 Aluminium Alloy - WikipediaDocument2 pagini2219 Aluminium Alloy - WikipediaVysakh VasudevanÎncă nu există evaluări

- EPC Contractor Rep. Authority/Authority's EngineerDocument6 paginiEPC Contractor Rep. Authority/Authority's Engineersunil kuldeepÎncă nu există evaluări

- ATT III - 13. Prevent, Control and Fight Fires On BoardDocument9 paginiATT III - 13. Prevent, Control and Fight Fires On BoardPak WeÎncă nu există evaluări

- SurveillanceDocument17 paginiSurveillanceGaurav Khanna100% (1)

- ISO/TC 46/SC 9/working Group 1Document4 paginiISO/TC 46/SC 9/working Group 1João Paulo CésarÎncă nu există evaluări

- Real Time Braille To Speech Using PythonDocument10 paginiReal Time Braille To Speech Using PythonKali LinuxÎncă nu există evaluări

- Gabriel Feltran. "The Revolution We Are Living"Document9 paginiGabriel Feltran. "The Revolution We Are Living"Marcos Magalhães Rosa100% (1)

- 08 - Chapter 1 - Waveguide-Transmission Line - Microstrip LinesDocument76 pagini08 - Chapter 1 - Waveguide-Transmission Line - Microstrip Linesgilberto araujoÎncă nu există evaluări

- Automatic Helmet DetectDocument4 paginiAutomatic Helmet Detectvasanth100% (1)

- VnDoc - Tải tài liệu, văn bản pháp luật, biểu mẫu miễn phíDocument7 paginiVnDoc - Tải tài liệu, văn bản pháp luật, biểu mẫu miễn phíStranger NonameÎncă nu există evaluări

- Slippery? Contradictory? Sociologically Untenable? The Copenhagen School RepliesDocument10 paginiSlippery? Contradictory? Sociologically Untenable? The Copenhagen School RepliesDaniel CorrenteÎncă nu există evaluări

- 3.dummy VariablesDocument25 pagini3.dummy VariablesUnushka ShresthaÎncă nu există evaluări

- Accomplishment Report - English (Sy 2020-2021)Document7 paginiAccomplishment Report - English (Sy 2020-2021)Erika Ikang WayawayÎncă nu există evaluări

- Multiple Choice Bubble Sheet Template Customize This WordDocument3 paginiMultiple Choice Bubble Sheet Template Customize This WordAl Bin0% (1)