Documente Academic

Documente Profesional

Documente Cultură

Delec Lab Manual

Încărcat de

Reddyvari VenugopalDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Delec Lab Manual

Încărcat de

Reddyvari VenugopalDrepturi de autor:

Formate disponibile

DIGITAL ELECTRONICS LAB MANUAL

FOR

I I I SEMESTER B.E (E & C)

(For private circulation only)

VISHVESHWARAIAH TECHNOLOGICAL UNIVERSITY

NAME

REG NO

BATCH..

DEPARTMENT OF ELECTRONI CS & COMMUNI CATI ON

SRI SI DDHARTHA I NSTI TUTE OF TECHNOLOGY

MARLUR, TUMKUR-572105

DIGITAL ELECTRONICSLAB

DOS

DON TS

1. Be regular to the lab.

2. Follow proper Dress Code.

3. Maintain Silence.

4. Know the theory behind the

experiment before coming to the lab.

5. Identify the different leads or terminals

or pins of the IC before making

connection.

6. Know the Biasing Voltage required for

different families of ICs and connect

the power supply voltage and ground

terminals to the respective pins of the

ICs.

7. Know the Current and Voltage rating

of the ICs before using them in the

experiment.

8. Avoid unnecessary talking while doing

the experiment.

9. Handle the IC Trainer Kit properly.

10. Mount the IC Properly on the IC Zif

Socket.

11. Handle the microprocessor kit

properly.

12. While doing the Interfacing, connect

proper voltages to the interfacing kit.

13. Keep the Table clean.

14. Take a signature of the In charge

before taking the kit/components.

15. After the completion of the

experiments switch off the power

supply and return the apparatus.

16. Arrange the chairs/stools and

equipment properly before leaving the

lab.

1. Do not exceed the voltage Rating.

2. Do not inter change the ICs while

doing the experiment.

3. Avoid loose connections and short

circuits.

4. Do not throw the connecting wires to

floor.

5. Do not come late to the lab.

6. Do not operate p/IC trainer kits

unnecessarily.

7. Do not panic if you dont get the

output.

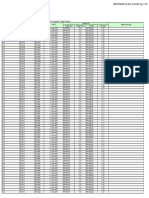

CONTENTS

Experiment No Page. No

1. Verification of Gates 2

2. Half/Full Adder/Subtractor 6

3. Parallel Adder/Subtractor 10

4. Excess-3 to BCD & Vice Versa 12

5. Binary-Grey & Grey-Binary Converter 16

6. MUX/DEMUX 20

7. MUX/DEMUX using only NAND Gates 26

8. Comparators 28

9. Encoder/Decoder 32

10. Flip-Flops 36

11. Counters 38

12. Shift Registers 44

13. J ohnson/Ring Counters 48

14. Sequence Generator 50

15. Multivibrators 52

16. Static RAM 56

17. Question Bank 57

Digital Electronics Lab SSIT

1

I nverter Gate (NOT Gate) 7404LS

A O/P

Y1

(V)

Y2

(V)

Y3

(V)

Y4

(V)

Y5

(V)

Y6

(v)

0 1

1 0

2-I nput AND Gate 7408LS

A B O/P Y1

(V)

Y2

(V)

Y3

(V)

Y4

(V)

0 0 0

0 1 0

1 0 0

1 1 1

2-I nput OR Gate 7432LS

A B O/P

Y1

(V)

Y2

(V)

Y3

(V)

Y4

(V)

0 0 0

0 1 0

1 0 0

1 1 1

2-I nput NAND Gate 7400LS

A B O/P Y1

(V)

Y2

(V)

Y3

(V)

Y4

(V)

0 0 1

0 1 0

1 0 0

1 1 0

Digital Electronics Lab SSIT

2

Experiment No: Date: __/__/____

VERI FI CATI ON OF GATES

Aim: - To study and verify the truth table of logic gates

Apparatus Required: -

All the basic gates mention in the fig.

Procedure: -

1. Place the I C on I C Trainer Kit.

2. Connect V

CC

and ground to respective pins of I C Trainer Kit.

3. Connect the inputs to the input switches provided in the I C Trainer

Kit.

4. Connect the outputs to the switches of O/P LEDs,

5. Apply various combinations of inputs according to the truth table and

observe condition of LEDs.

6. Disconnect output from the LEDs and note down the corresponding

multimeter voltage readings for various combinations of inputs.

2-I nput NOR Gate 7402LS

Digital Electronics Lab SSIT

3

A B O/P

Y1

(V)

Y2

(V)

Y3

(V)

Y4

(V)

0 0 1

0 1 0

1 0 0

1 1 0

2-I nput EX-OR Gate 7486LS

A B O/P

Y1

(V)

Y2

(V)

Y3

(V)

Y4

(V)

0 0 0

0 1 1

1 0 1

1 1 0

3-I nput NAND Gate 7410LS

A B C O/P

Y1

(V)

Y2

(V)

Y3

(V)

0 0 0 1

0 0 1 1

0 1 0 1

0 1 1 1

1 0 0 1

1 0 1 1

1 1 0 1

1 1 1 0

2-I nput NAND Gate CD4011

A B O/P

Y1

(V)

Y2

(V)

Y3

(V)

Y4

(V)

0 0 1

0 1 1

1 0 1

1 1 0

Digital Electronics Lab SSIT

4

2-I nput NOR Gate CD4001

A B O/P

Y1

(V)

Y2

(V)

Y3

(V)

Y4

(V)

0 0 1

0 1 0

1 0 0

1 1 0

4-I nput NAND Gate 7420LS

A B C D O/P

Y1

(V)

Y2

(V)

Y3

(V)

0 0 0 0 1

0 0 0 1 1

0 0 1 0 1

0 0 1 1 1

0 1 0 0 1

0 1 0 1 1

0 1 1 0 1

0 1 1 1 1

1 0 0 0 1

1 0 0 1 1

1 0 1 0 1

1 0 1 1 1

1 1 0 0 1

1 1 0 1 1

1 1 1 0 1

1 1 1 1 0

Conclusion:-

.

Signature of the staff

Digital Electronics Lab SSIT

5

Half Adder using basic gates:-

AB C

B A S

B A B A S

=

=

+ =

Full Adder using basic gates:-

Half Adder using NAND gates only:-

Full Adder using NAND gates only:-

Digital Electronics Lab SSIT

6

Experiment No: Date: __/__/____

HALF/FULL ADDER & HALF/FULL SUBTRACTOR

Aim: - To realize half/full adder and half/full subtractor.

i. Using X-OR and basic gates

ii. Using only nand gates.

Apparatus Required: -

I C 7486, I C 7432, I C 7408, I C 7400, etc.

Procedure: -

1. Verify the gates.

2. Make the connections as per the circuit diagram.

3. Switch on V

CC

and apply various combinations of input according to the

truth table.

4. Note down the output readings for half/full adder and half/full

subtractor sum/difference and the carry/borrow bit for different

combinations of inputs.

Digital Electronics Lab SSIT

7

Using X OR and Basic Gates (a)Half Subtractor

Full Subtractor

(ii) Using only NAND gates (a) Half subtractor

(b) Full Subtractor

Digital Electronics Lab SSIT

8

Half Adder

A B S C S(V) C(V)

0 0 0

0 1 1 0

1 0 1 0

1 1 0 1

Half Subtractor

A B D B D(V) B(V)

0 0 0 0

0 1 1 1

1 0 1 0

1 1 0 0

Full Adder

A B Cn-1 S C S(V) C(V)

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

Full Subtractor

A B Cn-1 D B D(v) B(v)

0 0 0 0 0

0 0 1 1 1

0 1 0 1 1

0 1 1 0 1

1 0 0 1 0

1 0 1 0 0

1 1 0 0 0

1 1 1 1 1

Digital Electronics Lab SSIT

9

Conclusion: -

..

Signature of the staff in charge

Digital Electronics Lab SSIT

9

Pin Detail: -

Adder: -

Truth Table: -

A3 A2 A1 A0 B3 B2 B1 B0 C4 (V) S3(V) S2(V) S1(V) S0(V)

0 0 0 1 0 0 1 0 0 0 0 1 1

0 1 0 1 1 0 1 1 1 1 0 0 0

1 0 1 0 1 0 1 0 1 0 1 0 0

1 1 1 1 1 1 1 1 1 1 1 1 0

0 1 1 1 0 0 1 1 0 1 0 1 0

Subtractor:-

7483

Digital Electronics Lab SSIT

10

Experiment No: Date: __/__/____

PARALLEL ADDER AND SUBTRACTOR USI NG 7483

Aim: - To realize I C7483 as parallel adder / Subtractor.

Apparatus Required: -

I C 7483, I C 7404, etc.

Procedure: -

1. Apply the inputs to A0 to A3 and B0 to B3.

2. Connect C0 to the Ground.

3. Check the output sum on the S0 to S3 and also C4.

4. For subtraction connect C0 to Vcc, Apply the B input through NOT

gate, which gives the complement of B.

5. The truth table of adder and Subtractor are noted down.

Truth Table for Subtractor

A3 A2 A1 A0 B3 B2 B1 B0 C4(V) S3(V) S2(V) S1(V) S0(V)

0 0 1 0 0 0 0 1 1 0 0 0 1

0 1 0 1 0 0 1 1 1 0 0 1 0

0 0 1 1 0 1 0 1 0 1 1 1 0

Digital Electronics Lab SSIT

11

1 0 1 0 0 1 1 0 1 0 1 0 0

1 0 0 0 1 1 1 1 0 1 0 0 1

Conclusion: -

.

Signature of the staff

Digital Electronics Lab SSIT

9

BCD To Excess-3

Truth Table For Code Conversion: -

I nputs Outputs

B3 B2 B1 B0 E3 (v) E2 (v) E1 (v) E0 (v)

0 0 0 0 0 0 1 1

0 0 0 1 0 1 0 0

0 0 1 0 0 1 0 1

0 0 1 1 0 1 1 0

0 1 0 0 0 1 1 1

0 1 0 1 1 0 0 0

0 1 1 0 1 0 0 1

0 1 1 1 1 0 1 0

1 0 0 0 1 0 1 1

1 0 0 1 1 1 0 0

Digital Electronics Lab SSIT

10

Experiment No: Date: __/__/____

BCD to Excess 3 AND Excess 3 to BCD

Aim: - To verify BCD to excess 3 code conversion using NAND gates. To study

and verify the truth table of excess-3 to BCD code converter

Apparatus Required: -

I C 7400, I C 7404, etc.

Procedure: - (BCD Excess 3 and Vice Versa)

1. Make the connections as shown in the fig.

2. Pin [14] of all I CS are connected to +5V and pin [7] to the ground.

3. The inputs are applied at E3, E2, E1, and E0 and the corresponding

outputs at B3, B2, B1, and B0 are taken for excess 3 to BCD.

4. B3, B2, B1, and B0 are the inputs and the corresponding outputs are E3,

E2, E1 and E0 for BCD to excess 3.

5. Repeat the same procedure for other combinations of inputs.

6. Truth table is written.

Digital Electronics Lab SSIT

11

Excess-3 To BCD :-

Truth Table For Code Conversion: -

I nputs Outputs

E3 E2 E1 E0 B3 (v) B2 (v) B1 (v) B0(v)

0 0 1 1 0 0 0 0

0 1 0 0 0 0 0 1

0 1 0 1 0 0 1 0

0 1 1 0 0 0 1 1

0 1 1 1 0 1 0 0

1 0 0 0 0 1 0 1

1 0 0 1 0 1 1 0

1 0 1 0 0 1 1 1

1 0 1 1 1 0 0 0

1 1 0 0 1 0 0 1

Digital Electronics Lab SSIT

12

Exercise: -

1. Obtain the expression for E3, E2, E1 and E0

2. Obtain the expression for B3, B2, B1 and B0

Conclusion: -

..

Signature of the staff-in charge

Digital Electronics Lab SSIT

13

Circuit Diagram: -

Binary To Gray Gray To Binary

Truth Table For Both: -

I nputs Outputs

B3 B2 B1 B0 G3 (V) G2 (V) G1 (V) G0 (V)

0 0 0 0 0 0 0 0

0 0 0 1 0 0 0 1

0 0 1 0 0 0 1 1

0 0 1 1 0 0 1 0

0 1 0 0 0 1 1 0

0 1 0 1 0 1 1 1

0 1 1 0 0 1 0 1

0 1 1 1 0 1 0 0

1 0 0 0 1 1 0 0

1 0 0 1 1 1 0 1

1 0 1 0 1 1 1 1

1 0 1 1 1 1 1 0

1 1 0 0 1 0 1 0

1 1 0 1 1 0 1 1

1 1 1 0 1 0 0 1

1 1 1 1 1 0 0 0

Digital Electronics Lab SSIT

14

Experiment No: Date: __/__/____

BI NARY TO GRAY AND GRAY TO BI NARY

CONVERSI ON

Aim: - To convert given binary numbers to gray codes.

Apparatus Required: -

I C 7486, etc

Procedure: -

1. The circuit connections are made as shown in fig.

2. Pin (14) is connected to +Vcc and Pin (7) to ground.

3. I n the case of binary to gray conversion, the inputs B0, B1, B2 and B3 are

given at respective pins and outputs G0, G1, G2, G3 are taken for all the

16 combinations of the input.

4. I n the case of gray to binary conversion, the inputs G0, G1, G2 and G3 are

given at respective pins and outputs B0, B1, B2, and B3 are taken for all

the 16 combinations of inputs.

5. The values of the outputs are tabulated.

Digital Electronics Lab SSIT

15

Using Nand Gates Only: -

Binary To Gray

Gray To Binary

Digital Electronics Lab SSIT

16

Truth Table For Both: -

I nputs Outputs

B3 B2 B1 B0 G3 (V) G2 (V) G1 (V) G0 (V)

0 0 0 0 0 0 0 0

0 0 0 1 0 0 0 1

0 0 1 0 0 0 1 1

0 0 1 1 0 0 1 0

0 1 0 0 0 1 1 0

0 1 0 1 0 1 1 1

0 1 1 0 0 1 0 1

0 1 1 1 0 1 0 0

1 0 0 0 1 1 0 0

1 0 0 1 1 1 0 1

1 0 1 0 1 1 1 1

1 0 1 1 1 1 1 0

1 1 0 0 1 0 1 0

1 1 0 1 1 0 1 1

1 1 1 0 1 0 0 1

1 1 1 1 1 0 0 0

Conclusion: -

..

Signature of the staff in charge

Digital Electronics Lab SSIT

17

Digital Electronics Lab SSIT

17

Pin Details: -

Truth Table: -

CHANNEL A

INPUTS SELECT

LINES

O/P

a Ioa I1a I2a I3a S1 S2 Za(v)

1 X X X X X X 0

0 0 X X X 0 0 0

0 1 X X X 0 0 1

0 X 0 X X 0 1 0

0 X 1 X X 0 1 1

0 X X 0 X 1 0 0

0 X X 1 X 1 0 1

0 X X X 0 1 1 0

0 X X X 1 1 1 1

CHANNEL B

INPUTS SELECT

LINES

O/P

a Iob I1b I2b I3b S1 S2 Za(v)

1 X X X X X X 0

0 0 X X X 0 0 0

0 1 X X X 0 0 1

0 X 0 X X 0 1 0

0 X 1 X X 0 1 1

0 X X 0 X 1 0 0

0 X X 1 X 1 0 1

0 X X X 0 1 1 0

0 X X X 1 1 1 1

Digital Electronics Lab SSIT

18

Experiment No: Date: __/__/____

MUX/DEMUX USING 74153 & 74139

Aim: - To verify the truth table of multiplexer using 74153 & to verify a

demultiplexer using 74139. To study the arithmetic circuits half-adder half

Subtractor, full adder and full Subtractor using multiplexer.

Apparatus Required: -

IC 74153, IC 74139, IC 7404, etc.

Procedure: - (IC 74153)

1. The Pin [16] is connected to + Vcc.

2. Pin [8] is connected to ground.

3. The inputs are applied either to A input or B input.

4. If MUX A has to be initialized, Ea

is made low and if MUX B has to be

initialized, E

b

is made low.

5. Based on the selection lines one of the inputs will be selected at the output

and thus the truth table is verified.

6. In case of half adder using MUX, sum and carry is obtained by applying a

constant inputs at I

0a

, I

1a,

I

2a,

I

3a

and

I

0b,

I

1b,

I

2b

and I

3b

and the

corresponding values of select lines are changed as per table and the

output is taken at Z0a as sum and Z0b as carry.

7. In this case, the channels A and B are kept at constant inputs according to

the table and the inputs A and B are varied. Making Ea and Eb zero and

the output is taken at Za, and Zb.

8. In full adder using MUX, the input is applied at Cn-1, An and Bn.

According to the table corresponding outputs are taken at Cn and Dn.

Digital Electronics Lab SSIT

19

Half Adder Using 74153 Half Subtractor: -

Full Adder Using 74153: - Full Subtractor Using 74153: -

Truth Tables: - Same for both Subtractor and adder

Half adder/subtractor

A B Sn/Dn (V) Cn/Bn (V)

0 0

0 1

1 0

1 1

Full Adder/subtractro

An Bn Cn-1 Sn/Dn (V) Cn/Bn (V)

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Digital Electronics Lab SSIT

20

Pin Details: -

Truth Table For Demux: -

CHANNEL A CHANNEL B

Inputs Outputs Inputs Outputs

a S1a S0a Y0a Y1a Y2a Y3a b S1b S0b Y0b Y1b Y2b Y3b

1 X X 1 1 1 1 1 X X 1 1 1 1

0 0 0 0 1 1 1 0 0 0 0 1 1 1

0 0 1 1 0 1 1 0 0 1 1 0 1 1

0 1 0 1 1 0 1 0 1 0 1 1 0 1

0 1 1 1 1 1 0 0 1 1 1 1 1 0

Procedure: - (IC 74139)

1. The inputs are applied to either a input or b input

2. The demux is activated by making Ea low and Eb low.

3. The truth table is verified.

Digital Electronics Lab SSIT

21

Half adder

Half Adder

A B Sn (V) Cn (V)

0 0 0 0

0 1 1 0

1 0 1 0

1 1 0 1

Half subtractor:-

Half Subtractor

A B Dn (V) Bn (V)

0 0 0 0

0 1 1 1

1 0 1 0

1 1 0 0

Exercise:-

Repeat the experiment to verify Channel B.

Full Adder using IC 74139:-

Digital Electronics Lab SSIT

22

Full subtractor using IC 74139:-

Truth Tables:-

Full Adder

An Bn Cn-1 Sn (V) Cn (V)

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Full Subtractor

An Bn Cn-1 Dn (V) Bn (V)

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Conclusion:-

..

Signature of the staff in charge

Department of E & C SSIT

31

MUX USING NAND GATES ONLY: -

DEMUX USING NAND GATES ONLY: -

Department of E & C SSIT

32

Experiment No: DATE: __/__/____

MUX AND DEMUX USING NAND GATES

AIM: - To verify the truth table of MUX and DEMUX using NAND.

APPARATUS REQUIRED: -

IC 7400, IC 7410, IC 7420, etc.

PROCEDURE: -

1. Connections are made as shown in the Circuit diagram.

2. Change the values of the inputs as per the truth table and note down

the outputs readings using multimeter.

TRUTH TABLES: -

INPUT OUPUT INPUT OUPUT

A B I0 I1 I2 I3 Y (V) A B Y0 (V) Y1 (V) Y2 () Y3 (V)

0 0 0 X X X 0 1 X X 1 1 1 1

0 0 1 X X X 1 0 0 0 0 1 1 1

0 1 X 0 X X 0 0 0 1 1 0 1 1

0 1 X 1 X X 1 0 1 0 1 1 0 1

1 0 X X 0 X 0 0 1 1 1 1 1 0

1 0 X X 1 X 1

1 1 X X X 0 0

1 1 X X X 1 1

Conclusion:-

..

Department of E & C SSIT

33

Signature of the staff in charge

Digital Electronics Lab SSIT

21

One Bit Comparator: -

A B

Y1

(A>B)

Y2

(A = B)

Y3

(A < B)

0 0 0 1 0

0 1 0 0 1

1 0 1 0 0

1 1 0 1 0

Two Bit Comparator: -

Two-Bit Comparator: -

A1 A0 B1 B0 Y1 (A > B) Y2 (A = B) Y3 (A < B)

0 0 0 0 0 1 0

0 0 0 1 0 0 1

0 0 1 0 0 0 1

0 0 1 1 0 0 1

0 1 0 0 1 0 0

0 1 0 1 0 1 0

0 1 1 0 0 0 1

0 1 1 1 0 0 1

1 0 0 0 1 0 0

1 0 0 1 1 0 0

1 0 1 0 0 1 0

1 0 1 1 0 0 1

1 1 0 0 1 0 0

1 1 0 1 1 0 0

1 1 1 0 1 0 0

1 1 1 1 0 1 0

Digital Electronics Lab SSIT

22

Experiment No: Date: __/__/____

COMPARATORS

Aim: - To verify the truth table of one bit and two bit comparators using logic

gates.

Apparatus Required: -

I C 7486, I C 7404, I C 7408, etc.

Procedure: -

1. Verify the gates.

2. Make the connections as per the circuit diagram.

3. Switch on Vcc.

4. Applying i/p and Check for the outputs.

5. The voltameter readings of outputs are taken and tabulated in tabular

column.

6. The o/p are verified.

Digital Electronics Lab SSIT

23

4-bit Comparator

Tabular Coloumn For 8-Bit Comparator: -

A

3

B

3

A

2

B

2

A

1

B

1

A

0

B

0

A>B A=B A<B A>B A=B A<B

A

3

>B

3

X X X X X X

A

3

<B

3

X X X X X X

A

3

=B

3

A

2

>B

2

X X X X X

A

3

=B

3

A

2

<B

2

X X X X X

A

3

=B

3

A

2

=B

2

A

1

>B

1

X X X X

A

3

=B

3

A

2

=B

2

A

1

<B

1

X X X X

A

3

=B

3

A

2

=B

2

A

1

=B

1

A

0

>B

0

X X X

A

3

=B

3

A

2

=B

2

A

1

=B

1

A

0

<B

0

X X X

A

3

=B

3

A

2

=B

2

A

1

=B

1

A

0

=B

0

1 0 0

A

3

=B

3

A

2

=B

2

A

1

=B

1

A

0

=B

0

0 1 0

A

3

=B

3

A

2

=B

2

A

1

=B

1

A

0

=B

0

0 0 1

Digital Electronics Lab SSIT

24

8-Bit Comparator: -

LSB MSB

Exercise:-

Write the truth table for 8-bit comparator and verify the same for the

above circuit.

Conclusion:-

..

Digital Electronics Lab SSIT

25

Signature of the staff in charge

Department of E & C SSIT

5

PI N DETAI LS:-

TRUTH TABLE:-

En A B C D E F G H Q2(V) Q1(V) Q0(V) ES(V) EO(V)

1 X X X X X X X X 1 1 1 1 1

0 0 1 1 1 1 1 1 1 1 1 1 0 1

0 X 0 1 1 1 1 1 1 1 1 0 0 1

0 0 X 0 1 1 1 1 1 1 0 1 0 1

0 0 0 X 0 1 1 1 1 1 0 0 0 1

0 0 0 0 X 0 1 1 1 0 1 1 0 1

0 0 0 0 0 X 0 1 1 0 1 0 0 1

0 0 0 0 0 0 X 0 1 0 0 1 0 1

0 0 0 0 0 0 0 0 0 0 0 0 0 1

0 1 1 1 1 1 1 1 1 1 1 1 1 0

Department of E & C SSIT

6

Experiment No: DATE: __/__/____

ENCODER & DECODER

AI M:-To convert a given octal input to the binary output and to study the LED

display using 7447 7-segment decoder/ driver.

APPARATUS REQUI RED: -

I C 74148, I C 7447, 7-segment display, etc.

PROCEDURE: - (Encoder)

1. Connections are made as per circuit diagram.

2. The octal inputs are given at the corresponding pins.

3. The outputs are verified at the corresponding output pins.

PROCEDURE: - (Decoder)

1. Connections are made as per the circuit diagram.

2. Connect the pins of I C 7447 to the respective pins of the LED display board.

3. Give different combinations of the inputs and observe the decimal numbers

displayed on the board.

RESULT: -

The given octal numbers are converted into binary numbers.

The given data is displayed using &-segment LED decoder.

Department of E & C SSIT

7

TABULAR COLUMN:-

Q4 Q3 Q2 Q1 O/P Display Glowing LEDs

0 0 0 0 0

a,b,c,d,e,f

0 0 0 1 1

b,c

0 0 1 0 2

a,b,d,e,g

0 0 1 1 3

a,b,c,d,g

0 1 0 0 4

b,c,f,g

0 1 0 1 5

a,c,d,f,g

0 1 1 0 6

a.c.d.e.f.g

0 1 1 1 7

a.b.c

1 0 0 0 8

a,b,c,d,e,f,g

1 0 0 1 9

a,b,c,d,f,g

1 0 1 0 10

d,e,g

1 0 1 1 11

c,d,g

1 1 0 0 12

c,d,e

1 1 0 1 13

a,g,d

1 1 1 0 14

d,e,f,g

1 1 1 1 15

blank

Department of E & C SSIT

8

PI N DETAI LS:-

DI SPLAY:-

Conclusion:-

.

Signature of the staff in charge

Digital Electronics Lab SSIT

29

Circuit Diagram: - (Master Slave J K Flip-Flop)

D Flip-Flop:-

T Flip-Flop:-

Digital Electronics Lab SSIT

30

Experiment No: Date: __/__/____

FLI P-FLOP

Aim:- Truth table verification of Flip-Flops: (i) J K Master Slave

(ii) D- Type

(iii) T- Type.

Apparatus Required: -

I C 7410, I C 7400, etc.

Procedure: -

1. Connections are made as per circuit diagram.

2. The truth table is verified for various combinations of inputs.

Truth Table:- (Master Slave J K Flip-Flop)

Preset Clear J K Clock Qn+1 1 Qn+

0 1 X X X 1 0 Set

1 0 X X X 0 1 Reset

1 1 0 0 Qn Qn No Change

1 1 0 1

0 1 Reset

1 1 1 0

1 0 Set

1 1 1 1 Qn Qn Toggle

D Flip-Flop:-

Preset Clear D Clock Qn+1 1 Qn+

1 1 0

0 1

1 1 1

1 0

T Flip-Flop:-

Preset Clear T Clock Qn+1 1 Qn+

1 1 0 Qn Qn

1 1 1 Qn Qn

Exercise:-

Write the timing diagrams for all the above Flip-Flops

Signature of the staff in charge

Digital Electronics Lab SSIT

31

Pin Details: - Truth Table:-

Clock QC QB QA

0 0 0 0

1 0 0 1

2 0 1 0

3 0 1 1

4 1 0 0

5 1 0 1

6 1 1 0

7 1 1 1

Timing Diagram:-

Circuit Diagram: - 3-Bit Asynchronous Up Counter

3-bit Asynchronous

up counter

Clock QC QB QA

0 0 0 0

1 0 0 1

2 0 1 0

3 0 1 1

4 1 0 0

5 1 0 1

6 1 1 0

7 1 1 1

8 0 0 0

Digital Electronics Lab SSIT

32

9 0 0 1

Experiment No: Date: __/__/____

COUNTERS

Aim:-

Realization of 3-bit counters as a sequential circuit and Mod-N counter

design (7476, 7490, 74192, 74193).

Apparatus Required: -

I C 7408, I C 7476, I C 7490, I C 74192, I C 74193, I C 7400, I C 7416, I C 7432

etc.

Procedure: -

1. Connections are made as per circuit diagram.

2. Clock pulses are applied one by one at the clock I /P and the O/P is

observed at QA, QB & QC for I C 7476.

3. Truth table is verified.

Procedure (I C 74192, I C 74193):-

1. Connections are made as per the circuit diagram except the connection

from output of NAND gate to the load input.

2. The data (0011) = 3 is made available at the data i/ps A, B, C & D

respectively.

3. The load pin made low so that the data 0011 appears at QD, QC, QB & QA

respectively.

4. Now connect the output of the NAND gate to the load input.

5. Clock pulses are applied to count up pin and the truth table is verified.

6. Now apply (1100) = 12 for 12 to 5 counter and remaining is same as for 3

to 8 counter.

Digital Electronics Lab SSIT

33

7. The pin diagram of I C 74192 is same as that of 74193. 74192 can be

configured to count between 0 and 9 in either direction. The starting value

can be any number between 0 and 9.

Circuit Diagram: - 3-Bit Asynchronous Down Counter

3-bit Asynchronous

down counter

Clock QC QB QA

0 1 1 1

1 1 1 0

2 1 0 1

3 1 0 0

4 0 1 1

5 0 1 0

6 0 0 1

7 0 0 0

8 1 1 1

9 1 1 0

Mod 5 Asynchronous Counter:-

Digital Electronics Lab SSIT

34

Mod 5 Asynchronous

counter

Clock QC QB QA

0 0 0 0

1 0 0 1

2 0 1 0

3 0 1 1

4 1 0 0

5 0 0 0

Mod 3 Asynchronous Counter:-

Mod 3 Asynchronous

counter

Clock QC QB QA

0 0 0 0

1 0 0 1

2 0 1 0

3 0 0 0

4 0 0 1

5 0 1 0

3-bit Synchronous Counter:-

Digital Electronics Lab SSIT

35

I C 7490 (Decade Counter):-

Clock QD QC QB QA

0 0 0 0 0

1 0 0 0 1

2 0 0 1 0

3 0 0 1 1

4 0 1 0 0

5 0 1 0 1

6 0 1 1 0

7 0 1 1 1

8 1 0 0 0

9 1 0 0 1

10 0 0 0 0

I C 7490 (MOD-8 Counter):-

Clock QD QC QB QA

0 0 0 0 0

1 0 0 0 1

2 0 0 1 0

3 0 0 1 1

4 0 1 0 0

5 0 1 0 1

6 0 1 1 0

7 0 1 1 1

8 0 0 0 0

9 0 0 0 1

Circuit Diagram (I C 74193) To Count from 3 to 8:-

Digital Electronics Lab SSIT

36

Clock QD QC QB QA

Count in

Decimal

0 0 0 1 1 3

1 0 1 0 0 4

2 0 1 0 1 5

3 0 1 1 0 6

4 0 1 1 1 7

5 1 0 0 0 8

6 0 0 1 1 3

7 repeats 4

Circuit Diagram (I C 74193) To Count from 8 to 3:-

Clock QD QC QB QA

Count in

Decimal

0 0 1 0 1 5

1 0 1 1 0 6

2 0 1 1 1 7

3 1 0 0 0 8

4 1 0 0 1 9

5 1 0 1 0 10

6 1 0 1 1 11

7 1 1 0 0 12

8 0 1 0 1 5

9 repeats 6

Function Table for 7490:-

Digital Electronics Lab SSIT

37

4 I /P OR Gate can be realized as follows:-

Conclusion:-

..

Signature of the staff in charge

Clock R1 R2 S1 S2 QD QC QB QA

X H H L X L L L L RESET

X H H X L L L L L RESET

X X X H H H L L H

SET

TO 9

X L X L COUNT

L X L X COUNT

L X X L COUNT

X L L X COUNT

Digital Electronics Lab SSIT

35

Circuit Diagram: - Shift Left

SI PO (Right Shift):-

SI SO:-

Clock Serial i/p QA QB QC QD

1 do=0 0 X X X

2 d1=1 1 0 X X

3 d2=1 1 1 0 X

4 d3=1 1 1 1 0=do

5 X X 1 1 1=d1

6 X X X 1 1=d2

7 X X X X 1=d3

Clock Serial i/p QA QB QC QD

1 1 X X X 1

2 0 X X 1 0

3 1 X 1 0 1

4 1 1 0 1 1

Clock Serial i/p QA QB QC QD

1 0 0 X X X

2 1 1 0 X X

3 1 1 1 0 X

4 1 1 1 1 0

Digital Electronics Lab SSIT

36

Experiment No: Date: __/__/____

SHI FT REGI STERS

Aim:-

Realization of 3-bit counters as a sequential circuit and Mod-N counter

design (7476, 7490, 74192, 74193).

Apparatus Required: -

I C 7495, etc.

Procedure: -

Serial I n Parallel Out:-

1. Connections are made as per circuit diagram.

2. Apply the data at serial i/p

3. Apply one clock pulse at clock 1 (Right Shift) observe this data at QA.

4. Apply the next data at serial i/p.

5. Apply one clock pulse at clock 2, observe that the data on QA will shift to

QB and the new data applied will appear at QA.

6. Repeat steps 2 and 3 till all the 4 bits data are entered one by one into the

shift register.

Serial I n Serial Out:-

1. Connections are made as per circuit diagram.

2. Load the shift register with 4 bits of data one by one serially.

3. At the end of 4

th

clock pulse the first data d0 appears at QD.

4. Apply another clock pulse; the second data d1 appears at QD.

5. Apply another clock pulse; the third data appears at QD.

6. Application of next clock pulse will enable the 4

th

data d3 to appear at

QD. Thus the data applied serially at the input comes out serially at QD

PI SO:-

Digital Electronics Lab SSIT

37

PI PO:-

Mode Clock Parallel i/p Parallel o/p

A B C D QA QB QC QD

1 1 1 0 1 1 1 0 1 1

0 2 X X X X X 1 0 1

0 3 X X X X X X 1 0

0 4 X X X X X X X 1

Clock Parallel i/p Parallel o/p

A B C D QA QB QC QD

1 1 0 1 1 1 0 1 1

Digital Electronics Lab SSIT

38

Parallel I n Parallel Out:-

1. Connections are made as per circuit diagram.

2. Apply the 4 bit data at A, B, C and D.

3. Apply one clock pulse at Clock 2 (Note: Mode control M=1).

4. The 4 bit data at A, B, C and D appears at QA, QB, QC and QD

respectively.

Parallel I n Serial Out:-

1. Connections are made as per circuit diagram.

2. Apply the desired 4 bit data at A, B, C and D.

3. Keeping the mode control M=1 apply one clock pulse. The data applied at

A, B, C and D will appear at QA, QB, QC and QD respectively.

4. Now mode control M=0. Apply clock pulses one by one and observe the

data coming out serially at QD.

Left Shift:-

1. Connections are made as per circuit diagram.

2. Apply the first data at D and apply one clock pulse. This data appears at

QD.

3. Now the second data is made available at D and one clock pulse applied.

The data appears at QD to QC and the new data appears at QD.

4. Step 3 is repeated until all the 4 bits are entered one by one.

5. At the end 4

th

clock pulse the 4 bits are available at QA, QB, QC and QD.

Conclusion:-

..

Signature of the staff in charge

Digital Electronics Lab SSIT

39

Circuit Diagram: - Ring Counter

J ohnson Counter:-

Mode Clock QA QB QC QD

1 1 1 0 0 0

0 2 0 1 0 0

0 3 0 0 1 0

0 4 0 0 0 1

0 5 1 0 0 0

0 6 repeats

Mode Clock QA QB QC QD

1 1 1 0 0 0

0 2 1 1 0 0

0 3 1 1 1 0

0 4 1 1 1 1

0 5 0 1 1 1

0 6 0 0 1 1

0 7 0 0 0 1

0 8 0 0 0 0

0 9 1 0 0 0

0 10 repeats

Digital Electronics Lab SSIT

40

Experiment No: Date: __/__/____

J OHNSON COUNTERS / RI NG COUNTER

Aim:- Design and testing of Ring counter/ J ohnson counter.

Apparatus Required: -

I C 7495, I C 7404, etc.

Procedure: -

1. Connections are made as per the circuit diagram.

2. Apply the data 1000 at A, B, C and D respectively.

3. Keeping the mode M = 1, apply one clock pulse.

4. Now the mode M is made 0 and clock pulses are applied one by one and

the truth table is verified.

5. Above procedure is repeated for J ohnson counter also.

Digital Electronics Lab SSIT

41

Circuit Diagram: - Sequence Generator

Truth Table:-

Map

Value

Clock QA QB QC QD o/p D

15 1 1 1 1 1 0

7 2 0 1 1 1 0

3 3 0 0 1 1 0

1 4 0 0 0 1 1

8 5 1 0 0 0 0

4 6 0 1 0 0 0

2 7 0 0 1 0 1

9 8 1 0 0 1 1

12 9 1 1 0 0 0

6 10 0 1 1 0 1

11 11 1 0 1 1 0

5 12 0 1 0 1 1

10 13 1 0 1 0 1

13 14 1 1 0 1 1

14 15 1 1 1 0 1

Karnaugh Map for D:-

QA QB

QCQD 00 01 11 10

00 0 0 0 0

01 1 1 1 1

11 0 0 0 0

10 1 1 1 1

Digital Electronics Lab SSIT

42

Experiment No: Date: __/__/____

SEQUENCE GENERATOR

Aim:- Design of Sequence Generator.

Apparatus Required: -

IC 7495, IC 7486, etc.

Design:-

To generate a sequence of length S it is necessary to use at least N number of

Flip-Flops, which satisfies the condition S 2

N

-1.

The given sequence length S = 15.

Therefore N = 4.

Note: - There is no guarantee that the given sequence can be generated by 4 f/fs.

If the sequence is not realizable by 4 f/fs then 5 f/fs must be used and so on.

Procedure: -

1. Connections are made as per the circuit diagram.

2. Clock pulses are applied one by one and truth table is verified.

Conclusion:-

.

Signature of the staff in charge

Digital Electronics Lab SSIT

43

Circuit Diagram: - Monostable Multivibrator

Waveform:-

Digital Electronics Lab SSIT

44

Experiment No: Date: __/__/____

MULTIVIBRATORS

Aim:-

Design and testing of Monostable and Astable multivibrators using 555

timer.

Apparatus Required: -

IC 555 timer, resistor, capacitor, etc.

Design:- (Monostable)

Given pulse width required = 1ms

Pulse width T = 1.1RC

Therefore 1ms = 1.1RC

Let C = 0.1f

Therefore

6

3

10 1 . 0 1 . 1

10 1

R

=

Procedure: -(Monostable)

1. Connections are made as per the circuit diagram.

2. Triggering pulses are applied at pin 2.

3. The pulse width of the waveform at pin3 is measured and verified with the

designed value.

Digital Electronics Lab SSIT

45

Astable Multivibrator:-

Wave form:-

Digital Electronics Lab SSIT

46

Design:-

Ton = 0.69(R

A

+ R

B

)C, Toff = 0.69 R

B

C

Given; f = 10 KHz, duty cycle = 70%,

Therefore T = (1/f) = (1/10x10

3

) = 0.1ms

D = (Ton/T) = 0.7

Ton = 0.7T = 0.7x0.1ms = 0.07ms

T = Ton + Toff

Therefore Toff = 0.03ms

Ton = 0.69 (R

A

+ R

B

) C

Let C = 0.1f

Therefore 0.07 x 10

-3

= 0.69 (R

A

+ R

B

) 0.1 x 10

-6

Therefore R

A

+ R

B

= 1014 ohms

Toff = 0.69 R

B

C

0.03 x 10

-3

= 0.69 (R

B

) 0.1 x 10

-6

Therefore R

B

= 434.7 ohms

Therefore R

A

= 579 ohms

Procedure: -

1. Connections are made as per circuit diagram

2. Switch on the 5V power supply

3. Observe the waveforms at pin 3 on CRO, measure Ton, Toff, T and its

amplitude.

4. Also observe capacitor voltage on CRO.

Conclusion:-

.

Digital Electronics Lab SSIT

47

Signature of the staff in charge

Example for Data I nput:-

Address I nputs

A3 A2 A1 A0

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

Data I nputs

I /O4 I /O3 I /O2 I /O1

0 0 1 0

0 1 0 0

0 1 0 1

0 1 1 0

Example for Data Output:-

Address I nputs

A3 A2 A1 A0

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

Data Outputs

I /O4 I /O3 I /O2 I /O1

0 0 1 0

0 1 0 0

0 1 0 1

0 1 1 0

Experiment No: Date: __/__/____

STATI C RAM

Aim: - To conduct an experiment to store a set of data in a RAM using I C 2114

starting from location ------- to location-------- and retrieve the same data.

Apparatus Required: -

I C 2114, etc.

Procedure: -

1. circuits connections are made to the appropriate pins of I C 2114

2. First you have to write the data and then read the data, for writing data

make WE to low and CS input to low

3. for a 4-bit data select any address input from A0 to A9. for ex, select A3 to

A0 and connect the data inputs/ outputs i.e., I /O4 I /O1

4. write a 4-bit data of your choice in each of the required address inputs or

memory locations

5. by doing the above steps 2, 3 and 4 the data will be stored in the memory

location

6. for reading data

a. make WE to high and CS input to low

b. disconnect the data inputs I /O4 I /O1 from input lines and connect

them to output lines to read the data

c. and then give the address inputs of the data you have stored and

observe the outputs through I /O4 I /O1.

Conclusion:-

.

Signature of the staff in charge

S-ar putea să vă placă și

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Autonomous Colleges ListDocument35 paginiAutonomous Colleges ListReddyvari VenugopalÎncă nu există evaluări

- Boy NamesDocument1 paginăBoy NamesReddyvari VenugopalÎncă nu există evaluări

- Enter data only in green cells to calculate insurance needsDocument6 paginiEnter data only in green cells to calculate insurance needsReddyvari VenugopalÎncă nu există evaluări

- Physics and Electronics CBCSDocument39 paginiPhysics and Electronics CBCSReddyvari VenugopalÎncă nu există evaluări

- Heat transfer over stretching sheet in micropolar fluidDocument10 paginiHeat transfer over stretching sheet in micropolar fluidReddyvari VenugopalÎncă nu există evaluări

- PH 411 Physics Laboratory I (Electronics) : Instruction Manual IndexDocument28 paginiPH 411 Physics Laboratory I (Electronics) : Instruction Manual IndexReddyvari VenugopalÎncă nu există evaluări

- Èí©'°Æ Ƒyk! Èí©'°Æ Ƒyk! Èí©'°Æ Ƒyk! Èí©'°Æ Ƒyk! Èí©'°Æ Ƒyk! Èí©'°Æ Ƒyk! Èí©'°Æ Ƒyk! Èí©'°Æ Ƒyk! Y Y Y Y Y Y Y YDocument1 paginăÈí©'°Æ Ƒyk! Èí©'°Æ Ƒyk! Èí©'°Æ Ƒyk! Èí©'°Æ Ƒyk! Èí©'°Æ Ƒyk! Èí©'°Æ Ƒyk! Èí©'°Æ Ƒyk! Èí©'°Æ Ƒyk! Y Y Y Y Y Y Y YReddyvari VenugopalÎncă nu există evaluări

- AP GeographyDocument86 paginiAP Geographyvenkat76175% (4)

- CE Transistor CharacteristicsDocument4 paginiCE Transistor CharacteristicsReddyvari VenugopalÎncă nu există evaluări

- Crystal Structure FundamentalsDocument20 paginiCrystal Structure FundamentalsReddyvari VenugopalÎncă nu există evaluări

- D.C. Power Supply: Experiment ADocument5 paginiD.C. Power Supply: Experiment AReddyvari VenugopalÎncă nu există evaluări

- Lab ExperimentDocument7 paginiLab ExperimentBryan Owen Salcedo SantosÎncă nu există evaluări

- Determine the dielectric constant of capacitors by charging and dischargingDocument6 paginiDetermine the dielectric constant of capacitors by charging and dischargingReddyvari Venugopal33% (3)

- Attenuation in OFCDocument4 paginiAttenuation in OFCReddyvari VenugopalÎncă nu există evaluări

- Article PDFDocument13 paginiArticle PDFReddyvari VenugopalÎncă nu există evaluări

- Açúõ Ûª°Æ¤P©'! Îáê°P-¢√∞¡Ÿx ™‰Éπ..Document1 paginăAçúõ Ûª°Æ¤P©'! Îáê°P-¢√∞¡Ÿx ™‰Éπ..Reddyvari VenugopalÎncă nu există evaluări

- IP AddressDocument1 paginăIP AddressReddyvari VenugopalÎncă nu există evaluări

- Sakshi: V. X, X, X, X .... X W, W, W, W .... WDocument3 paginiSakshi: V. X, X, X, X .... X W, W, W, W .... WReddyvari VenugopalÎncă nu există evaluări

- Modern Physics Sample UseDocument1 paginăModern Physics Sample UseReddyvari VenugopalÎncă nu există evaluări

- Importance of Handwriting in Civils MainsDocument6 paginiImportance of Handwriting in Civils MainsReddyvari VenugopalÎncă nu există evaluări

- Alternating CurrentDocument12 paginiAlternating CurrentReddyvari Venugopal50% (2)

- APDocument14 paginiAPReddyvari VenugopalÎncă nu există evaluări

- Suggested BooksDocument4 paginiSuggested BooksReddyvari VenugopalÎncă nu există evaluări

- Public AdministrationDocument2 paginiPublic AdministrationReddyvari VenugopalÎncă nu există evaluări

- 09 4 Compton Effect PDFDocument6 pagini09 4 Compton Effect PDFReddyvari Venugopal100% (1)

- Suggested BooksDocument4 paginiSuggested BooksReddyvari VenugopalÎncă nu există evaluări

- 09 3 X-Rays PDFDocument7 pagini09 3 X-Rays PDFReddyvari VenugopalÎncă nu există evaluări

- 09 3 X-Rays PDFDocument7 pagini09 3 X-Rays PDFReddyvari VenugopalÎncă nu există evaluări

- 09 2 Photo Electric Effect PDFDocument10 pagini09 2 Photo Electric Effect PDFReddyvari VenugopalÎncă nu există evaluări

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (894)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (265)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (73)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (119)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- 8B10B CodingDocument29 pagini8B10B CodingRamakrishnaRao SoogooriÎncă nu există evaluări

- Special Diodes and Their Applications-18Document26 paginiSpecial Diodes and Their Applications-18sakib9ahmed-2Încă nu există evaluări

- Neutral Inversion and Neutral Displacement - Voltage DisturbanceDocument12 paginiNeutral Inversion and Neutral Displacement - Voltage DisturbanceVishnu ShankerÎncă nu există evaluări

- Internship ReportDocument32 paginiInternship ReportAdit RajÎncă nu există evaluări

- Introduction to Computers: An Essential GuideDocument97 paginiIntroduction to Computers: An Essential Guideta_1091100% (1)

- Eee374 Emi Solved ManualDocument3 paginiEee374 Emi Solved Manualraja badarÎncă nu există evaluări

- LT Spice ExperimentsDocument15 paginiLT Spice ExperimentsSachin George ThomasÎncă nu există evaluări

- Mobile cinema packages for exclusive film nights anywhereDocument10 paginiMobile cinema packages for exclusive film nights anywhereCarlos VuelveÎncă nu există evaluări

- NTP8230 IcpdfDocument55 paginiNTP8230 IcpdfAldy PutraprasetiyoÎncă nu există evaluări

- LG Oled65g6p T-Con Board Layout Voltages 2017Document10 paginiLG Oled65g6p T-Con Board Layout Voltages 2017Fernando AguiarÎncă nu există evaluări

- 01 - Difference Between WCDMA and GSMDocument11 pagini01 - Difference Between WCDMA and GSMAdil SumantriÎncă nu există evaluări

- Occupancy Based Fan Speed ControllerDocument28 paginiOccupancy Based Fan Speed ControllerVinay MishraÎncă nu există evaluări

- Jm506 Programmable Logic ControlDocument10 paginiJm506 Programmable Logic ControlMuhammad HafizÎncă nu există evaluări

- EX3G HMI PLC All-in-One User Manual Specs and DimensionsDocument2 paginiEX3G HMI PLC All-in-One User Manual Specs and DimensionsMarcos Luiz AlvesÎncă nu există evaluări

- 15.6Document31 pagini15.6Recep TOSUNÎncă nu există evaluări

- Convert 12V to 5V Using LM7805 ICDocument4 paginiConvert 12V to 5V Using LM7805 ICsudÎncă nu există evaluări

- Millman's Theorem: Chapter 10 - DC Network AnalysisDocument17 paginiMillman's Theorem: Chapter 10 - DC Network AnalysisAce Dela CruzÎncă nu există evaluări

- PastPapersDownload (6) - 220227 - 212448Document11 paginiPastPapersDownload (6) - 220227 - 212448Deer DeerÎncă nu există evaluări

- USB Digital Microscope User ManualDocument42 paginiUSB Digital Microscope User ManualMarcos SilvaÎncă nu există evaluări

- Rocktron Utopia G100 - Owner's GuideDocument72 paginiRocktron Utopia G100 - Owner's GuideIvan JonesÎncă nu există evaluări

- Project Report On Safety BoatDocument36 paginiProject Report On Safety BoatNikil.A HadiÎncă nu există evaluări

- Dynamic Microphone Order # 406.910: Eatures Echnical PecificationsDocument2 paginiDynamic Microphone Order # 406.910: Eatures Echnical PecificationsgbÎncă nu există evaluări

- DS 1147 SS CMCDT2100LTC ADocument3 paginiDS 1147 SS CMCDT2100LTC ANightcrawlerÎncă nu există evaluări

- REN R20ut0757ej3500-Pgfp5-List MAN 20201006Document35 paginiREN R20ut0757ej3500-Pgfp5-List MAN 20201006KingÎncă nu există evaluări

- HFSS Design GuideDocument69 paginiHFSS Design GuidedilaawaizÎncă nu există evaluări

- Circuits 2 Quiz 3Document2 paginiCircuits 2 Quiz 3John Lenard SanchezÎncă nu există evaluări

- P4m90-M7a P4M89-M7B 0611CDocument47 paginiP4m90-M7a P4M89-M7B 0611CEscri Thor MentaÎncă nu există evaluări

- User Manual of DCH-4000P-Ver DDocument17 paginiUser Manual of DCH-4000P-Ver DRobertÎncă nu există evaluări

- How To Start Programming For ARM7 Based LPC2148 MicrocontrollerDocument5 paginiHow To Start Programming For ARM7 Based LPC2148 Microcontrollerrudra_1Încă nu există evaluări

- Rx 1575.42MHz AGPS Supported MSM_ADocument58 paginiRx 1575.42MHz AGPS Supported MSM_ASalvadorRodriguesÎncă nu există evaluări