Documente Academic

Documente Profesional

Documente Cultură

System e Minimum

Încărcat de

Salah DahouathiDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

System e Minimum

Încărcat de

Salah DahouathiDrepturi de autor:

Formate disponibile

Structure des systmes minimums de traitement de l'information

Dpartement GEII

Structure des systmes minimums de traitement de l'information

Philippe Hoppenot

hoppenot@lsc.univ-evry.fr http://lsc.univ-evry.fr/~hoppenot/presentationfrancaise.html

Ce cours sur la structure des systmes minimums de traitement de l'information est dispens en licence professionnelle Concepteurs de Systmes de Commande Industrielle. Son utilisation est libre avec les contraintes suivantes : - Ne pas l'utiliser des fins commerciales - Citer la source lors de son utilisation - Avertir l'auteur de son utilisation Toutes les remarques sur le fond et la forme de ce document sont les bienvenues.

P. Hoppenot (09/06/04)

Informatique Industrielle

1/16

Structure des systmes minimums de traitement de l'information

Structure des systmes minimums de traitement de l'information

I. Architecture d'un systme minimum ................................................................................................3 I.1. Elments constitutifs ............................................................................................................3 I.2. Communication - les bus ......................................................................................................3 I.2.1. Bus de donnes.........................................................................................................3 I.2.2. Bus d'adresses ..........................................................................................................4 I.2.3. Bus de contrle.........................................................................................................4 I.3. Structure d'un composant priphrique ................................................................................5 II. Bus d'un systme minimum.............................................................................................................6 II.1. Bus non multiplexs Exemple de la famille 68K de Motorola ........................................6 II.2. Bus multiplexs - Exemple du 8051 d'Intel ........................................................................7 II.3. Les conflits d'accs au bus ..................................................................................................8 III. Echanges processeur priphrique ..............................................................................................9 III.1. Echange synchrone ............................................................................................................9 III.2. Echange asynchrone ..........................................................................................................9 IV. Gestion d'un systme minimum ...................................................................................................10 IV.1. Registres internes.............................................................................................................11 IV.2. Accs aux donnes Modes d'adressage ........................................................................12 IV.2.1. Immdiat ..............................................................................................................12 IV.2.2. Direct ...................................................................................................................12 IV.2.3. Indirect.................................................................................................................12 IV.3. Notion de programme ......................................................................................................12 IV.3.1. Instructions ..........................................................................................................12 IV.3.2. Structure d'un programme...................................................................................13 IV.3.3. Codage.................................................................................................................13 IV.3.4. Excution d'un programme..................................................................................13 IV.4. Interruptions.....................................................................................................................14

P. Hoppenot (09/06/04)

Informatique Industrielle

2/16

Structure des systmes minimums de traitement de l'information

Le cur d'un systme industriel est le traitement d'information. Le cours d'lectronique prsente le traitement des informations analogiques. Le cours d'informatique industrielle prsente le traitement des donnes numriques. Il existe deux manires de mettre en uvre un traitement numrique. La solution cble, les composants "programmables" en VHDL de type CPLD remplaant depuis le milieu des annes 90 les composants discrets, donne des systmes optimiss mais peu volutifs dans lesquels toutes les fonctions sont dcrites par le concepteur. La solution programme, base sur les microprocesseurs, permet la mise en uvre de solutions plus complexes et plus volutives. C'est cette seconde solution que s'atle ce cours. L'architecture de ces systmes est prsente dans la section I. La section suivante (II) prsente le mdium de communication entre le processeur et ces priphriques. Le fonctionnement de ces changes est expliqu dans la section III. Enfin, la section IV aborde la notion fondamentale de l'interruption, interface indispensable entre le programme et le matriel. I. Architecture d'un systme minimum I.1. Elments constitutifs Processeur : Cur du systme, il accueille et met en uvre le traitement dcrit sous la formes d'une suite d'instructions. ROM : Read Only Memory (mmoire lecture seule), de type PROM, EPROM ou EEPROM, elle contient le programme et l'environnement ncessaire son excution (moniteur, debogueur, boot loader, table de vecteurs d'interruption). Elle est non volatile. RAM : Random Access Memory (mmoire accs alatoire), de type SRAM (statique RAM) ou DRAM (Dynamique RAM), elle contient les donnes temporaires utiles au bon droulement des programmes. Elle est volatile. Entres sorties : Dispositifs permettant au systme de communiquer avec l'extrieur : port parallle, port srie, contrleur de rseau en fonction des utilisations. Alimentation : Tous les circuits lectronique ont besoin d'une alimentation. Quartz : Tous les systmes voluant dans le temps on besoin d'une rfrence. Elle est donne par un quartz qui dfinit l'unit de temps de base. I.2. Communication - les bus L'change d'information entre le processeur et ses priphriques s'effectue en deux temps. Dans la premire phase, le processeur impose l'adresse laquelle la donne va tre lue ou crite. Durant la seconde phase, la donne est change. Un change d'information s'effectue travers un bus, ensemble de fils. Chaque fils peut se trouver dans trois tats : 0, 1, haute impdance. Trois bus permettent le fonctionnement d'un systme minimum : - le bus de donnes - le bus d'adresses - le bus de contrle I.2.1. Bus de donnes Bus sur lequel circulent les donnes ncessaires au traitement et les instructions qui ralisent ces traitements. Il est bidirectionnel et commun au processeur et tous les priphriques. La taille du bus de donnes varie de 8 bits 64 bits voire 128 bits. Cela correspond au nombre de bits transfr en un seul change.

P. Hoppenot (09/06/04)

Informatique Industrielle

3/16

Structure des systmes minimums de traitement de l'information

I.2.2. Bus d'adresses Bus sur lequel circule l'adresse de la donne change. Il est unidirectionnel : c'est le processeur qui choisit l'adresse. La taille du bus d'adresses donne le nombre de donnes que le processeur peut traiter. En combinant la taille du bus de donnes et la taille du bus d'adresses, on obtient la capacit d'adressage du processeur. Exemples : 8051 68360 I.2.3. Bus de contrle Bus sur lequel circulent les signaux permettant le fonctionnement du systme. Les signaux les plus classiques sont R pour la lecture et W pour l'criture (Intel), RW pour la lecture-criture (Motorola), LDS et UDS pour le choix entre le poids fort et le poids faible des donnes (Motorola). Les et donnent des exemples de lecture et d'criture avec le 8051. Bus d'adresses : 16 bits => 216 adresses = 26x210 adresses = 64 K Bus de donnes : 8 bits => 64 Koctets Bus d'adresses : 32 bits => 232 adresses = 22x210 x210x210 adresses = 4 G Bus de donnes : 16 bits => 4 Gmots = 8 Goctets

Figure I.1 : Cycle de lecture dans une mmoire de donnes avec le 8051.

Figure I.2 : Cycles de lecture et d'criture avec le 68000.

D'autres signaux de contrle seront abords au fur et mesure.

P. Hoppenot (09/06/04)

Informatique Industrielle

4/16

Structure des systmes minimums de traitement de l'information

I.3. Structure d'un composant priphrique Un composant priphrique a deux caractristiques : - Il ralise une fonction : mmoire, comptage - Il s'interface avec le processeur. Exemples : EEPROM 27C256 - Fonction : mmoire morte effaable lectriquement, non volatile.

Figure I.3 : Schma de cblage DIP de la mmoire EEPROM 27C256.

- Valeur par dfaut de chaque point mmoire : 1 logique - Programmation de la mmoire : mise 0 de certains points logiques. - PROM : dfinitif - EPROM : Impulsion sur le drain d'un transistor MOS. L'effet d'avalanche provoque la conduction. Un bombardement aux ultraviolets permet de rtablir l'tat bloqu. - EEPROM : La grille du transistor MOS est plac un potentiel lectrique. La mmoire est effaable lectriquement. - Interfaage avec le bus : ralis avec des "buffers" trois tats. - 0 logique reprsent par un potentiel entre 0 V et 0,8 V - 1 logique reprsent par un potentiel entre 2 V et 5 V - Haute impdance reprsent par une broche dconnecte du bus (potentiel flottant).

Figure I.4 : Structure physique du buffer trois tats CMOS.

- Le bus est unidirectionnel. RAM 5256 - Fonction : mmoire vive, volatile - Structure d'un point mmoire : - SRAM (Static RAM)

P. Hoppenot (09/06/04)

Informatique Industrielle

5/16

Structure des systmes minimums de traitement de l'information

Figure I.5 : Structure d'un point mmoire SRAM.

Dans ce cas, deux buffers se rafrachissent mutuellement. -DRAM (Dynamic RAM)

Figure I.6 :Structure d'un point mmoire DRAM.

Ici, la dcharge du condensateur ncessite une rafrachissement actif. Plus lentes que les mmoires statiques, elles sont plus denses et donc largement utilises. - Interfaage avec le bus : ralis avec des "buffers" trois tats. - 0 logique reprsent par un potentiel entre 0 V et 0,8 V - 1 logique reprsent par un potentiel entre 2 V et 5 V - Haute impdance reprsent par une broche dconnecte du bus (potentiel flottant). - Le bus est bidirectionnel. Par convention, le sens du bus est donn vu du processeur. Ainsi, en criture le bus est en sortie pour le processeur et en entre pour la mmoire ; en lecture le bus est en entre pour le processeur et en sortie pour la mmoire. II. Bus d'un systme minimum Le bus est l'interface entre le processeur et ses priphriques. Il existe deux familles de bus d'adresses et de donnes : multiplexs et non multiplexs. Dans les deux cas, les deux phases de l'change (adresses puis donnes) sont respectes. C'est l'implantation physique des bus qui diffre. Il convient aussi de se demander comment les conflits d'accs au bus sont grs. II.1. Bus non multiplexs Exemple de la famille 68000 de Motorola Les bus d'adresses et de donnes du 68000 sont physiquement spars (Figure II.1). On dit qu'il s'agit de bus non multiplexs. Le bus d'adresses comprend 23 bits et le bus de donnes 16 bits. On peut donc adresser 223 mots de 16 bits soit 8 Mmots ou 16 Moctets. On remarque que le bit A0 n'existe pas. Il est en fait remplac par LDS et UDS qui dsignent le poids faible ou le poids fort de la donne change (Figure I.2).

P. Hoppenot (09/06/04)

Informatique Industrielle

6/16

Structure des systmes minimums de traitement de l'information

Figure II.1 : Description des entres/sorties du 68000.

L'change est pilot par les signaux suivants du bus de contrle : - AS : Validation des adresses - R/W : Sens du bus de donnes : lecture ou criture - DTACK : acquittement des donnes (voir change asynchrone, III.2) II.2. Bus multiplexs - Exemple du 8051 d'Intel

mmorisation de ADL

P0

DATA

1re

phase

ADL

573

ADL

C

P2

ALE

MEM

ADH OE WE

2me

phase

RD WR

DATA

Les ports P0 et P2 ne sont plus utilisables en tant que ports

Figure II.2 : Exemple de bus multiplex Cas du 8051.

Dans le cas du 8051, les bus d'adresses et de donnes utilisent des ressources physiques communes. En effet, le bus d'adresse est compos de 16 bits et le bus de donnes de 8 bits soit 24 bits, le tout devant se partager 2 ports (P0 et P2) de 8 bits soit 16 bits. Cette apparente contradiction se rsout en tirant profit des deux tapes dans l'change de donnes (I.2). Dans la premire phase, l'adresse est

P. Hoppenot (09/06/04)

Informatique Industrielle

7/16

Structure des systmes minimums de traitement de l'information

prsente sur les 16 bits disponibles, les poids faibles sur P0 et les poids forts sur P2. A la fin de cette phase, identifie par ALE, les poids faibles des adresses sont mmorises dans une latch (573). Ainsi, le port P0 est-il libr pour permettre aux donnes de circuler. La Figure II.2 illustre ce type d'change. II.3. Les conflits d'accs au bus Les bus d'adresses, de donnes et de contrle sont communs au processeur et ses diffrents priphriques. Dans tous ces changes, c'est le processeur qui choisit l'adresse de la donne transfrer et gre l'change. Ainsi, seul le processeur crit sur les bus d'adresses et de contrle. En revanche, tous les priphriques peuvent tre amens crire sur le bus de donnes. Lorsque le processeur initie une lecture, quel priphrique doit rpondre ? Le principe consiste dcouper l'espace d'adressage du processeur. Par exemple, pour un systme base de 68000, on peut imaginer le dcoupage suivant de la mmoire : FF FFFF 04 0000 03 FFFF 03 0000 02 FFFF 02 0000 01 FFFF 01 0000 00 FFFF 00 0000 CAN E/S RAM ROM

Figure II.3 : Exemple d'espace d'adressage avec le 68000.

La Table II.1 donne les adresses correspondant aux zones mmoires dfinies dans la Figure II.3. On remarque que les bits A17 et A16 sont dterminants pour dsigner une zone. On obtient la table d'un dcodeur dmultiplexeur. La validation de ce circuit est ralis grce la patte AS du 68000. Chaque composant priphrique possde une entre de type CS (Chip Select, slection du circuit) qui le met en mode de fonctionnement. Ainsi, un seul priphrique est valid pour un change donn.

A23-A18 A17 A16 000000 1 1 000000 1 1 000000 1 0 000000 1 0 000000 0 1 000000 0 1 000000 0 0 000000 0 0 A15-A0 0000000000000000 FFFFFFFFFFFFFFFF 0000000000000000 FFFFFFFFFFFFFFFF 0000000000000000 FFFFFFFFFFFFFFFF 0000000000000000 FFFFFFFFFFFFFFFF CAN 0 0 1 1 1 1 1 1 E/S RAM ROM 1 1 1 1 1 1 0 1 1 0 1 1 1 0 1 1 0 1 1 1 0 1 1 0

Table II.1 : Exemple de dcodage d'adresses avec le 68000.

Dans l'exemple prsent, seuls les bits A17 et A16 sont pris en compte dans le dcodage d'adresses. Ainsi, les adresses 10 0000 et 00 0000 slectionnent le mme botier. Il s'agit d'adresses image. Un dcodage d'adresses est toujours un compromis entre la complexit du dcodage et le nombre d'adresses images.

P. Hoppenot (09/06/04)

Informatique Industrielle

8/16

Structure des systmes minimums de traitement de l'information

III. Echanges processeur priphrique On a vu qu'un change de donnes s'effectue en deux tapes : - une tape d'adressage, - une tape de transfert de donnes. Le processeur est matre de la phase d'adressage. Le transfert de donnes fait intervenir un priphrique. Deux modes d'change sont possibles. Dans le mode synchrone, est dfini une fois pour toute. Il doit donc tenir compte du priphrique le plus lent. Dans le mode asynchrone, le priphrique informe le processeur qu'il est prt recevoir des donnes ou qu'il a fini de les mettre. Ce mode est quant lui un peu plus difficile mettre en uvre. III.1. Echange synchrone Lors d'un change synchrone, le rythme de l'change est dfini l'avance, une fois pour toutes. Ainsi, une fois la phase d'adressage termine, la phase d'change de donne commence et s'arrte automatiquement au bout d'un temps fix. La Figure III.1 illustre l'change synchrone dans le cas du 8051. Une fois le signal ALE pass 0, la phase de donne commence (aprs tLLWL) et se termine au bout de tRLRH. Le signal RD indique qu'il s'agit d'une lecture. Puis un nouveau cycle peut commencer.

Figure III.1 : Echange de donnes synchrone - Exemple du 8051.

III.2. Echange asynchrone Lors d'un change asynchrone, la phase d'adressage est toujours pilote par le processeur. En revanche, la dure de la phase de transfert de donnes est indique par le priphrique l'aide d'un signal spcifique. La Figure III.2 illustre l'change asynchrone lors d'un transfert de donnes avec le 68000. Une fois la phase d'adressage termine, la phase de transfert de donnes commence. Le signal R/W indique qu'il s'agit d'une criture. Le processeur positionne donc le bus de donnes D15D0. Quand le priphrique a fini de lire les donnes, il l'indique au processeur l'aide du signal DTACK. Alors seulement le processeur enclenche la procdure de fin de transmission.

P. Hoppenot (09/06/04)

Informatique Industrielle

9/16

Structure des systmes minimums de traitement de l'information

Figure III.2 : Echange de donnes asynchrone- Exemple du 68000.

Que se passe-t-il si le priphrique choisi ne rpond pas ? Le processeur attend Et si le priphrique ne rpond toujours pas ? Un mcanisme est prvu pour dbloquer la situation : un niveau bas sur l'entre BERR du processeur initie un traitement particulier (interruption) permettant au processeur de ne pas rester bloquer (Figure III.3). C'est au concepteur du systme de prvoir la gnration de ce signal chaque change. Par exemple, au bout de 16 tops d'horloge, BERR peut tre plac l'tat bas interrompre le cycle d'attente.

Figure III.3 : Cycle d'erreur de bus sur le 68000 signal BERR.

IV. Gestion d'un systme minimum Une fois le systme dcrit, il faut pouvoir l'utiliser. On dispose de registres internes (IV.1) servant contrler le processeur. Il faut ensuite pouvoir accder aux donnes suivant divers modes d'adressage (IV.2). On peut alors crire des programmes (IV.3). La notion d'interruption permet la gestion d'vnements extrieurs (IV.4).

P. Hoppenot (09/06/04)

Informatique Industrielle

10/16

Structure des systmes minimums de traitement de l'information

IV.1. Registres internes Ils permettent de contrler le processeur. La Figure IV.1 donne les registres du 68000, la Figure IV.2 donne ceux du 8051 et la Figure IV.3 donne ceux du 80386.

Figure IV.1 : Registres internes du 68000.

Pour le 68000, on dispose d'un registre d'tat, de huit pointeurs d'adresses et de huit registres de donnes.

Figure IV.2 : Registres internes du 8051.

Le 8051 dispose de 128 octets de mmoire de donnes (00h-7Fh) et de registres spciaux (80hFFh). Parmi ceux-ci, on retrouve un registre d'tat, un pointeur d'adresses, deux registres de donnes On retrouve des registres quivalents sur les 80386 (Figure IV.3).

P. Hoppenot (09/06/04)

Informatique Industrielle

11/16

Structure des systmes minimums de traitement de l'information

Registres gnraux 31 16 15 8 7 0 AX AH | AL CX CH | CL DX DH | DL BX BH | BL SP BP SI DI

Registres d'tat et de contrle 31 16 15 0 EAX EBX ECX EDX ESP EBP ESI EDI

Figure IV.3 : Les registres du 80386.

Registres de segments 15 0 EIP EFLAGS ES CS SS DS FS GS

IP Flags

IV.2. Accs aux donnes Modes d'adressage Un processeur ne peut fonctionner qu'avec des donnes. Il faut pouvoir y accder. Diffrents modes sont disponibles, les principaux tant immdiat, direct et indirect. IV.2.1. Immdiat La donne est contenue dans l'instruction. Exemples : 8051 68000 IV.2.2. Direct La donne est contenue dans un registre. Exemples : 8051 68000 IV.2.3. Indirect L'adresse est contenue dans l'instruction. Exemples : 8051 68000 mov move.l @R0, A D0, (A2) mov move.b A, R0 D1, D3 mov move.w A, #2fh D0, #$4F52

IV.3. Notion de programme Pour traiter les donnes, on utilise des programmes. Il s'agit de suites d'instructions (IV.3.1), organises dans uns structure spcifique (IV.3.2). Le tout est cod (IV.3.3) et stock en mmoire de programme pour pouvoir tre excut (IV.3.4). IV.3.1. Instructions Une instruction permet de manipuler des donnes. Il en existe de plusieurs types : - Arithmtique (addition, soustraction) - Logique (et, ou) - Transfert - Sauts inconditionnels et conditionnels - Appel sous programme

P. Hoppenot (09/06/04)

Informatique Industrielle

12/16

Structure des systmes minimums de traitement de l'information

Une instruction comprend au moins : - Un nom ou mnmonique - Un ou plusieurs oprandes IV.3.2. Structure d'un programme Un programme est une suite d'instructions qui s'excutent les unes la suite des autres. Si on tombe sur une instruction de saut, c'est le code se trouvant l'adresse prcise qui s'excute. Un sous-programme est une suite d'instructions qui peut tre appele de plusieurs endroits dans le programme. Il dbute par une tiquette pour le nommer et une instruction spcifique qui permet un retour au niveau de l'appel. Pour cela, l'adresse de l'instruction d'appel doit avoir t stocke avant le dtournement du programme. La Figure IV.4 montre un exemple d'appel d'un sous-programme en 8051.

programme principal

2 1

sous programme

TOTO:

LCALL TOTO

4

phase 2

pile phase 1

+1 +1 SP PCH PCL ***

LCALL TOTO

phase 3

SP 3 -1 LCALL TOTO -1 RET

Figure IV.4 : Excution d'un sous-programme en 8051.

IV.3.3. Codage L'criture d'un programme se ralise en trois phases principales : - Edition du code Fichiers sources - Compilation, assemblage Fichiers objets - Edition des liens Fichier excutable, en langage machine IV.3.4. Excution d'un programme Le code machine doit tre transfr dans la mmoire de programme du systme. On obtient ainsi une liste d'octets dcrivant le fonctionnement du programme. Pour excuter le programme, le compteur de programme est initialis l'adresse du premier octet. Le code de l'instruction correspondante est charg dans l'unit centrale qui effectue l'action associe. Le compteur de programme pointe alors sur l'instruction suivante. Bien qu'une instruction (en assembleur) soit la plus petite entit accessible au programmeur, son excution est ralise en plusieurs phases. Pour le 486 et le Pentium, elles sont au nombre de 5 (Figure IV.5). Dans la phase PF, l'instruction est recherche dans la mmoire et transfre dans le processeur. Lors du premier dcodage (D1), l'instruction est examine pour dterminer le type d'action dclencher. La seconde phase de dcodage (D2) sert complter la premire par exemple en dterminant les oprandes associs l'instruction. La phase d'excution (EX) met en uvre l'instruction avec les accs mmoire ncessaires. La dernire phase met jour les registres internes du processeur. Un cycle machine est consomm par phase (parfois 2 dans D2 et EX).

P. Hoppenot (09/06/04)

Informatique Industrielle

13/16

Structure des systmes minimums de traitement de l'information

PF D1 D2 EX WB

PreFetch Decode 1 Decode 2 EXecute Write Back

Figure IV.5 : Phases d'excution d'une instruction.

La structure de pipeline part de cette dcomposition (Figure IV.5) : chaque cycle machine, toutes les phases dcrites ci-dessus sont actives. Cela revient traiter en permanence cinq instructions, chacune dans une phase diffrente (Figure IV.6). Une fois le mcanisme enclench, le rythme d'excution revient une instruction par cycle. Pgm PF D1 D2 EX WB Etat Cycle mov ax,1 mov ax,1 1 add ax,bx add ax,bx Mov ax,1 2 cmp ax,15 cmp ax,15 add ax,bx mov ax,1 3 int 123 int 123 cmp ax,15 add ax,bx mov ax,1 4 Shl ax,1 shl ax,1 int 123 cmp ax,15 add ax,bx mov ax,1 Fini 5 shl ax,1 int 123 cmp ax,15 Add ax,bx Fini 6 shl ax,1 int 123 cmp ax,15 Fini 7

Figure IV.6 : Excution d'un programme avec la structure de pipeline.

Le Pentium utilise mme deux pipelines en parallle (U et V). C'est l'architecture de pipeline superscalaire. On arrive thoriquement un doublement de la cadence d'instructions ralises. En ralit, deux instructions successives ne sont pas forcment indpendantes : la seconde peut devoir utiliser le rsultat de la premire. C'est dans la phase D1 que la dcision est prise d'une excution parallle quand elle est possible : la seconde instruction est traite par le pipeline V. Sinon, la seconde instruction suit la premire dans le pipeline U. Certains compilateurs pour Pentium sont dots d'une fonction d'optimisation qui organise le programme de telle faon que le plus d'instructions possibles soient traites en parallle. IV.4. Interruptions L'interruption est un mcanisme fondamental de tout processeur. Il permet de prendre en compte des vnements extrieurs au processeur et de leur associer un traitement spcifique. La Figure IV.7 donne le droulement d'une interruption. La squence classique de fonctionnement d'une interruption est la suivante : 0- Dtection de l'vnement dclencheur 1- Sauvegarde de l'adresse de retour 2- Droutement vers la routine d'interruption 3- Sauvegarde du contexte 4- Acquittement de l'interruption L'vnement est alors trait. 5- Restauration du contexte 6- Rcupration de l'adresse de retour 7- Retour au programme initial

P. Hoppenot (09/06/04)

Informatique Industrielle

14/16

Structure des systmes minimums de traitement de l'information

programme principal

MOV B,#35h interruption MOV A,# 22h 2

prog d'int

push PSW push ACC acquitement de l'interruption MOV A,# 7Fh

phase 3 (sauvegarde du contexte) phase 4

1 pile phase 3 phase 1 +1 +1 +1 +1 SP ACC PSW PCH PCL

***

instruction en cours

7 SP -1 -1 -1 -1 phase 5 phase 6 6 pop ACC pop PSW RETI phase 5 (restitution du contexte)

Figure IV.7 : Droulement d'une interruption.

Un point important n'a pas t abord : quelle est l'adresse de la routine d'interruption ? En effet, pour un sous-programme, l'instruction d'appel est suivie de l'adresse du sous-programme. Pour chaque source d'interruption, cette adresse est donne par le systme. Pour le 68000, une table des adresses d'interruption est disponible une adresse donne par le systme : VBR (Figure IV.8). Pour le 8051, une adresse fige est affecte chaque source d'interruption : - RESET : Saut l'adresse 0000h de la mmoire de programme - INT0 : Saut l'adresse 0003h de la mmoire de programme - TIMER0 :saut l'adresse 000Bh de la mmoire de programme - INT1 : Saut l'adresse 0013h de la mmoire de programme - TIMER1 :Saut l'adresse 001Bh de la mmoire de programme - TI ou RI : Saut l'adresse 0023h de la mmoire de programme

P. Hoppenot (09/06/04)

Informatique Industrielle

15/16

Structure des systmes minimums de traitement de l'information

Figure IV.8 : Listes des vecteurs d'interruption en 68000.

Pour qu'une interruption puisse tre prise en compte, elle doit tre valide. Au reset, elles sont toutes masques, ce qui permet de raliser des programmes simples sans tenir compte de ce mcanisme. Les interruptions sont ranges par ordre de priorit. Pour le 68000, on valide toutes les interruptions partir d'un niveau de priorit. Pour le 8051, chaque interruption est valide sparment grce au registre IE (Figure IV.9). Les cinq bits de poids faible de ce registre permettent d'autoriser les cinq sources d'interruption. Le bit EA est une validation gnrale qui doit aussi tre positionn pour que l'interruption puisse se drouler. Un bit de IE "1" valide l'interruption. Un bit "0" l'invalide. AFh AEh Adh ACh ABh AAh A9h A8h adresse EA ES ET1 EX1 ET0 EX0 A8h

Figure IV.9 : Registre IE de validation des interruptions en 8051.

P. Hoppenot (09/06/04)

Informatique Industrielle

16/16

S-ar putea să vă placă și

- Cours E Simulation D Un Pic Sous ProteusDocument4 paginiCours E Simulation D Un Pic Sous ProteusHerve DerouleauxÎncă nu există evaluări

- Devoir de Synthèse N°2 - SVT - 1ère AS (2011-2012) MR Korbi Wissem PDFDocument3 paginiDevoir de Synthèse N°2 - SVT - 1ère AS (2011-2012) MR Korbi Wissem PDFSalah DahouathiÎncă nu există evaluări

- 2012 Cours5 SerialDocument16 pagini2012 Cours5 SerialJerba Mainte Hichem MandarÎncă nu există evaluări

- Devoir de Synthèse N°2 - SVT - 1ère AS (2012-2013) Mme Manaa Hanen PDFDocument2 paginiDevoir de Synthèse N°2 - SVT - 1ère AS (2012-2013) Mme Manaa Hanen PDFSalah Dahouathi100% (1)

- Enonce MSISDocument46 paginiEnonce MSISSalah DahouathiÎncă nu există evaluări

- Devoir de Synthèse N°3 - SVT - 1ère AS (2012-2013) Mme BEN REJEB Manel PDFDocument3 paginiDevoir de Synthèse N°3 - SVT - 1ère AS (2012-2013) Mme BEN REJEB Manel PDFSalah Dahouathi100% (3)

- U C16 F877Document37 paginiU C16 F877Salah DahouathiÎncă nu există evaluări

- Microprocesseur 8088 8086Document86 paginiMicroprocesseur 8088 8086Afenspy Pipose100% (3)

- TP Pic 09Document30 paginiTP Pic 09Salah Dahouathi100% (1)

- C Hitech Sur Pic18Document0 paginiC Hitech Sur Pic18Salah DahouathiÎncă nu există evaluări

- C Hitech Sur Pic18Document0 paginiC Hitech Sur Pic18Salah DahouathiÎncă nu există evaluări

- OBJINTRYDocument1 paginăOBJINTRYSalah DahouathiÎncă nu există evaluări

- Exploitation Mplab FjobardDocument12 paginiExploitation Mplab FjobardSalah DahouathiÎncă nu există evaluări

- TP ProgC ClavierDocument13 paginiTP ProgC ClavierSalah DahouathiÎncă nu există evaluări

- Bus USBDocument10 paginiBus USBSalah Dahouathi100% (1)

- MPLAB Et Simulateur ISISDocument2 paginiMPLAB Et Simulateur ISISSalah DahouathiÎncă nu există evaluări

- Notice Prog C MPLAB & Cc5xDocument10 paginiNotice Prog C MPLAB & Cc5xkaimissÎncă nu există evaluări

- Liaison Serie PrincipeDocument11 paginiLiaison Serie PrincipeSalah DahouathiÎncă nu există evaluări

- Bts2008 5 CorrigeDocument20 paginiBts2008 5 CorrigeSalah DahouathiÎncă nu există evaluări

- Bus USBDocument10 paginiBus USBSalah Dahouathi100% (1)

- TPMP N1Document9 paginiTPMP N1Salah Dahouathi100% (2)

- Microprocess EursDocument23 paginiMicroprocess EursSalah DahouathiÎncă nu există evaluări

- MicroDocument7 paginiMicroSalah DahouathiÎncă nu există evaluări

- Micro Cours I2cDocument27 paginiMicro Cours I2cSalah DahouathiÎncă nu există evaluări

- INF445 C1 PIC Archi Systemes EmbarquesDocument43 paginiINF445 C1 PIC Archi Systemes EmbarquesSalah DahouathiÎncă nu există evaluări

- Pic 16F877Document39 paginiPic 16F877Oussama El B'charri100% (1)

- Intel 8086Document53 paginiIntel 8086maatoufi1667% (3)

- Systeme Temps 5 LCD ClavierDocument8 paginiSysteme Temps 5 LCD ClavierSalah DahouathiÎncă nu există evaluări

- PIC16F877 DocTechniqueDocument24 paginiPIC16F877 DocTechniqueSalah DahouathiÎncă nu există evaluări

- Microprocesseur 8088 8086Document86 paginiMicroprocesseur 8088 8086Afenspy Pipose100% (3)

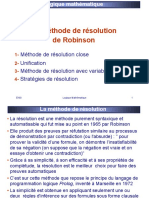

- Principe de Resolution de Robinson-CH4Document71 paginiPrincipe de Resolution de Robinson-CH4youssef ghaouiÎncă nu există evaluări

- Le Désir de Participation, David BerlinerDocument20 paginiLe Désir de Participation, David BerlinerIoana Miruna VoiculescuÎncă nu există evaluări

- Present TorsionDocument9 paginiPresent TorsionKhalid TamiÎncă nu există evaluări

- Serie 1Document1 paginăSerie 1zizikokoÎncă nu există evaluări

- Avant Le Chantier - Planete TPDocument1 paginăAvant Le Chantier - Planete TPndongmo aldoÎncă nu există evaluări

- Grammaire Negation InterrogationDocument3 paginiGrammaire Negation InterrogationZomba RinkÎncă nu există evaluări

- Serie 2-1Document5 paginiSerie 2-1bsalsabil592Încă nu există evaluări

- FourierDocument8 paginiFourierhenryÎncă nu există evaluări

- HDR LissorguesDocument216 paginiHDR Lissorguesruda64Încă nu există evaluări

- 2017 Nassori DouniaDocument159 pagini2017 Nassori DouniaLilia LinaÎncă nu există evaluări

- Mecanique de FluideDocument15 paginiMecanique de FluideJoshua Carpenter100% (1)

- Scenario Didactique ArticleDocument2 paginiScenario Didactique ArticleNicole's DiamondÎncă nu există evaluări

- Caslaru L Interlangue Des Apprenants Roumains de FleDocument262 paginiCaslaru L Interlangue Des Apprenants Roumains de FlerevedepierreÎncă nu există evaluări

- Éthique, Morale, Déontologie: René AuclairDocument6 paginiÉthique, Morale, Déontologie: René Auclairسيدامحمد خطري تام0% (1)

- Etude de Cas Sujet 1Document91 paginiEtude de Cas Sujet 1Salma GamÎncă nu există evaluări

- DEVOIR DE MATHS N°1 GSA11Nov23Document2 paginiDEVOIR DE MATHS N°1 GSA11Nov23dianechibidouxÎncă nu există evaluări

- Du Datamining À L'apprentissage StatistiqueDocument11 paginiDu Datamining À L'apprentissage StatistiqueGomiri AnonymeÎncă nu există evaluări

- LE TEST DE CATTELL Ou CULTURE FAIR INTELLIGENCE TEST - CFIT (4 Pages - 115 Ko) .Document4 paginiLE TEST DE CATTELL Ou CULTURE FAIR INTELLIGENCE TEST - CFIT (4 Pages - 115 Ko) .jo100% (1)