Documente Academic

Documente Profesional

Documente Cultură

SPI Interface

Încărcat de

Edwin Javier Garavito HernándezDescriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

SPI Interface

Încărcat de

Edwin Javier Garavito HernándezDrepturi de autor:

Formate disponibile

Serial Peripheral Interface (SPI) and Microwire/Plus implementation Using the SX Communications Controller

Application Note 20

November 2000

1.0

Introduction

2.0

SPI Description

Synchronous serial interfaces are widely used to provide economical board-level interface between different devices such as microcontrollers, DACs, ADCs and other. Although there is no single standard for the synchronous serial bus, there are industry accepted guidelines based on the two most popular implementations: SPI (a trademark of Motorola Semiconductor) and Microwire/Plus (a trademark of National Semiconductor). Many IC manufacturers produce components that are compatible with SPI and Microwire/Plus. This documentation describes the operation of SPI and details how it can be implemented on a SX communications controller using SPI Virtual PeripheralTM software modules.

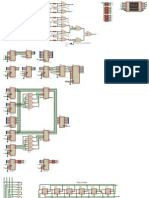

SPI uses a master-slave model and typically has three signal lines: data input line, data output line and clock line. Chip select signals from the master are used to address different slaves on the bus (Figure 2-1). The hardware realization of such an interface is a simple shift register. The data bits are shifted in/out MSB (most significant bit) first. Often the data is shifted simultaneously out from the output pin and into the input pin. SPI interface defines only the communication lines and the clock edge, other parameters vary for different devices. Clock frequencies happen to be anywhere from 100kHz to a few MHz and word lengths are from 8 to 16 or more bits.

SX MASTER

SCLK

MOSI MISO MISO MOSI SCLK MISO MOSI SCLK MISO MOSI SCLK

SS

SS

SS

SX SLAVE 0

SX SLAVE 1

SX SLAVE n

Figure 2-1. Master-Slave System Configuration 2.1 SIGNAL DESCRIPTIONS The four basic signals (MOSI, MISO, SCLK and SS) are described in the following paragraphs. 2.2 MASTER OUT, SLAVE IN The MOSI line is defined as an output line from the master device to an input into the slave devices. The MOSI line transfers data in one direction only, from the master to a slave. 2.3 MASTER IN, SLAVE OUT The MISO line is defined as an input line into the master device and as an output in a slave device. The MISO line transfers data in the opposite direction to the MOSI line, it transfers data from a slave device to the master. 2.4 SERIAL CLOCK The SCLK line is used to synchronize both data in and out of a device via the MOSI and MISO lines. The SCLK line is generated by the master device and thus is an input into all slave devices.

Ubicom and the Ubicom logo are trademarks of Ubicom, Inc. SPI is a trademark of Motorola.

All other trademarks mentioned in this document are property of their respective companies.

2000 Ubicom, Inc. All rights reserved.

-1-

www.ubicom.com

Serial Peripheral Interface (SPI) and Microwire/Plus implementation Using the SX Communications Controller

AN20

2.5 SLAVE SELECT The Slave Select (SS) lines are controlled by the master to select a slave device. The SS line must be low prior to data transactions and must stay low for the duration of the transaction. Each slave device requires its own SS input line from the master. The timing diagram of these lines can be seen in Figure 3-1.

3.0

SPI Operation

To initiate the data transfer between a master and slave device, the SS line must go low. This synchronizes the slave device with the master. Data can now be transferred between the master and slave device in one of two modes: either data is sampled on the rising edge of the clock or the falling edge of the clock. Figure 3-1 shows the data/clock timing diagram.

Rising Edge Mode SCLK SS

Sample Input

MSB

Bit 6

Bit 1

LSB

Figure 3-1. Data/Clock Timing Diagram In a slave device a logic low is received on the SS line and the clock input is at the SCLK pin. This synchronizes the slave with the master. Data is then received serially at the MOSI pin. During a write cycle, data is shifted out onto the MISO pin on clocks from the master device. Figure 3-2 illustrates the signal line interconnections.

MASTER

MISO 8-bit Shift Register MOSI SCLK SPI CLOCK Generator MISO MOSI SCLK 8-bit Shift Register

SLAVE

Figure 3-2. SPI Master Slave Interconnections

4.0

SX Implementation

On the SX device, the SPI master-slave interface can be implemented using two Virtual Peripheral software modules, one for the slave devices and one for the master device. An SPI demo program that will be described later in this document, has been developed to demonstrate the use of these Virtual Peripheral modules. Features: Full duplex, three-wire synchronous transfers Clock rate selectable up to 1.72MHz (2.5MHz possible with slight modifications) Master send frequency adjustable up to 1.72MHz Slave receive frequency adjustable up to 1.1MHz

Word length selectable anywhere from 1 16bits. (More than 16bits easily implemented if required) Clock polarity is configurable by using the appropriate command byte Arbitrary pins of the SX52BD and SX18/SX20/28AC devices may be assigned for the SPI interface lines Four I/O signal lines are required with any SPI communication: Master-Out-Slave-In Master-In-Slave_Out Serial Clock Slave Select MOSI signal line MISO signal line SCLK signal line SS signal line

2000 Ubicom, Inc. All rights reserved.

-2-

www.ubicom.com

AN20

Serial Peripheral Interface (SPI) and Microwire/Plus implementation Using the SX Communications Controller spim_port = rb

4.1 SPIM (SPI MASTER) VIRTUAL PERIPHERAL (SPIM.SRC) This Virtual Peripheral provides a simple and efficient way to send/receive data between SPI compatible slave devices. 4.2 SPIM CLOCK SPIM Clock rate can be selected starting from 1.72 MHz (max) which corresponds to a minimum clock period of 580ns. Clock period can be incremented with 160ns increments. The maximum clock rate of 2.5MHz can be achieved by removing part of the program, responsible for the programmable clock rate. The minimum clock rate is practically unlimited. Clock polarity is configurable by using the appropriate command byte. 4.3 SPIM I/O PINS SPIM controls the MOSI, MISO and SCLK lines. The user must assign the appropriate control for SS lines. Arbitrary pins of the SX device can be assigned to the signal lines used by SPIM. 4.4 SPIM DATA Word length can be set to anywhere from 1 to 16 bits. Longer word lengths can be easily implemented if needed. If necessary, the user may want to add Read/Write and handshaking signals. This can be easily implemented without affecting the core SPIM program. 4.5 USING SPIM To initialize SPIM, the user program must perform the following steps: Disable the interrupts Initialize SX I/O ports (calling SPIM_INIT) Place the outgoing data into the I/O buffer Set SS signal low and call SPIM_EXECUTE Since SPIM is not using any interrupts, it will transfer the data and return control to user program. The two-byte send/receive buffer is allocated in memory as SPIM_LSB and SPIM_MSB. Data is shifted starting from the most significant bit (MSB). In case of less than 16-bit long data words, the SPIM will automatically align the MSB of the word to the MSB of the buffer before shifting. No user intervention is required. It is important to note that the contents of SPIM_LSB and SPIM_MSB are not preserved during the driver operation since the bits are always shifted in. 4.6 SPIM CONTROL, STATUS AND I/O DATA REGISTERS SPIM_RATE. This byte defines the clock rate. When set to 1, the maximum clock rate is 1.72 MHz (580ns period). The actual clock period can be calculated as: Clock Period = 420 ns + (160 ns x SPIM_RATE) The one exception to the rule is if SPIM_RATE is zero, in this case the minimum clock rate of 24.17kHz (41.38s Period) is selected. SPIM_PORT. This register must be configured to point to the SX Ports (A, B, C, D, or E) which will generate the SPI Clock signal. For instance:

SPIM_PORTA_MASK, SPIM_PORTB_MASK,SPIM_PORTC_MASK.These bytes are the images of SX I/O port direction registers. The values written into these registers correspond to the ports direction registers. A value of 1 defines the pin as an input while a value of 0 defines the pin as an output. For the master device, all the signal lines must be defined as outputs except the MISO line. SPIM_CLK_MASK defines the SPI Clock pin. The pin is defined by setting the corresponding bit of SPIM_CLK_MASK. For instance, to define RC1 as the SPI clock input pin (SCLK):

spim_portc_mask spim_port spim_clk_mask = = = $fd rc $02

SPIM_CMD This register is defined as the command and configuration byte. This byte defines: SPI Clock polarity Data direction (Read/Write) Number of bits to send/receive. SPIM supports 4 commands, specified by the 4 MSB bits of the SPIM_CMD byte. They are defined as:

4 MSB Bits Command 0011 GET WORD in MASTER FAST mode, define FALLING edge; 0111 GET WORD in MASTER FAST mode, define RISING edge; 1011 SEND WORD in MASTER FAST mode, define FALLING edge; 1111 SEND WORD in MASTER FAST mode, define RISING edge.

Practically there is no difference between the GET and SEND commands. When the I/O buffer is shifted out, the input data is always shifted in. The different commands are provided for user convenience and to avoid confusion. The four LSB bits of the command byte define the word length.

4 LSB Bits Command

0000 0001 .. 1111

Sets the length to 16 bits Sets the length to 1 bit . Sets the length to 15 bits

The SPIM_CMD byte also serves as a ready flag. SPIM will clear this byte upon the completion of data transfer. The SPIM_STATUS byte provides the error status information. It has 1 error flag. Bit 4 is set to 1 when the SPIS_CMD byte contains an unsupported command.

2000 Ubicom, Inc. All rights reserved.

-3-

www.ubicom.com

Serial Peripheral Interface (SPI) and Microwire/Plus implementation Using the SX Communications Controller

AN20

4.7 SPIM ENTRY POINTS SPIM_INIT. Initialization subroutine. It provides appropriate configuration for the SX I/O pins. SPIM_EXECUTE. This is the actual Virtual Peripheral entry point, which may be called either from the interrupt service routine or from MAIN program. SPIM_SS_SET. User defined subroutine to set active level on SS pin. SPIM_SS_RESET. User defined subroutine to set passive level on SS pin. In the case of multiple devices on the SPI bus, the user must provide appropriate control over the SS signals. SPIM_ORG. This is the base address of the SPIM Virtual Peripheral. Typically it will be the next program memory location, after the user program. 4.8 USING SPIM FROM THE USER PROGRAM 1. Make sure that no interrupt is allowed during execution of SPIM. 2. Verify that the execution parameters are configured properly: SPIM_RATE SPIM_PORT_A_MASK SPIM_PORT_B_MASK SPIM_PORT_C_MASK SPIM_PORT SPIM_CLK_MASK SPIM_CMD 3. Configure I/O ports by calling SPIM_INIT. 4. Verify that SPIM is ready for execution by testing the SPIM_CMD byte. 5. Place the outgoing data into SPIM_LSB and SPIM_MSB. 6. Call SPIM_EXECUTE from the interrupt. 7. Test SPIM_CMD for completion and SPIM_STATUS for errors. 8. Unload the data from SPIM_LSB and SPIM_MSB. SPIM is now ready for reuse. Repeat from step 4.

maximum receive speed of SPIS is 1.1MHz. Receiving data at 1.1MHz is the very maximum speed because of this interrupt latency, even at this speed SPIS only just has enough time (20ns) to put data onto the MISO line before the next rising edge of the clock. Clock polarity is configurable by using the appropriate command byte. 5.2 SPIS DATA Word length can be set to anywhere from 1 to 16 bits. Longer word lengths could be easily implemented if needed. SPIS does not make any differentiation between read and write cycles. The data is clocked in and out simultaneously. 5.3 SPIS I/O PINS SPIS makes use of the Wake-UP interrupt from the SS signal. Therefore, the SS signal must be assigned to one of the Port B pins. Other signals may use any other free pins. 5.4 USING SPIS To initialize SPIS, the user program must disable the RTCC interrupt and enable the appropriate edge (wakeup interrupt from the SS pin). SPIS will then wait for the interrupt from the SS input. When the interrupt occurs, SPIS will start execution of the send/receive loop, waiting for SPI clock signal and start processing the incoming and outgoing data lines. After the predefined number of clock pulses, SPIS will finish the communication cycle and exit the interrupt routine. In order to prevent locking of the driver in case of a communication error, SPIS uses it's internal SPIS_WATCHDOG counter, which would expire if SPIS has not received the clock pulse for too long, the data transfer will be aborted. The two-byte (16 bits) send/receive buffer is allocated in memory as SPIS_LSB and SPIS_MSB. Data is shifted starting from the most significant bit. In case of less than 16-bit long data word, the SPIS will automatically align the MSB of the word to the MSB of the buffer before shifting (no user intervention is required). The contents of SPIS_LSB and SPIS_MSB are not preserved during the driver operation since the bits are always shifted in.

5.0 SPIS (SPI Slave) Virtual Peripheral Description (SPIS.SRC)

This Virtual Peripheral provides a simple and efficient way to send/get one word of data to/from a SPI compatible MASTER device. 5.1 SPIS CLOCK SPIS is developed to work with relatively fast SPI devices. It occupies the CPU during the entire data transfer. Maximum clock rate is 1.1 MHz (900 ns clock period). The clock rate may vary during data transfer cycle. If the watchdog timer is enabled, this will limit the minimum clock rate. One very important aspect to note when using SPIS is that on a clock pulse a wake-up interrupt is generated. Now, before SPIS can react to this clock pulse there is a 220ns delay, including ISR, which is why the

2000 Ubicom, Inc. All rights reserved. -4www.ubicom.com

AN20

Serial Peripheral Interface (SPI) and Microwire/Plus implementation Using the SX Communications Controller

5.5 SPIS CONTROL, STATUS AND I/O DATA REGISTERS SPIS_WATCHDOG. This byte defines the timeout period for the SPI slave. If SPIS will not receive the clock signal within this waiting period, the communication will be aborted and the error flag will be set. The actual timeout can be calculated as 160ns multiplied by SPIS_WATCHDOG. SPIS_PORTA_MASK,SPIS_PORTB_MASK, SPIS_PORTC_MASK. These bytes are the images of SX I/O ports direction registers. They are written to corresponding ports direction registers during SPIS initialization. SPIS_WKUP_MASK - SPIS writes SPIS_WKUP_MASK into Port B Wakeup Enable register. SPIS_CMD - Command and configuration byte. This byte defines: SPI Clock polarity direction (Read/Write) number of bits to send/receive SPIS supports 4 commands, specified by the 4 MSB bits of the SPIS_CMD byte:

4 MSB Bits Command 0001 GET BYTE in SLAVE mode, define FALLING edge 0101 GET BYTE in SLAVE mode, define RISING edge 1001 SEND BYTE in SLAVE mode, define FALLING edge 1101 SEND BYTE in SLAVE mode, define RISING edge

SPIS_EXECUTE. This is the actual VP entry point, which is normally called from the interrupt service routine. SPIS_ORG. This is the base address of SPIM VP. Typically it will be next ROM location, after the user program. 5.7 USING SPIS FROM THE USER PROGRAM 1. Verify that the execution parameters are configured properly: SPIS_WATCHDOG SPIS_PORT_A_MASK SPIS_PORT_B_MASK SPIS_PORT_C_MASK SPIS_WKUP_MASK SPIS_CMD 2. Call SPIS_INIT 3. Verify that SPIS is ready for execution by testing the SPIS_CMD byte. 4. Place the outgoing data into SPIS_LSB and SPIS_MSB 5. Disable the RTCC interrupt and enable the SS interrupt from Port B. 6. Call SPIS_EXECUTE from the interrupt. 7. Test SPIS_CMD for completion and SPIS_STATUS for errors. 8. Unload the data from SPIS_LSB and SPIS_MSB SPIS is now ready for reuse. Repeat from step 3.

The contents of SPIS_LSB and SPIS_MSB are not preserved during the r operation since the bits are always shifted in even if they don't make any sense. The four LSB bits of the command byte define the word length. 4 LSB Bits 0000 0001 .. 1111

Command

Sets the length to 16 bits Sets the length to 1 bit ............. Sets the length to 15 bits

The SPIS_CMD byte also serves as a ready flag. SPIS will clear this byte upon the success of data transfer. SPIS_STATUS. Provides the error status information to the user program. It has 2 error flags: bit 4 - set to 1 when the SPIS_CMD byte contains an unsupported command bit 7 - set to 1 when the data transfer was not completed successfully 5.6 SPIS ENTRY POINTS SPIS_INIT. Initialization subroutine, it provides appropriate configuration for SX I/O pins.

2000 Ubicom, Inc. All rights reserved.

-5-

www.ubicom.com

Serial Peripheral Interface (SPI) and Microwire/Plus implementation Using the SX Communications Controller

AN20

6.0

Demo Description

SPI DEMO provides an example of data transfer between two SX devices through the SPI data bus. SPI DEMO consists of two programs - SPI DEMOM.SRC and SPI DEMOS.SRC, which correspond to the SPI Master and SPI Slave sides accordingly. These demo files have within them the two VPs described above SPI Master and SPI Slave. There are 4 signal lines that connect the Master to the Slave: Master-Out-Slave-In Master-In-Slave-Out Serial Clock Slave Select MOSI signal line MISO signal line SCLK signal line SS signal line

The Slave Select (SS) Line from Master to Slave signals the latter to start sending/receiving data. The word length is set to 16 bits in this demo (VP permits 1 to 16 bits). SPI virtual peripherals perform shifting in and out at the same time, as most hardware SPI implementations do. The demo works as follows:

Assuming that Slave has been initialized prior to Master, the Master sends the predefined word 256 times.The predefined words are in registers SPI_DEMO_DATA_MSB and SPIM_DEMO_DATA_LSB. The Slave SX is configured to perform the loop-back function, that is, every time Slave sends to the Master whatever it has received from the Master during the previous transmission. After the initial 256 transmissions Master switches into the loop-back mode. The data transfer of the predefined word can be easily observed with the help of an oscilloscope. SPI clock period for this demo is 900 ns - maximum clock rate supported by the SPIS (SPI Slave VP). Data transfer from the Master side is triggered by RTCC interrupt with a period of 25.6 microseconds. To run the SPI demo program connect two SX28AC devices in a master slave configuration as shown in figure 6-1, do not forget to connect a common ground. By connecting an oscilloscope to the signal lines it is possible to see the data being sent back and forth between the master and slave devices on each clock pulse.

SX28AC MASTER

RB0 RB1 RB2 RB3 VSS SCLK MOSI MISO SS

SX28AC SLAVE

RB0 RB2 RB1 RB3 VSS

Figure 6-1. SPI Master-Slave Demo Program Configuration

2000 Ubicom, Inc. All rights reserved.

-6-

www.ubicom.com

AN20

Serial Peripheral Interface (SPI) and Microwire/Plus implementation Using the SX Communications Controller

Once you are familiar with the SPI demo, the master and slave VPs can be configured for your exact needs by writing to the appropriate registers. In Figure 6-2 a scope

capture of the SS and SCLK was taken to show how the SS line is used to synchronize the clock and data.

Clock Signal

SS Line on Slave device

Figure 6-2. Clock and SS line on slave device 6.1 INTERFACE CONSIDERATIONS To protect the integrity of data exchange when using synchronous serial communication, two aspects must be considered: Serial Data Exchange Timing Fan-out/fan-in requirements Theoretically, infinite devices can access the same interface and be uniquely enabled sequentially in time. In practice, however the actual number of devices that can access the same serial interface depends on the following: System data transfer rate, system supply requirements, capacitive loading, and the fan-in requirements of the logic families or discrete devices to be interfaced. Lastly, it is important to take into consideration the minimum response time of the slave to a clock pulse. Using the current SPI slave Virtual PeripheralTM architecture there is an inherent response delay of 220ns which limits the maximum clock speed to which the slave can work with. This could be reduced by changing the SPIS architecture, for instance, polling the SCLK instead of using an interrupt which adds a 100ns delay. For optimal use of resources of the SX it is advised to use these Virtual PeripheralTM modules as a guide to possible implementations but modify them to meet your exact application requirements.

2000 Ubicom, Inc. All rights reserved.

-7-

www.ubicom.com

Serial Peripheral Interface (SPI) and Microwire/Plus implementation Using the SX Communications Controller

AN20

Lit#: AN20-03

Sales and Tech Support Contact Information

For the latest contact and support information on SX devices, please visit the Ubicom website at www.ubicom.com. The site contains technical literature, local sales contacts, tech support and many other features. 1330 Charleston Road Mountain View, CA 94043 Tel.: (650) 210-1500 Fax: (650) 210-8715 E-Mail: sales@ubicom.com Web Site: www.ubicom.com

2000 Ubicom, Inc. All rights reserved. -8www.ubicom.com

S-ar putea să vă placă și

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Liquiphant M Density - E+H - DIA-SPDocument4 paginiLiquiphant M Density - E+H - DIA-SPEdwin Javier Garavito HernándezÎncă nu există evaluări

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5795)

- ADM Quick Start GuideDocument8 paginiADM Quick Start GuideEdwin Javier Garavito HernándezÎncă nu există evaluări

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Special Tool ListDocument4 paginiSpecial Tool ListEdwin Javier Garavito Hernández100% (1)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Specs BicicletasDocument14 paginiSpecs BicicletasEdwin Javier Garavito HernándezÎncă nu există evaluări

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- КПП MYY5T АНГЛDocument31 paginiКПП MYY5T АНГЛEdwin Javier Garavito Hernández100% (2)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (74)

- MC Feed-Through Packers: Remotely Isolate Zones in Marginal or Mature AssetsDocument2 paginiMC Feed-Through Packers: Remotely Isolate Zones in Marginal or Mature AssetsEdwin Javier Garavito HernándezÎncă nu există evaluări

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- E-Pak Feed-Thru Packer Esp4596: "Custom Solutions For Your Application"Document1 paginăE-Pak Feed-Thru Packer Esp4596: "Custom Solutions For Your Application"Edwin Javier Garavito HernándezÎncă nu există evaluări

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- Go To Download Full Manual: Cummins Engine Signature ISX and QSX15 Workshop Service Repair Manual PDF DownloadDocument1 paginăGo To Download Full Manual: Cummins Engine Signature ISX and QSX15 Workshop Service Repair Manual PDF DownloadEdwin Javier Garavito HernándezÎncă nu există evaluări

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Isx15overhaulkit Content BypartnumberDocument2 paginiIsx15overhaulkit Content BypartnumberEdwin Javier Garavito Hernández100% (1)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (400)

- Contact: Downhole Completion Products: Seal Bore/Profile Connection MaterialDocument6 paginiContact: Downhole Completion Products: Seal Bore/Profile Connection MaterialEdwin Javier Garavito HernándezÎncă nu există evaluări

- Datasheet Nucleo E EA77Document2 paginiDatasheet Nucleo E EA77Edwin Javier Garavito HernándezÎncă nu există evaluări

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (345)

- Hino Workshop Manual J08cDocument1 paginăHino Workshop Manual J08cEdwin Javier Garavito Hernández0% (1)

- J55 L80 N80Q P110 Pup Joints: SpecificationDocument1 paginăJ55 L80 N80Q P110 Pup Joints: SpecificationEdwin Javier Garavito HernándezÎncă nu există evaluări

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- 2013 Volvo Maintenance ScheduleDocument3 pagini2013 Volvo Maintenance ScheduleEdwin Javier Garavito Hernández100% (2)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- A Low Cost Automation System Based On IoTDocument6 paginiA Low Cost Automation System Based On IoTEdwin Javier Garavito HernándezÎncă nu există evaluări

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- ' Abrir Puerto Mientras Se Ejecute La AplicaciónDocument4 pagini' Abrir Puerto Mientras Se Ejecute La AplicaciónEdwin Javier Garavito HernándezÎncă nu există evaluări

- NVME M.2 Disk CompatibilityDocument3 paginiNVME M.2 Disk CompatibilityEdwin Javier Garavito HernándezÎncă nu există evaluări

- Datasheet Nucleo E EA77Document2 paginiDatasheet Nucleo E EA77Edwin Javier Garavito HernándezÎncă nu există evaluări

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- 10 STATCOM Vs SVC PDFDocument27 pagini10 STATCOM Vs SVC PDFshiva sai donthulaÎncă nu există evaluări

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- 4PMMNL Abridged User GuideDocument4 pagini4PMMNL Abridged User Guidew_muangphuanÎncă nu există evaluări

- Soln To Some ProblemsDocument2 paginiSoln To Some ProblemsEdwin Quinlat DevizaÎncă nu există evaluări

- Overvoltage DefinitionsDocument17 paginiOvervoltage DefinitionsaocalayÎncă nu există evaluări

- Lcd2s SPI ExamplesDocument2 paginiLcd2s SPI ExamplesJarfoÎncă nu există evaluări

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- Geometry Dependence: Chapter 2 MOS Transistor TheoryDocument1 paginăGeometry Dependence: Chapter 2 MOS Transistor TheoryCarlos SaavedraÎncă nu există evaluări

- Ic FabricationDocument31 paginiIc FabricationMukesh Nexus100% (1)

- Article Labview and WaspmoteDocument3 paginiArticle Labview and WaspmoteIonel Valeriu GrozescuÎncă nu există evaluări

- VX 427 4 5 VX 417 4 5Document30 paginiVX 427 4 5 VX 417 4 5FalcoÎncă nu există evaluări

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- 1 UL 864 Compliance: Network Communications Module NCM-W/F Product Installation DocumentDocument7 pagini1 UL 864 Compliance: Network Communications Module NCM-W/F Product Installation DocumentRicardo StimpelÎncă nu există evaluări

- Memory Management in OSDocument76 paginiMemory Management in OSratanÎncă nu există evaluări

- Mvs CommandsDocument2 paginiMvs CommandsrickparkinsonÎncă nu există evaluări

- Diode As A Switch WorkingDocument4 paginiDiode As A Switch Workingbantu1210% (1)

- Dell 2209WA Service Manual Rev 1.0Document85 paginiDell 2209WA Service Manual Rev 1.01133523568585Încă nu există evaluări

- © Sal La Duca,, 908-454-3965Document4 pagini© Sal La Duca,, 908-454-3965xman17Încă nu există evaluări

- Co Unit 1Document146 paginiCo Unit 1Adivardhan Akash MaheshwariÎncă nu există evaluări

- BD 2Document1 paginăBD 2Luis Arturo Leiva Monjaras100% (1)

- The Computer System UnitDocument2 paginiThe Computer System UnitRichard Balicat Jr.Încă nu există evaluări

- Step Response Unit ResponseDocument6 paginiStep Response Unit ResponsetirsollantadaÎncă nu există evaluări

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- Course Title: Power Electronics Course Code: ELEC304 Credit Units: 5 Level: UGDocument3 paginiCourse Title: Power Electronics Course Code: ELEC304 Credit Units: 5 Level: UGShivansh BhardwajÎncă nu există evaluări

- Diagramas Esquematicos TV LED LGDocument49 paginiDiagramas Esquematicos TV LED LGLuis Alonso Rosero Velez100% (1)

- Linear Circult Analysis Lab-Manual - 16jun 2016 PDFDocument71 paginiLinear Circult Analysis Lab-Manual - 16jun 2016 PDFHaris -Încă nu există evaluări

- EN-Sharys IP-Catalogue 2016 PDFDocument4 paginiEN-Sharys IP-Catalogue 2016 PDFThien BinhÎncă nu există evaluări

- Lc50le650u FinalDocument90 paginiLc50le650u FinalLuis Hum0% (1)

- SAP-1 Simple As Possible Computer Schematic Diagram - Updated DesignDocument1 paginăSAP-1 Simple As Possible Computer Schematic Diagram - Updated Designpong74lsÎncă nu există evaluări

- Technical Manual: Acoustic & Electrical Specifications: System ComponentsDocument2 paginiTechnical Manual: Acoustic & Electrical Specifications: System ComponentsGINO GELSIÎncă nu există evaluări

- 82-P9008-Rev2-EN - 02.11.2015Document174 pagini82-P9008-Rev2-EN - 02.11.2015MarcielArturÎncă nu există evaluări

- Ponciango AmpDocument10 paginiPonciango AmpMond Timpog LagmanÎncă nu există evaluări

- Agilent Programing DocDocument454 paginiAgilent Programing DocahmadrzrÎncă nu există evaluări

- 1040 L Scheme EceDocument201 pagini1040 L Scheme EceEng Abdulkadir MahamedÎncă nu există evaluări

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102De la EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Evaluare: 5 din 5 stele5/5 (2)