Documente Academic

Documente Profesional

Documente Cultură

VLSI QA's

Încărcat de

hvrkDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

VLSI QA's

Încărcat de

hvrkDrepturi de autor:

Formate disponibile

VLSI Design (2mark questions and answers)

Unit I

1. Define Threshold voltage The threshold voltage VT for a MOS transistor can be defined as the voltage between the gate and the source terminals below which the drain to source current effectively dro s to !ero" Define body effect or substrate bias effect. The threshold voltage VT is not a constant with res ect to the voltage difference between the substrate and the source of the MOS transistor" This effect is called the body effect or substrate bias effect" 2. Give the different modes of o eration of !"S transistor #ut off mode $inear mode Saturation mode #. $hat are the different regions of o eration of a !"S transistor% a. &ut off region %ere the current flow is essentially !ero (accumulation mode) b. Linear region &t is also called weak inversion region where the drain current is de endent on the gate and the drain voltage w" r" to the substrate" c. Saturation region #hannel is strongly inverted and the drain current flow is ideally inde endent of the drain'source voltage (strong'inversion region)" '. Give the e( ressions for drain current for different modes of o eration of !"S transistor. a" #ut off region &( )* b" $inear region &( ) kn +(V,S - VT) V(S - V(S2.2/ c" Saturation region &( ) (kn .2) (V,S - VT)2

). *lot the current+voltage characteristics of a n!"S transistor.

,. Define accumulation mode. The initial distribution of mobile ositive holes in a ty e silicon substrate of a mos transistor for a voltage much less than the threshold voltage -. $hat are the secondary effects of !"S transistor% a" Threshold voltage variations b" Source to drain resistance c" Variation in &'V characteristics d" Subthreshold conduction e" #MOS latchu .. $hat is &!"S latchu % /o0 it can be revented% The MOS technology contains a number of intrinsic bi olar transistors"These are es ecially troublesome in #MOS rocesses0 where the combination of wells and subtrates results in the formation of 'n' 'n structures" Triggering these thyristor like devices leads to a shorting of V(( 1 VSS lines0 usually resulting in a destruction of the chi " The remedies for the latch+u roblem include1

(i) an increase in substrate do ing levels with a consequent dro in the value of 2 subs" (ii) reducing 2nwell by control of fabrication arameters and ensuring a low contact resistance to V((" (iii) by introducing guard rings" 2. $hat are the different fabrication rocesses available to &!"S technology% a" 'well rocess b" n'well rocess c" Twin'tub rocess d" Silicon On &nsulator (SO&) . Silicon On Sa hire (SOS) rocess 13. $hat is intrinsic and e(trinsic semiconductor% The ure silicon is known as &ntrinsic Semiconductor" 3hen im urity is added with ure silicon0 it is electrical ro erties are varied" This is known as 45trinsic semiconductor" 12. $hat are the ste s involved in manufacturing of I&% 66 i" wafer re aration ii" 4 ita5ial growth iii" O5idation iv" hoto lithogra hy v" (iffusion and &on &m lantation vi" &solation vii" Metalli!ation 1#. $hat is meant by 4 e ita(y 5 % 4 ita5y means arranging atoms in single crystal fashion u on a single crystal substrate" 1'. 0hat are the rocess involved in hoto lithogra hy% i" making rocess ii" hoto etching rocess these are im ortant rocess involved in hotolithogra hy" 1). 0hat is the ur ose of mas6ing in fabrication of I&% Masking is used to identify the lace in which &on &m lantion should not be occurred"

1,. 0hat are the materials used for mas6ing% 7hoto resist0 Sio20 Si80 oly Silicon" 1-.0hat are the ty es of etching % 3et etching and dry etching are the ty es of hoto etching" 1.. 0hat is diffusion rocess % 0hat are do ing im urities% (iffusion is a rocess in which im urities are diffused in to the silicon chi at 9****# tem erature" :2O; and 72O< are used as im urities" 12. 0hat is isolation% &t is a rocess used to rovide electrical isolation between different com onents and interconnections" 23. 0hat are the various &!"S technologies% Various #MOS technologies are i" n'well rocess or n'tub rocess ii" 'well rocess or 'tub rocess iii" twin'tub rocess iv" Silicon on &nsulator (SO&) rocess" 21. 0hat is channel sto im lantation% &n n'well fabrication0 n'well is rotected with resist material" :ecause0 it should not be affected by :oron im lantation" The boron is im lane5ce t n'well" &t is done using hotoresist mask" This ty e of im lantation is known as channel im lantation" 22. 0hat is L"&S% $O#OS means $ocal O5idation Of Silicon" This is one ty e of o5ide construction" 2#. 0hat is S$7!I% S3=M& means Side 3all Masked &solation" &t is used to reduce bird>s beak effect" 2'. 0hat is LDD% $(( means $ight (o ed (rain Structures" &t is used for im lantation of n' in n'well rocess"

2). 0hat is t0in+tub rocess% $hy it is called so% Twin'tub rocess is one of the #MOS technology" There are two wells are available in this rocess" The other name of well is tub" So0 because of these two tubs0 this rocess is known as twin'tub rocess"

Unit II

1. Dra0 the circuit of a n!"S inverter.

" 2. Give the e( ression for ull+u to ull+do0n ratio 8 Zpu/Zpd9 for an n!"S inverter driven by another n!"S inverter.

" "

#. Dra0 the circuit of a &!"S inverter.

'. $hat are the advantages of &!"S inverter over the other inverter configurations% a" The steady state ower dissi ation of the #MOS inverter circuit is negligible" b. The voltage transfer characteristic (VT#) e5hibits a full out ut voltage wing between *V and V((" This results in high noise margin" ). $hat are stic6 diagrams% Stick diagrams are used to convey layer information through the use of a color code" = stick diagram is a cartoon of a chi layout" They are not e5act models of layout" The stick diagram re resents the rectangles with lines which re resent wires and com onent symbols" ,. $hat are the different color codes used for single oly silicon n!"S technology% n'diffusion (n'diff") and other thino5ide regions 'green 7olysilicon ( oly") ' red Metal 9 (metal) ' blue &m lant ' yellow #ontacts ' black or brown (buried) -. $hat are design rules% (esign rules are the communication link between the designer s ecifying requirements and the fabricator who materiali!es them" (esign rules are used to roduce workable mask layouts from which the various layers in silicon will be formed or atterned"

.. Define a su erbuffer. = su erbuffer is a symmetric inverting or noninverting gate that can su ly or remove large currents and switch large ca acitive loads faster than a standard inverter" 2.$hat are :i&!"S Gates% 3hen bi olar and MOS technology are merged0 the resulting circuits are referred to as bi#MOS circuits" %igh gain vertical n n transistors with their collectors tied to the ositive rail0 and medium'gain lateral n n transistors are both com atible with conventional #MOS rocessing" :i#MOS gates can be used to im rove the erformance of line drivers and sense am lifiers" 13. 0hat is the s ecial feature of t0in+tub rocess% &n twin'tub rocess0 threshold voltage0 body effect n and inde endently o timi!ed" 11. 0hat are the advantage of t0in+tub rocess% =dvantages of twin'tub rocess are i" Se arate o timi!ed wells are available" ii" :alance erformance is obtained for n and devices are

transistors"

12. 0hat is S"I% $hat is the material used as Insulator% SO& means Silicon'on'&nsulator" &n this rocess0 Sa hire or SiO2 is used as insulator" 1#. 0hat are the various etching rocess used in S"I rocess% Various etching rocess used in SO& are i" &sotro ic etching rocess" ii" =nisotro ic etching rocess" iii" 7referential etching rocess" 1'. 0hat are the advantages and disadvantages 3f S"I rocess% 7dvantages of S"I rocess i" There is no well formation in this rocess" ii" There is no field'&nversion roblem" iii" There is no body effect roblem"

Disadvantages of S"I rocess i" &t is very difficult to rotect in uts in this rocess" ii" (evice gain is low" iii" The cou ling ca acitance between wires always e5ist" 1). 0hat are the ossible modes in n!"S enhancement transistor% i" accumulation mode ii" de letion mode ii" &nversion mode 1,. In saturation region; 0hat are the factors that affect Ids% i" distancebetween source and drain" ii" channel width iii"Threshold oltage iv"thickness of o5ide layer v" dielectric constant of gate insulator vi" #arrier mobility" 1-. $hat is :ody effect% The threshold voltage VT is not a constant w" r" to the voltage difference between the substrate and the source of MOS transistor" This effect is called substrate'bias effect or body effect" 1..$hat is &hannel+length modulation% The current between drain and source terminals is constant and inde endent of the a by the a lied voltage over the terminals" This is not entirely correct" The effective length of the conductive channel is actually modulated lied V(S0 increasing V(S causes the de letion region at the drain ?unction to grow0 reducing the length of the effective channel" 12.Define Threshold voltage in &!"S% The Threshold voltage0 VT for a MOS transistor can be defined as the voltage a lied between the gate and the source of the MOS transistor below which the drain to source current0 &(S effectively dro s to !ero"

23. Define <ise time 2ise time0 tr is the time taken for a waveform to rise from 9*@ to A*@ of its steady'state value" 21. Define =all time =all time0 tf is the time taken for a waveform to fall from A*@ to 9*@ of its steady'state value" 22. Define Delay time (elay time0 td is the time difference between in ut transition (<*@) and the <*@ out ut level" This is the time taken for a logic transition to ass from in ut to out ut" 2#. $hat are t0o com onents of *o0er dissi ation. There are two com onents that establish the amount of ower dissi ated in a #MOS circuit" These areB i) Static dissi ation due to leakage current or other current drawn continuously from the ower su ly" ii) (ynamic dissi ation due to ' Switching transient current ' #harging and discharging of load ca acitances" 2'. Give some of the im ortant &7D tools. Some of the im ortant #=( tools areB i) $ayout editors ii) (esign 2ule checkers ((2#) iii) #ircuit e5traction

2).$hat is Verilog% Verilog is a general ur ose hardware descri tor language" &t is similar in synta5 to the # rogramming language" &t can be used to model a digital system at many levels of abstraction ranging from the algorithmic level to the switch level"

Unit III

1. $hat are the static ro erties of com lementary &!"S Gates% a" They e5hibit rails'to'rail swing with VO% ) V(( and VO$ ) ,8(" b" The circuits have no static ower dissi ation0 since the circuits are designed such that the ull'down and ull'u networks are mutually e5clusive" c" The analysis of the (# voltage transfer characteristics and the noise margins is more com licated than for the inverter0 as these arameters de end u on the data in ut atterns a lied to the gate" 2. Dra0 the e>uivalent <& model for a t0o+in ut ?7?D gate.

#. $hat are the ma@or limitations associated 0ith com lementary &!"S gate% a" The number of transistors required to im lement an 8 fan'in gate is 28" This can result in a significantly large im lementation area" b" The ro agation delay of a com lementary #MOS gate deteriorates ra idly as a function of the fan'in" '. $hat is meant by ratioed logic% &n ratioed logic0 a gate consists of an nMOS ull'down network that

reali!es the logic function and a sim le load device0 which re lace the entire ull'u network" = ratioed logic which uses a grounded MOS load is referred to as a seudo'nMOS gate ). $hat is true single hase cloc6ed register% The True single' hase clocked register (TS7#2) uses a single clock0 #$C" Dor the ositive latch0 when #$C is high0 the latch is in the trans arent mode and corres onds to two cascaded invertersE the latch is non'inverting0 and ro agates the in ut to the out ut" On the other hand0 when #$C)*0 both inverters are disabled0 and the latch is in the hold mode" ,. Define a tally circuit. = tally circuit counts the number of in uts that are high and out uts the answer" &f there are 8 in uts there are 8 F9 ossible out uts0 corres onding to *0 90 20 G" 8 in uts that are high" -. Give the ?7?D+1A1BCL*S"/*/D$D$L<DC<IC EFCCCB89CLDCV$L=?CI<U*C C CA

.. BUDGC$H/C,$D$L=CA2;CF32,CID$/VC$<CU/D"LJ/C C CCA ECCCFBCC

A" Dra0 the &!"S im lementation of '+to+1 !UK using transmission gates "

13. $hat are the various modeling used in Verilog% 9" ,ate'level modeling 2" (ata'flow modeling ;" Switch'level modeling H" :ehavioral modeling 11. $hat is the structural gate+level modeling% Structural modeling describes a digital logic networks in terms of the com onents that make u the system" ,ate'level modeling is based on using rimitive logic gates and s ecifying how they are wired together" 12.$hat is S0itch+level modeling% Verilog allows switch'level modeling that is based on the behavior of MOSD4Ts" (igital circuits at the MOS'transistor level are described using the MOSD4T switches"

1#. $hat are the ty es of rogrammable device% 7rogrammable logic structure

7rogrammable &nterconnect 2e rogrammable gate arry 1'. $hat is &L:% #$: means #onfigurable $ogic :lock" 1).$hat are the t0o ty es of !"S=LT% Two ty es of MOS4T are n'channel MOS4T and 'channel MOSD4T" These are known as n'MOS and 'MOS" 1,.0hich !"S can ass logic 1 and logic 3 strongly% 'MOS can ass strong logic 9 n'MOS can ass strong logic * 1-. $hat is 7"I logic function% =8( O2 &nvert logic function (=O&) im lements o eration in the order of =8(0 O20 8OT o erations" So this logic function is known as =O& logic function" 1.. $hat is bubble ushing% =ccording to (e Morgan>s laws0 ) F F ) So 8=8( gate may be drawn as bubbled O2 gate" :ubbles are introduced in the in ut side" This conce t is known as bubble ushing" 12. Im lement y M using bubble ushing conce t% I) can be im lemented using bubbled =8( gate" ) F 23. $hat is "7I 221 Gate% O=& 2290 here 229 refers to number of in uts in each section" 21. $rite the features of &!"S Domino Logic% These structures occu y small area com ared with conventional logic structure" 7arasitic ca acitance is to be small to increase the s eed" 4ach gate can make one Jlogic 9> to Jlogic *> transition"

22. $hat are the tally circuits% Tally circuits one of the a lications of the ass transistor logic" &t is used to count the number of in uts which are high and the out ut is roduced" 2#. $hat are the various forms of inverter based &!"S logic% i" 7seudo 8'MOS logic ii" (ynamic #'MOS logic iii" #locked #'MOS logic iv" #'MOS domino logic v" n' #'MOS logic 2'. $hat is *I* in KILI?IK% 7&7 means 7rogrammable &nterconnect 7oint in K&$&8&K" 2). $hat are the advantages and disadvantages of *L7% 7dvantages of *L7 Sim licity Small si!e Disadvantages of *L7 S eed roblem occur ( ull'u s may become slow on large terms )

Unit IV

1. Give the basic n!"S *L7 structure.

The basic 7$= structure consists of an =8( lane driving an O2 lane" The terminology corres onds to a sum of roducts (SO7) reali!ation of the desired function" The SO7 reali!ation converts directly into a 8=8(' 8=8( im lementation" 3hen a roduct of sums (7OS) reali!ation is desired0 it can be im lemented in O2'=8( or 8O2'8O2 logic" &n either case0 the first array is referred to as the =8( lane0 and the second array as the O2 lane" The line connecting the =8( lane to the O2 lane are called the roduct lines" 2. $hat do you mean by &!"S *L7. The basic #MOS 7$= is obtained by roviding a well and re lacing the ull'u devices in the 8=8('8=8( array or in the 8O2' 8O2 array with enhancement mode MOS devices" The #MOS array can be recharged or not0 and can be clocked 2 =8( lane O2 lane 2egister 2egister &n uts Out uts 9 with the same two' hase clocking scheme as used for the MOS 7$=" #MOS 7$= design offers many more varieties of layout than does nMOS" #. Define finite state machine. 3hen feedback is added to the =8( O2 7$= structure0 the 7$= becomes a finite state machine (DSM)" =n DSM can be designed as a Mealy Machine or a Moore Machine" The Mealy machine has out uts0 which may

change with in ut changes in an asynchronous manner and cause erroneous behavior" %ence0 the Mealy machine should be avoided whenever ossible" The Moore machine has out uts which de end u on and change only with state changes0 since all the out uts of the :oolean'logic block go through a state register0 and are synchronously clocked" '. $hat are the im ortance of the *L7N=S! in VLSI% (i) 2egularity B &t has a standard0 easily e5 andable layout" (ii) #onvenience B $ittle design effort is required" (iii) #om acted B &t is efficient for small circuits" (iv) Modularity B &t makes it ossible to design hierarchical 7$=s and DSMs into large sequential systems" (v) Suitability to being com uter generated" ). Give the structure of a &*LD. = #7$( com rises multi le circuit blocks on a single chi 0 with internal wiring resources to connect the circuit blocks" 4ach circuit block is similar to a 7$= or a 7=$"&t includes four 7=$ like blocks that are connected to a set of interconnection wires" 4ach 7=$ like block is also connected to a sub circuit labeled &.O block0 which is attached to a number of the chi >s in ut and out ut ins"

,. Give the &*LD ac6ages available.

a" *L&& ac6ageB The 7$## ackage has ins that Lwra aroundM the edges of the chi on all four of its sides" The socket that houses the 7$## is attached by solder to the circuit board0 and the 7$## is held in the socket by friction" b. >uad flat ac6 ac6age1 The ND7 ackage has ins on all four sides0 and they e5tend outward from the ackage0 with a downward'wiring sha e" The ND7>s ins are much thinner than those on a 7$##0 which means that the ackage can su ort a larger number of insE ND7s are available with more than 2** ins" -. Give the structure of !7K -333 &*LD.

.. $hat is meant by =*G7% = field rogrammable gate array (D7,=) is a rogrammable logic device that su orts im lementation of relatively large logic circuits" D7,=s can be used to im lement a logic circuit with more than 2*0*** gates whereas a #7$( can im lement circuits of u to about 2*0*** equivalent gates" D7,=s are quite different from #7$(s because D7,=s do not contain =8( or O2 lanes" &nstead0 they rovide logic blocks for im lementation of the required functions" A" Give the general structure of =*G7"

13. $hat are the different commercial =*G7 roducts% Manufacturer D7,= roducts www $ocator =ctel =ct 902 and ;0MK0SK www"actel"com =ltera D$4KO***0P*** and 9*k =74K 2*kwww"altera"com =tmel =TO***0 =TH*k www"ateml"com $ucent O2#= 902 and ; www"lucent"com Nuick$ogic =S&# 902 and ; www"quicklogic"com Vantis VD& www"vantis"com Kilin5 K#;***0K#H***0K#<2**0Virte5www"5ilin5"com 11. $hat are the ty es of re rogrammable G7% =d'hoc =rray and Structured =rray are the two ty es of 2e rogrammable ,ate =rray" 12. $hat is the ty e5s o =*L7% &" 72OM +7rogrammed 2ead'Only Memory/ &&" 7=$ +7rogrammed =rray $ogic/

1#. $hat are the a

lications of *7L%

i" ii" iii"

#ontrol logic a lication &n ut.Out ut (ata' ath logic

1). $hat is finite state machine 8=S!9% 3hen feedback is added to =8('O2 7$= structure0 then it becomes DSM" 1,. $hat are the characteristics of *L7N=S!% i" 2egularity ii" Modularity iii" Suitability iv" 4fficiency 1-. $hat is &L:% #$: means #onfigurable $ogic :lock" 1.. Define mealy machine% &n mealy machine0 out ut may change with the change in the in ut asynchronously" 12. Define moore machine% &n moore machine0 out ut can be changed when state is changed" 23. $hat is /DL% V%S&# %ardware descri tion $anguage" 21. $hat is V/SI&% Very %igh S ed &ntegrated #ircuits" 22. $hat are the various o erators in V/DL% i" $ogical o erators ii" 2elational o erators iii" Shift o erators iv" =dding o erators v" Multi lying o erators vi" Miscellaneous o erators 2#. $hat are the data ty es available in V/DL%

i" ii" iii" iv"

Scalar ty e #om osite ty e =ccess ty e Dile ty e

2'. $hat are the ty es of sub rograms% Dunctions and 7rocedures are ty es of sub rograms" 2). $hat is the use of actual% =ctual in a sub rogram call is used to ass the values from and to a sub rogram"

U?IT )

V/DL 19$rite the acronym for V/DL% V/DL is an acronym for V/SI& %ardware (escri tion $anguage (V%S&# is an acronym for Very %igh S eed &ntegrated #ircuits)" 29 $hat are the different ty es of modeling V/DL% 9) Structural modeling 2) (ata flow modeling ;) behavioral modeling H) Mi5ed ty e of modeling #9 $hat is ac6ages and 0hat is the use of these ac6ages = ackage declaration is used to store a set of common declaration such as com onents ty es rocedures and functions these declaration can then be im orted into others design units using a use caluse" '9 $hat is variable class ;give e(am le for variable =n ob?ect of variable class can also hold a single value of a given ty e 0 %owever in this case different values can be assigned to a variable at different time" 45Bvariable ssB integerE )9 ?ame t0o sub rograms and give the difference bet0een these t0o. 9) Dunction 2) rocedure Only one out ut is ossible in function"" Many out uts ossible using rocedure ,9 $hat is sub rogram "verloading &f two or more sub rogram to be e5ecuted in a same name" overloading of sub rogram should be erformed" -9 0rite the V/DL coding for a se>uential statement 8d+fli flo 9 entity dff is ort(clk0dBin stdQlogicE qBout stdQlogic)E endE architecture dff of dff is begin rocess(clk0d)

begin if clk> event and clk)> 9> then qR)dE end rocessE endE .9 $hat are the different 6inds of The test bench Stimulus only Dull testbench Simulator s ecific %ybrid testbench Dast testbench 29 $hat is !oore =S! The out ut of a Moore finite state machine(DSM) de ends only on the state and not on its in uts" This ty e of behaviour can be modeled using a single rocess with the case statement that switches on the state value" 139 $rite the testbench for and gate entity testand2 is end entity architecture io of testand2 is signal a0b0cBstdQlogicE begin g9Bentity work"and2(e52) ort ma (a0b0c) aR)> *> 0> 9> after 9** nsE bR)> *> 0 J9> after 9<* nsE endE 11. 0rite the synta( of rocedure body% 7rocedure rocedure name ( arameterlist) 12. $hat is test bench% = test bench is a model which is used to e5ercise and verify the correctness of a hardware model" 1#. $hat are the t0o methods to generate stimulus values%

i" ii"

To create waveforms and a ly stimulus at discrete time intervals" To generate stimulus based on the state of the entity or out ut of the entity"

1'. Differentiate bet0een channeled F channel less gate array. #hanneled ,ate =rray #hannel less ,ate =rray 9" Only the interconnect is customi!ed only the to few mask layers are customi!ed" 2" The interconnect uses redefined s aces between rows of base cells" 8o redefined areas are set aside for routing between cells" ;" 2outing is done using the s aces 2outing is done using the area of transistors unused" H" $ogic density is less $ogic density is higher" 1). $hat is a =*G7% = field rogrammable gate array (D7,=) is a rogrammable logic device that su orts im lementation of relatively large logic circuits" D7,=s can be used to im lement a logic circuit with more than 2*0*** gates whereas a #7$( can im lement circuits of u to about 2*0*** equivalent gates" 1,. $hat are the different methods of rogramming of *7Ls% The rogramming of 7=$s is done in three main waysB S Dusible links S TV - erasable 472OM S 4472OM (4272OM) - 4lectrically 4rasable 7rogrammable 2OM 1-.$hat is an antifuse% =n antifuse is normally high resistance (U9**M3)" On a lication of a ro riate rogramming voltages0 the antifuse is changed ermanently to a low' resistance structure (2**'<**3)" 1.. $hat are the different levels of design abstraction at hysical design. S =rchitectural or functional level S 2egister Transfer'level (2T$) S $ogic level

S #ircuit level 12.$hat are macros% The logic cells in a gate'array library are often called macros" 23. $hat are *rogrammable Interconnects% &n a 7=$0 the device is rogrammed by changing the characteristics if the switching element" =n alternative would be to rogram the routing" 21. Give the ste s in7SI& design flo0. a" (esign entry b" $ogic synthesisSystem artitioning c" 7relayout simulation" d" Dloor lanning e" 7lacement f" 2outing g" 45traction 22. $rite notes on functionality tests% Dunctionality tests verify that the chi erforms its intended function" These tests assert that all the gates in the chi 0 acting in concert0 achieve a desired function" These tests are usually used early in the design cycle to verify the functionality of the circuit" 2#. $rite notes on manufacturing tests% Manufacturing tests verify that every gate and register in the chi functions correctly" These tests are used after the chi is manufactured to verify that the silicon is intact" 2'. !ention the defects that occur in a chi % a) layer'to'layer shorts b) discontinuous wires c) thin'o5ide shorts to substrate or well 2). Give some circuit maladies to overcome the defects% a" nodes shorted to ower or ground b" nodes shorted to each other c" in uts floating.out uts disconnected

S-ar putea să vă placă și

- Design of Electrical Services For Buildings 4th Edition 1Document329 paginiDesign of Electrical Services For Buildings 4th Edition 1Ar Vishul Saxena100% (1)

- History of The Numeral Systems:: Unit1: Number Systems & CodesDocument20 paginiHistory of The Numeral Systems:: Unit1: Number Systems & CodeshvrkÎncă nu există evaluări

- Baliga Figure of MeritDocument3 paginiBaliga Figure of MeritKyle BotheÎncă nu există evaluări

- Preliminary Assignment A1-001-A Izaidi Bin Wan Ibrahim - GIT 0763Document2 paginiPreliminary Assignment A1-001-A Izaidi Bin Wan Ibrahim - GIT 0763Adam CkÎncă nu există evaluări

- Vlsi Final Notes Unit1Document31 paginiVlsi Final Notes Unit1RohitParjapatÎncă nu există evaluări

- Project Report: On Analyze Submerged Arc Welding (SAW) With Respect To MIG Welding (GMAW)Document32 paginiProject Report: On Analyze Submerged Arc Welding (SAW) With Respect To MIG Welding (GMAW)Rama Krishna Reddy DonthireddyÎncă nu există evaluări

- Jan 2010Document27 paginiJan 2010ವಿಶ್ವ ಚೆತನ್ ಗೌಡÎncă nu există evaluări

- Unit-Ii Mosfet Transistors: VI Semester ECEDocument5 paginiUnit-Ii Mosfet Transistors: VI Semester ECEMohamed MusthafaÎncă nu există evaluări

- Rvs College of Engineering and Technology Department of Ece Ec2254-Linear Intergated Circuits Two Mark Questions With Answers. Unit - IDocument14 paginiRvs College of Engineering and Technology Department of Ece Ec2254-Linear Intergated Circuits Two Mark Questions With Answers. Unit - ISJANTOSEELANÎncă nu există evaluări

- And Power in Full Subtractor Circuit: Transistor Gating: Reduction of Leakage CurrentDocument11 paginiAnd Power in Full Subtractor Circuit: Transistor Gating: Reduction of Leakage CurrentBhupender KumawatÎncă nu există evaluări

- Vlsi Unit-IDocument45 paginiVlsi Unit-Isuneelanubolu7Încă nu există evaluări

- Fin FEtDocument39 paginiFin FEtqwerty123890Încă nu există evaluări

- Unit 1 Basic MOS Technology: Figure 1. Moore's LawDocument18 paginiUnit 1 Basic MOS Technology: Figure 1. Moore's LawSushruth SastryÎncă nu există evaluări

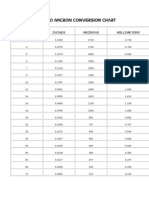

- Mesh To Micron Conversion ChartDocument4 paginiMesh To Micron Conversion Chartjackiee_262000Încă nu există evaluări

- FUNDAMENTALS of CMOS VLSI 5th SEM ECE PDFDocument190 paginiFUNDAMENTALS of CMOS VLSI 5th SEM ECE PDFVarunKaradesaiÎncă nu există evaluări

- Ec8095-Vlsi Design-607796847-Ec 8095 NotesDocument163 paginiEc8095-Vlsi Design-607796847-Ec 8095 Noteshmpudur1968Încă nu există evaluări

- Introduction To Vlsi TechnologyDocument32 paginiIntroduction To Vlsi TechnologysivaÎncă nu există evaluări

- Current Loop Application: Rolta Academy: Engineering Design ServicesDocument7 paginiCurrent Loop Application: Rolta Academy: Engineering Design ServicesRaj ChavanÎncă nu există evaluări

- Malvino Chapter 1-5 (P1-14)Document13 paginiMalvino Chapter 1-5 (P1-14)grachellesvampirebiteÎncă nu există evaluări

- Assignment M.E (Elp) Ept&dDocument1 paginăAssignment M.E (Elp) Ept&dSyed Asif Ali ShahÎncă nu există evaluări

- BASIC VLSI DESIGN .PptsDocument32 paginiBASIC VLSI DESIGN .PptsNarayana Rao RevallaÎncă nu există evaluări

- Ec6601 Vlsi QBW (R2013)Document20 paginiEc6601 Vlsi QBW (R2013)Bharath PonÎncă nu există evaluări

- Introduction To VLSI Technology: Abhijeet KumarDocument32 paginiIntroduction To VLSI Technology: Abhijeet KumarPrithireddy ThenetiÎncă nu există evaluări

- Eee-Vii-Vlsi Circuits and Design (10ee764) - NotesDocument225 paginiEee-Vii-Vlsi Circuits and Design (10ee764) - Notessammy100% (1)

- Silicon Controlled RectifierDocument7 paginiSilicon Controlled RectifierNur Indah IrianiÎncă nu există evaluări

- Microstrip Patch Antenna With Defected Ground Structure & Offset Feed in The Field of CommunicationDocument4 paginiMicrostrip Patch Antenna With Defected Ground Structure & Offset Feed in The Field of CommunicationUpendraSinghÎncă nu există evaluări

- Diploma in Electrical Engg. Semester-5 Power Electronics: Construction of SCRDocument6 paginiDiploma in Electrical Engg. Semester-5 Power Electronics: Construction of SCRDiogo RodriguesÎncă nu există evaluări

- Microelectronic CircuitDocument696 paginiMicroelectronic CircuitImtiaz AhmedÎncă nu există evaluări

- Important Short Questions and Answers - VLSI Design - CMOS TechnologyDocument10 paginiImportant Short Questions and Answers - VLSI Design - CMOS TechnologysamactrangÎncă nu există evaluări

- A Full Wave RectifierDocument14 paginiA Full Wave RectifierVarun Jain50% (6)

- Vlsi Unit1Document32 paginiVlsi Unit1venkatÎncă nu există evaluări

- Dokumen - Tips - Full Wave Rectifier ProjectDocument17 paginiDokumen - Tips - Full Wave Rectifier Projectsmtsushma9Încă nu există evaluări

- Future MOSFET Devices Using High-K (TiO2) DielectricDocument6 paginiFuture MOSFET Devices Using High-K (TiO2) DielectricIJRASETPublicationsÎncă nu există evaluări

- CH2Document45 paginiCH2himanshukatyal7Încă nu există evaluări

- Vlsi Viva QuestionsDocument9 paginiVlsi Viva Questionssheethal rokhadeÎncă nu există evaluări

- Mstrip-Slot Transtion MOTL98Document4 paginiMstrip-Slot Transtion MOTL98Sreedhar GundlapalliÎncă nu există evaluări

- Iiiyr Visem Vlsi DesignDocument20 paginiIiiyr Visem Vlsi DesignlokeshwarrvrjcÎncă nu există evaluări

- Welding Processes ModuleDocument27 paginiWelding Processes Moduleரமேஷ் பாலக்காடு100% (1)

- VLSI Ut1Document16 paginiVLSI Ut1Naveen TimmarioÎncă nu există evaluări

- Advances in Structural Concrete: Association of Engineers, Gaza Governorates, PalestineDocument33 paginiAdvances in Structural Concrete: Association of Engineers, Gaza Governorates, Palestinehanan-3000-1999Încă nu există evaluări

- A Simple ReceiverDocument8 paginiA Simple ReceiverSmai HondoÎncă nu există evaluări

- E24Document4 paginiE24harirajiniÎncă nu există evaluări

- Origins of Weak Inversion or Sub-Threshold CircuitDocument4 paginiOrigins of Weak Inversion or Sub-Threshold CircuitNaveed AhmedÎncă nu există evaluări

- Simulation and Characterization of Soi Mosfets: Dual Degree Project PresentationDocument28 paginiSimulation and Characterization of Soi Mosfets: Dual Degree Project Presentationsunilkmch505682Încă nu există evaluări

- AN211 FET Teory and PracticeDocument12 paginiAN211 FET Teory and PracticefabirznÎncă nu există evaluări

- Gate Induced Drain Leakage For Ultra Thin MOSFET Devices Using SilvacoDocument2 paginiGate Induced Drain Leakage For Ultra Thin MOSFET Devices Using Silvacosiddhant gangwalÎncă nu există evaluări

- Vlsi 2 Marks QSDocument16 paginiVlsi 2 Marks QSJay SubbareddyÎncă nu există evaluări

- Impact of Wafer-Bonding Defects On Monolithic 3D Integrated CircuitsDocument3 paginiImpact of Wafer-Bonding Defects On Monolithic 3D Integrated Circuitsakoneru31Încă nu există evaluări

- 2 Mark Questions & AnswersDocument6 pagini2 Mark Questions & AnswersMuthu KumarÎncă nu există evaluări

- M172 Section CorrosionfsadfDocument17 paginiM172 Section Corrosionfsadfmoganraj8munusamyÎncă nu există evaluări

- Question & AnswerDocument10 paginiQuestion & AnswerArighna BasakÎncă nu există evaluări

- 6 Sem Electronics Engineering VLSI (2mark Questions and Answers)Document19 pagini6 Sem Electronics Engineering VLSI (2mark Questions and Answers)Yogi ToliaÎncă nu există evaluări

- 1.what Is Design Hierarchy? What Are Its Types?Document5 pagini1.what Is Design Hierarchy? What Are Its Types?naveensilveriÎncă nu există evaluări

- Metal-Semiconductor Contacts: E E Q QDocument12 paginiMetal-Semiconductor Contacts: E E Q QLatte ValdezÎncă nu există evaluări

- Probing The Magnetic Field ProbeDocument7 paginiProbing The Magnetic Field Probeagmnm1962Încă nu există evaluări

- Testing On Generator StatorDocument36 paginiTesting On Generator StatorSajid Akhter100% (1)

- Lesson 28 Electric CurrentDocument7 paginiLesson 28 Electric Currenti5piritiÎncă nu există evaluări

- Equipment For SubmergedDocument4 paginiEquipment For SubmergedRaj BindasÎncă nu există evaluări

- Rogowski CoilDocument13 paginiRogowski CoilKanishka AhirwarÎncă nu există evaluări

- Layout ExamplesDocument13 paginiLayout Examplesnazibhd786Încă nu există evaluări

- Diode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesDe la EverandDiode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesEvaluare: 4.5 din 5 stele4.5/5 (7)

- MOS Integrated Circuit DesignDe la EverandMOS Integrated Circuit DesignE. WolfendaleÎncă nu există evaluări

- Aditya Institute of Technology & Management K.Kotturu, TekkaliDocument8 paginiAditya Institute of Technology & Management K.Kotturu, TekkalihvrkÎncă nu există evaluări

- Fundamentals of Telecommunications 1Document34 paginiFundamentals of Telecommunications 1hvrkÎncă nu există evaluări

- WRDOCDocument1.329 paginiWRDOChvrkÎncă nu există evaluări

- Unit - 2: Boolean Algebra and Switching FunctionsDocument19 paginiUnit - 2: Boolean Algebra and Switching FunctionshvrkÎncă nu există evaluări

- Pollution NDocument26 paginiPollution NhvrkÎncă nu există evaluări

- Basic Electrical Properties of MOSDocument30 paginiBasic Electrical Properties of MOShvrkÎncă nu există evaluări

- Entrepreneur QualitiesDocument16 paginiEntrepreneur QualitieshvrkÎncă nu există evaluări

- How To Start MSMEDocument24 paginiHow To Start MSMEhvrkÎncă nu există evaluări

- Biodiversity and Its ConservationDocument12 paginiBiodiversity and Its ConservationhvrkÎncă nu există evaluări

- PCB Layout DesignDocument5 paginiPCB Layout DesignhvrkÎncă nu există evaluări

- CMOS Fabrication ProcessDocument2 paginiCMOS Fabrication ProcesshvrkÎncă nu există evaluări

- Vlsi Imp QuestionsDocument2 paginiVlsi Imp QuestionsMahender VengalaÎncă nu există evaluări

- SSDocument1 paginăSShvrkÎncă nu există evaluări

- Msam 615Document2 paginiMsam 615hvrkÎncă nu există evaluări

- Rtos (IV-II Ece) I MidDocument1 paginăRtos (IV-II Ece) I MidhvrkÎncă nu există evaluări

- SL - No. Date Unit No. TopicDocument2 paginiSL - No. Date Unit No. TopichvrkÎncă nu există evaluări

- W.E.F. 2009-10 Jawaharlal Nehru Technological University: Kakinada KAKINADA 533 003Document17 paginiW.E.F. 2009-10 Jawaharlal Nehru Technological University: Kakinada KAKINADA 533 003hvrkÎncă nu există evaluări

- Quiz/Mid Marks Quiz/Mid Marks Quiz/Mid Marks: SNO Halltick Et Marks SNO Halltick Et Marks SNODocument6 paginiQuiz/Mid Marks Quiz/Mid Marks Quiz/Mid Marks: SNO Halltick Et Marks SNO Halltick Et Marks SNOhvrkÎncă nu există evaluări

- Basic Introduction To SQL PLUS: Getting StartedDocument6 paginiBasic Introduction To SQL PLUS: Getting StartedhvrkÎncă nu există evaluări

- Embedded RTOS TasksDocument42 paginiEmbedded RTOS TaskshvrkÎncă nu există evaluări

- II B. Tech I Semester, Supplementary Examinations, May - 2012 Fluid Mechanics & Hydraulic MachinesDocument44 paginiII B. Tech I Semester, Supplementary Examinations, May - 2012 Fluid Mechanics & Hydraulic MachineshvrkÎncă nu există evaluări

- ECA (R10) April 2012 PDFDocument93 paginiECA (R10) April 2012 PDFhvrkÎncă nu există evaluări

- Morning BellsDocument1 paginăMorning Bellshvrk50% (2)

- ECA (R10) April 2012 PDFDocument93 paginiECA (R10) April 2012 PDFhvrkÎncă nu există evaluări

- AO4606 Complementary Enhancement Mode Field Effect TransistorDocument7 paginiAO4606 Complementary Enhancement Mode Field Effect TransistorkhafjiÎncă nu există evaluări

- DatasheetDocument2 paginiDatasheetDidier DoradoÎncă nu există evaluări

- Data Sheet 2222Document8 paginiData Sheet 2222Yusafxai YxaiÎncă nu există evaluări

- Tutorial 1Document4 paginiTutorial 1Anonymous HyOfbJ6Încă nu există evaluări

- Finfet: Soi and The Non-Planar Finfet DeviceDocument34 paginiFinfet: Soi and The Non-Planar Finfet Devicesandeeppareek926100% (1)

- Physics Project On SemiconductorDocument25 paginiPhysics Project On Semiconductorvkanishka1999Încă nu există evaluări

- FlexicoreDocument16 paginiFlexicorelolfreealistarÎncă nu există evaluări

- 1979 Signetics Analog ApplicationsDocument418 pagini1979 Signetics Analog ApplicationsBapeÎncă nu există evaluări

- Tutorial 1: Carrier ConcentrationDocument4 paginiTutorial 1: Carrier ConcentrationSaeed MishalÎncă nu există evaluări

- Electroluminescence of Thin Film P-I-N Diodes Based On A-Sic:H With Integrated Ge NanoparticlesDocument6 paginiElectroluminescence of Thin Film P-I-N Diodes Based On A-Sic:H With Integrated Ge Nanoparticlessper kstorÎncă nu există evaluări

- Analog Electronics - K-Wiki - Chapter 2 - BJTDocument74 paginiAnalog Electronics - K-Wiki - Chapter 2 - BJTmadivala nagarajaÎncă nu există evaluări

- Lecture 5 - Special Purpose Diodes - 1Document40 paginiLecture 5 - Special Purpose Diodes - 1Willian CarlosÎncă nu există evaluări

- 10 Stickdiagrams PDFDocument55 pagini10 Stickdiagrams PDFrdanwaraÎncă nu există evaluări

- Silicon PNP Power Transistors: Savantic Semiconductor Product SpecificationDocument3 paginiSilicon PNP Power Transistors: Savantic Semiconductor Product SpecificationNatal2i2Încă nu există evaluări

- Digital Electronics - Contd.: Rijil RamchandDocument19 paginiDigital Electronics - Contd.: Rijil RamchandAshna JoseÎncă nu există evaluări

- Electronics 1: Ahsan KhawajaDocument17 paginiElectronics 1: Ahsan KhawajaRaja Uzair SaeedÎncă nu există evaluări

- Analog Ch5 Multistage AmplifierDocument12 paginiAnalog Ch5 Multistage Amplifierskgupta4281Încă nu există evaluări

- Is 2032-8Document17 paginiIs 2032-8suresh kumarÎncă nu există evaluări

- Tadahiro Ohmi (Auth.), André A. Jaecklin (Eds.) - Power Semiconductor Devices and Circuits-Springer US (1992) PDFDocument400 paginiTadahiro Ohmi (Auth.), André A. Jaecklin (Eds.) - Power Semiconductor Devices and Circuits-Springer US (1992) PDFYusuf ArdiÎncă nu există evaluări

- Silicon PNP Power Transistors: TIP42/42A/42B/42CDocument4 paginiSilicon PNP Power Transistors: TIP42/42A/42B/42CWhisnu BhuntoroÎncă nu există evaluări

- Fdpc5018Sg: Powertrench Power Clip 30V Asymmetric Dual N-Channel MosfetDocument12 paginiFdpc5018Sg: Powertrench Power Clip 30V Asymmetric Dual N-Channel MosfetDima RozhencovÎncă nu există evaluări

- Olution AnualDocument207 paginiOlution Anualmrgummy2013Încă nu există evaluări

- Chapter4 NonidealDocument19 paginiChapter4 NonidealHữu VinhÎncă nu există evaluări

- Low Noise GaAs FET/BJT VCODocument8 paginiLow Noise GaAs FET/BJT VCOsanjeevsoni64Încă nu există evaluări

- Yaesu DMU-2000 ServDocument21 paginiYaesu DMU-2000 ServlarsÎncă nu există evaluări

- Lab 2 Zener and LEDsDocument6 paginiLab 2 Zener and LEDsAlisha AasÎncă nu există evaluări

- Seminar 1Document17 paginiSeminar 1Udbhav MaheshwariÎncă nu există evaluări

- Vlsi Design PDFDocument120 paginiVlsi Design PDFHareesh Harsha100% (1)

- Current and Voltage Sources: Analog Design For CMOS VLSI SystemsDocument37 paginiCurrent and Voltage Sources: Analog Design For CMOS VLSI SystemsKaelan LockhartÎncă nu există evaluări