Documente Academic

Documente Profesional

Documente Cultură

ASIC June2011

Încărcat de

rajasekarkprDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

ASIC June2011

Încărcat de

rajasekarkprDrepturi de autor:

Formate disponibile

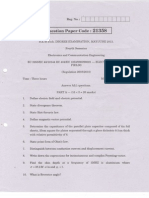

Reg. No.

Question Paper Code :

31212

Common to M.E. Applied Electronics/M.E. Computer and Communication/ M.E. VLSI Design Elective

252079 ASIC DESIGN (Regulation 2010) Time : Three hours

40

Answer ALL questions.

1.

What are the rules to be followed to find equivalent resistance of MOS transistors connected in series/parallel?

2. 3. 4. 5. 6. 7. 8. 9.

Enlist any four essential characteristics of FPGA of reconfigurable gate arrays. List different types of antifuses used in FPGAs. Differentiate DC & AC input cells in programmable ASIC. List few files created in the synthesis process of ACTEL device. What are the features of EDIF? What are the data formats supported in verilog? What are the types of simulation? Distinguish between Global and Detailed routing.

84

01 8

10.

What is the need for DRC in ASIC design?

40

18

PART A (10 2 = 20 marks)

18

M.E./M.Tech. DEGREE EXAMINATION, JUNE 2011.

40

Maximum : 100 marks

PART B (5 16 = 80 marks) 11. (a) (i) (ii)

Design a CMOS combinational cell to implement the function AOI (2, 11). (8) Find the logic area of the cell OAI (22) with a logic ratio of 3. Or (8)

(b)

(i)

Design CMOS logic gates for the following functions (1) (2)

Y = (A + B + C ) + D

Y = A + CD + B .

18

(ii)

Implement two input XOR cell using two input multiplexer.

40

12.

(a)

(i) (ii)

Write short notes FAMOS.

40

Or Or 2

(iii) A 32 bit off-chip bus operating at 5 V and 66 MHz clock rate is driving a capacitance of 25 pf/bit. Each bit is estimated to have a toggling probability of 0.25 at each clock cycle. Determine the power dissipation. (4) (12) (4)

(b)

(i) (ii)

Implement the function Y = AB + CD + B + C using Actel 2 logic cell. (10) With a neat circuit diagram explain the Xilinx Xc 4000 I/O block. (6)

13.

(a)

(i) (ii)

40

Briefly explain about half-gate ASIC synthesis in Xilinx. Write a technical note on PLA tools.

18

What are the different types of ASIC I/O cells?

01 8

(b)

Explain in detail the following : (i) Actel Act Interconnect Architecture Derive Elmores delay for the given RC circuit at node 5. (8 + 8)

(ii)

84

1

(4) + (4) (4) (10) (6)

31212

14.

(a)

Explain the following in VHDL logic synthesis. (i) (ii) Initialization and reset Combinational logic synthesis

40

(iii) Memory synthesis in VHDL and Verilog. Or (b) (i) (ii)

Discuss the procedure for path oriented decision making (PODEM) algorithm. (8) Find the test vector detecting the fault at pin 6 stuck-at-D in the following circuit. (8)

15.

(a)

Write short notes on : (i) (ii) Clock routing

Left-Edge algorithm.

18

Or 3

40

(8) + (8) (b) Briefly explain iterative partitioning improvement using Kernighan-lin algorithm.

84

01 8

40

18

(4) (6) (6)

31212

S-ar putea să vă placă și

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (894)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (73)

- Chapter 1 Power ProtectionDocument26 paginiChapter 1 Power Protectiontiegsti gebrehiwotÎncă nu există evaluări

- LED Running Lights CircuitsDocument17 paginiLED Running Lights CircuitsKaos Polos NakiraÎncă nu există evaluări

- Separately Excited DC Generator ExplainedDocument22 paginiSeparately Excited DC Generator ExplainedAbdulrazzaq50% (2)

- Question Bank - Lowpower VLSI Circuits - JNTUADocument3 paginiQuestion Bank - Lowpower VLSI Circuits - JNTUArajasekarkpr100% (5)

- User Manual: Record System 20Document16 paginiUser Manual: Record System 20derbalijalel100% (2)

- UNIT 4 - Switched CapacitanceDocument75 paginiUNIT 4 - Switched Capacitancerajasekarkpr100% (1)

- 12 - Emf 2012Document4 pagini12 - Emf 2012rajasekarkprÎncă nu există evaluări

- Power Amplifiers - Power PointDocument33 paginiPower Amplifiers - Power PointrajasekarkprÎncă nu există evaluări

- JNTUA - IV ECE - LPVLSI - Unit V - Leakage Power MinimizationDocument66 paginiJNTUA - IV ECE - LPVLSI - Unit V - Leakage Power Minimizationrajasekarkpr100% (2)

- 34 42 ConservationDocument9 pagini34 42 ConservationrajasekarkprÎncă nu există evaluări

- Orcad Capture and PspiceDocument25 paginiOrcad Capture and PspiceabhinandÎncă nu există evaluări

- 481lecture16 T Section S ParameterDocument10 pagini481lecture16 T Section S ParameterRuben BellÎncă nu există evaluări

- Ec6512 Communication Systems Laboratory ManuslDocument86 paginiEc6512 Communication Systems Laboratory ManuslSriram71% (24)

- Emf Novdec 2011Document4 paginiEmf Novdec 2011rajasekarkprÎncă nu există evaluări

- An OvervAn Overview of Low Power Techniqueiew of Low Power TechniqueDocument8 paginiAn OvervAn Overview of Low Power Techniqueiew of Low Power TechniquendtleeÎncă nu există evaluări

- Chapter 3Document17 paginiChapter 3rajasekarkprÎncă nu există evaluări

- An OvervAn Overview of Low Power Techniqueiew of Low Power TechniqueDocument8 paginiAn OvervAn Overview of Low Power Techniqueiew of Low Power TechniquendtleeÎncă nu există evaluări

- Tuned CollectorTuned Collector OscillatorDocument4 paginiTuned CollectorTuned Collector OscillatorrajasekarkprÎncă nu există evaluări

- Electromagnetic Field Novdec-2012Document3 paginiElectromagnetic Field Novdec-2012rajasekarkprÎncă nu există evaluări

- 13 - Emf May 2013Document3 pagini13 - Emf May 2013rajasekarkprÎncă nu există evaluări

- PCI6221Document7 paginiPCI6221rajasekarkprÎncă nu există evaluări

- List of Engineering Colleges in KeralaDocument7 paginiList of Engineering Colleges in KeralapoisonedstarÎncă nu există evaluări

- ECE 7th Sem R2008Document29 paginiECE 7th Sem R2008rajasekarkprÎncă nu există evaluări

- Question Paper Code:: Reg. No.Document3 paginiQuestion Paper Code:: Reg. No.Joshua DuffyÎncă nu există evaluări

- 11 EMF April11Document3 pagini11 EMF April11rajasekarkprÎncă nu există evaluări

- List of Engineering Colleges in KeralaDocument7 paginiList of Engineering Colleges in KeralapoisonedstarÎncă nu există evaluări

- ASIC June2010Document2 paginiASIC June2010rajasekarkprÎncă nu există evaluări

- P.G. Diploma Examination - 2010: (Vlsi Design)Document2 paginiP.G. Diploma Examination - 2010: (Vlsi Design)rajasekarkprÎncă nu există evaluări

- ASIC - April2011Document2 paginiASIC - April2011rajasekarkprÎncă nu există evaluări

- Implementation of Stronger Aes by Using Dynamic S-Box Dependent of Master KeyDocument9 paginiImplementation of Stronger Aes by Using Dynamic S-Box Dependent of Master KeyrajasekarkprÎncă nu există evaluări

- P.G. Diploma Examination - 2010: (Vlsi Design)Document2 paginiP.G. Diploma Examination - 2010: (Vlsi Design)rajasekarkprÎncă nu există evaluări

- Bit Serial MultiplierDocument4 paginiBit Serial MultiplierrajasekarkprÎncă nu există evaluări

- P.G. Diploma Examination - 2010: (Vlsi Design)Document2 paginiP.G. Diploma Examination - 2010: (Vlsi Design)rajasekarkprÎncă nu există evaluări

- Projeyardim 1Document4 paginiProjeyardim 1Victor SerranoÎncă nu există evaluări

- Ultrafast Soft Recovery Rectifier Diode: APT15D100K 1000V 15ADocument4 paginiUltrafast Soft Recovery Rectifier Diode: APT15D100K 1000V 15AQuickerManÎncă nu există evaluări

- sm2000 GBDocument4 paginism2000 GBRikky ChaniagoÎncă nu există evaluări

- Topical Test Chapter 18: AC Circuits Section A: Objective (10 Marks)Document4 paginiTopical Test Chapter 18: AC Circuits Section A: Objective (10 Marks)Wong Chai YenÎncă nu există evaluări

- Scooba Drydock: Charging and Drying StandDocument8 paginiScooba Drydock: Charging and Drying Standir3678Încă nu există evaluări

- Syntron - Feeders ControlsDocument3 paginiSyntron - Feeders ControlsMiguel A. CondeÎncă nu există evaluări

- Monthly Instrumentation and Monitoring For Excavation WorksDocument2 paginiMonthly Instrumentation and Monitoring For Excavation WorksJeff SoÎncă nu există evaluări

- Activity No. 3 Resistive Circuit: ObjectivesDocument3 paginiActivity No. 3 Resistive Circuit: ObjectivesJulius Chavez0% (1)

- Parts of Speech: Nouns, Verbs, Adjectives, Adverbs - Grand Learning SchoolDocument1 paginăParts of Speech: Nouns, Verbs, Adjectives, Adverbs - Grand Learning SchoolMr. RomeelÎncă nu există evaluări

- Practical No:-1: Know The Digital Lab IC Tester Multimeter Bread Board Trainer KitDocument16 paginiPractical No:-1: Know The Digital Lab IC Tester Multimeter Bread Board Trainer KitH123 Thawal GauravÎncă nu există evaluări

- Lab 7 Power Amplifier BBN 10205 (Done)Document6 paginiLab 7 Power Amplifier BBN 10205 (Done)Zhamir ZhakwanÎncă nu există evaluări

- Detecting Turn-to-Turn Failures (38Document3 paginiDetecting Turn-to-Turn Failures (38Zdenko SemanÎncă nu există evaluări

- Qab & Hqa Quick-Action Fuses: Overcurrent Protection For Semiconductor Elements and CablesDocument2 paginiQab & Hqa Quick-Action Fuses: Overcurrent Protection For Semiconductor Elements and CablesMAI_QualityÎncă nu există evaluări

- Technical Manual: SeriesDocument362 paginiTechnical Manual: SeriesDarshana DimbulwakaÎncă nu există evaluări

- VLSI Technology and Applications - 10B11EC612: Tutorial Sheet - 3Document1 paginăVLSI Technology and Applications - 10B11EC612: Tutorial Sheet - 3harshit420Încă nu există evaluări

- Power factor (cos φ and tan φ) : Fig. 5 Power triangle showing the effect ofDocument18 paginiPower factor (cos φ and tan φ) : Fig. 5 Power triangle showing the effect ofYusril AdrianÎncă nu există evaluări

- Bipolar Junction TransistorDocument6 paginiBipolar Junction TransistorPadirikuppam PavithraÎncă nu există evaluări

- MEDC BG3W2LBR Acionador Manual Ficha Tecnica Catalogo DatasheetDocument2 paginiMEDC BG3W2LBR Acionador Manual Ficha Tecnica Catalogo DatasheetPeter PenhaÎncă nu există evaluări

- Abdul Majid: Education Personal SkillsDocument1 paginăAbdul Majid: Education Personal SkillsAshikul AnikÎncă nu există evaluări

- Power Supply 17IPS19-5 Philips VES2.2E LA PDFDocument4 paginiPower Supply 17IPS19-5 Philips VES2.2E LA PDFJejeÎncă nu există evaluări

- C8516-CLT-QMT-0032 - Rev-00 Inspection Checklist For Kerbstone Installation WorksDocument1 paginăC8516-CLT-QMT-0032 - Rev-00 Inspection Checklist For Kerbstone Installation WorksJabin100% (2)

- Preposition Chart: Ø Exact Times Ø Meal Times Ø Parts of The Day Ø Age Ø Ø Ø Ø Ø ØDocument6 paginiPreposition Chart: Ø Exact Times Ø Meal Times Ø Parts of The Day Ø Age Ø Ø Ø Ø Ø ØDavid MurciaÎncă nu există evaluări

- Rotor Design For Whirl Flutter: An Examination of Options For Improving Tiltrotor Aeroelastic Stability MarginsDocument16 paginiRotor Design For Whirl Flutter: An Examination of Options For Improving Tiltrotor Aeroelastic Stability MarginsYonghui XUÎncă nu există evaluări

- 7.5 Kva UpsDocument54 pagini7.5 Kva UpsSumit DasÎncă nu există evaluări

- XDDocument509 paginiXDsleepyÎncă nu există evaluări

- Full Theory On Twilight SwitchDocument11 paginiFull Theory On Twilight SwitchAdarshVerma50% (4)