Documente Academic

Documente Profesional

Documente Cultură

Diseño Digital Con Esquemáticos y VHDL, Implementado en La FPGA Spartan 2

Încărcat de

Camilo RolónTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Diseño Digital Con Esquemáticos y VHDL, Implementado en La FPGA Spartan 2

Încărcat de

Camilo RolónDrepturi de autor:

Formate disponibile

1

Diseo Digital con Esquemticos y VHDL, Implementado en la FPGA Spartan 2

Daniel Camilo Roln Quintero - Cd.: 1160467 , Diego Andrs Parada Rozo - Cd.: 1160449

ResumenEn este documento se describe de manera breve el procedimiento para crear e implementar el diseo a travs de modelos esquemticos mediante el modo Schematic; e implementando el VHDL mediante el modo HDL de la herramienta Xilinx WebPack. No obstante, El proceso implementado le presta vital importancia a dos aspectos: el diseo a travs de VHDL y la simulacin del mismo a travs del software Xilinx ISE. Por ltimo, se darn las respectivas conclusiones producto de las observaciones de las seales lgicas de entrada y salida. Index TermsJTAG, VHDL, Schematic, I/O marker, cabecera, std_logic, entity, architecture.

II. II-A. Objetivo General

O BJETIVOS

Aplicar a un diagrama el lenguaje VHDL para la descripcin de circuitos digitales sencillos. II-B. Objetivos Especcos Conocer el procedimiento para disear circuitos lgicos a travs de modelos esquemticos y del cdigo fuente del VHDL. Aplicar el estilo de programacin ujo de datos (DataFlow) del VHDL. Simular cada circuito lgico implementado con la herramienta Xilinx ISE. III. M ARCO T ERICO

I.

I NTRODUCCIN

UANDO se usan herramientas CAD para sintetizar un circuito lgico, el diseador puede proporcionar la descripcin inicial de varias formas. Una de ellas es a travs de modelos esquemticos que no son ms que representaciones de algn cdigo HDL que describe su comportamiento.

Otro modo ms eciente, pero no ms importante que el otro1 , es a travs de lenguaje HDL. Comnmente se implementan dos tipos de este lenguaje, el VHDL y el Verilog. En este documento se implementa el VHDL. El compilador de VHDL traduce este cdigo en un circuito lgico. Cada seal lgica del circuito se representa en el cdigo de VHDL como un objeto de datos. As como las variables declaradas en cualquier lenguaje de programacin de alto nivel tienen tipos asociados enteros o caracteres, por ejemplo, los objetos de datos en VHDL pueden ser de varios tipos. Una norma VHDL, la IEEE 1164, incluye un tipo de datos llamado STD_LOGIC, que es un tipo de dato parecido al BIT, pero que no slo tiene los valores binarios 0 y 1, sino que puede tomar otros valores como: 0, 1, Z, , L, H, U, X y W. Slo los primeros cuatro son tiles para la sntesis de los circuitos lgicos. El valor Z representa una impedancia alta; y signica una condicin "no importa". El valor L representa una "seal dbil 0", H una "seal dbil 1", U indica "sin inicializar", X siginica "desconocido" y W quiere decir "seal dbil desconocida". Otro tipo es el STD_LOGIC_VECTOR representa un arreglo de objetos STD_LOGIC. [1]

1 Esto se debe a que la decisin de trabajar con esquemticos o con lenguajes HDL depende del diseo implementado. Esto quiere decir que, ninguno de los dos mtodos es ms prctico o eciente para todos los circuitos lgicos que el otro, es ms, se podr encontrar unos circuitos que se manipulen mejor con VHDL que con esquemticos y viceversa.

En esta seccin se expresa de manera breve y general el procedimiento a seguir para crear e implementar un diseo digital a partir de Schematic (esquemtico) y VHDL (Very High Speed Integrated Circuit) del programa Xilinx ISE 10.1. III-A. Diseo de Un Circuito Digital con Modelos Esquemticos [3] 1. Crear el nuevo proyecto aplicando File New Project.... En el cuadro de dilogo New Project Wizard Create New Project se asigna el nombre al proyecto (Project name), el directorio en el cual se guardar el proyecto (Project location) y el tipo de fuente para el proyecto (Top-level source type) del cual se selecciona el modo Schematic para poder crear el circuito con modelos esquemticos. 2. En el cuadro de dilogo New Project Wizard - Device Properties se indican las caractersticas principales de la FPGA (Family, Device, Package, Speed) que se obtienen directamente del texto estampado sobre le encapsulado de la FPGA a implementar. Adems, se selecciona la herramienta de sntesis (Synthesis Tool), el simulador (Simulator), y el lenguaje que el diseador preera que representen los esquemticos (Preferred Language). 3. Hasta ahora se ha creado el proyecto. Lo que sigue es crear el diseo. Para ello se selecciona el tipo de fuente que se desea crear, lo cual se logra aplicando Project New Source. En el cuadro de dilogo New Source Wizard - Select Source Type se selecciona el tipo Schematic y se le asigna un nombre al archivo (File name) y la direccin del mismo (Location).

4. En el rea de trabajo (espacio blanco de la ventana) se podr "dibujar" el esquema del circuito lgico que se quiere implementar en la FPGA. Los smbolos se encuentran en la pestaa Symbols de la ventana acoplable Sources. Estos smbolos pueden ser los de puertas lgicas, comparadores, contadores, memorias, etc. Adems, para incluir los marcadores de entrada y salida se selecciona Add I/O Marker. 5. Una vez terminado el diseo del circuito lgico, se procede a guardarlo. Esta es un accin que se recomienda realizar constantemente.

III-C.

Sntesis e Implementacin [3]

III-B.

Diseo de Un Circuito Digital con VHDL [2]

1. Crear el nuevo proyecto aplicando File New Project.... En el cuadro de dilogo New Project Wizard Create New Project se asigna el nombre al proyecto (Project name), el directorio en el cual se guardar el proyecto (Project location) y el tipo de fuente para el proyecto (Top-level source type) del cual se selecciona el modo HDL (Hardware Description Language) para poder crear (posteriormente) el circuito con lenguaje VHDL el cual es un Lenguaje de descripcin de hardware. 2. En el cuadro de dilogo New Project Wizard - Device Properties se indican las caractersticas principales de la FPGA (Family, Device, Package, Speed) que se obtienen directamente del texto estampado sobre le encapsulado de la FPGA a implementar. Adems, se selecciona la herramienta de sntesis (Synthesis Tool), el simulador (Simulator), y el lenguaje que el diseador preera (Preferred Language). Para este caso se selecciona VHDL. 3. Hasta ahora se ha creado el proyecto. Lo que sigue es crear el diseo. Para ello se selecciona el tipo de fuente que se desea crear, lo cual se logra aplicando Project New Source. En el cuadro de dilogo New Source Wizard - Select Source Type se selecciona el tipo VHDL Module y se le asigna un nombre al archivo (File name) y la direccin del mismo (Location). 4. Ahora aparece el cuadro de dilogo New Source Wizard Dene Module. En l se asignan el nombre de la entidad, el nombre de la arquitectura de la entidad y los puertos de la entidad. 5. En el espacio de trabajo se debe realizar la descripcin VHDL; conformada por una cabecera, las libreras, la entidad y la arquitectura. 6. En VHDL, la entidad dene las entradas y salidas del circuito. La arquitectura describe la estructura, el funcionamiento o el comportamiento del circuito. 7. Para denir la arquitectura se describe primero el nombre y en seguida se indica a qu entidad pertenece. 8. Para comenzar a escribir dentro de la arquitectura se enuncia la instruccin Begin y a partir de all se incluyen las sentencias concurrentes del circuito a disear 9. Una vez terminado el diseo del circuito lgico, se procede a guardarlo.

1. Se selecciona de la pestaa Sources el chero creado (formato .sch). 2. Ahora se debe indicar los pines de la FPGA que se van a utilizar, a travs de la herramienta Xilinx PACE. Esto se hace desde la ventana de procesos (Processes), desplegando el men User Constraints y ejecutando el Floorplan Area / IO / Logic - Post-Sinthesis. Ya en el entorno de Xilinx PACE, se muestra la arquitectura de la FPGA (Architecture View), la asignacin de los pines (Package View) y una tabla (Desing Object List - I/O Pins) que menciona el nombre (I/O Name) y la direccin (I/O Direction) de los puertos a implementar. 3. Se procede a guardar dichas asignaciones en el Xilinx PACE. Volviendo al Xilinx ISE, se ejecuta el Congure Target Device.2 Si hecho esto, la ventana Processes muestra que la ejecucin ha sido correcta, ya se podr programar la FPGA. De lo contrario habra que corregir los errores presentados. III-D. Simulacin [1],[2],[3]

1. Una vez que se haya guardado el diseo, se asigna sources for: Behavioural Simulation y se selecciona el archivo de formato .sch en la ventana Sources. 2. En la ventana Processes, se ejecuta Create New Source. De ello aparecer el cuadro de dilogo New Source Wizard - Select Source Type, donde se crea el archivo de simulacin (indica al simulador qu valores toman las entradas en funcin del tiempo). Adems, se crea una nueva fuente seleccionando el tipo Test Bench Waveform (banco de pruebas). 3. En el cuadro de dilogo New Source Wizard - Associate Source, se selecciona el diseo a probar con el banco de pruebas. 4. En el cuadro de dilogo Initial Timing and Clock Wizard - Initialize Timing se indica que el circuito del diseo es combinacional (Combinatorial (or internal clock)). 5. El resultado es una ventana que muestra los puertos de entrada y salida (Vertical) y un diagrama de tiempo en cero (Horizontal). Se asignan los valores de los puertos de entrada y se graba el diagrama de tiempo obtenido (slo de entradas). 6. Para simularlo, en la ventana Source debe estar seleccionado el archivo de formato .tbw y en la ventana Processes se ejecuta Simulate Behavioral Model. Esto dar la orden para llevar a cabo la simulacin obteniendo los resultados en el diagrama de tiempo. III-E. Programacin de La FPGA [3]

1. Ubicados en la FPGA se quitan los tres jumpers de conguracin.

2 Como este paso ejecuta el Generate Programming File y a su vez el Programming File Generation Report, entonces permitir ejecutar la herramienta iMPACT lo que mostrar un ventana en la que se ofrecen varias opciones. Se deja la opcin congure devices using Boundary-Scan (JTAG) y Automatically connect to a cable and identify Boudary-Scan chain.

2. Se conecta el extremo paralelo del cable JTAG al puerto paralelo del ordenador y el otro extremo al conector JTAG de la tarjeta. 3. Se conecta el cable de alimentacin. Lo cual produce que se encienda el LED de encendido de la tarjeta que se est implementando. 4. Desde el Xilinx ISE se ha ejecutado la herramienta iMPACT3 , la cual procede a identicar la placa por medio del protocolo Boundary-Scan (JTAG). Para la FPGA hay que asignar el chero creado en formato .bit. Luego se procede a programar la FPGA haciendo click derecho sobre el bloque que la representa. Esto hace que se despliegue un men del cual se selecciona Program. 5. Se Observa la tarjeta y se comprueba el resultado de la programacin.

Figura 2.

Simulacin del sistema lgico descrito en la g. 1.

V-B. IV. E QUIPO I MPLEMENTADO

Sistema Lgico

Segn la g. 3 las funciones generadas para las salidas S0, S1, S2 y S3 son: S0 = A0 A1 S1 = A0 A1 S2 = A0 A1 S3 = A0 A1 (1) (2) (3) (4)

Computadora. Herramienta de simulacin Xilinx WebPack 10.1. Tarjeta PEGASUS de Digilent. Cable d conexin JTAG. Cable de alimentacin para la PEGASUS.

V. V-A.

D ESARROLLO DE LA P RCTICA

Puertas Lgicas

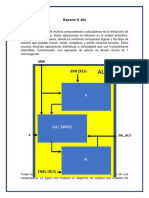

La g. 1 muestra el programa que se ha elaborado en cdigo VHDL para las puertas lgicas AND, OR, NOT, XOR y XNOR. Se anota que el cdigo se puede reducir si se considera que hayan slo dos entradas. Sin embargo, el diseo establece que cada compuerta posea sus propias entradas. La simulacin del cdigo de la g. 1 se muestra en la g. V-A.

De modo que el cdigo VHDL para el diagrama lgico de la g. 3 es como se muestra en la g.V-B. La simulacin del cdigo de la g. V-B y por ende, de la g. 3, se muestra en la g. V-B

Figura 1. XNOR.

Cdigo VHDL para las puertas lgicas AND, OR, NOT, XOR y

Figura 3.

3 Como

Circuito lgico de la sub-seccin V-B.

se explica en el pie de pgina2

[3] Universidad Rey Jaan Carlos, "Encender Un LED", Universidad Rey Juan Carlos.

Figura 4.

Cdigo VHDL para el circuito de la g. 3.

Figura 5. V-B.

Simulacin del sistema lgico descrito en la g. 3 y en la g.

VI.

C ONCLUSIONES

La decisin de trabajar con esquemticos o con lenguajes HDL depende del diseo implementado. Esto quiere decir que, ninguno de los dos mtodos es ms prctico o eciente para todos los circuitos lgicos que el otro, es ms, se podr encontrar unos circuitos que se manipulen mejor con VHDL que con esquemticos y viceversa. El estilo de programacin DataFlow permite tener mayor visibilidad de la funcin lgica que representa el circuito implementado. El VHDL no distingue entre maysculas y minsculas. Si se quiere hacer referencia al tipo de dato STD_LOGIC, se debe incluir la norma IEEE 1164. De lo contrario, si se quiere hacer referencia al tipo de dato BIT, se debe incluir la norma IEEE 1076. La tarjeta PEGASUS permite implementar 8 LEDs y un display de 7 segmentos de 4 dgitos como puertos de salida (O marker); y 8 interruptores y 4 pulsadores como puertos de entrada (I marker). VII. R EFERENCIAS

[1] Stephen Brown and Zvonko Vranesic, Fundamentos de Lgica Digital con Diseo VHDL, Segunda ed. Mxico: McGraw-Hill/Interamricana Editores, S.A. de C.V., 2006. [2] John Jairo Ramirez Mateus, "Introduccin al Lenguaje VHDL," Universidad Francisco de Paula Santander, San Jos de Ccuta, Gua de laboratoio.

S-ar putea să vă placă și

- Examen Diagnostico-Juan Carlos Gonzalez GutierrezDocument4 paginiExamen Diagnostico-Juan Carlos Gonzalez GutierrezJuan Carlos Gonzalez GutierrezÎncă nu există evaluări

- Integrados Apoyo 8086Document2 paginiIntegrados Apoyo 8086Fernando PantusinÎncă nu există evaluări

- Notas Diseño Logico UAM AzcapotzalcoDocument321 paginiNotas Diseño Logico UAM AzcapotzalcoLeonardo Vinicio Olarte CarrilloÎncă nu există evaluări

- Introduccion Al Ensamblador Emu8086Document9 paginiIntroduccion Al Ensamblador Emu8086Ariel Matos SantosÎncă nu există evaluări

- Tarea 2Document13 paginiTarea 2yimmyÎncă nu există evaluări

- Práctica1 MYMDocument15 paginiPráctica1 MYMEnedino Torres100% (1)

- Historia de Los MicroprocesadoresDocument15 paginiHistoria de Los MicroprocesadoresJaneth QuicoÎncă nu există evaluări

- Introducción A VHDLDocument32 paginiIntroducción A VHDLafgr1990Încă nu există evaluări

- Practica 9 Laboratorio de Diseño Lógico VHDLDocument6 paginiPractica 9 Laboratorio de Diseño Lógico VHDLPaco VeggitoÎncă nu există evaluări

- Preguntas Capitulo 1 Lengiaje de InterfazDocument2 paginiPreguntas Capitulo 1 Lengiaje de InterfazJasiel MolinaÎncă nu există evaluări

- Generador de RelojDocument6 paginiGenerador de RelojRicardo Jarquin AndurayÎncă nu există evaluări

- Conta Int II - Eq. 1Document14 paginiConta Int II - Eq. 1Omar QuirozÎncă nu există evaluări

- Reporte de Laboratorio Microprocesador 8086 PDFDocument10 paginiReporte de Laboratorio Microprocesador 8086 PDFCarlos ConradoÎncă nu există evaluări

- Manual de Practicas de MicroprocesadoresDocument54 paginiManual de Practicas de MicroprocesadoresaisenyÎncă nu există evaluări

- Proyecto de Programables Control de TemperaturaDocument49 paginiProyecto de Programables Control de TemperaturaCarlos ArriazaÎncă nu există evaluări

- 8284 Clock GeneratorDocument4 pagini8284 Clock GeneratorKennyi Aro ApazaÎncă nu există evaluări

- Protocolo BFDDocument49 paginiProtocolo BFDoalabiÎncă nu există evaluări

- Controlador 8288Document3 paginiControlador 8288Kevin Vladimir CarrilloÎncă nu există evaluări

- UPM - Introducción Al Lenguaje VHDLDocument153 paginiUPM - Introducción Al Lenguaje VHDLAldoAxel100% (3)

- Estructura de Un Programa en EnsambladorDocument21 paginiEstructura de Un Programa en EnsambladorAzmir Jimenez100% (1)

- Practica 10 Laboratorio de Diseño LógicoDocument6 paginiPractica 10 Laboratorio de Diseño LógicoPaco VeggitoÎncă nu există evaluări

- PROYECTO FINAL Elizabeth Moya DiagnósticoDocument11 paginiPROYECTO FINAL Elizabeth Moya DiagnósticoraulÎncă nu există evaluări

- Introduccion A Los Microcontroladores PDFDocument17 paginiIntroduccion A Los Microcontroladores PDFMaximiliano GiniÎncă nu există evaluări

- Experimento de Electrónica Con Componente 74HC595Document11 paginiExperimento de Electrónica Con Componente 74HC595Josemaría VilledaÎncă nu există evaluări

- U de G - Curso de VHDLDocument113 paginiU de G - Curso de VHDLAldoAxel100% (9)

- Modos de Direccionamiento en MCDocument7 paginiModos de Direccionamiento en MCLarry Fjc100% (1)

- Examen PrincipalasdDocument10 paginiExamen PrincipalasdJosé Ignacio GunshaÎncă nu există evaluări

- Entrenamiento Ignition CoreDocument58 paginiEntrenamiento Ignition CoreMiguelÎncă nu există evaluări

- Problemas de Sincronización de ProcesosDocument12 paginiProblemas de Sincronización de ProcesosLucasÎncă nu există evaluări

- Ejercicios Básicos Emu8086 - 2Document9 paginiEjercicios Básicos Emu8086 - 2kenyvitÎncă nu există evaluări

- Practica U AluDocument5 paginiPractica U AluAmigos LolerosÎncă nu există evaluări

- Analisis de Componentes CpuDocument16 paginiAnalisis de Componentes CpuJesús Melchor Hau NohÎncă nu există evaluări

- PRESENTACIÓN Introducción Al Lenguaje EnsambladorDocument36 paginiPRESENTACIÓN Introducción Al Lenguaje EnsambladorRaciel VillagranaÎncă nu există evaluări

- Maquinas de Estado Con VHDLDocument20 paginiMaquinas de Estado Con VHDLMiguel Andrés Fino100% (2)

- Administracion de Redes - DNSDocument8 paginiAdministracion de Redes - DNSYohany Enrique ORTIZ ACOSTAÎncă nu există evaluări

- Brazo RoboticoDocument9 paginiBrazo RoboticoDANIEL VALERIO100% (2)

- Depuracion VTPDocument4 paginiDepuracion VTPLili HernandezÎncă nu există evaluări

- Guía de Instalación de NASM y SASMDocument19 paginiGuía de Instalación de NASM y SASMEdgar SalazarÎncă nu există evaluări

- Estructura y Funcionamiento de La CpuDocument6 paginiEstructura y Funcionamiento de La CpuJose BanquezÎncă nu există evaluări

- UAM Practica 7laboratorio de Diseño Lógico VHDLDocument4 paginiUAM Practica 7laboratorio de Diseño Lógico VHDLPaco Veggito100% (1)

- Proceso de Instalación ISE de XilinxDocument14 paginiProceso de Instalación ISE de Xilinxsilvana_bgÎncă nu există evaluări

- PROGRAMACIÓN CON MPI y OPENMP Cluster - OdpDocument270 paginiPROGRAMACIÓN CON MPI y OPENMP Cluster - OdpkastoloÎncă nu există evaluări

- ArduinoDocument14 paginiArduinombomfim432Încă nu există evaluări

- Investigacion U3 MovilesDocument10 paginiInvestigacion U3 MovilesRick Ramon AÎncă nu există evaluări

- Historia y Evolucion de Los MicroprocesadoresDocument24 paginiHistoria y Evolucion de Los MicroprocesadoresCoronadoVanessa100% (1)

- Trabajo Del Capitulo 7 Sistemas OperativosDocument15 paginiTrabajo Del Capitulo 7 Sistemas OperativosKenny BaezÎncă nu există evaluări

- 26.1.7 Lab - Snort and Firewall RulesDocument9 pagini26.1.7 Lab - Snort and Firewall RulesjuanÎncă nu există evaluări

- Practica de Laboratorio 4.4.3 Configuracion Del VTP para Solucionar ProblemasDocument20 paginiPractica de Laboratorio 4.4.3 Configuracion Del VTP para Solucionar ProblemasJames CazasÎncă nu există evaluări

- SD1 PR2 Introduccion VHDL 2023-1Document27 paginiSD1 PR2 Introduccion VHDL 2023-1Antonio MuroÎncă nu există evaluări

- Manual ISEDocument22 paginiManual ISEerick mondragon quintana0% (1)

- VHDL ProyectosDocument92 paginiVHDL ProyectosLander Arturo Rubio JuarezÎncă nu există evaluări

- Quartus Compuerta XnorDocument24 paginiQuartus Compuerta XnorDavid Gamboa GuzmánÎncă nu există evaluări

- Xilinx ISE TutorialDocument30 paginiXilinx ISE TutorialJavier Balam BasoraÎncă nu există evaluări

- L11 - FPGA (Casi Terminado)Document21 paginiL11 - FPGA (Casi Terminado)Gonzalo PereyraÎncă nu există evaluări

- Practica 101 Compuertas Logicas BasicasDocument4 paginiPractica 101 Compuertas Logicas BasicasPaola VazquezÎncă nu există evaluări

- Practicas RealizadasDocument28 paginiPracticas RealizadasRaysha Ross Enciso RaveloÎncă nu există evaluări

- Mux2a1 TutorialDocument30 paginiMux2a1 TutorialelkillyÎncă nu există evaluări

- Paper HDLDocument5 paginiPaper HDLdispo3cÎncă nu există evaluări

- VIVADODocument23 paginiVIVADODaniela Galvan ChavezÎncă nu există evaluări

- Todo Del VHDLDocument16 paginiTodo Del VHDLman soloÎncă nu există evaluări

- La VirginidadDocument13 paginiLa VirginidadCamilo RolónÎncă nu există evaluări

- 8 ClaseDocument3 pagini8 ClaseCamilo RolónÎncă nu există evaluări

- Concept PaperDocument13 paginiConcept PaperCamilo RolónÎncă nu există evaluări

- Concept PaperDocument18 paginiConcept PaperCamilo RolónÎncă nu există evaluări

- La Virginidad y La Primera VezDocument1 paginăLa Virginidad y La Primera VezCamilo RolónÎncă nu există evaluări

- Arreglos 3Document17 paginiArreglos 3Camilo RolónÎncă nu există evaluări

- Acuerdos Comerciales y de InversiónDocument3 paginiAcuerdos Comerciales y de InversiónCamilo RolónÎncă nu există evaluări

- Arreglo SDocument12 paginiArreglo SCamilo RolónÎncă nu există evaluări

- Comercio InternacionalDocument39 paginiComercio InternacionalCamilo RolónÎncă nu există evaluări

- Incoterm 2010Document52 paginiIncoterm 2010Miguel Huamani RiveraÎncă nu există evaluări

- Arreglo 2Document1 paginăArreglo 2Camilo RolónÎncă nu există evaluări

- Arreglo 2Document1 paginăArreglo 2Camilo RolónÎncă nu există evaluări

- Formulas de ÁlgebraDocument2 paginiFormulas de ÁlgebraCamilo RolónÎncă nu există evaluări

- Teoria Analizador de EspectrosDocument4 paginiTeoria Analizador de EspectrosLuis Jerónimo Terán Yajurez100% (1)

- Algoritmo de Complemento A 2Document2 paginiAlgoritmo de Complemento A 2Diego Andres ParadaÎncă nu există evaluări

- Solucion Segundo Previo I 2012Document3 paginiSolucion Segundo Previo I 2012Camilo RolónÎncă nu există evaluări

- Autoevaluación - Moneda y BancaDocument22 paginiAutoevaluación - Moneda y BancaCamilo RolónÎncă nu există evaluări

- Algoritmo de Complemento A 2Document2 paginiAlgoritmo de Complemento A 2Diego Andres ParadaÎncă nu există evaluări

- Historia Del Sistema BinarioDocument3 paginiHistoria Del Sistema BinarioSilva SilvaÎncă nu există evaluări

- Prolog - Jesus Abimelec GBDocument5 paginiProlog - Jesus Abimelec GBJesus A. GonzalezÎncă nu există evaluări

- Apuntes de Clase 27 FebreroDocument103 paginiApuntes de Clase 27 FebreroAndres Salcedo MonterrosoÎncă nu există evaluări

- LÓGICA DEL OBJETO Romulo Lander PDFDocument189 paginiLÓGICA DEL OBJETO Romulo Lander PDFRoberto Rojas AracenaÎncă nu există evaluări

- Consideraciones para La Construccion de Objetivos EducacionalesDocument3 paginiConsideraciones para La Construccion de Objetivos EducacionalesCarvajal OrianaÎncă nu există evaluări

- Comprensión LectoraDocument4 paginiComprensión LectoraNirma Yepes SanchezÎncă nu există evaluări

- 2 Parcial, Cultura y SubjetividadDocument2 pagini2 Parcial, Cultura y SubjetividadVirginia GarciaÎncă nu există evaluări

- Constructivismo SocialDocument1 paginăConstructivismo SocialMiguel GuamánÎncă nu există evaluări

- 01 Explorando El Reto V2Document10 pagini01 Explorando El Reto V2Juan José Suárez YupanquiÎncă nu există evaluări

- LiteratuaDocument40 paginiLiteratuaAlonso Canchi Ramirez0% (1)

- Camino Al MediodiaDocument12 paginiCamino Al MediodiaAdriana FloresÎncă nu există evaluări

- 1 Pedro 3. 13-17Document3 pagini1 Pedro 3. 13-17marcos miguel salazar herreraÎncă nu există evaluări

- Múltiplos y DivisoresDocument18 paginiMúltiplos y DivisoresLourdes Mamani SaavedraÎncă nu există evaluări

- 07 Intro EDP y Separacion VariablesDocument32 pagini07 Intro EDP y Separacion VariablesCarla RamirezÎncă nu există evaluări

- Perfil Del Egrsado de Segundo GradoDocument3 paginiPerfil Del Egrsado de Segundo GradoLennys Goodyn100% (2)

- Intrumentos MusicalesDocument11 paginiIntrumentos MusicalesJeffer GarciaÎncă nu există evaluări

- El Matriarcalismo Vasco - Ciencia y ExistenciaDocument24 paginiEl Matriarcalismo Vasco - Ciencia y Existenciaraymondnomyar100% (1)

- La Última Ilusión de Don Juan AutorarmexDocument4 paginiLa Última Ilusión de Don Juan AutorarmexArmando LopezÎncă nu există evaluări

- QF Rubrica Exposicion Oral PDFDocument2 paginiQF Rubrica Exposicion Oral PDFHupal RafaelÎncă nu există evaluări

- MATEMATICAS: Aritmética, Algebra, y TrigonometriaDocument119 paginiMATEMATICAS: Aritmética, Algebra, y TrigonometriaRossana GallardoÎncă nu există evaluări

- TP1 Ej.9 TABLAS DE VERDAD - UnahurDocument4 paginiTP1 Ej.9 TABLAS DE VERDAD - UnahurdramaqueenÎncă nu există evaluări

- Microsoft Project 2Document32 paginiMicrosoft Project 2andrea galindoÎncă nu există evaluări

- Oratoria ParlamentariaDocument92 paginiOratoria ParlamentariaFrank Padilla AguilarÎncă nu există evaluări

- I SEM 2 Silabo Logica y FuncionesDocument3 paginiI SEM 2 Silabo Logica y FuncionesInperial CelendinÎncă nu există evaluări

- Teología Pastoral IDocument20 paginiTeología Pastoral IPonc Capell100% (1)

- Reparacion de Tablas PDFDocument22 paginiReparacion de Tablas PDFWilliam Fernando Arenas AlvarezÎncă nu există evaluări

- 202 Software Testing Interview Questions and Answers PDFDocument56 pagini202 Software Testing Interview Questions and Answers PDFFabianAcuñaÎncă nu există evaluări

- Castellano La Dramática ClásicaDocument3 paginiCastellano La Dramática ClásicaBarbara Carpio GonzalezÎncă nu există evaluări

- ArgumentacionDocument11 paginiArgumentacionAle AlejandraÎncă nu există evaluări

- Evaluacion de Lenguan2Document2 paginiEvaluacion de Lenguan2Natalia VerdiniÎncă nu există evaluări