Documente Academic

Documente Profesional

Documente Cultură

Lecture 410 - High-Speed Comparators: (READING: AH - 483-488) Objective

Încărcat de

Van Nguyen Huu VanDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Lecture 410 - High-Speed Comparators: (READING: AH - 483-488) Objective

Încărcat de

Van Nguyen Huu VanDrepturi de autor:

Formate disponibile

Lecture 410 High-Speed Comparators (4/8/02)

Page 410-1

LECTURE 410 HIGH-SPEED COMPARATORS

(READING: AH 483-488) Objective The objective of this presentation is: 1.) Show how to achieve high-speed comparators Outline Concepts of high-speed comparators Amplifier-latch comparators Summary

ECE 6412 - Analog Integrated Circuit Design - II Lecture 410 High-Speed Comparators (4/8/02)

P.E. Allen - 2002 Page 410-2

Conceptual Illustration of a Cascaded Comparator How does a cascaded, high-speed comparator work?

A0 sT+1 A0 sT+1 A0 sT+1 A0 sT+1 A0 sT+1 A0 sT+1

Linear small signal

Linear small signal

Linear & large signal

Large signal small C

Large signal bigger C

Large signal big C

Fig. 8.6-1

Assuming a small overdrive, 1.) The initial stage build the driving capability. 2.) The latter stages swing rail-to-rail and build the ability to quickly charge and discharge capacitance.

ECE 6412 - Analog Integrated Circuit Design - II

P.E. Allen - 2002

Lecture 410 High-Speed Comparators (4/8/02)

Page 410-3

Minimizing the Propagation Delay Time in Comparators Fact: The input signal is equal to Vin(min) for worst case Amplifiers have a step response with a negative argument in the exponential Latches have a step response with a positive argument in the exponential Result: Use a cascade of linear amplifier to quickly build up the signal level and apply this amplified signal level to a latch for quick transition to the full binary output swing. Illustration of a preamplifier and vout latch cascade: VOH Minimization of tp: Latch Q. If the preamplifer consists of n stages of gain A having a singlePreamplifier pole response, what is the value of n and A that gives minimum VX propagation delay time? t1 t2 A. n = 6 and A = 2.62 but this is a VOL t very broad minimum and n is Fig. 8.6-2 usually 3 and A 6-7 to save area.

ECE 6412 - Analog Integrated Circuit Design - II Lecture 410 High-Speed Comparators (4/8/02) P.E. Allen - 2002 Page 410-4

Fully Differential, Three-Stage Amplifier and Latch Comparator Circuit:

FB Reset Reset C1 Cv2 C2 Cv1 + -+ Reset FB Cv4 FB Cv3 FB + -+ Reset Cv6 FB Cv5 FB + -+ Reset

+ Latch vout Clock

Fig. 8.6-3

+ vin -

Comments: Autozero and reset phase followed by comparison phase More switches are needed to accomplish the reset and autozero of all preamplifiers simultaneously Can run as high as 100Msps

ECE 6412 - Analog Integrated Circuit Design - II

P.E. Allen - 2002

Lecture 410 High-Speed Comparators (4/8/02)

Page 410-5

Preamplifier and Latch Circuits Gain: gm1 gm2 Av = - gm3 = - gm4 = Dominant Pole: gm3 gm4 |pdominant| = C = C where C is the capacitance seen from the output nodes to ground. KN(W1/L1) Kp(W3/L3)

FB M3

VDD

M4 Q Reset FB M1 M2 M5 M6 Q

Latch Enable If (W1/L1)/(W3/L3) = 100 and the bias current is 100A, then A = -3.85 Latch Preamplifier and the bandwidth is 15.9MHz if C = 0.5pF. VBias Comments: Fig. 8.6-4 If a buffer is used to reduce the output capacitance, one must take into account the loss of the buffer. The use of a preamplifier before the latch reduces the latch offset by the gain of the preamplifier so that the offset is due to the preamplifier only.

ECE 6412 - Analog Integrated Circuit Design - II Lecture 410 High-Speed Comparators (4/8/02) P.E. Allen - 2002 Page 410-6

An Improved Preamplifier Circuit:

VDD

VBiasP vout- M5 M3 Reset FB M11 M7 vin+ M1 VBiasN M9 VBias M2 M10 M8 M4 M6

VBiasP vout+

M12

FB

vin-

Fig. 8.6-5

Gain: gm1 KN(W1/L1)I1 KN(W1/L1) Av = - gm3 = KP(W3/L3)I3 = KP(W3/L3) If I5 = 24I3, the gain is increased by a factor of 5

ECE 6412 - Analog Integrated Circuit Design - II

I5 1+I3

P.E. Allen - 2002

Lecture 410 High-Speed Comparators (4/8/02)

Page 410-7

Charge Transfer Preamplifier The preamplifier can be replaced by the charge transfer circuit shown.

vin=VREF VPR vin=VREF VPR vin = VREF+V

S2 vin-VT S1 CT CO + vout CT + vout =VPR -

VREF-VT+V + vout =VPR -CT V CO

CO

CT

CO

Charge transfer amplifier.

Precharge phase.

Amplification phase.

Fig. 8.6-6

Comments: Only positive values of voltage will be amplified. Large offset voltages result as a function of the subthreshold current.

ECE 6412 - Analog Integrated Circuit Design - II Lecture 410 High-Speed Comparators (4/8/02)

P.E. Allen - 2002 Page 410-8

A CMOS Charge Transfer Preamplifier Circuit:

VDD VDD CT vin S3 S1 M1 CO S1 M2 S3 S2 vout VPR

CT

Fig. 8.6-7

Comments: NMOS and PMOS allow both polarities of input CMOS switches along with dummy switches reduce the charge injection Switch S3 prevents the subthreshold current influence Used as a preamplifier in a comparator with 8-bit resolution at 20Msps and a power dissipation of less than 5W

ECE 6412 - Analog Integrated Circuit Design - II

P.E. Allen - 2002

Lecture 410 High-Speed Comparators (4/8/02)

Page 410-9

A High-Speed Comparator Circuit:

VDD Self-biased diff amp Output Driver Preamp vout vin+ vin-

IBias Latch

Fig. 8.6-8

Comments: Designed to have a tp = 10ns with a 5pF load and a 10mV overdrive Not synchronous Comparator gain is greater than 2000V/V and the quiescent current was 100A

ECE 6412 - Analog Integrated Circuit Design - II Lecture 410 High-Speed Comparators (4/8/02) P.E. Allen - 2002 Page 410-10

SUMMARY Types of Comparators Presented High-gain, open-loop Improved high-gain, open-loop, comparators Hysteresis Autozeroing Regenerative comparators Discrete-time comparators Performance Characterization Propagation delay time Binary output swing Input resolution and/or gain Input offset voltage Power dissipation Important Principles The speed of the comparator depends on the linear and slewing responses The dc input offset voltage depends on the matching and is reduced by autozeroing. Charge injection is the limit of autozeroing The comparator gain should be large enough for a binary output when vin = Vin(min) Cascaded comparators, the first stages should large GB and the last stages high SR

ECE 6412 - Analog Integrated Circuit Design - II P.E. Allen - 2002

S-ar putea să vă placă și

- Lecture 220 - Clock and Data Recovery Circuits - IiiDocument12 paginiLecture 220 - Clock and Data Recovery Circuits - IiiDDragos GeorgeÎncă nu există evaluări

- Modular Drives: Combivert F5Document32 paginiModular Drives: Combivert F5costam22Încă nu există evaluări

- Analog Circuit Design Volume 2: Immersion in the Black Art of Analog DesignDe la EverandAnalog Circuit Design Volume 2: Immersion in the Black Art of Analog DesignÎncă nu există evaluări

- v42 63Document5 paginiv42 63Bala KumarÎncă nu există evaluări

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsDe la EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsEvaluare: 3.5 din 5 stele3.5/5 (6)

- Irjet V4i4820Document10 paginiIrjet V4i4820aditya317crazyÎncă nu există evaluări

- 4Document5 pagini4Alsmany ArdabÎncă nu există evaluări

- Analog To Digital Converter in Wireless Local Area NetworkDocument29 paginiAnalog To Digital Converter in Wireless Local Area Networkkumarbsnsp0% (1)

- 52F5 07 2016Document32 pagini52F5 07 2016mamaligosu1Încă nu există evaluări

- EC2 Exp2 F09Document17 paginiEC2 Exp2 F09Nurul Hanim HashimÎncă nu există evaluări

- Fpga Based Multilevel Inverter DesignDocument18 paginiFpga Based Multilevel Inverter DesignmidhunÎncă nu există evaluări

- Topswitch: Designing Multiple Output Flyback Power Supplies WithDocument24 paginiTopswitch: Designing Multiple Output Flyback Power Supplies WithteomondoÎncă nu există evaluări

- How To Design A Driver Circuit For An Efficient Synchronous RectifierDocument20 paginiHow To Design A Driver Circuit For An Efficient Synchronous RectifiertongaiÎncă nu există evaluări

- LED Applications Design and Implementation of A Novel Bridgeless Interleaved SEPIC Converter ForDocument5 paginiLED Applications Design and Implementation of A Novel Bridgeless Interleaved SEPIC Converter ForArun KumarÎncă nu există evaluări

- IPM ModelDocument66 paginiIPM Modelbobo249Încă nu există evaluări

- Design and Simulation of Modified Ultra Low Power CMOS Comparator For Sigma Delta ModulatorDocument3 paginiDesign and Simulation of Modified Ultra Low Power CMOS Comparator For Sigma Delta ModulatorASHFAQ AHMEDÎncă nu există evaluări

- ABB DrivesDocument36 paginiABB DrivesGurmeet SinghÎncă nu există evaluări

- Ece - Mits.ac - in - Electronic Circuit Analysis Lab ManualDocument51 paginiEce - Mits.ac - in - Electronic Circuit Analysis Lab ManualDileep KumarÎncă nu există evaluări

- Slyt 802Document8 paginiSlyt 802batuhanÎncă nu există evaluări

- Development of New AC To DC Converters For EHVDocument5 paginiDevelopment of New AC To DC Converters For EHVMouliÎncă nu există evaluări

- LM5085 PDFDocument8 paginiLM5085 PDFSreeram PanigrahiÎncă nu există evaluări

- A Low-Power 1-V Supply Dynamic ComparatorDocument4 paginiA Low-Power 1-V Supply Dynamic Comparator22pimt01Încă nu există evaluări

- CycloconverterDocument23 paginiCycloconverterSatpute M.D.Încă nu există evaluări

- XC9235 - 36 - 37 DCDC Study GuideDocument14 paginiXC9235 - 36 - 37 DCDC Study GuideTumenbayar LkhagvatserenÎncă nu există evaluări

- Rail SFC Light - Tech Note - RevC - ENDocument7 paginiRail SFC Light - Tech Note - RevC - ENmhd.amin4Încă nu există evaluări

- Irjet V8i5487Document3 paginiIrjet V8i5487Sado HusseinYusufÎncă nu există evaluări

- Stick, TIG, Flux-Cored, Gouging: ProcessesDocument4 paginiStick, TIG, Flux-Cored, Gouging: ProcessesMostafa ElabdÎncă nu există evaluări

- 500w Power Amplifier Circuit DiagramDocument6 pagini500w Power Amplifier Circuit DiagramJoão Alberto0% (1)

- Electric Motor CatalogueDocument20 paginiElectric Motor Cataloguevipulpanchotiya100% (1)

- PDFDocument44 paginiPDFjalilemadiÎncă nu există evaluări

- IEC61727 - Characteristics of The Utility Interface - Design Qualification For InvertorsDocument28 paginiIEC61727 - Characteristics of The Utility Interface - Design Qualification For InvertorsCliffÎncă nu există evaluări

- IEC61727 - Characteristics of The Utility Interface - Design Qualification For Invertors PDFDocument28 paginiIEC61727 - Characteristics of The Utility Interface - Design Qualification For Invertors PDFCliffÎncă nu există evaluări

- Chapter 8 - Cmos ComparatorsDocument39 paginiChapter 8 - Cmos Comparatorsfabio-delima8012100% (1)

- Single-Stage Bridgeless AC-DC PFC Converter Using A Lossless Passive Snubber and Valley SwitchingDocument9 paginiSingle-Stage Bridgeless AC-DC PFC Converter Using A Lossless Passive Snubber and Valley SwitchingAshwin Kumar JÎncă nu există evaluări

- A High Efficiency Bridgeless Flyback PFC Converter For Adapter ApplicationDocument5 paginiA High Efficiency Bridgeless Flyback PFC Converter For Adapter ApplicationAshwin Kumar JÎncă nu există evaluări

- A 10-Bit 5 Msample/s ADC: Two-Step FlashDocument9 paginiA 10-Bit 5 Msample/s ADC: Two-Step FlashRaghav ChaudharyÎncă nu există evaluări

- UploDocument116 paginiUplobashasvuceÎncă nu există evaluări

- Ec 262 Pspice ManualDocument69 paginiEc 262 Pspice ManualRama KrishnaÎncă nu există evaluări

- Inversores Keb - Homag PDFDocument32 paginiInversores Keb - Homag PDFeliasÎncă nu există evaluări

- Finfet Based Flash Adc PDFDocument4 paginiFinfet Based Flash Adc PDFJam 234Încă nu există evaluări

- Acs2000 PDFDocument42 paginiAcs2000 PDFHans Morten100% (1)

- Integrated Converter For Plug-In Electric VehiclesDocument17 paginiIntegrated Converter For Plug-In Electric VehiclesY SAI SREELATHAÎncă nu există evaluări

- ATV71-61 Active Front End V2 S09Document32 paginiATV71-61 Active Front End V2 S09shaikhsajid242Încă nu există evaluări

- A New Topology For Unipolar Brushless DC Motor DriveDocument55 paginiA New Topology For Unipolar Brushless DC Motor Drivesrikaanth06Încă nu există evaluări

- UploDocument115 paginiUplobashasvuceÎncă nu există evaluări

- ECD Lab NEC 752Document17 paginiECD Lab NEC 752Ravindra Kumar0% (1)

- 123/145 KV SF Gas Insulated Switchgear: Three-Phase Common Enclosure Gas Insulated Switch Gear (Both Side CT Type)Document8 pagini123/145 KV SF Gas Insulated Switchgear: Three-Phase Common Enclosure Gas Insulated Switch Gear (Both Side CT Type)nowoman20103990Încă nu există evaluări

- Ijeet: International Journal of Electrical Engineering & Technology (Ijeet)Document11 paginiIjeet: International Journal of Electrical Engineering & Technology (Ijeet)IAEME PublicationÎncă nu există evaluări

- Kec - 452 - Analog - Circuit - Lab Manual - FinalDocument40 paginiKec - 452 - Analog - Circuit - Lab Manual - FinalAnurag siwachÎncă nu există evaluări

- Ofc Lab Manual 2Document21 paginiOfc Lab Manual 2Shobhit JainÎncă nu există evaluări

- Oil, Gas and Petrochemicals IEC 61850: Per Arind Berg, AEO, 2011-01-27Document26 paginiOil, Gas and Petrochemicals IEC 61850: Per Arind Berg, AEO, 2011-01-27Hugo Hernandez JuarezÎncă nu există evaluări

- Design of A Fully Differential High-Speed High-Precision AmplifierDocument10 paginiDesign of A Fully Differential High-Speed High-Precision Amplifierkirkland1337Încă nu există evaluări

- Flyback Power Supply Development - Part IIIDocument4 paginiFlyback Power Supply Development - Part IIIMuhammad Saqib AliÎncă nu există evaluări

- A DC-DC Converter With High Voltage Gain and Two Input Boost StagesDocument10 paginiA DC-DC Converter With High Voltage Gain and Two Input Boost Stagesnadeemq_0786Încă nu există evaluări

- Htl-6602 Pcn1600 VHF TXDocument9 paginiHtl-6602 Pcn1600 VHF TXabhinavthedhimanÎncă nu există evaluări

- Design and Simulation of Power ConvertersDocument48 paginiDesign and Simulation of Power ConvertersHoang NgoÎncă nu există evaluări

- Voltage To Frequency Converter Folosind Ci 555 TimerDocument11 paginiVoltage To Frequency Converter Folosind Ci 555 TimerAl ZanoagaÎncă nu există evaluări

- Oltc FundamentalDocument118 paginiOltc Fundamentalusefi100% (1)

- Unit 12: The Right Approach: 1 ReadingDocument5 paginiUnit 12: The Right Approach: 1 ReadingVan Nguyen Huu VanÎncă nu există evaluări

- Unit 9 8231Document7 paginiUnit 9 8231Van Nguyen Huu VanÎncă nu există evaluări

- Unit 10: Hard To Believe?: Bi Li:vDocument5 paginiUnit 10: Hard To Believe?: Bi Li:vVan Nguyen Huu VanÎncă nu există evaluări

- L330 LowPowerOpAmps 2UPDocument7 paginiL330 LowPowerOpAmps 2UPVan Nguyen Huu VanÎncă nu există evaluări

- Lecture 230 - 741 Frequency Response: (READING: GHLM - 537-544) ObjectiveDocument5 paginiLecture 230 - 741 Frequency Response: (READING: GHLM - 537-544) ObjectiveVan Nguyen Huu VanÎncă nu există evaluări

- Lecture 250 - Introduction To Feedback Concepts: (READING: GHLM - 553-563) ObjectiveDocument8 paginiLecture 250 - Introduction To Feedback Concepts: (READING: GHLM - 553-563) ObjectiveVan Nguyen Huu VanÎncă nu există evaluări

- L170 IntuitiveAnalysis 2UPDocument10 paginiL170 IntuitiveAnalysis 2UPVan Nguyen Huu VanÎncă nu există evaluări

- L100 MultistageFreq II (2UP)Document6 paginiL100 MultistageFreq II (2UP)Van Nguyen Huu VanÎncă nu există evaluări

- Lecture 070 - Single-Stage Frequency Response - I: (READING: GHLM - 488-504) ObjectiveDocument6 paginiLecture 070 - Single-Stage Frequency Response - I: (READING: GHLM - 488-504) ObjectiveVan Nguyen Huu VanÎncă nu există evaluări

- CBSE Sample Paper Class 7 Maths Set 1 MergedDocument21 paginiCBSE Sample Paper Class 7 Maths Set 1 MergedNAMANÎncă nu există evaluări

- Nünning - Literary Studies. Theories, Models and Methods (Excerpts)Document2 paginiNünning - Literary Studies. Theories, Models and Methods (Excerpts)E KÎncă nu există evaluări

- Elementary Introduction To Stochastic Interest Rate ModelingDocument15 paginiElementary Introduction To Stochastic Interest Rate ModelingIgor PavlovÎncă nu există evaluări

- Serial ATA II: Extensions To Serial ATA 1.0aDocument110 paginiSerial ATA II: Extensions To Serial ATA 1.0aRaj Shekhar ReddyÎncă nu există evaluări

- FenestrationDocument14 paginiFenestrationKing AravindÎncă nu există evaluări

- Deepwater Development OverviewDocument11 paginiDeepwater Development OverviewBarry HiiÎncă nu există evaluări

- The Salvation Army Chikankata College of Biomedical Sciences The Ministry of HealthDocument7 paginiThe Salvation Army Chikankata College of Biomedical Sciences The Ministry of HealthChabala Ng'anduÎncă nu există evaluări

- Tugas Paper Mekanika PatahanDocument1 paginăTugas Paper Mekanika PatahanRahmandhika Firdauzha Hary HernandhaÎncă nu există evaluări

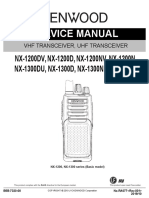

- Service Manual: NX-1200DV, NX-1200D, NX-1200NV, NX-1200N, NX-1300DU, NX-1300D, NX-1300NU, NX-1300NDocument86 paginiService Manual: NX-1200DV, NX-1200D, NX-1200NV, NX-1200N, NX-1300DU, NX-1300D, NX-1300NU, NX-1300NMarcelo LilloÎncă nu există evaluări

- 3G Cluster Pre-OptimizationDocument41 pagini3G Cluster Pre-OptimizationAditya NamaÎncă nu există evaluări

- Important Gate Topics For Mechanical Engineering (Me) - Mechanical Gate Basic ConceptsDocument9 paginiImportant Gate Topics For Mechanical Engineering (Me) - Mechanical Gate Basic ConceptsSatheesh ChandranÎncă nu există evaluări

- ZVT ECR Interface SpecificationDocument179 paginiZVT ECR Interface Specificationcristi_pet4742Încă nu există evaluări

- Soy Sauce Production FinalDocument40 paginiSoy Sauce Production Finalafidah99Încă nu există evaluări

- P521 OrderForm - V18 - 09 - 2014Document11 paginiP521 OrderForm - V18 - 09 - 2014Pakde NdokÎncă nu există evaluări

- J. Biol. Chem.-1917-Currie-15-37Document26 paginiJ. Biol. Chem.-1917-Currie-15-37NataliaCampeloÎncă nu există evaluări

- MGB 2Document9 paginiMGB 2afacanevrimÎncă nu există evaluări

- Operation & Maintenance Manual For Hypercomp CNG Compressor Model 3W815Document208 paginiOperation & Maintenance Manual For Hypercomp CNG Compressor Model 3W815Asim Riaz80% (5)

- Yuva Nikhil Reddy LonkaDocument9 paginiYuva Nikhil Reddy LonkaankulÎncă nu există evaluări

- Unit 6-Fluid MechanicsDocument25 paginiUnit 6-Fluid MechanicsApechRanger100% (4)

- CTS+ Configuration For PI 7.3Document23 paginiCTS+ Configuration For PI 7.3RaQÎncă nu există evaluări

- Mivec FaultDocument1 paginăMivec Faultbjr6627Încă nu există evaluări

- Oscillating Universe TheoryDocument1 paginăOscillating Universe TheoryArabella BasilioÎncă nu există evaluări

- Sqlassignment 03Document3 paginiSqlassignment 03pokegex798Încă nu există evaluări

- Conduction Convection RadiationDocument23 paginiConduction Convection Radiationsuhaila bakarÎncă nu există evaluări

- A Presentation On ER-DiagramDocument9 paginiA Presentation On ER-DiagramLee Kally100% (1)

- Respiratory System: StructureDocument29 paginiRespiratory System: StructureDr. Abir Ishtiaq100% (1)

- Arithmetic Progressons (Part-1)Document16 paginiArithmetic Progressons (Part-1)shambhaviÎncă nu există evaluări

- Class-X (Two Hours) : Section BDocument4 paginiClass-X (Two Hours) : Section Bsamanway_banerjeeÎncă nu există evaluări

- HSR 1.63 (For HYSYS V10.0)Document4 paginiHSR 1.63 (For HYSYS V10.0)Ba Jun Thối0% (1)