Documente Academic

Documente Profesional

Documente Cultură

El Módulo Adc de Los Avr PDF

Încărcat de

mi_papi0 evaluări0% au considerat acest document util (0 voturi)

410 vizualizări27 paginiTitlu original

EL MÓDULO ADC DE LOS AVR.pdf

Drepturi de autor

© © All Rights Reserved

Formate disponibile

PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

410 vizualizări27 paginiEl Módulo Adc de Los Avr PDF

Încărcat de

mi_papiDrepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 27

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 1

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELECTRICA Y ELECTRNICA

CURSO: MICROCONTROLADORES

MODULO ADC

ATMEGA8 - LENGUAJE C

PROFESOR: MSc ING. ASTOCONDOR VILLAR 1ACOB

CALLAO, ........... DEL ..............

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 2

EL MDULO ADC DE LOS AVR

Los AVR de la serie megaAVR tienen un ADC de aproximaciones sucesivas de 10 bits. Es uno

solo pero esta multiplexado para dar cabida hasta a 8 entradas analogicas. Se convierte solo una

entrada o la diIerencia de dos entradas analogicas a la vez.

Concretamente, los AVR de la serie A1megaXX4 cuentan con 8 canales de conversion, todos

ubicados en su puerto A. Por otro lado los AVR de la serie ATmegaXX8 destinan todo su

puerto C como canales de entrada del ADC.

El detalle con los ATmegaXX8 es que su puerto C solo tiene pines si vienen en empaque DIP

pero tiene 8 pines en los empaques TQFP y QFN/MLF. De modo que estos megaAJR pueden

tener u 8 canales de conversin dependiendo de su empaque.

Operacin del Mdulo ADC

En las aplicaciones ordinarias solo los registros ADCSRA y ADMUX son los que se manipulan

activamente. Los registros ADCH y ADCL son de solo lectura y como no tienen Iormato, basta

con recordar sus nombres.

ADCSRA. Es el principal registro de control y estado del ADC. Manipulando los bits

de este registro iniciamos la conversion, establecemos la velocidad de conversion o

elegimos el Iormato del resultado de la conversion. Veremos los detalles en adelante.

ADCSRB. Es el segundo registro de control y estado del ADC. Sus pocos bits

Iuncionales conIiguran el modo de conversiones automaticas y como ese modo es

raramente usado, el registro ADCSRB tampoco esta muy avistado en los programas.

Los viejos AVR no lo tienen.

ADCH y ADCL. Son los registros que almacenan el resultado de la conversion. Uno

guarda 8 bits y el otro los dos bits restantes. La Iorma como se distribuyen se debe

especiIicar con el bit ADLAR del registro ADMUX.

Para cuestiones de programacion estos registros se Iusionan para Iormar un unico

registro de 16 bits normalmente llamado ADC o ADCW.

ADMUX. Es el registro que selecciona el canal de conversion y establece los voltajes

de reIerencia.

DIDR0. Es tambien un nuevo registro no disponible en los viejos AVR. Su Iuncion es

desconectar los pines seleccionados como canales latentes del conversor para asi evitar

que se desgaste corriente en parte del circuito del ADC.

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 2

EL MDULO ADC DE LOS AVR

Los AVR de la serie megaAVR tienen un ADC de aproximaciones sucesivas de 10 bits. Es uno

solo pero esta multiplexado para dar cabida hasta a 8 entradas analogicas. Se convierte solo una

entrada o la diIerencia de dos entradas analogicas a la vez.

Concretamente, los AVR de la serie A1megaXX4 cuentan con 8 canales de conversion, todos

ubicados en su puerto A. Por otro lado los AVR de la serie ATmegaXX8 destinan todo su

puerto C como canales de entrada del ADC.

El detalle con los ATmegaXX8 es que su puerto C solo tiene pines si vienen en empaque DIP

pero tiene 8 pines en los empaques TQFP y QFN/MLF. De modo que estos megaAJR pueden

tener u 8 canales de conversin dependiendo de su empaque.

Operacin del Mdulo ADC

En las aplicaciones ordinarias solo los registros ADCSRA y ADMUX son los que se manipulan

activamente. Los registros ADCH y ADCL son de solo lectura y como no tienen Iormato, basta

con recordar sus nombres.

ADCSRA. Es el principal registro de control y estado del ADC. Manipulando los bits

de este registro iniciamos la conversion, establecemos la velocidad de conversion o

elegimos el Iormato del resultado de la conversion. Veremos los detalles en adelante.

ADCSRB. Es el segundo registro de control y estado del ADC. Sus pocos bits

Iuncionales conIiguran el modo de conversiones automaticas y como ese modo es

raramente usado, el registro ADCSRB tampoco esta muy avistado en los programas.

Los viejos AVR no lo tienen.

ADCH y ADCL. Son los registros que almacenan el resultado de la conversion. Uno

guarda 8 bits y el otro los dos bits restantes. La Iorma como se distribuyen se debe

especiIicar con el bit ADLAR del registro ADMUX.

Para cuestiones de programacion estos registros se Iusionan para Iormar un unico

registro de 16 bits normalmente llamado ADC o ADCW.

ADMUX. Es el registro que selecciona el canal de conversion y establece los voltajes

de reIerencia.

DIDR0. Es tambien un nuevo registro no disponible en los viejos AVR. Su Iuncion es

desconectar los pines seleccionados como canales latentes del conversor para asi evitar

que se desgaste corriente en parte del circuito del ADC.

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 2

EL MDULO ADC DE LOS AVR

Los AVR de la serie megaAVR tienen un ADC de aproximaciones sucesivas de 10 bits. Es uno

solo pero esta multiplexado para dar cabida hasta a 8 entradas analogicas. Se convierte solo una

entrada o la diIerencia de dos entradas analogicas a la vez.

Concretamente, los AVR de la serie A1megaXX4 cuentan con 8 canales de conversion, todos

ubicados en su puerto A. Por otro lado los AVR de la serie ATmegaXX8 destinan todo su

puerto C como canales de entrada del ADC.

El detalle con los ATmegaXX8 es que su puerto C solo tiene pines si vienen en empaque DIP

pero tiene 8 pines en los empaques TQFP y QFN/MLF. De modo que estos megaAJR pueden

tener u 8 canales de conversin dependiendo de su empaque.

Operacin del Mdulo ADC

En las aplicaciones ordinarias solo los registros ADCSRA y ADMUX son los que se manipulan

activamente. Los registros ADCH y ADCL son de solo lectura y como no tienen Iormato, basta

con recordar sus nombres.

ADCSRA. Es el principal registro de control y estado del ADC. Manipulando los bits

de este registro iniciamos la conversion, establecemos la velocidad de conversion o

elegimos el Iormato del resultado de la conversion. Veremos los detalles en adelante.

ADCSRB. Es el segundo registro de control y estado del ADC. Sus pocos bits

Iuncionales conIiguran el modo de conversiones automaticas y como ese modo es

raramente usado, el registro ADCSRB tampoco esta muy avistado en los programas.

Los viejos AVR no lo tienen.

ADCH y ADCL. Son los registros que almacenan el resultado de la conversion. Uno

guarda 8 bits y el otro los dos bits restantes. La Iorma como se distribuyen se debe

especiIicar con el bit ADLAR del registro ADMUX.

Para cuestiones de programacion estos registros se Iusionan para Iormar un unico

registro de 16 bits normalmente llamado ADC o ADCW.

ADMUX. Es el registro que selecciona el canal de conversion y establece los voltajes

de reIerencia.

DIDR0. Es tambien un nuevo registro no disponible en los viejos AVR. Su Iuncion es

desconectar los pines seleccionados como canales latentes del conversor para asi evitar

que se desgaste corriente en parte del circuito del ADC.

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 3

Registro ADCSRA

ADEN ADSC ADATE ADIF ADIE ADPS2 ADPS1 ADPS0

Registro ADCSRB

----- ACME --- --- --- ADTS2 ADTS1 ADTS0

Registro ADMUX

REFS1 REFS0 ADLAR MUX4 MUX3 MUX2 MUX1 MUX0

Registro DIDR0

ADC7D ADC6D ADC5D ADC4D ADC3D ADC2D ADC1D ADC0D

Registro ADCH

Registro ADCL

El ADC de los megaAVR es bastante Iacil de controlar si se le emplea en su modo habitual de

conversiones normales de entrada unica. Tras conIigurar este modo, se escoge un canal a la vez

y se setea el bit ADSC para iniciar la conversion. Despues esperamos a que este mismo bit se

limpie automaticamente por hardware como seal de que la conversion termino, y cuando lo

haga podremos leer el resultado. Eso seria todo.

El proceso descrito se puede desglosar en los siguientes pasos. Los pasos 2 al 5 (que estan

relacionados con el registro ADMUX) no necesariamente tienen que ir en ese orden de hecho se

pueden juntar todos en un solo paso. Esto es porque el registro ADMUX trabaja con un buIIer

de respaldo del cual es actualizado continuamente para asegurar un buen trabajo del ADC. Esto

es, cuando escribimos en ADMUX en realidad escribimos en su buIIer, el cual se copia

continuamente al registro ADMUX hasta que se inicia la conversion. En ese momento el

copiado continuo se detiene y se reanudara cuando termine la conversion. De ese modo se

evitan los resultados 'Irankenstenianos' de lo que seria un mal uso del registro ADMUX.

1. Seleccionar el reloj del conversor ADC, con los bits ADPS2:ADPS0.

2. Seleccionar los voltajes de reIerencia del conversor, usando los bits REFS1 y REFS0.

3. Establecer la justiIicacion del resultado con el bit ADLAR.

4. Seleccionar el canal o los canales de entrada del ADC, con los bits MUX4:MUX0.

5. Encender el modulo ADC, seteando el bit ADEN.

6. Iniciar la conversion, seteando el bit ADSC.

7. Esperar a que termine la conversion. Cuando esto pase el Ilag ADIF se pondra a uno y

si la conversion es normal y el bit ADSC se limpiara automaticamente.

8. Leer el resultado de la conversion del par de registros ADCH: ADCL.

Para bien o para mal, la Ilexibilidad del ADC complica aun mas su control, pues tambien

existen el modo de conversiones diIerenciales y el modo de conversiones auto-disparadas, el

cual se puede aplicar para cada caso, es decir, el ADC puede desdoblar su operacion hasta en

cuatro modos.

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 4

Seales para iniciar conversiones normales y auto-disparadas.

Conversiones normales de entrada unica, donde el ADC convierte el valor de un canal,

cada vez que se setee el bit ADSC.

Conversiones normales de entradas diIerenciales, donde el ADC convierte la diIerencia

de dos canales. La conversion se inicia seteando el bit ADSC.

Conversiones auto-disparadas de entrada unica, donde el ADC convierte un canal

cuando se produzca alguno de los eventos seleccionados por los bits ADTS2, ADTS1 y

ADTS0, que puede ser, por ejemplo, el desbordamiento de un Timer o simplemente la

activacion del Ilag ADIF. Este ultimo caso es peculiar y se conoce como modo de

conversiones de corrida libre, porque el ADC realiza conversiones una tras otra sin

cesar. Aqui la primera conversion se inicia seteando el bit ADSC.

Conversiones auto-disparadas de entradas diIerenciales. Es una combinacion de los dos

modos anteriores.

No hay una Iorma explicita de establecer cada uno de estos cuatro modos de operacion del

ADC. Si la conversion sera de entrada unica o diIerencial sera resultado de conIigurar el

multiplexor del ADC con los bits MUX4...MUX0. Por deIecto las conversiones seran normales.

Si queremos que se disparen automaticamente habra que conIigurarlas con los bits ADTS2,

ADTS1 y ADTS0 del registro ADCSRB, siempre que el bit ADATE de ADCSRA valga uno.

Tabla ADTS2

ADTS2 ADTS1 ADTS0 Fuente de disparo

0 0 0 Modo de Corrida Libre

0 0 1 Comparador Analogico

0 1 0 Interrupcion Externa INT0

0 1 1 Coincidencia del Timer/Counter0

1 0 0 Desbordamiento del Timer/Counter0

1 0 1 Coincidencia B del Timer/Counter1

1 1 0 Desbordamiento del Timer/Counter1

1 1 1 Evento de Captura del Timer/Counter1

SELECCIN DEL CANAL DE CONVERSIN

Las 8 entradas analogicas del ADC son los pines del puerto A de los AVR que tienen 4 puertos

o mas. En los AVR de 3 puertos son los pines del puerto C; estos AVR tienen 6 entradas

analogicas si vienen en empaque PDIP u 8 si vienen en empaque TQFP, QFP o MLF. Las dos

entradas adicionales son pines independientes, que no Iorman parte de ningun puerto.

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 4

Seales para iniciar conversiones normales y auto-disparadas.

Conversiones normales de entrada unica, donde el ADC convierte el valor de un canal,

cada vez que se setee el bit ADSC.

Conversiones normales de entradas diIerenciales, donde el ADC convierte la diIerencia

de dos canales. La conversion se inicia seteando el bit ADSC.

Conversiones auto-disparadas de entrada unica, donde el ADC convierte un canal

cuando se produzca alguno de los eventos seleccionados por los bits ADTS2, ADTS1 y

ADTS0, que puede ser, por ejemplo, el desbordamiento de un Timer o simplemente la

activacion del Ilag ADIF. Este ultimo caso es peculiar y se conoce como modo de

conversiones de corrida libre, porque el ADC realiza conversiones una tras otra sin

cesar. Aqui la primera conversion se inicia seteando el bit ADSC.

Conversiones auto-disparadas de entradas diIerenciales. Es una combinacion de los dos

modos anteriores.

No hay una Iorma explicita de establecer cada uno de estos cuatro modos de operacion del

ADC. Si la conversion sera de entrada unica o diIerencial sera resultado de conIigurar el

multiplexor del ADC con los bits MUX4...MUX0. Por deIecto las conversiones seran normales.

Si queremos que se disparen automaticamente habra que conIigurarlas con los bits ADTS2,

ADTS1 y ADTS0 del registro ADCSRB, siempre que el bit ADATE de ADCSRA valga uno.

Tabla ADTS2

ADTS2 ADTS1 ADTS0 Fuente de disparo

0 0 0 Modo de Corrida Libre

0 0 1 Comparador Analogico

0 1 0 Interrupcion Externa INT0

0 1 1 Coincidencia del Timer/Counter0

1 0 0 Desbordamiento del Timer/Counter0

1 0 1 Coincidencia B del Timer/Counter1

1 1 0 Desbordamiento del Timer/Counter1

1 1 1 Evento de Captura del Timer/Counter1

SELECCIN DEL CANAL DE CONVERSIN

Las 8 entradas analogicas del ADC son los pines del puerto A de los AVR que tienen 4 puertos

o mas. En los AVR de 3 puertos son los pines del puerto C; estos AVR tienen 6 entradas

analogicas si vienen en empaque PDIP u 8 si vienen en empaque TQFP, QFP o MLF. Las dos

entradas adicionales son pines independientes, que no Iorman parte de ningun puerto.

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 4

Seales para iniciar conversiones normales y auto-disparadas.

Conversiones normales de entrada unica, donde el ADC convierte el valor de un canal,

cada vez que se setee el bit ADSC.

Conversiones normales de entradas diIerenciales, donde el ADC convierte la diIerencia

de dos canales. La conversion se inicia seteando el bit ADSC.

Conversiones auto-disparadas de entrada unica, donde el ADC convierte un canal

cuando se produzca alguno de los eventos seleccionados por los bits ADTS2, ADTS1 y

ADTS0, que puede ser, por ejemplo, el desbordamiento de un Timer o simplemente la

activacion del Ilag ADIF. Este ultimo caso es peculiar y se conoce como modo de

conversiones de corrida libre, porque el ADC realiza conversiones una tras otra sin

cesar. Aqui la primera conversion se inicia seteando el bit ADSC.

Conversiones auto-disparadas de entradas diIerenciales. Es una combinacion de los dos

modos anteriores.

No hay una Iorma explicita de establecer cada uno de estos cuatro modos de operacion del

ADC. Si la conversion sera de entrada unica o diIerencial sera resultado de conIigurar el

multiplexor del ADC con los bits MUX4...MUX0. Por deIecto las conversiones seran normales.

Si queremos que se disparen automaticamente habra que conIigurarlas con los bits ADTS2,

ADTS1 y ADTS0 del registro ADCSRB, siempre que el bit ADATE de ADCSRA valga uno.

Tabla ADTS2

ADTS2 ADTS1 ADTS0 Fuente de disparo

0 0 0 Modo de Corrida Libre

0 0 1 Comparador Analogico

0 1 0 Interrupcion Externa INT0

0 1 1 Coincidencia del Timer/Counter0

1 0 0 Desbordamiento del Timer/Counter0

1 0 1 Coincidencia B del Timer/Counter1

1 1 0 Desbordamiento del Timer/Counter1

1 1 1 Evento de Captura del Timer/Counter1

SELECCIN DEL CANAL DE CONVERSIN

Las 8 entradas analogicas del ADC son los pines del puerto A de los AVR que tienen 4 puertos

o mas. En los AVR de 3 puertos son los pines del puerto C; estos AVR tienen 6 entradas

analogicas si vienen en empaque PDIP u 8 si vienen en empaque TQFP, QFP o MLF. Las dos

entradas adicionales son pines independientes, que no Iorman parte de ningun puerto.

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 5

El ADC solo puede tomar una o dos entradas analogicas por conversion, asi que cada vez que se

desee obtener un valor analogico externo se debe seleccionar previamente dicha entrada

analogica mediante los bits MUX4, MUX3, MUX2, MUX1 y MUX0 del registro ADMUX.

Registro ADMUX

REFS1 REFS0 ADLAR MUX4 MUX3 MUX2 MUX1 MUX0

La siguiente tabla muestra todas las opciones posibles que se pueden obtener. Parece

complicado de desciIrar pero enseguida lo explicaremos.

Cananles del ADC del microcontrolador AVR

MUX4:MUX0 Entrada Unica Entrada Diferencial Positiva Entrada Diferencial Negativa Ganancia

00000 ADC0

N/A

00001 ADC1

00010 ADC2

00011 ADC3

00100 ADC4

00101 ADC5

00110 ADC6

00111 ADC7

01000

N/A

ADC0 ADC0 10x

01001 ADC1 ADC0 10x

01010 ADC0 ADC0 200x

01011 ADC1 ADC0 200x

01100 ADC2 ADC2 10x

01101 ADC3 ADC2 10x

01110 ADC2 ADC2 200x

01111 ADC3 ADC2 200x

10000 ADC0 ADC1 1x

10001 ADC1 ADC1 1x

10010 ADC2 ADC1 1x

10011 ADC3 ADC1 1x

10100 ADC4 ADC1 1x

10101 ADC5 ADC1 1x

10110 ADC6 ADC1 1x

10111 ADC7 ADC1 1x

11000 ADC0 ADC2 1x

11001 ADC1 ADC2 1x

11010 ADC2 ADC2 1x

11011 ADC3 ADC2 1x

11100 ADC4 ADC2 1x

11101 ADC5 ADC2 1x

11110 1.1V ( )

11111 0 V (GND)

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 6

Observemos en primer lugar que la tabla se puede separar en tres secciones.

La primera parte corresponde al denominado modo de conversin simple o de entrada nica,

la segunda parte es del modo de conversin diferencial y en la tercera parte no se elige

ningn canal analgico sino que se convierte el valor de la tension o GND.

El modo de conversin de entrada nica es el que se emplea en la gran mayoria de las

aplicaciones. Aqui los bits del multiplexor MUX4 y MUX3 valen 0 y el ADC solo puede

convertir una de las 8 entradas analogicas a la vez. El diagrama Iuncional del ADC en este caso

se representa asi.

Diagrama basico del ADC para conversiones de entrada unica.

Debemos tener en cuenta que este modo es compatible en todos los modulos ADC de los

megaAVR que lo tienen. Sobra decir que no tendran ningun eIecto las conIiguraciones de

MUX4:MUX0 que eligen los canales ADC6 y ADC7 en los AVR que no tienen estos pines. De

hecho los megaAVR de 3 puertos no tienen el bit MUX4 y es recomendable dejarlo siempre en 0.

En el modo de conversin diferencial las entradas analogicas se agrupan de a dos. Cada par

se constituye por una Entrada DiIerencial Positiva y una Entrada DiIerencial Negativa. Todas

las combinaciones posibles estan establecidas por los bits MUX4:MUX0, de acuerdo con la

tabla de arriba. Se puede observar alli y en la Iigura mostrada abajo que en este modo interviene

ademas un ampliIicador de ganancia que puede multiplicar la diIerencia entre las entradas por

un Iactor de 1x, 10x o 200x antes de ser convertido a su valor analogico. El inconveniente del

ampliIicador es que reduce la resolucion del ADC a 8 bits si se usa la ganancia de 1x o 10x y

hasta a 6 bits con la ganancia de 200x. Este modo de operacion del ADC solo esta disponible en

los megaAVR de 4 puertos o mas.

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 6

Observemos en primer lugar que la tabla se puede separar en tres secciones.

La primera parte corresponde al denominado modo de conversin simple o de entrada nica,

la segunda parte es del modo de conversin diferencial y en la tercera parte no se elige

ningn canal analgico sino que se convierte el valor de la tension o GND.

El modo de conversin de entrada nica es el que se emplea en la gran mayoria de las

aplicaciones. Aqui los bits del multiplexor MUX4 y MUX3 valen 0 y el ADC solo puede

convertir una de las 8 entradas analogicas a la vez. El diagrama Iuncional del ADC en este caso

se representa asi.

Diagrama basico del ADC para conversiones de entrada unica.

Debemos tener en cuenta que este modo es compatible en todos los modulos ADC de los

megaAVR que lo tienen. Sobra decir que no tendran ningun eIecto las conIiguraciones de

MUX4:MUX0 que eligen los canales ADC6 y ADC7 en los AVR que no tienen estos pines. De

hecho los megaAVR de 3 puertos no tienen el bit MUX4 y es recomendable dejarlo siempre en 0.

En el modo de conversin diferencial las entradas analogicas se agrupan de a dos. Cada par

se constituye por una Entrada DiIerencial Positiva y una Entrada DiIerencial Negativa. Todas

las combinaciones posibles estan establecidas por los bits MUX4:MUX0, de acuerdo con la

tabla de arriba. Se puede observar alli y en la Iigura mostrada abajo que en este modo interviene

ademas un ampliIicador de ganancia que puede multiplicar la diIerencia entre las entradas por

un Iactor de 1x, 10x o 200x antes de ser convertido a su valor analogico. El inconveniente del

ampliIicador es que reduce la resolucion del ADC a 8 bits si se usa la ganancia de 1x o 10x y

hasta a 6 bits con la ganancia de 200x. Este modo de operacion del ADC solo esta disponible en

los megaAVR de 4 puertos o mas.

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 6

Observemos en primer lugar que la tabla se puede separar en tres secciones.

La primera parte corresponde al denominado modo de conversin simple o de entrada nica,

la segunda parte es del modo de conversin diferencial y en la tercera parte no se elige

ningn canal analgico sino que se convierte el valor de la tension o GND.

El modo de conversin de entrada nica es el que se emplea en la gran mayoria de las

aplicaciones. Aqui los bits del multiplexor MUX4 y MUX3 valen 0 y el ADC solo puede

convertir una de las 8 entradas analogicas a la vez. El diagrama Iuncional del ADC en este caso

se representa asi.

Diagrama basico del ADC para conversiones de entrada unica.

Debemos tener en cuenta que este modo es compatible en todos los modulos ADC de los

megaAVR que lo tienen. Sobra decir que no tendran ningun eIecto las conIiguraciones de

MUX4:MUX0 que eligen los canales ADC6 y ADC7 en los AVR que no tienen estos pines. De

hecho los megaAVR de 3 puertos no tienen el bit MUX4 y es recomendable dejarlo siempre en 0.

En el modo de conversin diferencial las entradas analogicas se agrupan de a dos. Cada par

se constituye por una Entrada DiIerencial Positiva y una Entrada DiIerencial Negativa. Todas

las combinaciones posibles estan establecidas por los bits MUX4:MUX0, de acuerdo con la

tabla de arriba. Se puede observar alli y en la Iigura mostrada abajo que en este modo interviene

ademas un ampliIicador de ganancia que puede multiplicar la diIerencia entre las entradas por

un Iactor de 1x, 10x o 200x antes de ser convertido a su valor analogico. El inconveniente del

ampliIicador es que reduce la resolucion del ADC a 8 bits si se usa la ganancia de 1x o 10x y

hasta a 6 bits con la ganancia de 200x. Este modo de operacion del ADC solo esta disponible en

los megaAVR de 4 puertos o mas.

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 7

Diagrama basico del ADC para conversiones de entradas diIerenciales.

Finalmente, hay dos combinaciones de los bits MUX4:MUX0 que hacen que el valor analogico

a convertir sea la seal de tierra GND o una tension de reIerencia denominada que varia

segun el microcontrolador. En los megaAVR de las series 4xx y 8xx que son los enIocados con

prioridad en cursomicros.com esta tension vale 1.1V. Si vamos a trabajar con esta caracteristica

utilizando otros modelos de AVR, deberemos revisar su datasheet.

Conversion de las tensiones de reIerencia GND y .

LOS VOLTA1ES DE REFERENCIA

Son los valores analogicos limites entre los que debera estar comprendida la tension analogica a

convertir. El nivel superior se representa por VreI y el inIerior por VreI-.

Como seguramente lo habras notado en los diagramas anteriores, el valor de VreI- es igual al

negativo de VreI cuando el ADC realiza conversiones diIerenciales y es igual a 0V en los

demas casos. En cualquier modo de operacion VreI se puede conIigurar por los bits REFS1 y

REFS0, del registro ADMUX y podemos escoger una de estas tres opciones:

El valor del pin AVCC

El valor del pin AREF

Un Voltaje de ReIerencia Interno (de 1.1V o 2.56 V) que provee el megaAVR.

Registro DMUX

REFS1 REFS0 ADLAR MUX4 MUX3 MUX2 MUX1 MUX0

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 7

Diagrama basico del ADC para conversiones de entradas diIerenciales.

Finalmente, hay dos combinaciones de los bits MUX4:MUX0 que hacen que el valor analogico

a convertir sea la seal de tierra GND o una tension de reIerencia denominada que varia

segun el microcontrolador. En los megaAVR de las series 4xx y 8xx que son los enIocados con

prioridad en cursomicros.com esta tension vale 1.1V. Si vamos a trabajar con esta caracteristica

utilizando otros modelos de AVR, deberemos revisar su datasheet.

Conversion de las tensiones de reIerencia GND y .

LOS VOLTA1ES DE REFERENCIA

Son los valores analogicos limites entre los que debera estar comprendida la tension analogica a

convertir. El nivel superior se representa por VreI y el inIerior por VreI-.

Como seguramente lo habras notado en los diagramas anteriores, el valor de VreI- es igual al

negativo de VreI cuando el ADC realiza conversiones diIerenciales y es igual a 0V en los

demas casos. En cualquier modo de operacion VreI se puede conIigurar por los bits REFS1 y

REFS0, del registro ADMUX y podemos escoger una de estas tres opciones:

El valor del pin AVCC

El valor del pin AREF

Un Voltaje de ReIerencia Interno (de 1.1V o 2.56 V) que provee el megaAVR.

Registro DMUX

REFS1 REFS0 ADLAR MUX4 MUX3 MUX2 MUX1 MUX0

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 7

Diagrama basico del ADC para conversiones de entradas diIerenciales.

Finalmente, hay dos combinaciones de los bits MUX4:MUX0 que hacen que el valor analogico

a convertir sea la seal de tierra GND o una tension de reIerencia denominada que varia

segun el microcontrolador. En los megaAVR de las series 4xx y 8xx que son los enIocados con

prioridad en cursomicros.com esta tension vale 1.1V. Si vamos a trabajar con esta caracteristica

utilizando otros modelos de AVR, deberemos revisar su datasheet.

Conversion de las tensiones de reIerencia GND y .

LOS VOLTA1ES DE REFERENCIA

Son los valores analogicos limites entre los que debera estar comprendida la tension analogica a

convertir. El nivel superior se representa por VreI y el inIerior por VreI-.

Como seguramente lo habras notado en los diagramas anteriores, el valor de VreI- es igual al

negativo de VreI cuando el ADC realiza conversiones diIerenciales y es igual a 0V en los

demas casos. En cualquier modo de operacion VreI se puede conIigurar por los bits REFS1 y

REFS0, del registro ADMUX y podemos escoger una de estas tres opciones:

El valor del pin AVCC

El valor del pin AREF

Un Voltaje de ReIerencia Interno (de 1.1V o 2.56 V) que provee el megaAVR.

Registro DMUX

REFS1 REFS0 ADLAR MUX4 MUX3 MUX2 MUX1 MUX0

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 8

Si los bits REFS1:REFS0 eligen como voltaje de reIerencia VreI al pin AVCC, ese pin lo

debemos conectar a Vcc mediante un Iiltro pasa-bajas. Puesto que el pin AREF queda

internamente conectado a AVCC, es mas que recomendable colocarle un capacitor para Iiltrar el

ruido. Abajo se muestra un boceto del circuito descrito. Recordemos que el pin AVCC es en

principio la alimentacion del puerto que lleva los canales del ADC, asi como la alimentacion del

mismo modulo ADC. Sin embargo, incluso de no usar el ADC, el pin AVCC se debe conectar a

Vcc, con Iiltro o sin el.

Si los bits REFS1:REFS0 eligen como voltaje de reIerencia VreI al pin AREF, podemos

conectar a ese pin cualquier Iuente de voltaje, siempre que no supere el valor de la alimentacion

Vcc y en caso de que trabajemos con canales diIerenciales no debe ser menor de 2 V. De esto

ultimo se deduce que no se podria elegir el Voltaje de ReIerencia Interno de 1.1V, descrito

luego.

Es muy poco Irecuente programar el ADC para que opere de este modo, pero si lo vamos a

hacer, debemos Iijarnos bien en la conIiguracion de los bits REF1 y REF0. Si aplicamos una

Iuente de tension en el pin AREF y los bits REF1 y REF0 seleccionan una reIerencia diIerente,

entonces se producira un corto-circuito interno entre el pin AREF y la reIerencia seleccionada

(AVCC, por ejemplo).

Los bits REFS1:REFS0 tambien pueden elegir como VreI alguno de los Voltajes de

ReIerencia Internos que provee el AVR, pero aqui se debe tener en cuenta que sus valores

pueden variar entre las diIerentes series de AVR, incluso si son de Iamilias cercanas. Tambien

en este caso la reIerencia se vera reIlejada por el pin AREF, de modo que deberiamos conectar

alli un capacitor de estabilizacion.

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 8

Si los bits REFS1:REFS0 eligen como voltaje de reIerencia VreI al pin AVCC, ese pin lo

debemos conectar a Vcc mediante un Iiltro pasa-bajas. Puesto que el pin AREF queda

internamente conectado a AVCC, es mas que recomendable colocarle un capacitor para Iiltrar el

ruido. Abajo se muestra un boceto del circuito descrito. Recordemos que el pin AVCC es en

principio la alimentacion del puerto que lleva los canales del ADC, asi como la alimentacion del

mismo modulo ADC. Sin embargo, incluso de no usar el ADC, el pin AVCC se debe conectar a

Vcc, con Iiltro o sin el.

Si los bits REFS1:REFS0 eligen como voltaje de reIerencia VreI al pin AREF, podemos

conectar a ese pin cualquier Iuente de voltaje, siempre que no supere el valor de la alimentacion

Vcc y en caso de que trabajemos con canales diIerenciales no debe ser menor de 2 V. De esto

ultimo se deduce que no se podria elegir el Voltaje de ReIerencia Interno de 1.1V, descrito

luego.

Es muy poco Irecuente programar el ADC para que opere de este modo, pero si lo vamos a

hacer, debemos Iijarnos bien en la conIiguracion de los bits REF1 y REF0. Si aplicamos una

Iuente de tension en el pin AREF y los bits REF1 y REF0 seleccionan una reIerencia diIerente,

entonces se producira un corto-circuito interno entre el pin AREF y la reIerencia seleccionada

(AVCC, por ejemplo).

Los bits REFS1:REFS0 tambien pueden elegir como VreI alguno de los Voltajes de

ReIerencia Internos que provee el AVR, pero aqui se debe tener en cuenta que sus valores

pueden variar entre las diIerentes series de AVR, incluso si son de Iamilias cercanas. Tambien

en este caso la reIerencia se vera reIlejada por el pin AREF, de modo que deberiamos conectar

alli un capacitor de estabilizacion.

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 8

Si los bits REFS1:REFS0 eligen como voltaje de reIerencia VreI al pin AVCC, ese pin lo

debemos conectar a Vcc mediante un Iiltro pasa-bajas. Puesto que el pin AREF queda

internamente conectado a AVCC, es mas que recomendable colocarle un capacitor para Iiltrar el

ruido. Abajo se muestra un boceto del circuito descrito. Recordemos que el pin AVCC es en

principio la alimentacion del puerto que lleva los canales del ADC, asi como la alimentacion del

mismo modulo ADC. Sin embargo, incluso de no usar el ADC, el pin AVCC se debe conectar a

Vcc, con Iiltro o sin el.

Si los bits REFS1:REFS0 eligen como voltaje de reIerencia VreI al pin AREF, podemos

conectar a ese pin cualquier Iuente de voltaje, siempre que no supere el valor de la alimentacion

Vcc y en caso de que trabajemos con canales diIerenciales no debe ser menor de 2 V. De esto

ultimo se deduce que no se podria elegir el Voltaje de ReIerencia Interno de 1.1V, descrito

luego.

Es muy poco Irecuente programar el ADC para que opere de este modo, pero si lo vamos a

hacer, debemos Iijarnos bien en la conIiguracion de los bits REF1 y REF0. Si aplicamos una

Iuente de tension en el pin AREF y los bits REF1 y REF0 seleccionan una reIerencia diIerente,

entonces se producira un corto-circuito interno entre el pin AREF y la reIerencia seleccionada

(AVCC, por ejemplo).

Los bits REFS1:REFS0 tambien pueden elegir como VreI alguno de los Voltajes de

ReIerencia Internos que provee el AVR, pero aqui se debe tener en cuenta que sus valores

pueden variar entre las diIerentes series de AVR, incluso si son de Iamilias cercanas. Tambien

en este caso la reIerencia se vera reIlejada por el pin AREF, de modo que deberiamos conectar

alli un capacitor de estabilizacion.

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 9

Las siguientes tablas muestran la conIiguracion de los bits REFS1:REFS0 correspondiente a los

AVR de las series ATmegaXX4 y ATmegaXX8. Podemos observar que la clara divergencia se

encuentra en la eleccion de los Voltajes de ReIerencia Internos. Si vamos a utilizar estas

reIerencias en otros AVR sera recomendable revisar su datasheet respectivo.

Tabla REFS1

REFS1 REFS0 Voltaje de Referencia Vref+ para los ATmegaXX4

0 0 Pin AREF

0 1 Pin AVCC con capacitor externo en el pin AREF

1 0 Voltaje de ReIerencia Interno de 1.1V con capacitor externo en el pin AREF

1 1 Voltaje de ReIerencia Interno de 2.56V con capacitor externo en el pin AREF

Tabla REFS1

REFS1 REFS0 Voltaje de Referencia Vref+ para los ATmegaXX8

0 0 Pin AREF

0 1 Pin AVCC con capacitor externo en el pin AREF

1 0 Reservado

1 1 Voltaje de ReIerencia Interno de 1.1V con capacitor externo en el pin AREF

Suponiendo que trabajamos con conversiones de entrada unica, esto es, VreI- conectado a tierra,

GND 0V, como se ve en la siguiente Iigura, entonces una entrada analogica igual a 0V o

inIerior se convertira en 0x000 y las tensiones analogicas iguales a VreI o superiores se

convertiran en el valor digital 0x3FF. Recordando la teoria estudiada al inicio de este capitulo,

cualquier otro valor analogico Vin comprendido entre estos limites estara sujeto a la Iormula.

Voltajes de ReIerencia del ADC para conversiones de entrada unica.

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 10

Por otro lado, si nuestro ADC realiza conversiones diferenciales, entonces la maxima

diIerencia positiva o negativa que se podra convertir correctamente sera (/- VreI)/ganancia,

siendo esta ganancia igual a 1, 10 o 200. En este caso el resultado sera un numero entero con

signo, es decir, positivo o negativo, Iormateado en complemento a dos. De acuerdo con esto, la

maxima diIerencia negativa correspondera al valor digital 0x200 -512 y la maxima diIerencia

positiva se convertira en 0x1FF 511. Cualquier otra diIerencia analogica interpolada se

debera interpretar con la siguiente Iormula.

Donde Vpos en la entrada diIerencial positiva y Vneg es la entrada diIerencial negativa.

Voltajes de ReIerencia del ADC para conversiones de entradas diIerenciales.

La primera conversion despues de cambiar los voltajes de reIerencia es imprecisa y se

recomienda descartarla.

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 11

RESULTADO DE LA CONVERSIN

El resultado de la conversion es una cantidad binaria de 10 bits que se deposita entre los

registros ADCH y ADCL, segun la justiIicacion mostrada en la siguiente Iigura y de acuerdo

con el bit ADLAR (ADC LeIt Adjust Result) del registro ADMUX.

Registro DMUX

REFS1 REFS0 ADLAR MUX4 MUX3 MUX2 MUX1 MUX0

1ustificacin del resultado entre los registros ADCH y ADCL

Obviamente debemos esperar a que termine una conversion antes de leer un dato valido de estos

registros. Para esto podemos comprobar la activacion del Ilag ADIF (del registro ADCSRA) o

la puesta a cero del bit ADSC (tambien de ADCSRA), si es que el ADC opera en modo normal.

Los dos registros del resultado son de solo lectura y el acceso a ellos no involucra una operacion

atomica. Sin embargo, debemos saber que despues de leer el registro ADCL queda bloqueada la

actualizacion de los otros registros del ADC hasta que leamos el registro ADCH. De este modo

se asegura que los datos presentes en estos registros corresponden a una misma conversion. De

aqui se desprende que al terminar una conversion debemos empezar por leer ADCL y luego

ADCH, o simplemente podemos tomar el valor de ADCH y asi permitir que se puedan depositar

en ellos los valores de nuevas conversiones.

Cuando se establece la justiIicacion derecha los registros ADCH y ADCL conIorman el registro

de 16 bits llamado simplemente ADC y puede ser asi reconocido por los compiladores C puesto

que ocupan posiciones contiguas en el espacio de los registros de E/S

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 11

RESULTADO DE LA CONVERSIN

El resultado de la conversion es una cantidad binaria de 10 bits que se deposita entre los

registros ADCH y ADCL, segun la justiIicacion mostrada en la siguiente Iigura y de acuerdo

con el bit ADLAR (ADC LeIt Adjust Result) del registro ADMUX.

Registro DMUX

REFS1 REFS0 ADLAR MUX4 MUX3 MUX2 MUX1 MUX0

1ustificacin del resultado entre los registros ADCH y ADCL

Obviamente debemos esperar a que termine una conversion antes de leer un dato valido de estos

registros. Para esto podemos comprobar la activacion del Ilag ADIF (del registro ADCSRA) o

la puesta a cero del bit ADSC (tambien de ADCSRA), si es que el ADC opera en modo normal.

Los dos registros del resultado son de solo lectura y el acceso a ellos no involucra una operacion

atomica. Sin embargo, debemos saber que despues de leer el registro ADCL queda bloqueada la

actualizacion de los otros registros del ADC hasta que leamos el registro ADCH. De este modo

se asegura que los datos presentes en estos registros corresponden a una misma conversion. De

aqui se desprende que al terminar una conversion debemos empezar por leer ADCL y luego

ADCH, o simplemente podemos tomar el valor de ADCH y asi permitir que se puedan depositar

en ellos los valores de nuevas conversiones.

Cuando se establece la justiIicacion derecha los registros ADCH y ADCL conIorman el registro

de 16 bits llamado simplemente ADC y puede ser asi reconocido por los compiladores C puesto

que ocupan posiciones contiguas en el espacio de los registros de E/S

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 11

RESULTADO DE LA CONVERSIN

El resultado de la conversion es una cantidad binaria de 10 bits que se deposita entre los

registros ADCH y ADCL, segun la justiIicacion mostrada en la siguiente Iigura y de acuerdo

con el bit ADLAR (ADC LeIt Adjust Result) del registro ADMUX.

Registro DMUX

REFS1 REFS0 ADLAR MUX4 MUX3 MUX2 MUX1 MUX0

1ustificacin del resultado entre los registros ADCH y ADCL

Obviamente debemos esperar a que termine una conversion antes de leer un dato valido de estos

registros. Para esto podemos comprobar la activacion del Ilag ADIF (del registro ADCSRA) o

la puesta a cero del bit ADSC (tambien de ADCSRA), si es que el ADC opera en modo normal.

Los dos registros del resultado son de solo lectura y el acceso a ellos no involucra una operacion

atomica. Sin embargo, debemos saber que despues de leer el registro ADCL queda bloqueada la

actualizacion de los otros registros del ADC hasta que leamos el registro ADCH. De este modo

se asegura que los datos presentes en estos registros corresponden a una misma conversion. De

aqui se desprende que al terminar una conversion debemos empezar por leer ADCL y luego

ADCH, o simplemente podemos tomar el valor de ADCH y asi permitir que se puedan depositar

en ellos los valores de nuevas conversiones.

Cuando se establece la justiIicacion derecha los registros ADCH y ADCL conIorman el registro

de 16 bits llamado simplemente ADC y puede ser asi reconocido por los compiladores C puesto

que ocupan posiciones contiguas en el espacio de los registros de E/S

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 12

RELO1 DEL ADC Y TIEMPO DE CONVERSIN

Como todo circuito sincrono, el conversor ADC necesita de una seal de reloj para dirigir los

pasos de su algoritmo de aproximaciones sucesivas, ese que describimos al principio. Este reloj

deriva del oscilador del sistema FCPU. La Irecuencia del reloj del ADC dependera de la

resolucion del resultado que se desee obtener. Por ejemplo, si se va a trabajar con los 10 bits de

resolucion, entonces se requerira de un reloj cuya Irecuencia este entre 50kHz y 200kHz. Si se

requiere de una resolucion menor de 10 bits, el reloj del ADC puede superar los 200kHz.

El reloj del ADC es una ramiIicacion del reloj del sistema, FCPU. De alli proviene y antes de

aplicarse al ADC pasa por un prescaler programable que permite disminuir su valor. Los

Iactores de division se establecen por los bits ADPS2, ADPS1 y ADPS0, del registro ADCSRA,

de acuerdo con la tabla mostrada mas abajo.

Diagrama de la Iuente del reloj del ADC.

Tabla ADPS2

ADPS2 ADPS1 ADPS0 Factor de Divisin

0 0 0 2

0 0 1 2

0 1 0 4

0 1 1 8

1 0 0 16

1 0 1 32

1 1 0 64

1 1 1 128

A modo de ejemplo analicemos los valores de ADPS1, ADPS1 y ADPS0 que podriamos usar

suponiendo que trabajamos con nuestro acostumbrado XTAL (FCPU) de 8MHz.

Si ADPS2:ADPS0 111b, el reloj del ADC tendra una Irecuencia de 8MHz/128 62.5kHz,

valor suIiciente para conseguir resultados Iiables de 10 bits, tan Iiables como los generados a

125kHz con el Iactor de prescaler de 64.

Sin embargo, si escogemos el Iactor de 32, con ADPS2:ADPS0 101b, el ADC operara a

8MHz/32 250kHz, que es una Irecuencia superior a los 200kHz que garantizan una buena

conversion, de modo que deberemos evitarla, a menos tal vez que solo nos interesen los 8 bits

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 12

RELO1 DEL ADC Y TIEMPO DE CONVERSIN

Como todo circuito sincrono, el conversor ADC necesita de una seal de reloj para dirigir los

pasos de su algoritmo de aproximaciones sucesivas, ese que describimos al principio. Este reloj

deriva del oscilador del sistema FCPU. La Irecuencia del reloj del ADC dependera de la

resolucion del resultado que se desee obtener. Por ejemplo, si se va a trabajar con los 10 bits de

resolucion, entonces se requerira de un reloj cuya Irecuencia este entre 50kHz y 200kHz. Si se

requiere de una resolucion menor de 10 bits, el reloj del ADC puede superar los 200kHz.

El reloj del ADC es una ramiIicacion del reloj del sistema, FCPU. De alli proviene y antes de

aplicarse al ADC pasa por un prescaler programable que permite disminuir su valor. Los

Iactores de division se establecen por los bits ADPS2, ADPS1 y ADPS0, del registro ADCSRA,

de acuerdo con la tabla mostrada mas abajo.

Diagrama de la Iuente del reloj del ADC.

Tabla ADPS2

ADPS2 ADPS1 ADPS0 Factor de Divisin

0 0 0 2

0 0 1 2

0 1 0 4

0 1 1 8

1 0 0 16

1 0 1 32

1 1 0 64

1 1 1 128

A modo de ejemplo analicemos los valores de ADPS1, ADPS1 y ADPS0 que podriamos usar

suponiendo que trabajamos con nuestro acostumbrado XTAL (FCPU) de 8MHz.

Si ADPS2:ADPS0 111b, el reloj del ADC tendra una Irecuencia de 8MHz/128 62.5kHz,

valor suIiciente para conseguir resultados Iiables de 10 bits, tan Iiables como los generados a

125kHz con el Iactor de prescaler de 64.

Sin embargo, si escogemos el Iactor de 32, con ADPS2:ADPS0 101b, el ADC operara a

8MHz/32 250kHz, que es una Irecuencia superior a los 200kHz que garantizan una buena

conversion, de modo que deberemos evitarla, a menos tal vez que solo nos interesen los 8 bits

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 12

RELO1 DEL ADC Y TIEMPO DE CONVERSIN

Como todo circuito sincrono, el conversor ADC necesita de una seal de reloj para dirigir los

pasos de su algoritmo de aproximaciones sucesivas, ese que describimos al principio. Este reloj

deriva del oscilador del sistema FCPU. La Irecuencia del reloj del ADC dependera de la

resolucion del resultado que se desee obtener. Por ejemplo, si se va a trabajar con los 10 bits de

resolucion, entonces se requerira de un reloj cuya Irecuencia este entre 50kHz y 200kHz. Si se

requiere de una resolucion menor de 10 bits, el reloj del ADC puede superar los 200kHz.

El reloj del ADC es una ramiIicacion del reloj del sistema, FCPU. De alli proviene y antes de

aplicarse al ADC pasa por un prescaler programable que permite disminuir su valor. Los

Iactores de division se establecen por los bits ADPS2, ADPS1 y ADPS0, del registro ADCSRA,

de acuerdo con la tabla mostrada mas abajo.

Diagrama de la Iuente del reloj del ADC.

Tabla ADPS2

ADPS2 ADPS1 ADPS0 Factor de Divisin

0 0 0 2

0 0 1 2

0 1 0 4

0 1 1 8

1 0 0 16

1 0 1 32

1 1 0 64

1 1 1 128

A modo de ejemplo analicemos los valores de ADPS1, ADPS1 y ADPS0 que podriamos usar

suponiendo que trabajamos con nuestro acostumbrado XTAL (FCPU) de 8MHz.

Si ADPS2:ADPS0 111b, el reloj del ADC tendra una Irecuencia de 8MHz/128 62.5kHz,

valor suIiciente para conseguir resultados Iiables de 10 bits, tan Iiables como los generados a

125kHz con el Iactor de prescaler de 64.

Sin embargo, si escogemos el Iactor de 32, con ADPS2:ADPS0 101b, el ADC operara a

8MHz/32 250kHz, que es una Irecuencia superior a los 200kHz que garantizan una buena

conversion, de modo que deberemos evitarla, a menos tal vez que solo nos interesen los 8 bits

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 13

mas signiIicativos del resultado. En este ejemplo, los Iactores de prescaler inIeriores 32

conllevaran una operacion del ADC deIiciente e inaceptable.

De nuestras lecciones iniciales del conversor de aproximaciones sucesivas, sabemos que por

cada bit del resultado digital el ADC demora un ciclo del reloj. Esto es, si el conversor genera

datos de 10 bits se requeriran de 10 ciclos de reloj por conversion. Eso es del todo cierto solo en

el computo mismo de la conversion o en un ADC ideal; en un ADC real hay Iactores de

establecimiento que alargan ligeramente el tiempo de conversion.

En los megaAVR el tiempo de conversion depende del tipo de conversion que se realiza. La

siguiente tabla muestra las cuatro posibilidades.

Tabla Tipo de Conversion

Tipo de Conversin

Muestreo y retencin (Ciclos desde

el inicio de la conversin)

Tiempo de Conversin

(Ciclos)

Primera conversion 14.5 25

Conversiones Normales, de entrada

unica

1.5 13

Conversiones Normales, de entrada

diIerencial

1.5/2.5 13/14

Conversiones auto-disparadas 2 13.5

La primera conversion en cualquier modo es la que se ejecuta despues de habilitar el ADC,

seteando el bit ADEN; siempre demora mas debido a que se debe inicializar el circuito

analogico del ADC.

Los ciclos de muestreo y retencion se cuentan a partir del momento en que se inicia la

conversion, o sea, despues de setear el bit ADSC, del registro ADCSRA. Para comprender esto

debemos saber que el ADC no capta la seal a convertir directamente del pin ADCx, sino que

primero espera que dicho nivel de tension se deposite en el capacitor de muestreo y retencion

, para luego iniciar la conversion desde alli. El tiempo que demora este capacitor en

cargarse se denomina periodo de muestreo y retencion o a veces tiempo de adquisicion. Este

varia principalmente de acuerdo con la impedancia Rs del circuito externo al canal del ADC. El

ADC del AVR esta optimizado para acoplarse a impedancias de 10K o inIerior.

Circuito de entrada del ADC de los megaAVR.

Junto con su resolucion el tiempo de conversion es el parametro mas importante de un ADC.

Para Iines practicos esto se calcula como la suma del tiempo de conversion en si (el que

acabamos de describir) mas el tiempo de adquisicion. Por ejemplo, segun la tabla de arriba, las

conversiones normales de entrada unica, que son las mas usadas, demoran 131.5 14.5 ciclos.

Si el ADC trabajara a su maxima Irecuencia recomendada de 200kHz, cada ciclo duraria

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 13

mas signiIicativos del resultado. En este ejemplo, los Iactores de prescaler inIeriores 32

conllevaran una operacion del ADC deIiciente e inaceptable.

De nuestras lecciones iniciales del conversor de aproximaciones sucesivas, sabemos que por

cada bit del resultado digital el ADC demora un ciclo del reloj. Esto es, si el conversor genera

datos de 10 bits se requeriran de 10 ciclos de reloj por conversion. Eso es del todo cierto solo en

el computo mismo de la conversion o en un ADC ideal; en un ADC real hay Iactores de

establecimiento que alargan ligeramente el tiempo de conversion.

En los megaAVR el tiempo de conversion depende del tipo de conversion que se realiza. La

siguiente tabla muestra las cuatro posibilidades.

Tabla Tipo de Conversion

Tipo de Conversin

Muestreo y retencin (Ciclos desde

el inicio de la conversin)

Tiempo de Conversin

(Ciclos)

Primera conversion 14.5 25

Conversiones Normales, de entrada

unica

1.5 13

Conversiones Normales, de entrada

diIerencial

1.5/2.5 13/14

Conversiones auto-disparadas 2 13.5

La primera conversion en cualquier modo es la que se ejecuta despues de habilitar el ADC,

seteando el bit ADEN; siempre demora mas debido a que se debe inicializar el circuito

analogico del ADC.

Los ciclos de muestreo y retencion se cuentan a partir del momento en que se inicia la

conversion, o sea, despues de setear el bit ADSC, del registro ADCSRA. Para comprender esto

debemos saber que el ADC no capta la seal a convertir directamente del pin ADCx, sino que

primero espera que dicho nivel de tension se deposite en el capacitor de muestreo y retencion

, para luego iniciar la conversion desde alli. El tiempo que demora este capacitor en

cargarse se denomina periodo de muestreo y retencion o a veces tiempo de adquisicion. Este

varia principalmente de acuerdo con la impedancia Rs del circuito externo al canal del ADC. El

ADC del AVR esta optimizado para acoplarse a impedancias de 10K o inIerior.

Circuito de entrada del ADC de los megaAVR.

Junto con su resolucion el tiempo de conversion es el parametro mas importante de un ADC.

Para Iines practicos esto se calcula como la suma del tiempo de conversion en si (el que

acabamos de describir) mas el tiempo de adquisicion. Por ejemplo, segun la tabla de arriba, las

conversiones normales de entrada unica, que son las mas usadas, demoran 131.5 14.5 ciclos.

Si el ADC trabajara a su maxima Irecuencia recomendada de 200kHz, cada ciclo duraria

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 13

mas signiIicativos del resultado. En este ejemplo, los Iactores de prescaler inIeriores 32

conllevaran una operacion del ADC deIiciente e inaceptable.

De nuestras lecciones iniciales del conversor de aproximaciones sucesivas, sabemos que por

cada bit del resultado digital el ADC demora un ciclo del reloj. Esto es, si el conversor genera

datos de 10 bits se requeriran de 10 ciclos de reloj por conversion. Eso es del todo cierto solo en

el computo mismo de la conversion o en un ADC ideal; en un ADC real hay Iactores de

establecimiento que alargan ligeramente el tiempo de conversion.

En los megaAVR el tiempo de conversion depende del tipo de conversion que se realiza. La

siguiente tabla muestra las cuatro posibilidades.

Tabla Tipo de Conversion

Tipo de Conversin

Muestreo y retencin (Ciclos desde

el inicio de la conversin)

Tiempo de Conversin

(Ciclos)

Primera conversion 14.5 25

Conversiones Normales, de entrada

unica

1.5 13

Conversiones Normales, de entrada

diIerencial

1.5/2.5 13/14

Conversiones auto-disparadas 2 13.5

La primera conversion en cualquier modo es la que se ejecuta despues de habilitar el ADC,

seteando el bit ADEN; siempre demora mas debido a que se debe inicializar el circuito

analogico del ADC.

Los ciclos de muestreo y retencion se cuentan a partir del momento en que se inicia la

conversion, o sea, despues de setear el bit ADSC, del registro ADCSRA. Para comprender esto

debemos saber que el ADC no capta la seal a convertir directamente del pin ADCx, sino que

primero espera que dicho nivel de tension se deposite en el capacitor de muestreo y retencion

, para luego iniciar la conversion desde alli. El tiempo que demora este capacitor en

cargarse se denomina periodo de muestreo y retencion o a veces tiempo de adquisicion. Este

varia principalmente de acuerdo con la impedancia Rs del circuito externo al canal del ADC. El

ADC del AVR esta optimizado para acoplarse a impedancias de 10K o inIerior.

Circuito de entrada del ADC de los megaAVR.

Junto con su resolucion el tiempo de conversion es el parametro mas importante de un ADC.

Para Iines practicos esto se calcula como la suma del tiempo de conversion en si (el que

acabamos de describir) mas el tiempo de adquisicion. Por ejemplo, segun la tabla de arriba, las

conversiones normales de entrada unica, que son las mas usadas, demoran 131.5 14.5 ciclos.

Si el ADC trabajara a su maxima Irecuencia recomendada de 200kHz, cada ciclo duraria

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 14

1/200kHz 5us. De aqui concluimos que cada una de estas conversiones en realidad toma

14.5*5 72.5us y que en un segundo se pueden realizar hasta 1/72.5u 13793 conversiones ~

14 kSPS. Por si acaso, la unidad kSPS signiIica kilo Samples Per Second. El datasheet dice que

llega a 15 kSPS pero ya ves que segun nuestros calculos no sale asi. Como sea, es un conversor

bastante lento para mi gusto

INTERRUPCIN DEL ADC Y MODO SLEEP

Recordemos que el modo Sleep es un estado en que se detienen las diversas ramiIicaciones del

oscilador del sistema y dependiendo de las ramiIicaciones que se congelen se pueden conocer

varios modos Sleep. Pues bien, son dos los modos Sleep que nos competen en esta ocasion.

Idle mode. Es el estado de sueo menos proIundo que existe en los AVR. Aqui solo se congelan

los relojes del CPU y de la memoria FLASH, permitiendo que los demas periIericos como el

USART, TWI, SPI, los Timers,. y, por supuesto, el ADC, continuen trabajando normalmente.

ADC Noise Reduction Mode, o modo de reduccion de ruido del ADC. Es el segundo estado de

sueo y, por su nombre, Iue diseado para que el ADC opere sin interIerencias, o sea, aunque

normalmente se piensa en el modo Sleep como una Iorma de ahorrar energia, el principal objeto

de usar el ADC en este estado es tomar la seal analogica sin presencia del ruido de

conmutacion inherente de los otros componentes del microcontrolador. Aparte del CPU en este

estado se congelan todos los periIericos relacionados con las transIerencias de datos (USART,

SPI, etc.) quedando como despertadores solo las interrupciones asincronas, aparte del ADC, por

supuesto.

El evento que puede disparar la interrupcion del ADC es la conclusion de una conversion. En

ese instante, al mismo tiempo que se limpia el bit ADSC, se activara al Ilag ADIF. El bit ADIF

se limpia por hardware al ejecutarse la Iuncion de interrupcion ISR y si no se va a utilizar dicha

Iuncion tambien se puede limpiar por soItware escribiendo un uno.

La interrupcion del ADC se habilita seteando el bit ADIE, obviamente aparte de I de SREG.

Registro ADCSRA

ADEN ADSC ADATE ADIF ADIE ADPS2 ADPS1 ADPS0

Para realizar conversiones en modo ADC Noise Reduction se deben seguir los siguientes pasos.

El ADC debe estar habilitado, debe estar conIigurado para conversiones normales, no

debe tener una conversion en curso y debe tener habilitada la interrupcion del ADC.

Entrar en modo ADC Noise Reduction o Idle mode. El ADC iniciara la conversion

apenas se detenga el CPU.

Al terminar la conversion, la interrupcion del ADC despertara el CPU y se ejecutara la

rutina de interrupcion respectiva.

Debemos observar que el ADC no se apagara automaticamente al entrar en otros modos Sleep

que no sean Idle o ADC Noise Reduction. Se recomienda por tanto apagarlo manualmente

escribiendo cero en el bit ADEN para evitar desperdicio de energia. Si el ADC esta habilitado

en dichos modos Sleep y se desea realizar conversiones diIerenciales, se recomienda apagar y

luego encender el ADC despues de salir del modo Sleep para asegurar que se obtengan

resultados validos

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 15

REGISTROS DEL MDULO ADC

ADCSRA: ADC Control and Status Register A

Registro ADCSRA

ADEN ADSC ADATE ADIF ADIE ADPS2 ADPS1 ADPS0

Registro de Microcontrolador

ADEN

ADC Enable

Escribiendo uno en este bit se habilita el ADC. Escribiendo un cero el ADC se apaga. Si se apaga el

ADC cuando hay una conversion en progreso, se interrumpira y terminara dicha conversion.

ADSC

ADC Start Conversion

En modo de conversion normal escribir uno en este bit iniciara una conversion. En modo de

conversiones auto-disparadas, escribir uno en este bit iniciara la primera conversion. La primera

conversion despues de escribir en ADSC tras iniciar el ADC o si ADSC Iue escrito al mismo tiempo que

se habilito el ADC, tomara 25 ciclos de reloj del ADC en lugar de los 13 ciclos habituales. La primera

conversion conlleva la inicializacion del ADC.

ADSC se leera como uno mientras la conversion este en progreso. Al terminar la conversion este bit

retornara a cero. Escribir cero en este bit no tiene eIecto.

ADATE

ADC Auto Trigger Enable

Cuando se escribe uno en este bit se habilitan las conversiones automaticas del ADC. El ADC iniciara

una conversion en el Ilanco positivo de la seal de disparo seleccionada. La Iuente de disparo se

selecciona por los bits ADTS en el registro ADCSRB.

ADIF

ADC Interrupt Flag

Este bit se setea cuando termina una conversion y se actualizan los registros los registros de datos. La

interrupcion de Conversion de ADC Completada se ejecuta cuando valgan uno los bits ADIE e I de

SREG.

El Ilag ADIF se limpiara automaticamente por hardware cuando se ejecute la correspondiente rutina de

interrupcion ISR. Alternativamente, ADIF se limpia escribiendole un uno. Observa que ejecutar una

instruccion de Lectura-ModiIicacion-Escritura en ADCSRA puede deshabilitar una interrupcion

pendiente. Esto tambien se aplica cuando se usan las instrucciones SBI y CBI.

ADIE

ADC Interrupt Enable

Cuando se escribe uno en este bit y el bit I de SREG vale uno se activa la interrupcion de Conversion de

ADC Completada.

ADPS2:0

ADC Prescaler Select Bits

Estos bits determinan el Iactor de division entre la Irecuencia del XTAL y el reloj de entrada del ADC.

Tabla ADPS2

ADPS2 ADPS1 ADPS0 Factor de Divisin

0 0 0 2

0 0 1 2

0 1 0 4

0 1 1 8

1 0 0 16

1 0 1 32

1 1 0 64

1 1 1 128

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 16

ADCSRB: ADC CONTROL AND STATUS REGISTER B

Registro ADCSRB

--- ACME --- --- --- ADTS2 ADTS1 ADTS0

Registro de Microcontrolador

ACME

Analog Comparator Multiplexer Enable

Al escribir uno en este bit estando el ADC apagado (ADEN en ADCSRA es cero), el

multiplexor del ADC selecciona la entrada negativa del Comparador Analogico.

Cuando se escribe cero en este bit, la entrada negativa del Comparador Analogico

sera AIN1.

ADTS2:0

ADC Auto Trigger Source

Si el bit ADATE de ADCSRA vale uno, la conIiguracion de los bits ADTS2:0

selecciona la Iuente de las conversiones auto-disparadas del ADC.

Si ADATE vale cero, la conIiguracion de ADTS2:0 no tendra eIecto. La conversion

se inicia en el Ilanco de subida de la seal seleccionada. Observa que cambiar de una

Iuente de disparo que vale cero a una Iuente que vale uno generara un Ilanco de

subida en la seal de disparo, y si el bit ADEN de ADCSRA vale uno, esto iniciara

una conversion. El cambio al Modo de Corrida Libre (ADTS2:0 000) no originara

un evento de disparo, incluso si esta activado el Ilag de interrupcion del ADC.

Tabla ADTS2

ADTS2 ADTS1 ADTS0 Fuente de disparo

0 0 0 Modo de Corrida Libre

0 0 1 Comparador Analogico

0 1 0 Interrupcion Externa INT0

0 1 1 Coincidencia del Timer/Counter0

1 0 0 Desbordamiento del Timer/Counter0

1 0 1 Coincidencia B del Timer/Counter1

1 1 0 Desbordamiento del Timer/Counter1

1 1 1 Evento de Captura del Timer/Counter1

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 17

ADMUX: ADC MULTIPLEXER SELECTION REGISTER

Registro ADMUX

REFS1 REFS0 ADLAR MUX4 MUX3 MUX2 MUX1 MUX0

Registro de Microcontrolador

REFS1:0

Reference Selection Bits

Estos bits seleccionan los voltajes de reIerencia del ADC, como se muestra en la

siguiente tabla. Si estos se cambian durante una conversion, el cambio no tendra

eIecto hasta que termine la conversion (hasta que se ponga a uno el Ilag ADIF en

ADCSRA). Si se usa un voltaje de reIerencia aplicado al pin AREF, no se podran

usar las opciones de voltaje de reIerencia internos.

Nota: Si se seleccionan canales diIerenciales, solo se podra usar 2.56V como

Voltaje de ReIerencia Interno.

Tabla REFS1

REFS1 REFS0 Voltaje de Referencia Vref+ Seleccionado (ATmega 4xx)

0 0 Pin AREF, VreI Interno desconectado

0 1 Pin AVCC con capacitor externo en el pin AREF

1 0

Voltaje de ReIerencia Interno de 1.1V

con capacitor externo en el pin AREF

1 1

Voltaje de ReIerencia Interno de 2.56V

con capacitor externo en el pin AREF

ADLAR

ADC Left Adjust Result

El bit ADLAR aIecta la representacion del resultado de la conversion en los

registros de datos del ADC. Al escribir uno en ADLAR el resultado se justiIicara a

la izquierda, de otro modo, el resultado se justiIica a la derecha. El cambio del bit

ADLAR aIectara inmediatamente los registros de datos del ADC, sin importar si

hay conversiones en curso.

MUX4:0

Analog Channel and Gain Selection Bits

El valor de estos bits selecciona la combinacion de las entradas analogicas que se

conectan al ADC. Estos bits tambien seleccionan la ganancia de los canales

diIerenciales. Para mas inIormacion ver la seccion Seleccion del Canal de

Conversion. Si se cambian estos bits durante una conversion, el cambio no tendra

eIecto hasta que se complete la conversion en curso (hasta que el bit ADIF de

ADCSRA se ponga a uno).

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 18

ADCH Y ADCL: ADC DATA REGISTER

Registro ADCH

Registro ADCL

Registro de Microcontrolador

ADC Conversion Result

Cuando termine una conversion del ADC el resultado sera almacenado en estos dos registros.

Si se usan canales diIerenciales, el resultado se presentara en Iormato de complemento a dos.

Al leer ADCL los registros de datos del ADC no se actualizan hasta que se lea ADCH. Como

consecuencia, si el resultado se justiIica a la izquierda y si no se requiere de mas de 8 bits de

precision, bastara con leer ADCH. De otro modo, ADCL se debera ser el primer registro en

leer.

El bit ADLAR del ADMUX y los bits MUXn de ADMUX aIectan el modo en que se lee el

resultado de estos registros. Si ADLAR vale uno, el resultado se justiIica a la izquierda. Si

ADLAR vale cero (valor por deIecto), el resultado se justiIica a la derecha.

DIDR0: Digital Input Disable Register 0

Registro DIDR0

ADC7D ADC6D ADC5D ADC4D ADC3D ADC2D ADC1D ADC0D

Registro de Microcontrolador

Bit 7:0

ADC7D..ADC0D: ADC7:0 Digital Input Disable

Cuando se escribe uno en este bit, se deshabilita el buIIer de entrada digital

correspondiente al pin ADCx. Si este bit vale uno, el correspondiente bit del registro

PIN se leera siempre como cero. Cuando se aplica una seal analogica al pin ADC7.0 y

no se necesita la entrada digital de este pin, este bit se deberia setear para reducir el

consumo de energia en el buIIer de entrada digital

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 19

PRACTICA 1

MODULO ADC

CONVERSION DE SEAL ANALOGICA A DIGITAL CON

EL ATMEGA8

FUNDAMENTO TEORICO

El Conversor Analgico a Digital del ATMEGA8 tiene una resolucin de

conversin de 10bits de hasta 15kSPS, 6 canales Analgicos, Ajuste a

derecha i izquierda del resultado de la conversin, Voltajes de referencia, 2

modos de conversin: simple y continuo, Interrupcin en el momento de la

conversin completada, cancelacin de ruido activando modo Sleep, y

algunos m que se pueden ver en la hoja de datos.

El mtodo de conversin que usa el micro es de aproximaciones sucesivas.

Los registros involucrados con el Conversor A/D son:

ADMUX - ADC Multiplexer Selection Register - ADMUX

ADCSRA - ADC Control and Status Register A

ADCL and ADCH - The ADC Data Register

ADMUX - ADC Multiplexer Selection Register - ADMUX

Este registro es muy importante ya que en el se realizan la mayora de las

configuraciones para el ADC:

Bit 7:6 - REFS1:0: Reference Selection Bits:Se utilizan para seleccionar el tipo

de voltaje de referncia que se usar, si interno, externo o deshabilitado, segn la

tabla:

Bit 5 - ADLAR: ADC Left Adjust Result: Configurado con 1, ajustar el resultado

de la conversin en los registros ADCH y ADCL a la Izquierda, caso contrario con un

0 lo har a la derecha, esto lo veremos ms adelante con unas imgenes.

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 20

Bits 3:0 - MUX3:0: Analog Channel Selection Bits: Estos bits seleccionarn el

canal analgico que se usar en la presente conversin, de acuerdo a la siguiente

tabla:

ADCSRA - ADC Control and Status Register A

En este registro se hacen las dems configuraciones y tambin se tiene los bits de

control de inicio/fin de conversin.

Bit 7 - ADEN: ADC Enable: Es la habilitacin del ADC para su uso (1), caso

contrario el ADC estar apagado (0)

Bit 6 - ADSC: ADC Start Conversion: Colocando un 1 en este bit se inicia la

conversin analgica, ya sea en modo normal o en modo contnuo, salvo que en el

contnuo no har falta volverlo a colocar a 1 cuando se necesite otra conversin, lo

que si se debe hacer en modo normal, ya que el conversor en este modo coloca a

cero por hardware a este bit cuando la conversin AD se ha terminado

Bit 5 - ADFR: ADC Free Running Select: Con 1 se habilita el modo contnuo

(free running), y el ADC muestrear y actualizar los registros de datos de la

conversin contnuamente, colocando un 0 el modo contnuo se detiene.

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 21

Bit 4 - ADIF: ADC Interrupt Flag: Este bit se coloca a 1 cuando la conversin AD

es completada y los registros de datos de la conversin son actualizados. Se

ejecutar la rutina de interrupcin si esta implementada y se tiene configurada las

mscaras correspondientes para esta interrupcin y el bit de Interrupciones

globales, y se pondr a 0 por hardware al terminar la rutina de interrupcin.

Bit 3 - ADIE: ADC Interrupt Enable: Es la mscara de habilitacin para la

interrupcin por Conversin AD completada, se la habilita colocando un 1.

Bits 2:0 - ADPS2:0: ADC Prescaler Select Bits: Estos bits determinan el divisor

entre la frecuencia del Osilador principal y la entrada de reloj del ADC, es segn la

tabla:

ADCL and ADCH - The ADC Data Register

Por ltimo los registros de datos donde se almacena el resultado de 10bits de la

conversin AD, que son de dos formas segn la justificacin configurada en ADLAR

ADLAR=0

ADLAR=1

Cuando la conversin AD ha sido completada, el resultado puede ser encontrado en

stos 2 registros, en el formato que ADLAR indique, primero se debe leer ADCL y

posteriormente ADCH. Si no ms de 8 bits de resolucin son necesarios se puede

usar ADLAR=1 y leer directamente ADCH.

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 22

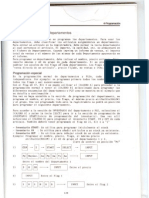

PRACTICA1 -ADC

En este ejemplo veremos cmo funciona el ADC de 10bits de resolucin del micro,

usaremos un potencimetro conectado en el canal 0 el cual nos dar los diferentes

valores de tensin analgica entre 0 y 5V. Visualizaremos el dato convertido en 10

LEDs conectados en el puertoD y los restantes 2 en los bits menos

significativos del puerto B.

PROGRAMA

;Programa: Conversor A/D de 10bits

;Notas:Este programa realiza una conversin de una tensin analgica a valores

;digitales de 10bits

;

;Registros: r16 para configuraciones de los puertos, del ADC, y para lectura de la

;conversin. r17 y r18 para retardos.

;

MODULO ADC

1O BITS

VISUALIZACION 5

0

%

RV2

1k

CANAL 0

PC0

ATMEGA8

PB0/CP1

14

PB1/OC1A

15

PB2/SS/OC1B

16

PB3/MOS/OC2

17

PB4/MSO

18

PB5/SCK

19

PB6/TOSC1/XTAL1

9

PB7/TOSC2/XTAL2

10

PC6/RESET

1

PD0/RXD

2

PD1/TXD

3

PD2/NT0

4

PD3/NT1

5

PD4/T0/XCK

6

PD5/T1

11

PD6/AN0

12

PD7/AN1

13

PC0/ADC0

23

PC1/ADC1

24

PC2/ADC2

25

PC3/ADC3

26

PC4/ADC4/SDA

27

PC5/ADC5/SCL

28

AREF

21

AVCC

20

U1

ATMEGA8

8

5

%

RV1

1k

D1

LED-YELLOW

D2

LED-YELLOW

.

.

D4

.

D5

-

D6

LED-YELLOW

D7

LED-YELLOW

D8

LED-YELLOW

D9

LED-YELLOW

D10

LED-YELLOW

CONVERSION DE SELAN ANALOGICA A DIGITAL

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 23

;Conexiones: ADC0/C0 -> Potenciometro a Vcc y Gnd

; D0-D7 -> Led's

;B0 y B1 -> Led's

;--------------------------------------------------------------------------------

;DIRECTIVAS EN ENSAMBLADOR

.include "m8def.inc" ;ATmega8

;reset-vector address $0000

.org $0000

rjmp main ;ve al main

;PROGRAMA PRINCIPAL

main:

ldi r16,$04 ;Configuracion de...

out sph,r16

ldi r16,$5F

out spl,r16 ;...la pila: Stack: $045F=RAMEND

clr r16 ;r16 <- $00

out ddrc,r16 ;portC entrada

ser r16 ;r16 <- $ff

out ddrd,r16 ;portD salidas

out ddrb,r16 ;portB salidas

ldi r16,$40 ;r16 <- $40

out admux,r16 ;configuro ADC a canal0, ajuste a derecha y referencia en Vref con cap

ldi r16,$85 ;r16 <- $85

out adcsra,r16 ;habilito ADC, interrupcion y free running desactivados, divisor 32

rcall delay200u ;retardo para inicializar el conversor A/D

;se necesita 25 cilos del clock ADC, el clock ADC esta puesto a 4MHz/32=125kHz

;25 ciclos de 125Khz, es 200us que se debe esperar para la configuracin de todo el circuito

;interno del conversor A/D del micro

loop:

sbi adcsra,adsc ;se inicia conversion A/D, seteando el bit adsc

convertir:

sbis adcsra,adsc ;pregunto por el bit de conversin terminada

rjmp leer ;si termino la conversin, voy a leer la conversin

rjmp convertir ;si no se sigue esperando hasta que termine

leer: ;rutina de lectura de los datos convertidos

in r16,adcl ;carga el valor de ADCL en r16

out portd,r16 ;muestra por el puertoD

in r16,adch ;carga el valor de ADCH en r16

out portb,r16 ;muestra por el puertoB

rcall delay25m ;retardo para visualizar, puede no ser necesario

rjmp loop ;bucle infinito

; =============================

; delay loop generator

; 100000 cycles:

; -----------------------------

; delaying 99990 cycles:

delay25m:

ldi R17, $A5

YY1: ldi R18, $C9

XX1: dec R18

brne XX1

dec R17

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELCTRICA Y ELECTRNICA

MICROCONTROLADORE -ATMEGA8 24

brne YY1

; -----------------------------

; delaying 9 cycles:

ldi R17, $03

ZZ1: dec R17

brne ZZ1

; -----------------------------

; delaying 1 cycle:

nop

ret

; =============================

; delay loop generator

; 800 cycles:

; -----------------------------

; delaying 798 cycles:

delay200u:

ldi R17, $02

YY2: ldi R18, $84

XX2: dec R18