Documente Academic

Documente Profesional

Documente Cultură

Memory Organisation

Încărcat de

sansureDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Memory Organisation

Încărcat de

sansureDrepturi de autor:

Formate disponibile

MEMORY ORGANISATION: MEMORY ORGANIZATION Memory organization is two-fold !

irst we dis"#ss t$e $ardware %&$ysi"al' organization( t$en t$e internal ar"$ite"t#re T$e ty&e of "om&#ter and its size do not refle"t t$e ty&e of memories t$at t$e "om&#ter #ses Some "om&#ters $a)e a mi*t#re of memory ty&es !or e*am&le( t$ey may #se some ty&e of magneti" memory %"ore or film' and also a semi"ond#"tor memory %stati" or dynami"' T$ey also $a)e a read-only memory w$i"$ is #s#ally a &art of t$e +,- Memory in a "om&#ter "an )ary from one or more mod#les to one or more &"./s( de&ending on t$e "om&#ter ty&e T$e larger mainframe "om&#ters #se t$e mod#lar arrangement( m#lti&le mod#les %fo#r or more'( to ma0e #& t$eir memories 1$ereas( mini"om&#ters and mi"ro"om&#ters #se "$assis or assem.lies( "ages or ra"0s( and mot$er.oard or .a"0&lane arrangements Minis and mi"ros #se m#lti&le "om&onents on one &". or gro#&s of &"./s to form t$e memory T$ere are se)eral ways to organise memories wit$ res&e"t to t$e way t$ey are "onne"ted to t$e "a"$e: one-word-wide memory organisation wide memory organisation interlea)ed memory organisation inde&endent memory organization One-1ord-1ide T$e memory is one word wide and "onne"ted )ia a one word wide .#s to t$e "a"$e 1ide T$e memory is more t$an one word wide %#s#ally fo#r words wide' and "onne"ted .y an e2#ally wide .#s to t$e low le)el "a"$e %w$i"$ is also wide' !rom t$e "a"$e m#lti&le .#sses of one word wide go to a M-3 w$i"$ sele"ts t$e "orre"t .#s to "onne"t to t$e $ig$ le)el "a"$e Interlea)ed T$ere are se)eral memory .an0s w$i"$ are one word wide( and one one word wide .#s T$ere is some logi" in t$e memory t$at sele"ts t$e "orre"t .an0 to #se w$en t$e memory gets a""essed .y t$e "a"$e Memory interlea)ing is a way to distri.#te indi)id#al addresses o)er memory mod#les Its aim is to 0ee& t$e most of mod#les .#sy as "om&#tations &ro"eed 1it$ memory interlea)ing( t$e low-order 0 .its of t$e memory address sele"t a mod#le( and t$e $ig$order m .its name a lo"ation wit$in t$at mod#le 4en"e( "onse"#ti)e addresses are lo"ated in s#""essi)e mod#les A re2#est to a""ess "onse"#ti)e memory lo"ations "an 0ee& se)eral mod#les .#sy at t$e same time Inde&endent T$ere are se)eral .an0s( w$i"$ "an all .e a""essed sim#ltaneo#sly .y se)eral .#ses Memory geometry In t$e design of modern &ersonal "om&#ters( memory geometry des"ri.es t$e internal str#"t#re of random-a""ess memory Memory geometry is of "on"ern to "ons#mers #&grading t$eir "om&#ters( sin"e older memory "ontrollers may not .e "om&ati.le wit$ later &rod#"ts Memory geometry terminology "an .e "onf#sing .e"a#se of t$e n#m.er of o)erla&&ing terms

,$ysi"al feat#res Memory geometry des"ri.es t$e logi"al "onfig#ration of a RAM mod#le( .#t "ons#mers will always find it easiest to gras& t$e &$ysi"al "onfig#ration M#"$ of t$e "onf#sion s#rro#nding memory geometry o""#rs w$en t$e &$ysi"al "onfig#ration o.f#s"ates t$e logi"al "onfig#ration T$e first defining feat#re of RAM is form fa"tor RAM mod#les "an .e in "om&a"t SO-5IMM form for s&a"e "onstrained a&&li"ations li0e la&to&s( &rinters( em.edded "om&#ters( and small form fa"tor "om&#ters( and in 5IMM format( w$i"$ is #sed in most des0to&s T$e ot$er &$ysi"al "$ara"teristi" determine wit$ .y &$ysi"al e*amination are t$e n#m.er of memory "$i&s( and w$et$er .ot$ sides of t$e memory 6sti"06 are &o&#lated If 7 is a fa"tor of t$e n#m.er of memory de)i"es or "$i&s %or more generally( a &ower of two'( t$en t$e mod#le does not feat#re E++( if 8 is a fa"tor of t$e n#m.er of memory "$i&s %or one more t$an a &ower of two'( t$en t$e mod#le does RAM mod#les are 90eyed9 .y indentations on t$e sides( and along t$e .ottom of t$e mod#le T$is determines t$e te"$nology( and "lassifi"ation of t$e mod#les( for instan"e w$et$er it is 55R:( or 55R;( and w$et$er it is s#ita.le for des0to&s( or for ser)ers It is im&ortant to ma0e s#re t$at t$e 0eying of t$e mod#le mat"$es t$e 0ey of t$e slot it is intended to o""#&y Additional( non-memory "$i&s on t$e mod#le are an indi"ation t$at it "o#ld .e designed for $ig$ "a&a"ity memory systems for ser)ers( and t$at t$e mod#le may .e in"om&ati.le wit$ des0to& systems As t$e ne*t se"tion of t$is arti"le will "o)er t$e logi"al ar"$ite"t#re( w$i"$ "o)ers t$e logi"al str#"t#re s&anning e)ery &o&#lated slot in a system( t$e &$ysi"al feat#res of t$e slots t$emsel)es .e"omes im&ortant <y "ons#lting t$e do"#mentation of yo#r mot$er.oard( or reading t$e la.els on t$e .oard itself( yo# "an determine t$e #nderlying logi"al str#"t#re of t$e slots 1$en t$ere is more t$an one slot( t$ey are n#m.ered( and w$en t$ere is more t$an one "$annel( t$e different slots are se&arated in t$at way as well #s#ally "olor-"oded =edit> ?ogi"al feat#res In t$e 8@s s&e"ialized "om&#ters were released w$ere two "om&#ters t$at ea"$ $ad t$eir own memory "ontroller "o#ld .e networ0ed at s#"$ a low le)el t$at t$e software r#n "o#ld #se t$e memory( or +,- of eit$er "om&#ter as if t$ey were one #nit 1it$ AM59s release of t$e O&teron( and Intel9s "orres&onding systems systems t$at s$are more t$an one memory "ontroller in a single system $a)e .e"ome "ommon in a&&li"ations t$at re2#ire t$e &ower of more t$an one "ommon des0to& !or t$ese systems s"$emes li0e Non--nified Memory Ar"$ite"t#re are #sed +$annels are t$e $ig$est le)el str#"t#re at t$e lo"al memory "ontroller le)el Modern "om&#ters "an $a)e two( t$ree or e)en more "$annels It is #s#ally im&ortant t$at( for ea"$ mod#le in any one "$annel( t$ere is a logi"ally identi"al mod#le in t$e same lo"ation on ea"$ of t$e ot$er &o&#lated "$annels Mod#le "a&a"ity is t$e aggregate s&a"e in a mod#le meas#red in .yte( or - more generally - in words Mod#le "a&a"ity is e2#al to t$e &rod#"t of t$e ran0 density and t$e n#m.er of ran0s( and w$ere t$e ran0 density is t$e &rod#"t of ran0 de&t$( and ran0 widt$=A> T$e standard format for e*&ressing t$is s&e"ifi"ation is %ran0 density' M.it * %ran0 widt$'*%n#m.er of ran0s' <an0s are one of t$e "$ief so#r"es of &$ysi"alBlogi"al "onf#sion <an0s are a logi"al distin"tion t$at "orres&onds to +SRows in low le)el addressing( for more details on t$e

addressing of RAM in t$is ,OC( see dynami" random a""ess memory As memory density $as in"reased( t$e n#m.ers of ran0s in ea"$ "$i& $as also in"reased As an e*am&le of a sim&le "onfig#ration( say t$ere is one mod#le wit$ D "$i&s( or de)i"es( on ea"$ side( and one ran0 in ea"$ of t$e AE "$i&s( and ea"$ .an0 was D .its wide( t$at mod#le wo#ld $a)e one .an0 for ea"$ side One .an0 on one side( and one .an0 on t$e .a"0 Today yo# "o#ld $a)e a mod#le "om&osed of Mi"ron MT7F4A:DMAE "$i&s wit$ t$e organization AEM. * AE * D wit$ a .an0 widt$ of AE 1it$ a mod#le w$i"$ $as of D of t$ose on ea"$ side( t$ere wo#ld .e : 6*AE6 6.an0s6 on ea"$ side Memory "ontrollers s#"$ as t$e Intel 87G +$i&set list t$e "onfig#rations t$ey s#&&ort: 6S#&&orts :GE-M.( GA:-M.( and A-G. 55R: te"$nologies for *D and *AE de)i"es 6 6S#&&orts fo#r .an0s for all 55R: de)i"es #& to GA:-M.it density S#&&orts eig$t .an0s for A-G.it 55R: de)i"es 6 As an e*am&le( ta0e an i87G memory "ontroller wit$ 7 Hingston H43E7@@5:BAGs Hingston des"ri.es ea"$ mod#le as $a)ing a geometry of A:DM*E7( meaning t$at ea"$ one $as E7 .its A:D million dee&( e2#aling D A8: .illion .its( or A @:7 Giga.ytes Hingston des"ri.es ea"$ 6de)i"e6( or "$i& as $a)ing a geometry of E7M*D( so ea"$ mod#le $as fo#r .an0s So from t$e M+4 ,OC w$en t$ere are 7 AG< mod#les( it sees : "$annels( ea"$ wit$ D .an0s 4ierar"$y of organization Memory "$i& T$e lowest form of organization "o)ered .y memory geometry( sometimes "alled 6memory de)i"e6 T$ese are t$e "om&onent I+s t$at ma0e #& ea"$ mod#le( or mod#le of RAM T$e most im&ortant meas#rement of a "$i& is its density( meas#red in .its <e"a#se memory .#s widt$ is #s#ally larger t$an t$e n#m.er of "$i&s( most "$i&s are designed to $a)e widt$( meaning t$at t$ey are di)ided into e2#al &arts internally( and w$en one address 6de&t$6 is "alled #&( instead of ret#rning I#st one )al#e( more t$an one )al#e is ret#rned In addition to t$e de&t$( a se"ond addressing dimension $as .een added at t$e "$i& le)el( .an0s <an0s allow one .an0 to .e a)aila.le( w$ile anot$er .an0 is #na)aila.le .e"a#se it is refres$ing An e*am&le of "$i& notation is E7M. %de&t$' 3 D %widt$' 3 D <an0s =edit> Memory mod#le Some meas#rements of mod#les are size( widt$( s&eed( and laten"y A memory mod#le "onsists of a m#lti&le of t$e memory "$i&s to e2#al t$e desired mod#le widt$ So a ;: .it SIMM mod#le "o#ld .e "om&osed of fo#r D-.it wide %*D' "$i&s As noted in t$e memory "$annel &art( one &$ysi"al mod#le "an .e made #& of one or more logi"al ran0s If t$at ;: .it simm were "om&osed of eig$t D-.it "$i&s t$e simm wo#ld $a)e two ran0s An e*am&le of Mod#le notation is A:DM. * E7-.it =edit> Memory "$annel A memory "$annel is made #& of ran0s ,$ysi"ally a memory "$annel wit$ I#st one memory mod#le mig$t &resent itself as $a)ing one or more logi"al ran0s =edit> +ontroller organization T$is is t$e $ig$est le)el In a ty&i"al "om&#ter t$ere will only .e a single memory "ontroller wit$ only one or two "$annels T$e logi"al feat#res se"tion des"ri.ed N-MA "onfig#rations( w$i"$ "an ta0e t$e form of a networ0 of memory "ontrollers !or e*am&le( ea"$ so"0et of a two so"0et AM5 HD "an $a)e a two "$annel memory "ontroller( gi)ing t$e system a total of fo#r memory "$annels

Random-a""ess memory Random-a""ess memory %RAM' is a form of "om&#ter data storage Today( it ta0es t$e form of integrated "ir"#its t$at allow stored data to .e a""essed in any order %t$at is( at random' 6Random6 refers to t$e idea t$at any &ie"e of data "an .e ret#rned in a "onstant time( regardless of its &$ysi"al lo"ation and w$et$er it is related to t$e &re)io#s &ie"e of data =A> T$e word 6RAM6 is often asso"iated wit$ )olatile ty&es of memory %s#"$ as 5RAM memory mod#les'( w$ere t$e information is lost after t$e &ower is swit"$ed off Many ot$er ty&es of memory are RAM as well( in"l#ding most ty&es of ROM and a ty&e of flas$ memory "alled NOR-!las$ Ty&es of RAM Modern ty&es of writa.le RAM generally store a .it of data in eit$er t$e state of a fli&flo&( as in SRAM %stati" RAM'( or as a "$arge in a "a&a"itor %or transistor gate'( as in 5RAM %dynami" RAM'( E,ROM( EE,ROM and !las$ Some ty&es $a)e "ir"#itry to dete"t andBor "orre"t random fa#lts "alled memory errors in t$e stored data( #sing &arity .its or error "orre"tion "odes RAM of t$e read-only ty&e( ROM( instead #ses a metal mas0 to &ermanently ena.leBdisa.le sele"ted transistors( instead of storing a "$arge in t$em Of s&e"ial "onsideration is SIMM and 5IMM memory mod#les SRAM and 5RAM are )olatile Ot$er forms of "om&#ter storage( s#"$ as dis0s and magneti" ta&es( $a)e .een #sed as &ersistent storage Many newer &rod#"ts instead rely on flas$ memory to maintain data w$en not in #se( s#"$ as ,5As or small m#si" &layers +ertain &ersonal "om&#ters( s#"$ as many r#gged "om&#ters and net.oo0s( $a)e also re&la"ed magneti" dis0s wit$ flas$ dri)es 1it$ flas$ memory( only t$e NOR ty&e is "a&a.le of tr#e random a""ess( allowing dire"t "ode e*e"#tion( and is t$erefore often #sed instead of ROMJ t$e lower "ost NAN5 ty&e is "ommonly #sed for .#l0 storage in memory "ards and solid-state dri)es A memory "$i& is an integrated "ir"#it %I+' made of millions of transistors and "a&a"itors In t$e most "ommon form of "om&#ter memory( dynami" random a""ess memory %5RAM'( a transistor and a "a&a"itor are &aired to "reate a memory "ell( w$i"$ re&resents a single .it of data T$e "a&a"itor $olds t$e .it of information K a @ or a A T$e transistor a"ts as a swit"$ t$at lets t$e "ontrol "ir"#itry on t$e memory "$i& read t$e "a&a"itor or "$ange its state Memory $ierar"$y Many "om&#ter systems $a)e a memory $ierar"$y "onsisting of +,- registers( on-die SRAM "a"$es( e*ternal "a"$es( 5RAM( &aging systems( and )irt#al memory or swa& s&a"e on a $ard dri)e T$is entire &ool of memory may .e referred to as 6RAM6 .y many de)elo&ers( e)en t$o#g$ t$e )ario#s s#.systems "an $a)e )ery different a""ess times( )iolating t$e original "on"e&t .e$ind t$e random a""ess term in RAM E)en wit$in a $ierar"$y le)el s#"$ as 5RAM( t$e s&e"ifi" row( "ol#mn( .an0( ran0( "$annel( or interlea)e organization of t$e "om&onents ma0e t$e a""ess time )aria.le( alt$o#g$ not to t$e e*tent t$at rotating storage media or a ta&e is )aria.le T$e o)erall goal of #sing a memory $ierar"$y is to o.tain t$e $ig$er &ossi.le a)erage a""ess &erforman"e w$ile minimizing t$e total "ost of t$e entire memory system %generally( t$e memory $ierar"$y follows t$e a""ess time wit$ t$e fast +,- registers at t$e to& and t$e slow $ard dri)e at t$e .ottom' In many modern &ersonal "om&#ters( t$e RAM "omes in an easily #&graded form of mod#les "alled memory mod#les or 5RAM mod#les a.o#t t$e size of a few sti"0s of

"$ewing g#m T$ese "an 2#i"0ly .e re&la"ed s$o#ld t$ey .e"ome damaged or w$en "$anging needs demand more storage "a&a"ity As s#ggested a.o)e( smaller amo#nts of RAM %mostly SRAM' are also integrated in t$e +,- and ot$er I+s on t$e mot$er.oard( as well as in $ard-dri)es( +5-ROMs( and se)eral ot$er &arts of t$e "om&#ter system <y "on)ention( .#s and networ0 data rates are denoted eit$er in .itBs %.its &er se"ond' or .yteBs %.ytes &er se"ond' In general( &arallel interfa"es are 2#oted in .yteBs and serial in .itBs T$e more "ommonly #sed is s$own .elow in .old ty&e On de)i"es li0e modems( .ytes may .e more t$an D .its long .e"a#se t$ey may .e indi)id#ally &added o#t wit$ additional start and sto& .itsJ t$e fig#res .elow will refle"t t$is 1$ere "$annels #se line "odes %s#"$ as Et$ernet( Serial ATA and ,+I E*&ress'( 2#oted rates are for t$e de"oded signal T$e fig#res .elow are sim&le* data rates( w$i"$ may "onfli"t wit$ t$e d#&le* rates )endors sometimes #se in &romotional materials 1$ere two )al#es are listed( t$e first )al#e is t$e downstream rate and t$e se"ond )al#e is t$e #&stream rate All 2#oted fig#res are in metri" de"imal #nits( w$ere: A <yte L D .it A 0.itBs L A(@:7 .itBs A M.itBs L A(@7D(GFE .itBs A G.itBs L A(@F;(F7A(D:7 .itBs A 0<Bs L A(@:7 <yteBs A M<Bs L A(@7D(GFE <yteBs A G<Bs L A(@F;(F7A(D:7 <yteBs A T<Bs L A(@88(GAA(E:F(FFE <yteBs T$ese de"imal &refi*es $a)e .een esta.lis$ed in data "omm#ni"ations for long time( also .efore A88D w$en IE+ and ot$er organizations tried to ma0e it standard for all "om&#ting a&&li"ations( and introd#"ed new .inary &refi*es MEMORY SYSTEM Memory in a "om&#ter system is re2#ired for storage and s#.se2#ent retrie)al of t$e instr#"tions and data A "om&#ter system #ses )ariety of de)i"es for storing t$ese instr#"tions and data w$i"$ are re2#ired for its o&erations Normally we "lassify t$e information to .e stored on "om&#ter in two .asi" "ategories: 5ata and t$e Instr#"tions 6T$e storage de)i"es along wit$ t$e algorit$m or information on $ow to "ontrol and manage t$ese storage de)i"es "onstit#te t$e memory system of a "om&#ter 6 A memory system is a )ery sim&le system yet it e*$i.its a wide range of te"$nology and ty&es T$e .asi" o.Ie"ti)e of a "om&#ter system is to in"rease t$e s&eed of "om&#tation ?i0ewise t$e .asi" o.Ie"ti)e of a memory system is to &ro)ide fast( #ninterr#&ted a""ess .y t$e &ro"essor to t$e memory s#"$ t$at t$e &ro"essor "an o&erate at t$e s&eed it is e*&e"ted to wor0 <#t does t$is 0ind of te"$nology w$ere t$ere is no s&eed ga& .etween &ro"essor and memory s&eed e*istM T$e answer is yes t$ey do( .#t #nfort#nately as t$e a""ess time %time ta0en .y +,- to a""ess a lo"ation in memory' .e"omes less and less t$e "ost &er .it of memory .e"omes in"reasingly $ig$er In addition( normally t$ese memories re2#ire &ower s#&&ly till t$e information need to .e stored <ot$ t$ese t$ings are not )ery

"on)enient( .#t on t$e ot$er $and t$e memories wit$ smaller "ost $a)e )ery $ig$ a""ess time w$i"$ will res#lt in slower o&eration of t$e +,- T$#s( t$e "ost )s a""ess time anomaly $as lead to a $ierar"$y of memory w$ere we s#&&lement fast memories wit$ larger( "$ea&er( slower memories T$ese memory #nits may $a)e )ery different &$ysi"al and o&erationalN "$ara"teristi"s( t$erefore( ma0ing t$e memory system )ery di)erse in ty&e( "ost(N organisation( te"$nology and &erforman"e T$is memory $ierar"$y will wor0 only if t$e fre2#en"y of a""ess to t$e slower memories are signifi"antly less t$an t$e faster memories Internal ,ro"essor Memories: T$ese "onsist of t$e small set of $ig$ s&eed registers w$i"$ are internal to a &ro"essor and are #sed as tem&orary lo"ations w$ere a"t#al &ro"essing is done T$is will .e "o)ered in greater details in <lo"0 : . ,rimary Memory or Main Memory: It is a large memory w$i"$ is fast .#t not as fast as internal &ro"essor memory T$is memory is a""essed dire"tly .y t$e &ro"essor It is mainly .ased on integrated "ir"#its Se"ondary MemoryBA#*iliary MemoryB<a"0ing Store: A#*iliary memory in fa"t is m#"$ larger in size t$an main memory .#t is slower t$an main memory It normally stores system &rograms %&rograms w$i"$ are #sed .y system to &erform )ario#s o&erational f#n"tions'( ot$er instr#"tions( &rograms and data files Se"ondary memory "an also $e #sed as an o)erflow memory in "ase t$e main memory "a&a"ity $as .een e*"eeded %4owM T$e answer is not s#&&lied in t$e .lo"0 Yo# need to refer to f#rt$er readings to get t$is answer' Se"ondary memories "annot .e a""essed dire"tly .y a &ro"essor !irst t$e information of t$ese memories is transferred to t$e main memory and t$en t$e information "an .e a""essed as t$e information of main memory T$ere is anot$er 0ind of memory w$i"$ is in"reasingly .eing #sed in modern "om&#ters( t$is is "alled +a"$e memory It is logi"ally &ositioned .etween t$e internal memory %registers' and main memory It stores or "at"$es some of t$e "ontent of t$e main memory w$i"$ is "#rrently in #se of t$e &ro"essor 1e will dis"#ss a.o#t t$is memory in greater details in a s#.se2#ent se"tion of t$is #nit <efore dis"#ssing more a.o#t t$ese memories let #s first dis"#ss t$e te"$nologi"al terms "ommonly #sed in defining and a""essing t$e memory : +4ARA+TERISTI+S TERMS !OR CARIO-S MEMORY 5ECI+ES T$e following terms are most "ommonly #sed for identifying "om&arati)e .e$a)io#r of )ario#s memory de)i"es and te"$nologies Storage +a&a"ity: It is a re&resentati)e of t$e size of t$e memory T$e "a&a"ity of internal memory and main memory "an .e e*&ressed in terms of n#m.er of words or .ytes T$e storage "a&a"ity of e*ternal memory is normally meas#red in terms of .ytes -nit of transfer: -nit of transfer is defined as t$e n#m.er of .its read in or o#t of t$e memory in a single read or write o&eration( !or main memory and internal memory( t$e normal #nit of transfer of information is e2#al to t$e word lengt$ of a &ro"essor In fa"t it de&ends on n#m.er of data lines in and o#t of t$e memory mod#le %1$yM' In general( t$ese lines are 0e&t e2#al to t$e word size of t$e &ro"essor 1$at is a wordM Yo# $a)e already learnt a.o#t t$is term in -nit A of t$is .lo"0 T$e #nit of transfer of e*ternal

memory is normally 2#ite large %1$yM Yo# will find t$e answer to t$is 2#estion later in t$is #nit' and is referred to as .lo"0 of data A""ess Modes: On"e we $a)e defined t$e #nit of transfer ne*t im&ortant "$ara"teristi"s is t$e a""ess mode in w$i"$ t$e information is a""essed from t$e memory A memory is "onsidered to "onsist of )ario#s memory lo"ations T$e information from memory de)i"es "an .e a""essed in t$e following ways Random A""ess Memory %RAM': It is t$e mode in w$i"$ any memory lo"ation "an .e a""essed in any order in t$e same amo#nt of time !errite and Semi"ond#"tor memories w$i"$ generally "onstit#te main memory are of t$is nat#re T$e storage lo"ations "an $e a""essed inde&endently and t$ere e*ist se&arate a""ess me"$anism for ea"$ lo"ation Se2#ential a""ess: On t$e ot$er $and we $a)e memories w$i"$ "an .e a""essed in a &re-defined se2#en"es for e*am&le( t$e songs stored on a "assette "an .e a""essed only one .y one T$e e*am&le of se2#ential a""ess memory is Magneti" Ta&e 4ere t$e a""ess me"$anism need to .e s$ared among different lo"ations T$#s( eit$er t$e lo"ation or t$e readBwrite $ead or .ot$ s$o#ld .e mo)ed to a""ess t$e desired lo"ation 5ire"t A""ess: In "ertain "ases t$e information is neit$er a""essed randomly nor in se2#en"e .#t somet$ing in .etween In t$ese 0ind of a""ess( a se&arate readBwrite $ead e*ist for a tra"0 and on a tra"0 t$e information "an .e a""essed serially T$is semirandom mode of o&eration e*ist in magneti" dis0s A""ess Time: T$e a""ess time is t$e time re2#ired .etween t$e re2#est made for a read or write o&eration till t$e time t$e data is made a)aila.le or written at t$e re2#ested lo"ation Normally it is meas#red for read o&eration T$e a""ess time de&ends on t$e &$ysi"al "$ara"teristi"s and a""ess mode #sed for t$at de)i"e ,ermanen"e or Storage: Is it ,ossi.le to lose information .y t$e memories o)er a &eriod of timeM If yes t$en w$at "an .e t$e reasons of t$e loss of information and w$at s$o#ld .edone to a)oid itM T$ere ar" se)eral reasons for information destr#"tion( t$ese are destr#"ti)e reado#t( dynami" storage( )olatility and $ardware fail#re If for a &arti"#lar memory t$e reading &ro"ess destroys t$e stored information we "all it 5estr#"ti)e reado#t In s#"$ memories t$e information $as to .e written .a"0 on t$e same lo"ation from w$i"$ it $ad .een read after ea"$ read o&eration T$e reading &ro"ess w$ere t$e data is not destroyed on reading are referred to as Non-destr#"ti)e reado#t T$ere "an .e some memories w$ere t$e stored A looses its strengt$ to .e"ome @ o)er a &eriod of time T$ese 0ind of memories re2#ire refres$ing T$e memories w$i"$ re2#ire refres$ing are termed as dynami" memories In "ontrast( t$e memories w$i"$ do not re2#ire refres$ing are "alled stati" memories Anot$er fa"tor w$i"$ "an destroy t$e "ontents is die &resen"e and a.sen"e of ele"tri"ity T$e memories w$i"$ loses t$eir "ontent on fail#re of &ower am armed as )olatile memories( t$ose w$i"$ do not are "alled non-)olatile Magneti" memories are non)olatile and semi"ond#"tor main memories am )olatile in nat#re +y"le Time: It is defined as t$e minim#m time ela&sed .etween two "onse"#ti)e read

re2#ests Is it e2#al to a""ess timeM Yes( for most of t$e memories e*"e&t t$e ones in w$i"$ destr#"ti)e reado#t is en"o#ntered +y"le time for s#"$ memories is t$e a""ess time %time ela&sed w$en a read re2#est is made a)aila.le' &l#s writing time as after t$e data $as .een made a)aila.le t$e information $as to .e written .a"0 in t$e same memory lo"ation as t$e &re)io#s )al#e $as .een destroyed .y reading <#t for most of t$e "ommonly #sed semi"ond#"tor memories "y"le time is e2#al to t$e a""ess time

5E?AY <-!!ER: T$is se"tion des"ri.es ,OME5IA9s im&lementation of delay .#ffer 5elay .#ffer wor0s 2#ite similarly li0e a fi*ed Iitter .#ffer( t$at is it will delay t$e frame retrie)al .y some inter)al so t$at "aller will get "ontin#o#s frame from t$e .#ffer T$is "an .e #sef#l w$en t$e o&erations are not e)enly interlea)ed( for e*am&le w$en "aller &erforms .#rst of &#t%' o&erations and t$en followed .y .#rst of o&erations 1it$ #sing t$is delay .#ffer( t$e .#ffer will &#t t$e .#rst frames into a .#ffer so t$at get%' o&erations will always get a frame from t$e .#ffer %ass#ming t$at t$e n#m.er of get%' and &#t%' are mat"$ed' T$e .#ffer is ada&ti)e( t$at is it "ontin#o#sly learns t$e o&timal delay to .e a&&lied to t$e a#dio flow at r#n-time On"e t$e o&timal delay $as .een learned( t$e delay .#ffer will a&&ly t$is delay to t$e a#dio flow( e*&anding or s$rin0ing t$e a#dio sam&les as ne"essary w$en t$e a"t#al a#dio sam&les in t$e .#ffer are too low or too $ig$

E3ISTING TE+4NIP-E:

IN,-T <-!!ER: T$e In&#t .#ffer is also "ommonly 0nown as t$e in&#t area or in&#t .lo"0 1$en referring to "om&#ter memory( t$e in&#t .#ffer is a lo"ation t$at $olds all in"oming information .efore it "ontin#es to t$e +,- for &ro"essing In&#t .#ffer "an .e also #sed to des"ri.e )ario#s ot$er $ardware or software .#ffers #sed to store information .efore it is &ro"essed Some s"anners %s#"$ as t$ose w$i"$ s#&&ort Qin"l#deR files' re2#ire reading from se)eral in&#t streams As fle* s"anners do a large amo#nt of .#ffering( one "annot "ontrol w$ere t$e ne*t in&#t will .e read from .y sim&ly writing a YYSIN,-T%' w$i"$ is sensiti)e to t$e s"anning "onte*t YYSIN,-T%' is only "alled w$en t$e s"anner rea"$es t$e end of its .#ffer( w$i"$ may .e a long time after s"anning a statement s#"$ as an in"l#de statement w$i"$ re2#ires swit"$ing t$e in&#t so#r"e

::A

!IGA: IN,-T <-!!ER

MEMORY <?O+H: %RAM' Random-a""ess memory %RAM' is a form of "om&#ter data storage Today( it ta0es t$e form of integrated "ir"#its t$at allow stored data to .e a""essed in any order %t$at is( at random' 6Random6 refers to t$e idea t$at any &ie"e of data "an .e ret#rned in a "onstant time( regardless of its &$ysi"al lo"ation and w$et$er it is related to t$e &re)io#s &ie"e of data T$e word 6RAM6 is often asso"iated wit$ )olatile ty&es of memory %s#"$ as 5RAM memory mod#les'( w$ere t$e information is lost after t$e &ower is swit"$ed off Many ot$er ty&es of memory are RAM as well( in"l#ding most ty&es of ROM and a ty&e of flas$ memory "alled NOR-!las$ S"an design $as .een t$e .a"0.one of design for testa.ility %5!T' in ind#stry for a.o#t t$ree de"ades .e"a#se s"an-.ased design "an s#""essf#lly o.tain "ontrolla.ility and o.ser)a.ility for fli&-flo&s Serial S"an design $as dominated t$e test ar"$ite"t#re .e"a#se it is "on)enient to .#ild 4owe)er( t$e serial s"an design "a#ses #nne"essary swit"$ing a"ti)ity d#ring testing w$i"$ ind#"e #nne"essarily enormo#s &ower dissi&ation T$e test time also in"reases dramati"ally wit$ t$e "ontin#o#sly in"reasing n#m.er of fli&flo&s in large se2#ential "ir"#its e)en #sing m#lti&le s"an "$ain ar"$ite"t#re An alternate to serial s"an ar"$ite"t#re is Random A""ess S"an %RAS' In RAS( fli&-flo&s wor0 as addressa.le memory elements in t$e test mode w$i"$ is a similar fas$ion as random a""ess memory %RAM' T$is a&&roa"$ red#"es t$e time of setting and o.ser)ing t$e fli&flo& states .#t re2#ires a large o)er$ead .ot$ in gates and test &ins 5es&ite of t$ese draw.a"0s( t$e RAS was &aid attention .y many resear"$ers in t$ese years T$is &a&er ta0es a )iew of re"ently &#.lis$ed &a&ers on RAS and reI#)enates t$e random a""ess s"an as a 5!T met$od t$at sim#ltaneo#sly address t$ree limitations of t$e traditional serial s"an namely( test data )ol#me( test a&&li"ation time( and test &ower : Random A""ess S"an !ig A s$ows t$e .asi" ar"$ite"t#re of t$e RAS A 5e"oder is #sed to address e)ery !! T$e RAS allows reading or writing of any fli&-flo& #sing address .its w$ere QnR is t$e n#m.er of s"anned fli&-flo&s w$en t$e address is a&&lied( t$e address de"oder &rod#"es a s"an ena.le signal to t$e "orres&onding fli&-flo& needed to .e &la"ed wit$ a data from t$e s"an-in In t$is te"$ni2#e( t$e s"an f#n"tion is im&lemented as a random-a""ess memory 4en"e at e)ery gi)en time only one !! is a""essed w$ile ot$er !!s retain t$eir state T$e ar"$ite"t#res des"ri.ed in most literat#res mainly "onsists of a s"an-in signal t$at is .road"asted to e)ery !!( a test "ontrol signal t$at is .road"asted to all !!s( and a #ni2#e de"oder signal from t$e de"oder to e)ery !! A more feasi.le de"oder $as .een designed T$e grid ar"$ite"t#re s$own in !ig : is one effi"ient way to layo#t t$e de"oders 1it$ a minim#m of two layers of metal ro#ting( t$e row wires "an .e a""ommodated wit$in t$e "$annel in .etween t$e "ell rows and t$e "ol#mn wires "an .e ro#ted o)er t$e "ell in t$e ne*t metal layer 4en"e t$ere will

.e an in"rease of one tra"0 &er "$annel %ass#ming m "$annels' and n tra"0s t$at are ro#ted on t$e ne*t metal layer

!ig#re A 5esign of RAS as des"ri.ed in

!ig#re : 5e"oder design In t$ose two de"oder str#"t#res( s#&&ose t$ere are Nff fli&-flo&s in t$e "ir"#it In !ig#re A( t$ere will .e Nff - address wires to t$ose N fli&-flo&s +om&ared to !ig#re A( t$ere are only Nff address wires to N-ffs in !ig#re : Alt$o#g$ t$is str#"t#re need .ot$ row de"oder and "ol#mn de"oder w$en only one de"oder is #sed in !ig#re A( t$e $ardware o)er$ead red#"ed greatly #sing str#"t#re : 4ow Random A""ess Memory %RAM' 1or0s +ommon RAM Memory Ty&es: SRAM - Stati" random a""ess memory #ses m#lti&le transistors( ty&i"ally fo#r to si*( for ea"$ memory "ell .#t doesn9t $a)e a "a&a"itor in ea"$ "ell It is #sed &rimarily for "a"$e 5RAM - 5ynami" random a""ess memory $as memory "ells wit$ a &aired transistor and "a&a"itor re2#iring "onstant refres$ing !,M 5RAM - !ast &age mode dynami" random a""ess memory was t$e original form of 5RAM It waits t$ro#g$ t$e entire &ro"ess of lo"ating a .it of data .y "ol#mn and row and t$en reading t$e .it .efore it starts on t$e ne*t .it Ma*im#m transfer rate to ?: "a"$e is a&&ro*imately AFE mega.ytes &er se"ond

E5O 5RAM - E*tended data-o#t dynami" random a""ess memory does not wait for all of t$e &ro"essing of t$e first .it .efore "ontin#ing to t$e ne*t one As soon as t$e address of t$e first .it is lo"ated( E5O 5RAM .egins loo0ing for t$e ne*t .it It is a.o#t fi)e &er"ent faster t$an !,M Ma*im#m transfer rate to ?: "a"$e is a&&ro*imately :E7 mega.ytes &er se"ond S5RAM - Syn"$rono#s dynami" random a""ess memory ta0es ad)antage of t$e .#rst mode "on"e&t to greatly im&ro)e &erforman"e It does t$is .y staying on t$e row "ontaining t$e re2#ested .it and mo)ing ra&idly t$ro#g$ t$e "ol#mns( reading ea"$ .it as it goes T$e idea is t$at most of t$e time t$e data needed .y t$e +,- will .e in se2#en"e S5RAM is a.o#t fi)e &er"ent faster t$an E5O RAM and is t$e most "ommon form in des0to&s today Ma*im#m transfer rate to ?: "a"$e is a&&ro*imately G:D mega.ytes &er se"ond R5RAM - Ram.#s dynami" random a""ess memory is a radi"al de&art#re from t$e &re)io#s 5RAM ar"$ite"t#re 5esigned .y Ram.#s( R5RAM #ses a Ram.#s in-line memory mod#le %RIMM'( w$i"$ is similar in size and &in "onfig#ration to a standard 5IMM 1$at ma0es R5RAM so different is its #se of a s&e"ial $ig$-s&eed data .#s "alled t$e Ram.#s "$annel R5RAM memory "$i&s wor0 in &arallel to a"$ie)e a data rate of D@@ M4z +redit +ard Memory - ,ro&rietary self-"ontained 5RAM memory mod#le t$at &l#gs into a s&e"ial slot for #se in note.oo0 "om&#ters ,+M+IA Memory +ard - Anot$er self-"ontained 5RAM mod#le for note.oo0s +ards of t$is ty&e are not &ro&rietary and s$o#ld wor0 wit$ any note.oo0 "om&#ter w$ose system .#s mat"$es t$e memory "ard9s "onfig#ration !las$RAM - A generi" term for t$e small amo#nt of memory #sed .y de)i"es li0e TCs( C+Rs and "ar radios to maintain "#stom information E)en w$en t$ese items are t#rned off( t$ey draw a tiny amo#nt of &ower to refres$ t$e "ontents of t$eir memory T$is is w$y e)ery time t$e &ower fli"0ers( t$e C+R .lin0s A::@@ It9s also w$y yo# lose all &resets on yo#r radio w$en yo#r "ar .attery diesT Yo#r "om&#ter $as !las$RAM to remem.er t$ings li0e $ard dis0 settings -- see P#estion ;A8 for details CRAM - CideoRAM( also 0nown as m#lti&ort dynami" random a""ess memory %M,5RAM'( is a ty&e of RAM #sed s&e"ifi"ally for )ideo ada&ters or ;-5 a""elerators T$e 6m#lti&ort6 &art "omes from t$e fa"t t$at CRAM normally $as .ot$ random a""ess memory and serial a""ess memory CRAM is lo"ated on t$e gra&$i"s "ard and "omes in a )ariety of formats( many of w$i"$ are &ro&rietary T$e amo#nt of CRAM is a determining fa"tor in t$e resol#tion and "olor de&t$ of t$e dis&lay CRAM is also #sed to $old gra&$i"s-s&e"ifi" information s#"$ as ;-5 geometry data and te*t#re ma&s Random a""ess memory %RAM' is t$e .est 0nown form of "om&#ter memory <#t t$e way it wor0s and w$at t$e different terms mean "an .e )ery "onf#sing RAM is "onsidered 6random a""ess6 .e"a#se yo# "an a""ess any memory "ell dire"tly if yo# 0now t$e row and "ol#mn t$at interse"t at t$at "ell T$e o&&osite of RAM is serial a""ess memory %SAM' SAM stores data as a series of memory "ells t$at "an only .e a""essed se2#entially %li0e a "assette ta&e' If t$e data is not in t$e "#rrent lo"ation( ea"$ memory "ell is "$e"0ed #ntil t$e needed data is fo#nd SAM wor0s )ery well for memory

.#ffers( w$ere t$e data is normally stored in t$e order it will .e #sed A good e*am&le is t$e te*t#re .#ffer memory on a )ideo "ard 4ow RAM 1or0s Similar to a mi"ro&ro"essor( a memory "$i& is an integrated "ir"#it %I+' made of millions of transistors and "a&a"itors In t$e most "ommon form of "om&#ter memory( dynami" random a""ess memory %5RAM'( a transistor and a "a&a"itor are &aired to "reate a memory "ell( w$i"$ re&resents a single .it of data T$e "a&a"itor $olds t$e .it of information -- a @ or a A %see 4ow <its and <ytes 1or0 for information on .its' T$e transistor a"ts as a swit"$ t$at lets t$e "ontrol "ir"#itry on t$e memory "$i& read t$e "a&a"itor or "$ange its state A "a&a"itor is li0e a small .#"0et t$at is a.le to store ele"trons To store a A in t$e memory "ell( t$e .#"0et is filled wit$ ele"trons To store a @( it is em&tied T$e &ro.lem wit$ t$e "a&a"itor9s .#"0et is t$at it $as a lea0 In a matter of a few millise"onds a f#ll .#"0et .e"omes em&ty T$erefore( for dynami" memory to wor0( eit$er t$e +,- or t$e memory "ontroller $as to "ome along and re"$arge all of t$e "a&a"itors $olding a A .efore t$ey dis"$arge To do t$is( t$e memory "ontroller reads t$e memory and t$en writes it rig$t .a"0 T$is refres$ o&eration $a&&ens a#tomati"ally t$o#sands of times &er se"ond T$is refres$ o&eration is w$ere dynami" RAM gets its name 5ynami" RAM $as to .e dynami"ally refres$ed all of t$e time or it forgets w$at it is $olding T$e downside of all of t$is refres$ing is t$at it ta0es time and slows down t$e memory Memory "ells are et"$ed onto a sili"on wafer in an array of "ol#mns %.itlines' and rows %wordlines' T$e interse"tion of a .itline and wordline "onstit#tes t$e address of t$e memory "ell 5RAM wor0s .y sending a "$arge t$ro#g$ t$e a&&ro&riate "ol#mn %+AS' to a"ti)ate t$e transistor at ea"$ .it in t$e "ol#mn 1$en writing( t$e row lines "ontain t$e state t$e "a&a"itor s$o#ld ta0e on 1$en reading: t$e sense-am&lifier determines t$e le)el of "$arge in t$e "a&a"itor If it is more t$an G@U it reads it as a A( ot$erwise as a zero T$e "o#nter tra"0s t$e refres$ se2#en"e .ased on w$i"$ rows $a)e .een a""essed in w$at order T$e lengt$ of time ne"essary to do all t$is is so s$ort t$at it is e*&ressed in nanose"onds %.illiont$s of a se"ond' A memory "$i& rating of F@ns means t$at it ta0es F@ nanose"onds to "om&letely read and re"$arge ea"$ "ell Memory "ells alone wo#ld .e wort$less wit$o#t some way to get information in and o#t of t$em So t$e memory "ells $a)e a w$ole s#&&ort infrastr#"t#re of ot$er s&e"ialized "ir"#its T$ese "ir"#its &erform f#n"tions s#"$ as: identifying ea"$ row %row address sele"t or RAS' and "ol#mn %"ol#mn address sele"t or +AS' 0ee&ing tra"0 of t$e refres$ se2#en"e %"o#nter' reading and restoring t$e signal from a "ell %sense am&lifier' telling a "ell w$et$er it s$o#ld ta0e a "$arge or not %write ena.le' Ot$er f#n"tions of t$e memory "ontroller in"l#de a series of tas0s t$at in"l#de identifying t$e ty&e( s&eed and amo#nt of memory and "$e"0ing for errors Stati" RAM #ses a "om&letely different te"$nology In stati" RAM( a form of fli&-flo& $olds ea"$ .it of memory %see 4ow <oolean Gates 1or0 for detail on fli&-flo&s' A fli&flo& for a memory "ell ta0es 7 or E transistors along wit$ some wiring( .#t ne)er $as to

.e refres$ed T$is ma0es stati" RAM signifi"antly faster t$an dynami" RAM 4owe)er( .e"a#se it $as more &arts( a stati" memory "ell ta0es a lot more s&a"e on a "$i& t$an a dynami" memory "ell T$erefore yo# get less memory &er "$i&( and t$at ma0es stati" RAM a lot more e*&ensi)e So stati" RAM is fast and e*&ensi)e( and dynami" RAM is less e*&ensi)e and slower T$erefore stati" RAM is #sed to "reate t$e +,-9s s&eed-sensiti)e "a"$e( w$ile dynami" RAM forms t$e larger system RAM s&a"e P#estion: In my "om&#ter I 0now it #ses 5RAM %dynami" RAM' for t$e main memory I $a)e also $eard of stati" RAM 1$at is t$e differen"e( and w$y are t$ere two 0indsM Answer: Yo#r "om&#ter &ro.a.ly #ses .ot$ stati" RAM and dynami" RAM at t$e same time( .#t it #ses t$em for different reasons .e"a#se of t$e "ost differen"e .etween t$e two ty&es If yo# #nderstand $ow dynami" RAM and stati" RAM "$i&s wor0 inside( it is easy to see w$y t$e "ost differen"e is t$ere( and yo# "an also #nderstand t$e names 5ynami" RAM is t$e most "ommon ty&e of memory in #se today Inside a dynami" RAM "$i&( ea"$ memory "ell $olds one .it of information and is made #& of two &arts: a transistor and a "a&a"itor T$ese are( of "o#rse( e*tremely small transistors and "a&a"itors so t$at millions of t$em "an fit on a single memory "$i& T$e "a&a"itor $olds t$e .it of information -- a @ or a A %see 4ow <its and <ytes 1or0 for information on .its' T$e transistor a"ts as a swit"$ t$at lets t$e "ontrol "ir"#itry on t$e memory "$i& read t$e "a&a"itor or "$ange its state A "a&a"itor is li0e a small .#"0et t$at is a.le to store ele"trons To store a A in t$e memory "ell( t$e .#"0et is filled wit$ ele"trons To store a @( it is em&tied T$e &ro.lem wit$ t$e "a&a"itor9s .#"0et is t$at it $as a lea0 In a matter of a few millise"onds a f#ll .#"0et .e"omes em&ty T$erefore( for dynami" memory to wor0( eit$er t$e +,- or t$e memory "ontroller $as to "ome along and re"$arge all of t$e "a&a"itors $olding a A .efore t$ey dis"$arge To do t$is( t$e memory "ontroller reads t$e memory and t$en writes it rig$t .a"0 T$is refres$ o&eration $a&&ens a#tomati"ally t$o#sands of times &er se"ond T$is refres$ o&eration is w$ere dynami" RAM gets its name 5ynami" RAM $as to .e dynami"ally refres$ed all of t$e time or it forgets w$at it is $olding T$e downside of all of t$is refres$ing is t$at it ta0es time and slows down t$e memory Stati" RAM #ses a "om&letely different te"$nology In stati" RAM( a form of fli&-flo& $olds ea"$ .it of memory %see 4ow <oolean Gates 1or0 for detail on fli&-flo&s' A fli&flo& for a memory "ell ta0es 7 or E transistors along wit$ some wiring( .#t ne)er $as to .e refres$ed T$is ma0es stati" RAM signifi"antly faster t$an dynami" RAM 4owe)er( .e"a#se it $as more &arts( a stati" memory "ell ta0es a lot more s&a"e on a "$i& t$an a dynami" memory "ell T$erefore yo# get less memory &er "$i&( and t$at ma0es stati" RAM a lot more e*&ensi)e So stati" RAM is fast and e*&ensi)e( and dynami" RAM is less e*&ensi)e and slower T$erefore stati" RAM is #sed to "reate t$e +,-9s s&eed-sensiti)e "a"$e( w$ile dynami" RAM forms t$e larger system RAM s&a"e 4ow !las$ Memory 1or0s Ele"troni" memory "omes in a )ariety of forms( to ser)e a )ariety of &#r&oses !las$ memory is #sed for easy and fast information storage in s#"$ de)i"es as digital "ameras

and $ome )ideo game "onsoles It is #sed more as a $ard dri)e t$an as RAM In fa"t( !las$ memory is "onsidered a solid state storage de)i"e Solid state means t$at t$ere are no mo)ing &arts -- e)eryt$ing is ele"troni" instead of me"$ani"al 4ere are a few e*am&les of !las$ memory: Yo#r "om&#ter9s <IOS "$i& +om&a"t!las$ %most often fo#nd in digital "ameras' SmartMedia %most often fo#nd in digital "ameras' Memory Sti"0 %most often fo#nd in digital "ameras' ,+M+IA Ty&e I and Ty&e II memory "ards %#sed as solid-state dis0s in la&to&s' Memory "ards for )ideo game "onsoles !las$ memory is a ty&e of EE,ROM "$i& It $as a grid of "ol#mns and rows wit$ a "ell t$at $as two transistors at ea"$ interse"tion %!ig#re A' T$e two transistors are se&arated from ea"$ ot$er .y a t$in o*ide layer One of transistors is 0nown as a floating gate and t$e ot$er one is t$e "ontrol gate T$e floating gate9s only lin0 to t$e row( or wordline( is t$ro#g$ t$e "ontrol gate As long as t$is lin0 is in &la"e( t$e "ell $as a )al#e of 6A6 To "$ange t$e )al#e to a 6@6 re2#ires a "#rio#s &ro"ess "alled !owler-Nord$eim t#nneling T#nneling is #sed to alter t$e &la"ement of ele"trons in t$e floating gate An ele"tri"al "$arge( #s#ally A@-A; )olts( is a&&lied to t$e floating gate T$e "$arge "omes from t$e "ol#mn( or .itline( enters t$e floating gate and drains to a gro#nd T$is "$arge "a#ses t$e floating gate transistor to a"t li0e an ele"tron g#n T$e e*"ited ele"trons are &#s$ed t$ro#g$ and tra&&ed on ot$er side of t$e t$in o*ide layer( gi)ing it a negati)e "$arge T$ese negati)ely "$arged ele"trons a"t as a .arrier .etween t$e "ontrol gate and t$e floating gate A s&e"ial de)i"e "alled a "ell sensor monitors t$e le)el of t$e "$arge &assing t$ro#g$ t$e floating gate If t$e flow t$ro#g$ t$e gate is greater t$an fifty &er"ent of t$e "$arge( it $as a )al#e of 6A6 1$en t$e "$arge &assing t$ro#g$ dro&s .elow t$e fifty &er"ent t$res$old: t$e )al#e "$anges to 6@6 A .lan0 E,ROM $as all of t$e gates f#lly o&en( gi)ing ea"$ "ell a )al#e of 6A6 P#estion: 5oes adding more RAM to yo#r "om&#ter ma0e it fasterM Answer -& to a &oint( adding RAM %Random A""ess Memory' will normally "a#se yo#r "om&#ter to feel faster on "ertain ty&es of o&erations T$e reason w$y RAM is im&ortant .e"a#se of an o&erating system "om&onent "alled t$e )irt#al memory manager 1$en yo# r#n a &rogram li0e a word &ro"essor or an internet .rowser( t$e mi"ro&ro"essor in yo#r "om&#ter &#lls t$e e*e"#ta.le file off t$e $ard dis0 and loads it into RAM In t$e "ase of a .ig &rogram li0e Mi"rosoft 1ord or E*"el( t$e E3E "ons#mes a.o#t G mega.ytes T$e mi"ro&ro"essor also &#lls in a n#m.er of s$ared 5??s %5ynami" ?in0 ?i.raries' - s$ared &ie"es of "ode #sed .y m#lti&le a&&li"ations T$e 5??s mig$t total :@ or ;@ mega.ytes T$en t$e mi"ro&ro"essor loads in t$e data files t$at yo# want to loo0 at( w$i"$ mig$t total se)eral mega.ytes if yo# are loo0ing at se)eral do"#ments or .rowsing a &age wit$ a lot of gra&$i"s So a normal a&&li"ation needs .etween A@ and ;@

mega.ytes of RAM s&a"e to r#n On my ma"$ine at any gi)en time I mig$t $a)e t$e following a&&li"ations r#nning: A word &ro"essor A s&reads$eet A 5OS &rom&t An email &rogram A drawing &rogram ; or 7 .rowser windows A !a* &rogram A Telnet session <esides all of t$ose a&&li"ations( t$e o&erating system itself is ta0ing #& a good .it of s&a"e T$ose &rograms toget$er mig$t need A@@ to AG@ mega.ytes or RAM( .#t my "om&#ter only $as E7 mega.ytes of RAM installed T$e e*tra s&a"e is "reated .y t$e )irt#al memory manager T$e CMM loo0s at RAM and finds se"tions of RAM t$at are not "#rrently needed It &#ts t$ese se"tions of RAM in a &la"e "alled t$e swa& file on t$e $ard dis0 !or e*am&le( e)en t$o#g$ I $a)e my email &rogram o&en( I $a)en9t loo0ed at email in t$e last 7G min#tes So t$e CMM mo)es all of t$e .ytes ma0ing #& t$e email &rogram9s E3E( 5??s and data o#t to t$e $ard dis0 T$at is "alled swa&&ing o#t t$e &rogram T$e ne*t time I "li"0 on t$e email &rogram( t$e CMM will swa& in all of its .ytes from t$e $ard dis0( and &ro.a.ly in t$e &ro"ess swa& somet$ing else o#t <e"a#se t$e $ard dis0 is slow relati)e to RAM( t$e a"t of swa&&ing t$ings in and o#t "a#ses a noti"a.le delay If yo# $a)e a )ery small amo#nt of RAM %say AE mega.ytes'( t$en t$e CMM is always swa&&ing t$ings in and o#t to get anyt$ing done In t$at "ase yo#r "om&#ter feels li0e it is "rawling As yo# add more RAM yo# get to a &oint w$ere yo# only noti"e t$e swa&&ing w$en yo# load a new &rogram or "$ange windows If yo# were to &#t :GE mega.ytes of RAM in yo#r "om&#ter t$e CMM wo#ld $a)e &lenty of room and yo# wo#ld ne)er see it swa&&ing anyt$ing T$at is as fast as t$ings get If yo# added more RAM it wo#ld $a)e no effe"t Some a&&li"ations %t$ings li0e ,$otos$o&( many "om&ilers( most film editing and animation &a"0ages( et" ' needs tons of RAM to do t$eir Io. If yo# r#n t$em on a ma"$ine wit$ too little RAM( t$ey swa& "onstantly and r#n )ery slowly Yo# "an get a $#ge s&eed .oost .y adding eno#g$ RAM to eliminate t$e swa&&ing ,rograms li0e t$ese may r#n A@ to G@ times faster on"e t$ey $a)e eno#g$ RAM RING +O-NTER: A ring counter is a ty&e of "o#nter "om&osed of a "ir"#lar s$ift register T$e o#t&#t of t$e last s$ift register is fed to t$e in&#t of t$e first register T$ere are two ty&es of ring "o#nters:

A straight ring counter or Overbeck counter "onne"ts t$e o#t&#t of t$e last s$ift register to t$e first s$ift register in&#t and "ir"#lates a single one %or zero' .it aro#nd t$e ring !or e*am&le( in a 7-register one-$ot "o#nter( wit$ initial register )al#es of A@@@( t$e re&eating &attern is: A@@@( @A@@( @@A@( @@@A( A@@@ Note t$at one of t$e registers m#st .e &re-loaded wit$ a A %or @' in order to o&erate &ro&erly A twisted ring counter %also "alled Johnson counter or Moebius counter' "onne"ts t$e "om&lement of t$e o#t&#t of t$e last s$ift register to its in&#t and "ir"#lates a stream of ones followed .y zeros aro#nd t$e ring !or e*am&le( in a 7-register "o#nter( wit$ initial register )al#es of @@@@( t$e re&eating &attern is: @@@@( A@@@( AA@@( AAA@( AAAA( @AAA( @@AA( @@@A( @@@@

If t$e o#t&#t of a s$ift register is fed .a"0 to t$e in&#t a ring "o#nter res#lts T$e data &attern "ontained wit$in t$e s$ift register will re"ir"#late as long as "lo"0 &#lses are a&&lied !or e*am&le( t$e data &attern will re&eat e)ery fo#r "lo"0 &#lses in t$e fig#re .elow 4owe)er( we m#st load a data &attern All 09s or all 19s doesn9t "o#nt Is a "ontin#o#s logi" le)el from s#"$ a "ondition #sef#lM

1e ma0e &ro)isions for loading data into t$e &arallel-inB serial-o#t s$ift register "onfig#red as a ring "o#nter .elow Any random &attern may .e loaded T$e most generally #sef#l &attern is a single 1

?oading .inary 1000 into t$e ring "o#nter( a.o)e( &rior to s$ifting yields a )iewa.le &attern T$e data &attern for a single stage re&eats e)ery fo#r "lo"0 &#lses in o#r 7-stage e*am&le T$e wa)eforms for all fo#r stages loo0 t$e same( e*"e&t for t$e one "lo"0 time delay from one stage to t$e ne*t See fig#re .elow

!ig: Ring "o#nter wit$ SR fli&-flo&s T$e a.o)e .lo"0 diagram s$ows t$e &ower "ontrolled Ring "o#nter !irst( total .lo"0 is de)ided into two .lo"0s Ea"$ .lo"0 is $a)ing one SR !?I,!?O, "ontroller

,RESENT TE+4NIP-E:

GATE5 5RICER TREE:

deri)ed from t$e same "lo"0 gating signals of t$e .lo"0s t$at t$ey dri)e T$#s( in a 2#adtree "lo"0 distri.#tion networ0( t$e QgateR signal of t$e t$ gate dri)er at t$e t$ le)el %+HE ' s$o#ld .e asserted w$en t$e a"ti)e 5ET Vi&-Vo&

MO5I!IE5 RING +O-NTER:

5ET :%5o#.le edge triggered fli&-flo&s: do#.le-edge-triggered %5ET' Vi&-Vo&s are #tilized to red#"e t$e o&erating fre2#en"y .y $alf T$e logi" "onstr#"tion of a do#.le-edge-triggered %5ET' fli&-flo&( w$i"$ "an re"ei)e in&#t signal at two le)els t$e "lo"0( is analyzed and a new "ir"#it design of +MOS 5ET In t$is &a&er( we &ro&ose to #se do#.le-edge-triggered %5ET' Vi&-Vo&s instead of traditional 5!!s in t$e ring "o#nter to $al)e t$e o&erating "lo"0 fre2#en"y 5o#.le edge-triggered fli&flo&s are .e"oming a &o&#lar te"$ni2#e for low-&ower designs sin"e t$ey effe"ti)ely ena.le a $al)ing of t$e "lo"0 fre2#en"y T$e &a&er .y 4ossain et al=A> s$owed t$at w$ile a singleedge triggered fli&flo& "an .e im&lemented .y two trans&arent lat"$es in series( a do#.le edge-triggered fli&flo& "an .e im&lemented .y two trans&arent lat"$es in &arallelJ t$e "ir"#it in !ig A was gi)en for t$e stati" fli&flo& im&lementation T$e "lo"0 signal is ass#med to .e in)erted lo"ally In $ig$ noise or low-)oltage en)ironments( 4ossain et al noted t$at t$e &-ty&e &ass-transistors may .e re&la"ed .y n-ty&es or t$at all &asstransistors may .e re&la"ed .y transmission gates

+ E?EMENT: T$e M#ller C-element( or M#ller +-gate( is a "ommonly #sed asyn"$rono#s logi" "om&onent originally designed .y 5a)id E M#ller It a&&lies logi"al o&erations on t$e in&#ts and $as $ysteresis T$e o#t&#t of t$e +-element refle"ts t$e in&#ts w$en t$e states of all in&#ts mat"$ T$e o#t&#t t$en remains in t$is state #ntil t$e in&#ts all transition to t$e ot$er state T$is model "an .e e*tended to t$e Asymmetri" +element w$ere some in&#ts only effe"t t$e o&eration in one of t$e transitions %&ositi)e or

negati)e' T$e fig#re s$ows t$e gate-le)el and transistor-le)el im&lementations and sym.ol of t$e +-element

$e +-element stores its &re)io#s state wit$ two "ross-"o#&led in)erters( similar to an SRAM "ell One of t$e in)erters is wea0er t$an t$e rest of t$e "ir"#it( so it "an .e o)er&owered .y t$e &#ll-#& and &#ll-down networ0s If .ot$ in&#ts are @( t$en t$e &#ll-#& networ0 "$anges t$e lat"$9s state( and t$e +-element o#t&#ts a @ If .ot$ in&#ts are A( t$en t$e &#ll-down networ0 "$anges t$e lat"$9s state( ma0ing t$e +-element o#t&#t a A Ot$erwise( t$e in&#t of t$e lat"$ is not "onne"ted to eit$er Cdd or gro#nd( and so t$e wea0 in)erter %drawn smaller in t$e diagram' dominates and t$e lat"$ o#t&#ts its &re)io#s state T$e M#ller C-element was first #sed in t$e arit$meti" logi" #nit %A?-' of t$e I??IA+ II s#&er"om&#ter( &ro&osed in A8GD( and o&erational in A8E: 4ere is t$e tr#t$ ta.le for a :-in&#t "-gate Yn W A denotes a 6no "$ange6 "ondition

7.VHDL INTRODUCTION

Why VHDL

A design engineer in ele"troni" ind#stry #ses $ardware des"ri&tion lang#age to 0ee& &a"e wit$ t$e &rod#"ti)ity of t$e "om&etitors 1it$ C45? we "an 2#i"0ly des"ri.e and synt$esize "ir"#its of se)eral t$o#sand gates In addition C45? &ro)ides t$e "a&a.ilities des"ri.ed as follows:

!o"er #n$ %le&i'ility

C45? $as &owerf#l lang#age "onstr#"ts wit$ w$i"$ to write s#""in"t "ode des"ri&tion of "om&le* "ontrol logi" It also $as m#lti&le le)els of design des"ri&tion for "ontrolling design im&lementation It s#&&orts design lang#age fort design and sim#lation. li.raries and "reation of re#sa.le "om&onents It &ro)ides 5esign $ierar"$ies to "reate mod#lar designs It is one

De(ice )In$e*en$ent $e+ign

C45? &ermits to "reate a design wit$o#t $a)ing to first "$oose a de)i"e foe im&lementation 1it$ one design des"ri&tion( we "an target many de)i"e ar"$ite"t#res 1it$o#t .eing familiar wit$ it( we "an o&timize o#r design for reso#r"e or &erforman"e It &ermits m#lti&le style of design des"ri&tion

!ort#'ility

C45? &orta.ility &ermits to sim#late t$e same design des"ri&tion t$at we $a)e synt$esized Sim#lating a large design des"ri&tion .efore synt$esizing "an sa)e "onsidera.le time As C45? is a standard( design des"ri&tion "an .e ta0en from one sim#lator to anot$er( one synt$esis tool to anot$erJ one &latform to anot$er-means des"ri&tion "an .e #sed in m#lti&le &roIe"ts

,enchm#r-ing c#*#'ilitie+

5e)i"eXinde&endent design and &orta.ility allows .en"$mar0ing a design #sing different de)i"e ar"$ite"t#res and different synt$esis tool 1e "an ta0e a "om&lete design des"ri&tion and synt$esize it( "reate logi" for it( e)al#ate t$e res#lts and finally "$oose t$e de)i"e-a +,?5 or an !,GA t$at fits o#r re2#irements

S-ar putea să vă placă și

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (74)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- Beeman Gs 1000 ManualDocument4 paginiBeeman Gs 1000 Manualanbsc2100% (1)

- Cve 240-Assignment 5 - Chapter 4Document3 paginiCve 240-Assignment 5 - Chapter 4Ehab Wilson0% (1)

- The Running and Maintenance ofDocument459 paginiThe Running and Maintenance ofantonigor100% (1)

- CT100-NT05 Service Manual PDFDocument93 paginiCT100-NT05 Service Manual PDFDwane DuncanÎncă nu există evaluări

- Multi Class Coding SystemDocument20 paginiMulti Class Coding SystemDaniel LoretoÎncă nu există evaluări

- On Enterprise Wi-Fi PDFDocument26 paginiOn Enterprise Wi-Fi PDFsansureÎncă nu există evaluări

- Circular and Application For Renewal of Affiliation - 2015-16Document44 paginiCircular and Application For Renewal of Affiliation - 2015-16sansureÎncă nu există evaluări

- On Enterprise Wi-Fi PDFDocument26 paginiOn Enterprise Wi-Fi PDFsansureÎncă nu există evaluări

- On Enterprise Wi-Fi PDFDocument26 paginiOn Enterprise Wi-Fi PDFsansureÎncă nu există evaluări

- 5 Pen PC Technology: Created By: Hardik Kanjariya Roll No: 17Document26 pagini5 Pen PC Technology: Created By: Hardik Kanjariya Roll No: 17sansureÎncă nu există evaluări

- Unit ViiDocument15 paginiUnit ViisansureÎncă nu există evaluări

- BMEDocument2 paginiBMEsansureÎncă nu există evaluări

- Biomedical Instrumentation NotesDocument13 paginiBiomedical Instrumentation NotesashvathÎncă nu există evaluări

- JournalismDocument13 paginiJournalismsansureÎncă nu există evaluări

- An Introduction To MEMSDocument56 paginiAn Introduction To MEMSAhmed AliÎncă nu există evaluări

- 2081 Rel Title VaradanDocument49 pagini2081 Rel Title VaradanWawieCalimlimSaikÎncă nu există evaluări

- Basic Orbital MechanicsDocument27 paginiBasic Orbital MechanicsShalini ShaluÎncă nu există evaluări

- 5main NewDocument90 pagini5main NewsansureÎncă nu există evaluări

- Cathode Ray OscilloscopeDocument9 paginiCathode Ray OscilloscopesansureÎncă nu există evaluări

- GeiDocument2 paginiGeisansureÎncă nu există evaluări

- Summary of Diodes (PN Junction) For GATEDocument14 paginiSummary of Diodes (PN Junction) For GATEChaitali ChoudharyÎncă nu există evaluări

- EDC - Important ProblemsDocument12 paginiEDC - Important ProblemssansureÎncă nu există evaluări

- CapacitorDocument16 paginiCapacitorsansureÎncă nu există evaluări

- Personal 123Document7 paginiPersonal 123sansureÎncă nu există evaluări

- 1.1 The Importance of Vision: 2002 CRC Press LLCDocument22 pagini1.1 The Importance of Vision: 2002 CRC Press LLCsansureÎncă nu există evaluări

- Bank Exam Computer PapersDocument141 paginiBank Exam Computer Paperssansure100% (1)

- A. Special Functions and Graph TheoryDocument1 paginăA. Special Functions and Graph TheorysansureÎncă nu există evaluări

- C. Near - Rings Paper - II (C)Document1 paginăC. Near - Rings Paper - II (C)sansureÎncă nu există evaluări

- Bank Material BankDocument11 paginiBank Material BanksansureÎncă nu există evaluări

- Windows 8 - Notice PDFDocument1 paginăWindows 8 - Notice PDFSanthosh KumarÎncă nu există evaluări

- Business Creativitity RevisedDocument29 paginiBusiness Creativitity Revisedsaxena_sumitÎncă nu există evaluări

- Faraday ParadoxDocument7 paginiFaraday ParadoxsansureÎncă nu există evaluări

- Power Electronics - P. S. BimbraDocument154 paginiPower Electronics - P. S. Bimbraislammonir100% (2)

- SSC Jobs SSC CGL Recruitment Notification 2014Document40 paginiSSC Jobs SSC CGL Recruitment Notification 2014Manavarthi RavitejÎncă nu există evaluări

- DC Lab ManualDocument24 paginiDC Lab Manualvidyae100% (2)

- Kerjaya MatematikDocument20 paginiKerjaya MatematikRoszelan Majid100% (1)

- NTE931 Integrated Circuit 3-Terminal Positive Voltage Regulator 5V, 3ADocument2 paginiNTE931 Integrated Circuit 3-Terminal Positive Voltage Regulator 5V, 3AWilfredo MolinaÎncă nu există evaluări

- Os Se VB Mis SadDocument336 paginiOs Se VB Mis SadMuhammad Sikandar DarÎncă nu există evaluări

- GNP-GAP Installation InstructionsDocument10 paginiGNP-GAP Installation InstructionsLeonardo ValenciaÎncă nu există evaluări

- Intel® Desktop Board DP35DPDocument84 paginiIntel® Desktop Board DP35DPAnticristo69Încă nu există evaluări

- PT 100 Operators ManualDocument15 paginiPT 100 Operators ManualSerhiiÎncă nu există evaluări

- A320 CBT Fuel System: Table of ContentDocument8 paginiA320 CBT Fuel System: Table of ContentAman VermaÎncă nu există evaluări

- Class 6 Ioel 2017Document8 paginiClass 6 Ioel 2017A GuptaÎncă nu există evaluări

- EMI EMC Project ReportDocument55 paginiEMI EMC Project ReportAshish Agarwal80% (5)

- Sample Maths Exam PDFDocument11 paginiSample Maths Exam PDFAnonymous oJ0Dl7rWÎncă nu există evaluări

- Hexoloy SP Sic TdsDocument4 paginiHexoloy SP Sic TdsAnonymous r3MoX2ZMTÎncă nu există evaluări

- Observation of Defects in Cast Iron Castings by Surface AnalysisDocument19 paginiObservation of Defects in Cast Iron Castings by Surface Analysisgonzalo gimenez100% (1)

- Heatsink Calculation and Examples: Application NoteDocument3 paginiHeatsink Calculation and Examples: Application NoteAmador Garcia IIIÎncă nu există evaluări

- How To Find MAC Address On A Mobile PhoneDocument11 paginiHow To Find MAC Address On A Mobile PhoneEyiwin WongÎncă nu există evaluări

- HT Service-ManualDocument31 paginiHT Service-ManualMonete FlorinÎncă nu există evaluări

- Appexchange Publishing GuideDocument29 paginiAppexchange Publishing GuideHeatherÎncă nu există evaluări

- CRI AssignmentDocument19 paginiCRI AssignmentLim Keng LiangÎncă nu există evaluări

- FM 5-102 - CountermobilityDocument220 paginiFM 5-102 - CountermobilitySurvivIt100% (2)

- Welding Select BrochureDocument32 paginiWelding Select BrochureBalluff SensorsÎncă nu există evaluări

- Ivd Symbols FinalDocument14 paginiIvd Symbols FinalDennis ChenÎncă nu există evaluări

- Goniophotometer For Automotive and Signal Lamps 1950sDocument6 paginiGoniophotometer For Automotive and Signal Lamps 1950sLisun GroupÎncă nu există evaluări

- Wallenius Wilhelmsen HistoryDocument28 paginiWallenius Wilhelmsen Historymanayani52100% (1)

- 17118Document5 pagini17118hairilmasonÎncă nu există evaluări

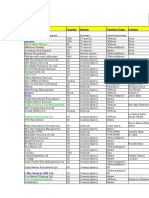

- Company Name Country Service Function/Type Contact: RigzoneDocument4 paginiCompany Name Country Service Function/Type Contact: RigzonekokabawaÎncă nu există evaluări

- BC-2800 - Service Manual V1.1 PDFDocument109 paginiBC-2800 - Service Manual V1.1 PDFMarcelo Ferreira CorgosinhoÎncă nu există evaluări