Documente Academic

Documente Profesional

Documente Cultură

802 3ab

Încărcat de

cdrbcTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

802 3ab

Încărcat de

cdrbcDrepturi de autor:

Formate disponibile

802.

3ab

A Tutorial

Presentation

802.3ab

1000BASE-T Tutorial Structure

Introduction, Market & History

Colin Mick, The Mick Group

Cabling

Chris DiMinico, Cabletron

Channel and Overall Architecture

Sreen Raghavan, ComCore Semiconductor

Technical Details

Sailesh Rao, Level One Communications

Detailed VLSI Implementation

Mehdi Hatamian, Broadcom Corporation

802.3ab

One New Design Task for 1000BASE-T

5 Level Signaling costs 6dB in SNR

Get back with Forward Error Correction (FEC)

Everything else has been done in:

100Base-TX

125Msps

DSP works

100Base-T4

Transmit/Receive on 4 channels

100Base-T2

ECHO and NEXT canceling

802.3ab

Where Does 802.3ab Fit?

Media Access Control (MAC)

Full Duplex / Half Duplex

1000BASE-T

Encoder / Decoder

1000BASE-X 8b/10b

Encoder / Decoder

1000BASE-SX

Transceiver

1000BASE-CX

Transceiver

1000BASE-T

Transceiver

Gigabit Media Independent Interface (GMII)

MAC

PHY

Fiber Channel Based Technology

1000BASE-LX

Transceiver

|802.3z| |802.3ab|

802.3ab

Target Market

70% of installed UTP is CAT 5

CAT 5 installed footage is growing 30% annually

0

10

20

30

40

50

60

70

80

90

100

1991 1992 1993 1994 1995 1996 1997

Voice

Fiber Optic

Coaxial

STP

UTP

802.3ab

Market Applications

Server Farms

High performance work groups

Graphic-based applications

Network computers

Shared gigabit networks

802.3ab

Objectives

Comply with specifications for GMII of 802.3z.

Provide line transmission which supports full and half duplex

operation.

Provide FCC Class A/CISPR or better operation

Support operation over 100 meters of Category 5 balanced

cabling

Achieve bit Error Rate better than to 10

-10

Support Auto-Negotiation (Clause 28)

Meet susceptibility requirements

Support the objectives of 802.3z of Nov. 13, 1996

802.3ab

Foundations

100BASE-TX demonstrates sending a 3-level symbol stream

over Category 5 cable at 125 Mbaud is possible and practical.

100BASE-TX DSP Based Phys now available

100BASE-T4 demonstrates techniques for sending multi-level

coded symbols over four pairs.

100BASE-T2 demonstrates the use of digital signal processing

(DSP), five-level coding, and simultaneous two-way data

streams while dealing with alien signals in adjacent pairs

802.3ab

Timeline

Milestone 802.3z 802.3ab

Work starts November 95 November 95

PAR received March 96 March 97

1

st

draft January 97 November 97

WG ballot July 97 March 98*

LMSC ballot November 97 July 98*

Ready for std June 98* December 98*

802.3ab

Status

Now reviewing D2-0

Task force doing final tuning on D2-0 during this Plenary.

On-track to request permission to go to working group

ballot at this Plenary

802.3ab

Cabling

Topology

Cabling Specifications

Cabling standards

802.3ab

Channel Cabling Topology

building Cable cross-connection

equipment

cable

work area

cable

connecting hardware

transition point

telecommunications

outlet/connector

equipment

TIA/EIA - 568-A Channel (w/o transition Point) = ISO 11801 Channel

Cross-Connect Topology

802.3ab

Installed Cabling

Minimizes connections

Minimizes crosstalk, both near-end and far-end

Minimizes return loss and insertion loss

building Cable

interconnection

equipment

cable

work area

cable

connecting hardware

telecommunications

outlet/connector

equipment

Recommended Interconnect Topology

802.3ab

Cabling Performance Specifications

Based on Category 5 Installed Cabling

Project Authorization Request (PAR) for the 1000BASE-T project specifically

requires operation on four pair 100 ohm Category 5 balanced copper cabling as

defined by TIA/EIA-568-A, or its equivalent as built from material specified by

ISO/IEC 11801: 1995 that meets the channel performance parameters specified

in TIA/EIA-568-A ANNEX E.

Additional cabling specifications: Draft Addendum to ANSI/TIA/EIA-568-A:

Additional specifications for FEXT (ELFEXT) and return loss, not currently

specified by TIA/EIA-568-A, are being developed developed to characterize

the vast majority of the installed base of Category 5 cabling built to TIA/EIA-

568-A and/or ISO/IEC 11801clauses 6, 8 & 9.

An addendum to ANSI/TIA/EIA-568-A will include the additional transmission

performance specifications and field test parameters for FEXT (ELFEXT) and

return loss.

802.3ab

Field Testing

A verification of the installed cabling performance per

the field test specification of ANSI/TIA/EIA-TSB-67-

"Transmission Performance Specifications for Field

Testing of Twisted Pair Cabling System" with the

additional test parameters for FEXT (ELFEXT) and

return loss (to be released as an addendum to TIA/EIA-

568-A) will be recommended.

802.3ab

Cabling Specifications

Frequency(MHz) Return Loss(dB)

1<=f<20 15

20<=f<100 15 - 10*LOG(f/20)

40.8.2.1 Insertion Loss

.4/f f * 2.1 loss(f) Insertion_

0.529

+ <

40.8.2.3 Return Loss

802.3ab

Channel Return Loss

C h a n n e l C o n f i g u r a t i o n R e t u r n L o ss

- 7 0

- 6 0

- 5 0

- 4 0

- 3 0

- 2 0

- 1 0

0

0 2 0 4 0 6 0 8 0 1 0 0

M H z

d

B

ma n u f 1 - Or a n g e p a ir 2 0 m

ma n u f 1 - B r o w n p a ir 2 0 m

ma n u f 1 - B r o w n p a ir 5 0 m

ma n u f 1 - B r o w n p a ir 9 0 m

1 5 - 1 0 *L OG( f / 2 0 )

1 7 - 1 0 *L OG( f / 2 0 )

ma n u f 2 - 2 0 m

802.3ab

Channel Insertion Loss

Insertion Loss Model - Category 5 100 Meter Measured Link,

Measured Link Scaled & EIA-568-A Annex E Insertion Loss Limit

0

2

4

6

8

10

12

14

16

18

20

22

24

26

147

1

0

1

3

1

6

1

9

2

2

2

5

2

8

3

1

3

4

3

7

4

0

4

3

4

6

4

9

5

2

5

5

5

8

6

1

6

4

6

7

7

0

7

3

7

6

7

9

8

2

8

5

8

8

9

1

9

4

9

7

1

0

0

Frequency (MHz)

I

n

s

e

r

t

i

o

n

L

o

s

s

(

d

B

)

Measured Link

Measured Link Scaled

EIA-568-A Annex E Limit

802.3ab

Coupling Parameters (Crosstalk)

40.8.3.1 Differential Near-End Crosstalk (NEXT) Loss

The NEXT loss between all duplex channels of a link segment shall be

greater than 27.1 - 16.8Log10 (f/100).

40.8.3.2 Equal Level Far-End Crosstalk (ELFEXT) Loss

The worst pair ELFEXT loss between a duplex channel shall be greater

than 17 - 20Log 10 (f/100) dB

40.8.3.2.1 Multiple Disturber Far-end Crosstalk (ELFEXT) Loss

1. 17.0 - 20Log 10 (f/100) dB.

2. 19.5 - 20Log 10 (f/100) dB.

3. 23.0 - 20Log 10 (f/100) dB.

PSELFEXT loss is 14.4-20*log(f/100)

802.3ab

Channel Next

Channel NEXT

-140

-120

-100

-80

-60

-40

-20

0

0 20 40 60 80 100

MHz

d

B

NEXT Model 2 (Lucent)

NEXT Model 3 (Lucent)

NEXT Model 4 (Lucent)

TIA/EIA-Channel Limit

802.3ab

Channel and Overall Architecture

Design Tasks

Design Approach

Receiver Startup

802.3ab

Gigabit Over CAT-5 Copper Cable

Topology -- Link segment of a 4-Pair Cat-5 Cable. Each pair a full

duplex channel supporting effective data rate of 250Mbp/s in both

directions simultaneously

ECHO, SELF NEXT and FEXT

Hybrid to cancel most of the NEAR END ECHO

Adaptive cancellers to reduce remaining ECHO and SELF NEXT

Signal to Noise Ratio (SNR) 6dB Less Than 100Base-TX due to

5-level signaling

Provide 6dB coding gain in the form of a 4-D Trellis code

Channel Impairments

20dB signal attenuation at 62MHz at 100 meters

Incorporate decision feedback channel equalization

External Noise

FCC imposed limits on transmit levels

Limit transmit spectrum above 30MHz

Partial Response spectral shaping at the transmitter (3/4 + 1/4Z

-1

)

802.3ab

Major Receiver Design Tasks

A/D conversion

125 Mega samples per second Conversion

Frequency Locking and Timing Recovery

Low Jitter Phase Locked Loop for clock recovery

FEC 4D-8 State Trellis Code

Design of critical timing path involving Trellis

decoder and decision feeback equalizer

802.3ab

<--------Insertion Loss

NEXT_41

FEXT_31

FEXT_21

FEXT_41

NEXT_31

NEXT_21

250Mb/S

250Mb/S

250Mb/S

250Mb/S

250Mb/S

250Mb/S

250Mb/S

250Mb/S

T

T

T

T

R

R

R

R

H

Y

B

R

I

D

H

Y

B

R

I

D

H

Y

B

R

I

D

H

Y

B

R

I

D

T

T

T

T

R

R

R

R

H

Y

B

R

I

D

H

Y

B

R

I

D

H

Y

B

R

I

D

H

Y

B

R

I

D

Near ECHO

Far Echo

Gigabit Ethernet over CAT-5 Cable

(using 4 wire pairs)

802.3ab

MLT-3 and PAM-5 Signal Levels

Recover the 6dB of SNR -- Add Forward Error Correction (FEC)

Time (in ns)

Eye pattern of PAM-5 signaling

Time (in ns)

Eye pattern of MLT-3 signaling

1 volt

.5 volt

802.3ab

Transmitter

GMII PCS

DAC

DAC

DAC

DAC

Tx1

Tx2

Tx3

Tx4

125 MBaud

5-PAM

1

4 / 1 4 / 3

+ z

1

4 / 1 4 / 3

+ z

1

4 / 1 4 / 3

+ z

1

4 / 1 4 / 3

+ z

Similar to 100Base-TX New DSP for

Gigabit

New Analog

for Gigabit

802.3ab

DSP Based Receiver Block Diagram

Hybrid

Analog

Front End

incl. A/D

Converter

DSP Based Receiver FEC

CAT-5

Cable

Transmitted Data This Channel

To Echo

Canceller

Clock

Recovery

Recovered

and

Corrected

Data

Transmitted Data --

Other Channels

To NEXT

Cancellers

Added FEC

for

Gigabit

802.3ab

Typical 100TX DSP Based Receiver

Feed Forward

Equalization

Slicer

(comparators)

Output

Data

Remove

Precursor

ISI

Reconstruction of

Transmitted Data

+

DFE

A

/

D Analog

Input

Recovere

d

Clock

Ideal sliced

data Error

Adjusts

Coefficients

Error

Adjusts

Coefficients

Error is the difference

between Ideal Sliced Data and

Reconstruction of

Transmitted Data

Remove Post-

Cursor ISI

Analog

Front

End

(AFE)

802.3ab

Detail of DFE Based Equalizer

{ X

k

}

T T T

X

+

m

k

T T T

{Z

k

} +

X X X

+

c

0ff

c

1ff

c

nff

-

b

0fb

b

1fb

b

nfb

{ D

k

}

X X

+

Feed Forward Equalizer

Feedback Equalizer

FBE

Slicer

The error signal used to set

the coefficients (c

0ff

- c

nff

and

b

0fb

- b

nfb

) is the difference

between m

k

(the actual input

to the slicer) and x

k

(the

output of the slicer -- the

ideal signal level)

+

+ -

802.3ab

Gigabit Receiver With FEC

NEXT

Canceller

Feed Forward

Equalization

Viterbi

Decoder

DFE #1

DFE #N

ECHO

Canceller

NEXT

Canceller

NEXT

Canceller

+

Receive

Data

TX output channel 1

TX output channel 2

TX output channel 3

TX output channel 4

Removes Post

Cursor ISI

(both from

channel and

PR shaping)

Remove

Precursor

ISI

Provides 6dB

coding gain

Decision Feedback

Equalizers

.

.

Input Samples to Viterbi

+

-

8

From Other Channels

A/D

conv

AFE

Recovered Clock

Receive

Signal

802.3ab

PHY Start-up

1000BASE-T Start-up protocol provides for two different

start-up procedures for maximum robustness while

preserving complete interoperability:

- Blind Start-up: where all adaptive filter blocks converge

without sequencing. If the PHYs at the two ends of the link both

implement this procedure (which is determined during the

autonegotiation), the sequenced start-up is bypassed.

- Sequenced Start-up: where the convergence of various

adaptive blocks are separated in a 3 step sequence.

802.3ab

Eye Diagrams (master sequenced start-up)

802.3ab

100BASE-TX Receiver 1000BASE-T Receiver

A/D Conversion 5.5 bit ideal at 125MSamples/sec 7 bit ideal at 125MSamples/sec

DFE 10 Taps 14 Taps/Channel

FFE 8 Taps 12 Taps/Channel

NEXT Cancellers 0 75 Taps/Channel

ECHO Canceller 0 60 Taps

Critical Path 3 Input Add

+ 3 Input Select

+ 1 Slicer

4 Input Add-Compare Select

+ 3 Input Add

+ 5 Input Select

+ Branch Metric Compute

Normalized Gate Complexity 1 8

Receiver Design Parameter Comparison

802.3ab

Technical Details of 1000BASE-T

1000BASE-T Topology

Operation of 1000BASE-T

Signaling

Trellis Coded Modulation

Performance Evaluations

802.3ab

1000BASE-T Topology

Link Segments

1000BASE-T

Master PHY

1000BASE-T

Slave PHY

External

timing

Tx

Rx

Tx

Rx

Tx

Rx

Tx

Rx

Recovered

timing

Tx

Rx

Tx

Rx

Tx

Rx

Tx

Rx

802.3ab

Block Diagram of Transceiver

Hybrid

RECEIVER_B

Analog

Hybrid

NEXT

Canceller

ECHO

Canceller

VGA

Cable

TRANSMITTER_A

RECEIVER_A

Gain, Timing

TRANSMITTER_B

+

1000 Mb/s

Digital

Transmit

Analog

Receive

Filter

Digital Linear

FeedForward

Equalizer

Transmit

Filter Filter

Pair A

Pair B

G

I

I

Control

Side-Stream

Scrambler

Symbol

Encoder

Side-Stream

Descrambler

Viterbi

Decoder

Escape + Controls

&

&

Escape + Controls

A/D

D/A

M

NEXT

Canceller

NEXT

Canceller

Hybrid

RECEIVER_C

TRANSMITTER_C

Hybrid

RECEIVER_D

TRANSMITTER_D

Pai r C

Pair D

DFE +

802.3ab

Transmitter

Transmit Spectrum of 1000BASE-T

Pulse Template Example Implementation of Transmitter

D

0.25 0.75

SLOPE

DAC

Digital Transmit Filter

A

n

BI_DA

CONTROLLED

802.3ab

Signaling Features

Forward Error Correction (FEC) coded symbol mapping for

data

Algorithmic mapping and inverse mapping from octet data to a

quartet of quinary symbols and back

Uncorrelated symbols in the transmitted symbol stream

No correlation between symbol streams traveling both directions

on any pair combination

No correlation between symbol streams on pairs A, B, C and D

Ternary symbol mapping in idle and training modes to ease

blind startup and retraining

802.3ab

Signaling Features (cont.)

Ability to rapidly or immediately determine if a symbol

stream represents data, idle or carrier extension

Robust delimiters for SSD, ESD, and other control

signals

Ability to signal the status of the local receiver to the

remote PHY to indicate that the local receiver is not

operating reliably and requires retraining

Ability to automatically detect and correct for pair

swapping and unexpected cross-over connections

Ability to automatically detect and correct for incorrect

polarity in the connections

Ability to automatically correct for differential delay

variations across the wire-pairs

802.3ab

Side Stream Scrambler

Side Stream Scrambler employed by Master PHY

Side Stream Scrambler employed by Slave PHY

802.3ab

Random Bits for Octet Scrambling

Scr

n-1

[0]

T

Scr

n-1

[12] Scr

n-1

[13] Scr

n-1

[32]

T

T T T T T T T T T

Scr_B

n-1

[0]

T T T T T T T T

Scr_C

n-1

[0]

T T T T T T T T

Scr_D

n-1

[0]

T T T T T T T T

Sy

n

[2]

Sx

n

[2]

Sg

n

[2]

Sy

n

[1]

Sx

n

[1]

Sg

n

[1]

Sy

n

[0]

Sx

n

[0]

Sg

n

[0]

Sy

n

[3]

Sx

n

[3]

Sg

n

[3]

802.3ab

Symbol Mapping Reference Diagram

Odd/Even

Coding

Scrambling &

Encoding

Convolutional

Symbol

Mapping

Sign

Encoding

SnA

n

SnB

n

SnC

n

SnD

n

tx_enable

n

tx_enable

n

tx_error

n

Tx_D

n

[0:7]

Sx

n

[0:3]

Sy

n

[0:3]

Sg

n

[0:3]

Sc

n

[0:7] Sd

n

[0:8]

TA

n

TB

n

TC

n

TD

n

A

n

B

n

C

n

D

n

tx_enable

n

802.3ab

Trellis Coded Modulation

Purpose: To match the robustness of 3-level

100BASE-TX signaling with 5-level

1000BASE-T signaling

Implemented as a two-step approach:

- Convolutional Encoding to convert scrambled octet data to 9-bit word.

- Mapping by Set Partitioning to get 6dB noise immunity gain.

Scrambler

Tx_D

n

[0:7]

Sc

n

[0:7]

(Bitwise XOR)

T T T

Sd

n

[0]

Sd

n

[1]

Sd

n

[2]

Sd

n

[3]

Sd

n

[4]

Sd

n

[5]

Sd

n

[6]

Sd

n

[7]

Sd

n

[8]

Subset

Points

in

Subset

Index

coding_enable

802.3ab

Subset Mapping

Partition 5-levels into 2 1-D subsets:

X={-1,+1}, Y={-2,0,+2}.

Squared distance between elements in 1D subset is 4.

802.3ab

Trellis Diagram

Convolutional Encoder

Bits at time n

Convolutional Encoder

Bits at time n+1

D0 D2 D4 D6

D1 D3 D5 D7

000

001

010

011

100

101

110

111

000

001

010

011

100

101

110

111

D2 D0 D6 D4

D3 D1 D7 D5

D4 D6 D0 D2

D5 D7 D1 D3

D6 D4 D2 D0

D7 D5 D3 D1

D0 D2 D4 D6

D2 D0 D6 D4

D4 D6 D0 D2

D6 D4 D2 D0

D1 D3 D5 D7

D3 D1 D7 D5

D5 D7 D1 D3

D7 D5 D3 D1

802.3ab

Sequential Decoding

Squared distance between valid paths is also 4.

D2

D1

D6

D3

802.3ab

Packetizing the Trellis Code

Idle/Carrier Extension use 3-level signaling i.e. D0

subset

Data uses Trellis Coding

Reset convolutional encoder states to zero using two

symbol periods at End of Packet

Data Packet => Any State

Idle => State 000 Idle => State 000

Csreset

SSD

ESD

802.3ab

1000BASE-T Frame Structure

tx_enable

n

SSD

n

ESD

n

TXD[7:0]

Data stream

A

n

IDLE IDLE ESD DATA SSD

B

n

csreset

n

csreset

IDLE IDLE ESD DATA SSD csreset

IDLE IDLE ESD DATA SSD csreset

IDLE IDLE ESD DATA SSD csreset

C

n

D

n

802.3ab

Performance Evaluations

Worst Case 100m UTP-5 Channel

characteristics.

Design Point - 10dB

Design Point Simulations

Matlab Code Published

802.3ab

Worst Case 100m UTP-5 Channel

802.3ab

Design Point - 10dB

D/A: 17 levels at 125MHZ

Launch Level: 2V P-P

Analog Transmit Filter: Single pole RC

Analog Receive Filter: BW2@100MHz

A/D: 6.5bits ideal at 125MHz

2.2 Volts p-p (prob. of clipping 1E-25)

Baseline Wander Correction: Digital

FFE - #taps: 16 taps at 125MHz

DFE - #taps: 12 taps at 125MHz

NEXT Cancellers - #taps: 72 taps at 125MHz

Echo Canceller - #taps: 120 taps at 125MHz

Viterbi Decoder: 12-stage

Total worst-case latency: 31BT < 40BT

Uniform Jitter Tolerance for 0dB margin: 1.5ns P-P [>10ns P-P Gaussian]

Worst-Case noise immunity: Crane Test: 140mV P-P

Est. Gate Count/Power Consumption: 330K/4W

Margin without FEXT: 10.5dB

Margin with Worst-Case FEXT: 5.7dB

802.3ab

Design Results - 10dB

802.3ab

Design Results - 10dB

802.3ab

Detailed VLSI Implementation

DSP Requirements

Technology Background

Power requirements

Size and Layout

802.3ab

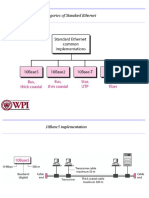

Transceiver Block Diagram

Blocks common between a Quad 100Base- TX and a 1000BASE-T

transceiver. NEXT and Echo cancellers are the major blocks

contributing to the added complexity over a Fully digital Quad-TX.

802.3ab

DSP Requirements

4 Equalizers (FFE/ FBE), 4 echo cancellers, 12 NEXT

cancellers running at 125 MHz clock rate which is also the

Baud rate

The bulk of the computation is in the adaptive Finite Impulse

Response (FIR) filters

The regularity of the filter structures makes the design task

quite manageable

802.3ab

Direct Form FIR Filter

802.3ab

Adaptive FIR

In an adaptive filter, in general, the output of the filter, y(n), is compared

against a desired reference r(n) which produces a measure to be used in an

algorithm for modifying the filter coefficients (a time varying system). The

filter coefficients are modified in a way to minimize the measure and bring

the filter output close to the desired output. In an important class of adaptive

filters, adaptation of the coefficients take place without any reference input.

This is called blind adaptation.

The most widely used adaptation algorithm is the Least Mean Square

(LMS) method where e (n) = r (n) - y (n) and the update is chosen to

minimize e

2

.

802.3ab

Linear Equalizer with LMS Update

The equalizers, NEXT cancellers and echo cancellers in a 1000Base- T

transceiver are all variations of this filter structure.

802.3ab

Echo Canceller Tap

802.3ab

Power Consumption

Corresponds to about 400,000 gates

Comparing to Quad-TX:

Fully digital Quad-TX, 3.3V, 0.50 CMOS 2.2W

1000BASE-T, 2.5V, 0.25 CMOS 3.1W

A worst case DSP complexity providing a very high margin of

operation:

802.3ab

1000BASE-T Copper Transceiver Layout

0.25mm CMOS, 5 layer metal

Based on actual layout from a

0.25mm CMOS library

4mm X 4mm active area

(65% - 75% of the area of

most existing 10/100 PHYs)

160 pins

802.3ab

3 Steps From 100Base-TX to 1000BASE-T

Start with a 100Base-TX DSP Based PHY

Use all four channels full duplex

400 MBps in both directions

Requires ECHO and NEXT canceling

Requires Master/Slave Clocking

Remove 4B/5B Encoding

500 MBps in both directions

5 Level Signaling - 2 Bits/Symbol

1000 MBps in both directions

Requires FEC to get back the 6dB SNR

The major task was adding FEC

S-ar putea să vă placă și

- Gigabit Ethernet Over Category 5 Fanny MlinarskyDocument20 paginiGigabit Ethernet Over Category 5 Fanny MlinarskyHusam Abduldaem MohammedÎncă nu există evaluări

- Panduit - Testing 10Gbps WPDocument12 paginiPanduit - Testing 10Gbps WPpmoreno64Încă nu există evaluări

- Roadcom Ieee802.3ap OverviewDocument30 paginiRoadcom Ieee802.3ap OverviewmilepnÎncă nu există evaluări

- Communication Standards IEEE 802 - 3Document3 paginiCommunication Standards IEEE 802 - 3Trung PhamÎncă nu există evaluări

- 802.3bz Link Segment Considerations Waikola, HI: July 2015Document24 pagini802.3bz Link Segment Considerations Waikola, HI: July 2015jose_franckÎncă nu există evaluări

- E-Rake Go The Extra Mile OFDM Multi Hops RepeaterDocument9 paginiE-Rake Go The Extra Mile OFDM Multi Hops Repeatermacao100Încă nu există evaluări

- ANSI - TIA-568-C.0-2009 February 2009 Annex DDocument3 paginiANSI - TIA-568-C.0-2009 February 2009 Annex DAndresÎncă nu există evaluări

- Ieee 802 PDFDocument4 paginiIeee 802 PDFthriller456Încă nu există evaluări

- Ws 13 Thornycroft 80211Document31 paginiWs 13 Thornycroft 80211javierdb2012Încă nu există evaluări

- Tranmission LineDocument47 paginiTranmission LineDanu MamlukatÎncă nu există evaluări

- IEEE 802.11n PHY Overview and Channel Models: Azimuth ConfidentialDocument26 paginiIEEE 802.11n PHY Overview and Channel Models: Azimuth ConfidentialVanhan HoÎncă nu există evaluări

- 7.extra Low Voltage System PDFDocument83 pagini7.extra Low Voltage System PDFCik Puan Oda67% (6)

- Alcatel-Lucent 9600 USY: Sdhmedium-Orhigh-CapacitydigitalmicrowavelinksDocument4 paginiAlcatel-Lucent 9600 USY: Sdhmedium-Orhigh-Capacitydigitalmicrowavelinksaltus_aryaÎncă nu există evaluări

- Alcatel 9600LSYDocument2 paginiAlcatel 9600LSYsamiÎncă nu există evaluări

- Pasolink Training in VietnamDocument332 paginiPasolink Training in Vietnamtuannv191177100% (1)

- Modular IP Streamer With Descrambling & Scrambling FunctionalityDocument5 paginiModular IP Streamer With Descrambling & Scrambling FunctionalityVíctor MayaÎncă nu există evaluări

- Cereagon - IP-50EX E-Band - Datasheet - Rev - N.04Document4 paginiCereagon - IP-50EX E-Band - Datasheet - Rev - N.04daniyartoktarbayev100% (1)

- 3HH11206AAAATQZZA03Document68 pagini3HH11206AAAATQZZA03seamesaiÎncă nu există evaluări

- Ethernet 102 The Physical Layer of EthernetDocument30 paginiEthernet 102 The Physical Layer of EthernetPhátTrầnÎncă nu există evaluări

- Comtech/EFData CTOG-250 Traffic Optimization Gateway DatasheetDocument2 paginiComtech/EFData CTOG-250 Traffic Optimization Gateway DatasheetarzeszutÎncă nu există evaluări

- 10GBASE T TutorialDocument56 pagini10GBASE T TutorialmonyongsiaÎncă nu există evaluări

- Alxxf Mp400: Wireless Ethernet SolutionDocument2 paginiAlxxf Mp400: Wireless Ethernet SolutionpgrÎncă nu există evaluări

- Ieee 802Document3 paginiIeee 802M Zubair AslamÎncă nu există evaluări

- (3-FIB) Fiber Optic Communications InterfaceDocument6 pagini(3-FIB) Fiber Optic Communications InterfaceRaghavanJayaramanÎncă nu există evaluări

- Transmission Is The Act of Transporting Information From One Location To Another Via A SignalDocument55 paginiTransmission Is The Act of Transporting Information From One Location To Another Via A SignalDeepesh TrivediÎncă nu există evaluări

- AZ110 DatasheetDocument2 paginiAZ110 DatasheetJuana SosaÎncă nu există evaluări

- Pasolink V4 Training ManualDocument88 paginiPasolink V4 Training ManualCong Thanh100% (3)

- Mimo Wifi NabarDocument33 paginiMimo Wifi NabarAmine BouazÎncă nu există evaluări

- SICOM3024P: Layer 2 24+4G Port Managed Rack Mountable IEC61850 SwitchDocument3 paginiSICOM3024P: Layer 2 24+4G Port Managed Rack Mountable IEC61850 SwitchRonal DouglasÎncă nu există evaluări

- 802.11n WLAN StandardDocument38 pagini802.11n WLAN StandardAyush KumarÎncă nu există evaluări

- EthernetDocument42 paginiEthernetDip DasÎncă nu există evaluări

- Air Ap2802i e k9 DatasheetDocument4 paginiAir Ap2802i e k9 DatasheetDarwin.pilloÎncă nu există evaluări

- DTXDocument22 paginiDTXEduardo SánchezÎncă nu există evaluări

- Panduit098765 PDFDocument6 paginiPanduit098765 PDFThi AgoÎncă nu există evaluări

- CN Data Sheet PTP 450i IntegratedDocument5 paginiCN Data Sheet PTP 450i IntegratedXavi QuingaÎncă nu există evaluări

- Ethernet Physical LayerDocument7 paginiEthernet Physical LayerMukesh ChavanÎncă nu există evaluări

- Solutions - Silvus Streamcaster 3800 Mimo Radio DatasheetDocument3 paginiSolutions - Silvus Streamcaster 3800 Mimo Radio Datasheetapi-163871212Încă nu există evaluări

- Etx-200 Datasheet OtdrDocument5 paginiEtx-200 Datasheet OtdrHudionoHoodÎncă nu există evaluări

- Ets 1000g1 Ang DiscontinuedDocument6 paginiEts 1000g1 Ang DiscontinuedAnu ThekkeveettilÎncă nu există evaluări

- Presentation On 802.11acDocument88 paginiPresentation On 802.11acokhtayÎncă nu există evaluări

- Lan Overview Tia Eia 568 b.1, b.2, b.2.1Document22 paginiLan Overview Tia Eia 568 b.1, b.2, b.2.1Ozz GarciaÎncă nu există evaluări

- 5G Solution Description-1Document12 pagini5G Solution Description-1mhnor48Încă nu există evaluări

- Imc-21 Series: Entry-Level Industrial 10/100baset (X) To 100basefx Media ConvertersDocument3 paginiImc-21 Series: Entry-Level Industrial 10/100baset (X) To 100basefx Media ConvertersRamesh BabuÎncă nu există evaluări

- IEEE 802 3 Cableado Cobre FIbraDocument17 paginiIEEE 802 3 Cableado Cobre FIbraIngKarasuma1Încă nu există evaluări

- Cambium Networks Data Sheet PTP-450i PDFDocument5 paginiCambium Networks Data Sheet PTP-450i PDFFlorin StoianÎncă nu există evaluări

- Flex900 TronkalDocument4 paginiFlex900 TronkalArmando GalindoÎncă nu există evaluări

- Optimux-1553: STM-1/OC-3 Terminal MultiplexerDocument4 paginiOptimux-1553: STM-1/OC-3 Terminal MultiplexerLe Viet HaÎncă nu există evaluări

- FibeAir IP-20E DatasheetDocument4 paginiFibeAir IP-20E DatasheetrgualbertÎncă nu există evaluări

- 802.11ac: Overcoming Test Challenges: National InstrumentsDocument24 pagini802.11ac: Overcoming Test Challenges: National Instrumentsjavierdb2012Încă nu există evaluări

- Eds-P510 Series: 7+3G-Port Gigabit Poe Managed Ethernet SwitchesDocument7 paginiEds-P510 Series: 7+3G-Port Gigabit Poe Managed Ethernet SwitchesUsman ZouqueÎncă nu există evaluări

- Fast Ethernet and Gigabit EthernetDocument35 paginiFast Ethernet and Gigabit EthernetWaqar AsmatÎncă nu există evaluări

- Microwave NotesDocument16 paginiMicrowave NotesIndrajit RoyÎncă nu există evaluări

- PLC1790 B1&2 enDocument48 paginiPLC1790 B1&2 enAghil Ghiasvand MkhÎncă nu există evaluări

- Huawei S5700-28p-Li-Ac DatasheetDocument9 paginiHuawei S5700-28p-Li-Ac DatasheetMeela Zeng100% (1)

- Radio Frequency Identification and Sensors: From RFID to Chipless RFIDDe la EverandRadio Frequency Identification and Sensors: From RFID to Chipless RFIDÎncă nu există evaluări

- Ethernet Networks: Design, Implementation, Operation, ManagementDe la EverandEthernet Networks: Design, Implementation, Operation, ManagementEvaluare: 4 din 5 stele4/5 (1)

- Chipless Radio Frequency Identification Reader Signal ProcessingDe la EverandChipless Radio Frequency Identification Reader Signal ProcessingÎncă nu există evaluări

- Indoor Radio Planning: A Practical Guide for 2G, 3G and 4GDe la EverandIndoor Radio Planning: A Practical Guide for 2G, 3G and 4GEvaluare: 5 din 5 stele5/5 (1)

- Advanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionDe la EverandAdvanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionÎncă nu există evaluări

- IBM 3271-3272 To Device Interface Spec May74Document23 paginiIBM 3271-3272 To Device Interface Spec May74cdrbcÎncă nu există evaluări

- VTL Release NotesDocument16 paginiVTL Release NotescdrbcÎncă nu există evaluări

- 3791 To 3277 Display Station Interface Product Attachement Manual Mar75Document10 pagini3791 To 3277 Display Station Interface Product Attachement Manual Mar75cdrbcÎncă nu există evaluări

- The MVS 3.8j Tur (N) Key 4-System: User's ManualDocument28 paginiThe MVS 3.8j Tur (N) Key 4-System: User's ManualcdrbcÎncă nu există evaluări

- RSA AM Virtual Appliance Getting StartedDocument10 paginiRSA AM Virtual Appliance Getting StartedcdrbcÎncă nu există evaluări

- README MVS TK4 - v1.00 Update 08 PDFDocument12 paginiREADME MVS TK4 - v1.00 Update 08 PDFcdrbc100% (1)

- Rsa Authentication Manager 8.2 SP1 Setup Config GuideDocument126 paginiRsa Authentication Manager 8.2 SP1 Setup Config GuidecdrbcÎncă nu există evaluări

- MindShare ISA 3rd EbookDocument544 paginiMindShare ISA 3rd Ebookcdrbc100% (1)

- Aw186 Quick View With Full TocDocument36 paginiAw186 Quick View With Full ToccdrbcÎncă nu există evaluări

- Cisco 7965 Installation GuideDocument12 paginiCisco 7965 Installation GuidecdrbcÎncă nu există evaluări

- SELinux Coloring BookDocument16 paginiSELinux Coloring BookMadeline ThompsonÎncă nu există evaluări

- 64bit Linux-Myths and FactsDocument38 pagini64bit Linux-Myths and FactspearlramarÎncă nu există evaluări

- Hitachi Thunder 9200 Windows NT Host Installation Guide (SCSI)Document26 paginiHitachi Thunder 9200 Windows NT Host Installation Guide (SCSI)cdrbcÎncă nu există evaluări

- Hitachi Thunder 9200 Dual Active ID Succession (5800/9200) User's GuideDocument34 paginiHitachi Thunder 9200 Dual Active ID Succession (5800/9200) User's GuidecdrbcÎncă nu există evaluări

- FalconStor VTL-S User GuideDocument352 paginiFalconStor VTL-S User GuidecdrbcÎncă nu există evaluări

- ISA System ArchitectureDocument521 paginiISA System Architecturecdrbc100% (1)

- System Architecture 3e - Tom ShanleyDocument206 paginiSystem Architecture 3e - Tom ShanleyMiftah Jannah100% (2)

- Virtual Memory Denning 1970Document37 paginiVirtual Memory Denning 1970cdrbcÎncă nu există evaluări

- AMS WMS Global 19 Inch Rack Reference GuideDocument36 paginiAMS WMS Global 19 Inch Rack Reference GuidecdrbcÎncă nu există evaluări

- SCSI-3 Enclosure ServicesDocument124 paginiSCSI-3 Enclosure ServicescdrbcÎncă nu există evaluări

- Fault Tolerant SytemsDocument7 paginiFault Tolerant SytemscdrbcÎncă nu există evaluări

- ISA System ArchitectureDocument521 paginiISA System Architecturecdrbc100% (1)

- SCSI Primary Commands 2 (SPC-2)Document293 paginiSCSI Primary Commands 2 (SPC-2)cdrbcÎncă nu există evaluări

- UEFI 2 3 1 Errata C FinalDocument2.224 paginiUEFI 2 3 1 Errata C FinalcdrbcÎncă nu există evaluări

- A20 Aix1lb02Document5 paginiA20 Aix1lb02cdrbcÎncă nu există evaluări

- Cisco Storage Design Fundamentals: Lab GuideDocument96 paginiCisco Storage Design Fundamentals: Lab Guidecdrbc100% (1)

- Cisco San PDFDocument364 paginiCisco San PDFhema_rao2250100% (1)

- MQ15 - WebSphere MQ System Administration IDocument660 paginiMQ15 - WebSphere MQ System Administration IcdrbcÎncă nu există evaluări

- Servicing HP Proliant Server Products - Student Guide - June 2003Document421 paginiServicing HP Proliant Server Products - Student Guide - June 2003cdrbcÎncă nu există evaluări

- Alteon-Tech-Spec ODS-VLDocument3 paginiAlteon-Tech-Spec ODS-VLYo ChepoÎncă nu există evaluări

- Mainboard Foxconn Model 741M01CDocument40 paginiMainboard Foxconn Model 741M01CHo Thanh BinhÎncă nu există evaluări

- 1 Electronica IndustrialDocument17 pagini1 Electronica Industrialjerrygo_03Încă nu există evaluări

- T-Con Power Main Chip Philips Tpm5.1e LaDocument2 paginiT-Con Power Main Chip Philips Tpm5.1e LaKamal AltawilÎncă nu există evaluări

- Adaptive FilterDocument3 paginiAdaptive FilterAjith Kumar RsÎncă nu există evaluări

- Counters, Ripple Counters, Ring CountersDocument16 paginiCounters, Ripple Counters, Ring CountersAmoga LekshmiÎncă nu există evaluări

- 2n3903 2n3904 PDFDocument8 pagini2n3903 2n3904 PDFOpik BiasaÎncă nu există evaluări

- Condor Cab SimDocument6 paginiCondor Cab SimWallas MouraÎncă nu există evaluări

- TASCAM Efs Model12 Om VCDocument212 paginiTASCAM Efs Model12 Om VCDorian BanegasÎncă nu există evaluări

- Liu 2019theoretical Analysis of The Peak-to-Average Power Ratio and Optimal Pulse Shaping Filter Design For GFDM SystemsDocument16 paginiLiu 2019theoretical Analysis of The Peak-to-Average Power Ratio and Optimal Pulse Shaping Filter Design For GFDM Systemssameer khanÎncă nu există evaluări

- Bridges: Electronic Instrumentation 15EC35Document41 paginiBridges: Electronic Instrumentation 15EC35Darshan rajÎncă nu există evaluări

- Specification DNA-31734 Tracking Resistant ADSS CableDocument5 paginiSpecification DNA-31734 Tracking Resistant ADSS CableDerrick Kojo SenyoÎncă nu există evaluări

- Sirio SY 27-4 PDFDocument4 paginiSirio SY 27-4 PDFAriel BecerraÎncă nu există evaluări

- TB No. Trisen Ferrule Details On TRISENDocument3 paginiTB No. Trisen Ferrule Details On TRISENabhishek murarkaÎncă nu există evaluări

- SsdacDocument4 paginiSsdacSavitha PadupallyÎncă nu există evaluări

- Kal Sys20 en 2V2 Rec 102-020401275Document8 paginiKal Sys20 en 2V2 Rec 102-020401275Amir IzzatÎncă nu există evaluări

- XII Chapter 15 Electrical Measuring InstrumentDocument7 paginiXII Chapter 15 Electrical Measuring InstrumentMaryum ZahidÎncă nu există evaluări

- MA-352 - Owner's ManualDocument28 paginiMA-352 - Owner's ManualStefanoViganóÎncă nu există evaluări

- Computer Science Test Systems Architecture.199788941Document8 paginiComputer Science Test Systems Architecture.199788941omotayoomotola485Încă nu există evaluări

- Giannis Parios 2007 Technical RiderDocument5 paginiGiannis Parios 2007 Technical RiderRiderGeeks.comÎncă nu există evaluări

- Portable Lte Base StationDocument5 paginiPortable Lte Base StationGülçin KöseÎncă nu există evaluări

- IP DECT UpdatesDocument13 paginiIP DECT UpdatesAnonymous 87K2OLÎncă nu există evaluări

- Economics (Internet Service Provider)Document20 paginiEconomics (Internet Service Provider)romelyn xygnetsÎncă nu există evaluări

- CSS Ret 200 PDFDocument3 paginiCSS Ret 200 PDFsaubhaagyapurnaÎncă nu există evaluări

- MOSFET ExperimentDocument13 paginiMOSFET ExperimentsureshÎncă nu există evaluări

- SM G610FDocument45 paginiSM G610FILAF TELELKOMÎncă nu există evaluări

- Meraki Datasheet MR18Document4 paginiMeraki Datasheet MR18fiqur1Încă nu există evaluări

- Synchronous Timer Series EM 1000 - GIC INdiaDocument2 paginiSynchronous Timer Series EM 1000 - GIC INdiaPrasadPurohitÎncă nu există evaluări

- LC-20S5U: LCD Color TelevisionDocument77 paginiLC-20S5U: LCD Color TelevisionFrancisco OrozcoÎncă nu există evaluări