Documente Academic

Documente Profesional

Documente Cultură

Diagrama Bloques Computadora

Încărcat de

lobo20110 evaluări0% au considerat acest document util (0 voturi)

90 vizualizări14 paginiDrepturi de autor

© © All Rights Reserved

Formate disponibile

DOC, PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca DOC, PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

90 vizualizări14 paginiDiagrama Bloques Computadora

Încărcat de

lobo2011Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca DOC, PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 14

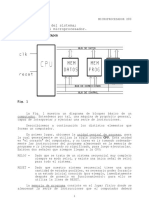

DIAGRAMA A BLOQUES DE UNA COMPUTADORA

BUS DE DATOS: Interconecta los dispositivos de entrada/salida, la memoria

RAM y el CU!

BUS DE DIRECCIO"ES: Se #tili$a para direccional las localidades de memoria

y los dispositivos de entrada/salida!

ROCESADOR

Se considera el cere%ro de la comp#tadora !Controla la

operaci&n de la comp#tadora y lleva a ca%o las '#nciones del

procesamiento de datos! (eneralmente se le conoce como

cp# por la si)la en in)les de central process #nit! Esta

'ormado por la #nidad de control la #nidad aritm*tica l&)ica y

re)istros!

+a #nidad de control es el n,cleo del procesador s#s '#nciones son:

A- +eer e interpretar las instr#cciones de los pro)ramas!

B- Diri)ir la operaci&n de los componentes internos del procesador!

C- Controlar el 'l#.o de entrada/salida de pro)rama y datos en RAM!

+A U"IDAD DE CO"TRO+ ESTA /ORMADA OR:

RE(ISTRO DE I"TRUCCIO": Contienen la con'i)#raci&n 0#e identi'ica a la

instr#cci&n 0#e en ese momento se esta e.ec#tando!

RE(ISTRO DE ROOSITO (E"ERA+: Memorias de alta velocidad 0#e

almacena los datos 0#e re0#ieren procesamiento inmediato e in'ormaci&n de

control!

CO"TADOR DE RO(RAMA: Contiene la direcci&n de RAM de la si)#iente

instr#cci&n 0#e se e.ec#tara! Al inicio contiene la primera direcci&n del

pro)rama! Cada ve$ 0#e se termina #na instr#cci&n, se incrementa

a#tom1ticamente en #no!

RE+O2: El relo. es #n circ#ito oscilador 0#e )enera p#lsos a #na 'rec#encia

constante! Estos p#lsos sincroni$an la e.ec#ci&n de cada instr#cci&n! Si en #na

comp#tadora el relo. tiene #n periodo de 344ns se dice 0#e tra%a.a a 34 M 5$!

E+ DECODI/ICADOR: Se encar)a de e6traer el c&di)o de operaci&n de la

instr#cci&n 0#e esta en el re)istro de instr#cci&n lo anali$a y determina el

con.#nto de pasos elementales en 0#e se descompone esa instr#cci&n

concreta y emite, a trav*s del sec#anciador, las se7ales necesarias al resto de

elementos para s# e.ec#ci&n!

E+ SECUE"CIADOR: Env8a mediante el %#s de datos se7ales de controla

tam%i*n llamadas microordenes a los componentes del sistema! Estas

microordenes sincroni$adas por el relo. 5acen 0#e se vaya e.ec#tando la

instr#cci&n!

U"IDAD ARITMETICA +O(ICA

Se le conoce como al#, si)las en in)les de 9arit5metic lo)ia #nit -! Es #n

con.#nto de circ#itos electr&nicos di)itales 0#e reali$an operaciones aritm*ticas

y l&)icas elementales! Se com#nica con las otras #nidades a trav*s del %#s! +a

al# esta constit#ida por :

Circ#ito operacional: Es #n con.#nto de

comp#ertas %1sicas or)ani$adas en

di'erentes arre)los para llevar aca%o las

operaciones!

Re)istros de entrada: (#ardan los datos

0#e necesita #na instr#cci&n para ser

e'ect#ada

Ac#m#lador: (#arda los res#ltados de las operaciones reali$adas por el circ#ito

operacional! Se conecta con los re)istros de entrada 9en caso de encadenaci&n-

y con el %#s de datos para la transmisi&n de res#ltados a la #nidad de control o a

la memoria!

Re)istro de estado: (r#po de %iesta%les 0#e )#ardan condiciones de la ,ltima

operaci&n 0#e p#eda a'ectar a operaciones posteriores

MEMORIA RIMARIA

Circ#itos donde se almacenan en 'orma temporal los pro)ramas y los datos!

+a in'ormaci&n procesada por el cp# se almacena normalmente en la memoria

principal 5asta 0#e termina la e.ec#ci&n del pro)rama! E6isten di'erentes tipos de

memoria primaria:

ROM 9read only memory-! :iene pro)ramada de 'a%rica

solo p#ede leerse #n e.emplo es el %ios

/las5: 9memoria instant1nea- memoria no vol1til 0#e el #s#ario p#ede alterar

es parte de m#c5os dispositivos de entrada/salida y de almacenamiento!

Cac5e: Tra%a.a de 'orma similar a la ram pero acelera y 'acilita a#n m1s la

transmisi&n de datos e instr#cciones! Se dice 0#e es ; o < veces m1s r1pida

0#e la ram pero es m#c5o mas cara se #%ica entre el procesador y la ram

RAM 9random access memory- memoria de lect#ra/escrit#ra #s#almente se

conoce como memoria principal todos los pro)ramas y datos de%en tras'erirse a

ram desde #n dispositivo de entrada! +a memoria esta dividida en celdas

n#meradas consec#tivamente! A esta n#meraci&n se le conoce como direcci&n

de memoria! +a memoria ram es vol1til!

E+EME"TOS DE U"A MEMORIA

3- Re)istro de memoria de datos contiene la direcci&n de memoria de celda en

la 0#e se va a reali$ar #na operaci&n de lect#ra o de escrit#ra!

=- Re)istro de intercam%io de memoria en operaciones de lect#ra reci%e el

dato 0#e se lee para enviarle a otra #nidad a trav*s del %#s! Si la operaci&n

es escrit#ra entonces el %#s reci%e #n dato procedente de otra #nidad!

>- Selector de memoria: conecta la celda con la 0#e va a reali$ar #na

operaci&n con el re)istro de intercam%io de memoria

MEMORIA SECU"DARIA

Son los diversos dispositivos en los c#ales se almacena in'ormaci&n en 'orma

semipermanente !los datos de almacenan en la memoria sec#ndaria y l#e)o se

llevan a la memoria ram act#almente e6iste #na )ran variedad de medios de

almacenamiento sec#ndario entre estos podemos mencionar: disco 'le6i%le

cintas ma)n*ticas disco d#ro CD ROM dvd etc!

CICLO de Instruccin

+a e.ec#ci&n de #na instr#cci&n invol#cra dos 'ases: la primera es la 'ase de

%,s0#eda de la instr#cci&n

En donde se 5ace la trans'erencia de la instr#cci&n 0#e se va a e.ec#tar desde

la RAM a la Unidad de Control! +a se)#nda es la 'ase de e.ec#ci&n la c#al

consiste en la reali$aci&n de todas las acciones 0#e

Con'orman la instr#cci&n en s8!

FASE DE BUSQUEDA

3- +a #nidad de control env8a #n micro orden para 0#e el Contador de

ro)rama pase s# contenido

Al Re)istro de Direcci&n de Memoria!

=- El selector activa la celda!

>- El contenido de la celda pasa al Re)istro de Intercam%io de Memoria

?- +a instr#cci&n pasa al Re)istro de Instr#cci&n

;- El Decodi'icador anali$a la instr#cci&n, se prepara para activar el circ#ito 0#e

reali$a la operaci&n En la A+U e in'orma al sec#enciador!

<- El contador de pro)rama se a#to incrementa en 3!

FASE DE EJECUCIN

3! Se transmite la direcci&n de la primera instr#cci&n del Re)istro de Instr#cci&n

al Re)istro de Direcci&n de Memoria!

=! El selector conecta la celda al Re)istro de Intercam%io de Memoria y e6trae

el operando 3!

>! El operando pasa del Re)istro de Intercam%io de Memoria al Re)istro de

Entrada 3!

?! Se transmite la direcci&n del se)#ndo operando del Re)istro de Instr#cci&n

al Re)istro de Direcci&n de Memoria!

;! El selector conecta la celda al Re)istro de Intercam%io de Memoria y e6trae

el operando >!

<! El operando pasa del Re)istro de Intercam%io de Memoria al Re)istro de

Entrada =!

@! El sec#enciador manda #n micro orden a la A+U para 0#e e.ec#te la

operaci&n! El res#ltado se (#arda en el Ac#m#lador!

A! El res#ltado pasa de la Al# al Re)istro de Intercam%io de Memoria!

B! Se trans'iere la direcci&n donde se va a )#ardar el res#ltado al Re)istro de

Direcci&n de

Memoria!

34! Se activa la celda con el Selector y el res#ltado pasa del Re)istro de

Intercam%io de Memoria a la celda de memoria!

S-ar putea să vă placă și

- Partes Internas Del MicroprocesadorDocument12 paginiPartes Internas Del MicroprocesadorAlfredo HBÎncă nu există evaluări

- El Computador RISC & CISCDocument32 paginiEl Computador RISC & CISCKEVIN SHARIFF MANTILLA MEZAÎncă nu există evaluări

- 1.0.el Computador-RISC - CISCDocument32 pagini1.0.el Computador-RISC - CISCBryan Daniell Arrivasplata RojasÎncă nu există evaluări

- Microprocesadores CuestionarioDocument11 paginiMicroprocesadores CuestionarioGastón GallegosÎncă nu există evaluări

- Introducción A Los MicrocontroladoresDocument12 paginiIntroducción A Los MicrocontroladoresJunior FigueroaÎncă nu există evaluări

- Apuntes HardwareDocument7 paginiApuntes Hardwareripela49011Încă nu există evaluări

- Examen de Certificación Práctica CCENT #1y2Document85 paginiExamen de Certificación Práctica CCENT #1y2María Gabriela CárdenasÎncă nu există evaluări

- Tecnicas Que Se Han Implementado Dentro Del Microprocesador para Mejorar Su RendimientoDocument3 paginiTecnicas Que Se Han Implementado Dentro Del Microprocesador para Mejorar Su RendimientoRenzo Bassallo LeonÎncă nu există evaluări

- TP MicrocontroladoresDocument3 paginiTP MicrocontroladoresBruno TorrejonÎncă nu există evaluări

- Prueba de Primer Modulo Alfabetizacion DigitalDocument2 paginiPrueba de Primer Modulo Alfabetizacion DigitalNadia AndradeÎncă nu există evaluări

- Guia 1 Informatica Basica.Document10 paginiGuia 1 Informatica Basica.lumarirairaÎncă nu există evaluări

- Teoria AssemblerDocument36 paginiTeoria Assemblerjaime_parada3097Încă nu există evaluări

- 1.2.1 El Procesador y Sus Registros - OdpDocument22 pagini1.2.1 El Procesador y Sus Registros - OdpErwin MontesÎncă nu există evaluări

- Programación en Lenguaje EnsambladorDocument35 paginiProgramación en Lenguaje EnsambladorRodrigo GarciaÎncă nu există evaluări

- Assembler InterrupcionesDocument6 paginiAssembler InterrupcionesMaricel Huamani MezaÎncă nu există evaluări

- Autoevaluacion 1 MicrocontroladoresDocument8 paginiAutoevaluacion 1 MicrocontroladoresAndres MartínezÎncă nu există evaluări

- Diagrama Bloques ComputadoraDocument6 paginiDiagrama Bloques ComputadoraLuis Felipe OsorioÎncă nu există evaluări

- Memorias ProgramablesDocument22 paginiMemorias ProgramablesA.JÎncă nu există evaluări

- Unidad Central de ProcesoDocument5 paginiUnidad Central de ProcesoJose NainÎncă nu există evaluări

- Diagrama A Bloques de Una ComputadoraDocument15 paginiDiagrama A Bloques de Una ComputadoraAnabelJulianaVarhenVilelaÎncă nu există evaluări

- Sistemas Operativos ISCDocument233 paginiSistemas Operativos ISCFernando Fuentes BetancourtÎncă nu există evaluări

- Un Microprocesador de 8 Bits Z80 PDFDocument85 paginiUn Microprocesador de 8 Bits Z80 PDFVictor Hugo Hernandez100% (1)

- Tutorial SimuprocDocument10 paginiTutorial SimuprocIrving Jesus Sanchez CamposÎncă nu există evaluări

- PROFIBUS VDFDocument12 paginiPROFIBUS VDFClemente Serrano JuradoÎncă nu există evaluări

- Uf ProcesadorDocument0 paginiUf Procesadormavimu_20Încă nu există evaluări

- Ejercicios de MMEDocument4 paginiEjercicios de MMEfraanmp93Încă nu există evaluări

- Organización Del ProcesadorDocument12 paginiOrganización Del ProcesadorGeovanny Quiroz MoncerradÎncă nu există evaluări

- Repertorio de Instrucciones-Características y FuncionesDocument49 paginiRepertorio de Instrucciones-Características y FuncionesxdadaÎncă nu există evaluări

- Sistemas Microprocesados PDFDocument40 paginiSistemas Microprocesados PDFrubenutnÎncă nu există evaluări

- Autómatas ProgramablesDocument7 paginiAutómatas ProgramablesTom FarroÎncă nu există evaluări

- Unidad Central de Proceso o UCPDocument3 paginiUnidad Central de Proceso o UCPPablo MontoyaÎncă nu există evaluări

- Romero Mendez Nelson Unidad 4 Sistemas ProgramablesDocument8 paginiRomero Mendez Nelson Unidad 4 Sistemas ProgramablesNelson Romero MéndezÎncă nu există evaluări

- Lab MC P3 1618200Document9 paginiLab MC P3 1618200luis gonzalezÎncă nu există evaluări

- Introduccion A Grafcet PDFDocument524 paginiIntroduccion A Grafcet PDFChava TututiÎncă nu există evaluări

- La Memoria ROMDocument8 paginiLa Memoria ROMJesus Marchan NavarroÎncă nu există evaluări

- Un Microprocesador de 8 Bits Z80Document85 paginiUn Microprocesador de 8 Bits Z80Sebastián SandovalÎncă nu există evaluări

- Sistemas EmbebidosDocument86 paginiSistemas EmbebidosfrednielsÎncă nu există evaluări

- Taller de OrganizaciónDocument5 paginiTaller de OrganizaciónGREGORY HUACONÎncă nu există evaluări

- Comandos OSIDocument3 paginiComandos OSIAlfredÎncă nu există evaluări

- UntitledDocument7 paginiUntitledBRUHÎncă nu există evaluări

- Unidad IDocument10 paginiUnidad IJose Manuel Godoy EscribarÎncă nu există evaluări

- Ensayo Unidad 1 Arquitectura CISC y RISCDocument15 paginiEnsayo Unidad 1 Arquitectura CISC y RISCing_jonny23Încă nu există evaluări

- Introduccion PVMDocument31 paginiIntroduccion PVMtorpocoe6797Încă nu există evaluări

- Manual de Mantenimiento de ComputadorasDocument84 paginiManual de Mantenimiento de ComputadorasMari MedranoÎncă nu există evaluări

- Circutos Digitales y Microprocesador (Diseño de Motor Paso A Paso Con Arduino)Document20 paginiCircutos Digitales y Microprocesador (Diseño de Motor Paso A Paso Con Arduino)Jose MorenoÎncă nu există evaluări

- Preguntas Iniciales Diagnostico Grado 10Document13 paginiPreguntas Iniciales Diagnostico Grado 10kiara1202Încă nu există evaluări

- Curso Basico PLCDocument49 paginiCurso Basico PLCSaul Garcia AguilarÎncă nu există evaluări

- Modelo OsiDocument61 paginiModelo OsiJesica Reyes FloresÎncă nu există evaluări

- Componentes de Una ComputadoraDocument22 paginiComponentes de Una ComputadoraAbdiel OmañaÎncă nu există evaluări

- Informe InstruccionesDocument32 paginiInforme InstruccionesAnthony ValleÎncă nu există evaluări

- Cuestionario de PLCDocument6 paginiCuestionario de PLCBrayan Iza MHÎncă nu există evaluări

- Diagrama de Computadora y Funcionamiento-El Fenómeno CibernéticoDocument8 paginiDiagrama de Computadora y Funcionamiento-El Fenómeno CibernéticoAli SerranoÎncă nu există evaluări

- Programación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeDe la EverandProgramación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeÎncă nu există evaluări

- UF0852 - Instalación y actualización de sistemas operativosDe la EverandUF0852 - Instalación y actualización de sistemas operativosEvaluare: 5 din 5 stele5/5 (1)

- Comprobación y optimización del programa cnc para el mecanizado por arranque de viruta. FMEH0109De la EverandComprobación y optimización del programa cnc para el mecanizado por arranque de viruta. FMEH0109Încă nu există evaluări

- UF1275 - Selección, instalación, configuración y administración de los servidores de transferencia de archivosDe la EverandUF1275 - Selección, instalación, configuración y administración de los servidores de transferencia de archivosÎncă nu există evaluări

- Operaciones Auxiliares de Mantenimiento de Sistemas Microinformáticos (MF1208_1)De la EverandOperaciones Auxiliares de Mantenimiento de Sistemas Microinformáticos (MF1208_1)Încă nu există evaluări

- UF0512 - Transmisión de información por medios convencionales e informáticosDe la EverandUF0512 - Transmisión de información por medios convencionales e informáticosÎncă nu există evaluări

- CanicasrojasDocument17 paginiCanicasrojaslobo2011Încă nu există evaluări

- Examen Diagnostico de AgroecologiaDocument3 paginiExamen Diagnostico de Agroecologialobo2011Încă nu există evaluări

- ¿Qué Es Un Gerente?Document9 pagini¿Qué Es Un Gerente?lobo2011Încă nu există evaluări

- Aprendizaje CooperativoDocument38 paginiAprendizaje CooperativoglovinÎncă nu există evaluări

- El Mayor Éxito Es Ser FelizDocument31 paginiEl Mayor Éxito Es Ser Felizlobo2011Încă nu există evaluări

- Desarrollo Sostenible UNESCODocument53 paginiDesarrollo Sostenible UNESCORobinson Chiran AcostaÎncă nu există evaluări

- Práctica 1-Disección de Un Corazón de CerdoDocument4 paginiPráctica 1-Disección de Un Corazón de Cerdolobo2011Încă nu există evaluări

- Calculo Diferencial Integral Func Una Var PDFDocument683 paginiCalculo Diferencial Integral Func Una Var PDFVíctor Raúl Macedo Q.Încă nu există evaluări

- FabulaDocument11 paginiFabulalobo2011Încă nu există evaluări

- TERNURADocument33 paginiTERNURAGabrielaCuadraditoUróborosSerendipiaÎncă nu există evaluări

- Apuntes para El Estudio de La Agri Cultura de Granada Y Su Tierra en Los Primeros Años de La ConquistaDocument18 paginiApuntes para El Estudio de La Agri Cultura de Granada Y Su Tierra en Los Primeros Años de La ConquistaeplajoscypqmcfeuekÎncă nu există evaluări

- Manual de Astrología BásicaDocument12 paginiManual de Astrología Básicamarcos3333Încă nu există evaluări

- Circuitos y Sistemas DigitalesDocument175 paginiCircuitos y Sistemas DigitalesCarlos Espinoza100% (11)

- TEMA 3 - Sistema CardiopulmonarDocument41 paginiTEMA 3 - Sistema CardiopulmonarRoberto Cruz ValenzuelaÎncă nu există evaluări

- Aula Historia Natural Del Cancer-1Document18 paginiAula Historia Natural Del Cancer-1luisÎncă nu există evaluări

- TEMA 4 - Los Sistemas de Coordinación y de RegulaciónDocument35 paginiTEMA 4 - Los Sistemas de Coordinación y de Regulaciónlobo2011Încă nu există evaluări

- Práctica 2-Toma de Signos VitalesDocument4 paginiPráctica 2-Toma de Signos Vitaleslobo2011Încă nu există evaluări

- Organización Básica Del Cuerpo Humano PDFDocument34 paginiOrganización Básica Del Cuerpo Humano PDFRoberto Cruz ValenzuelaÎncă nu există evaluări

- X - Respuesta Inmune EspecificaDocument3 paginiX - Respuesta Inmune Especificalobo2011Încă nu există evaluări

- Tema 6 - El Sistema InmunitarioDocument47 paginiTema 6 - El Sistema Inmunitariolobo2011Încă nu există evaluări

- Definicion de CancerDocument34 paginiDefinicion de Cancerlobo2011Încă nu există evaluări

- AstrologiaDocument756 paginiAstrologiadany_scribd89% (9)

- Astrología Cientifica Simplificada - Max HeidelDocument136 paginiAstrología Cientifica Simplificada - Max HeidelJessica Rubio100% (2)

- TEMA 5 - El Sistema LocomotorDocument37 paginiTEMA 5 - El Sistema Locomotorlobo2011Încă nu există evaluări

- Tema G-15Document12 paginiTema G-15lobo2011Încă nu există evaluări

- Conceptos Basicos de Biologia Molecular PDFDocument28 paginiConceptos Basicos de Biologia Molecular PDFAngelRamÎncă nu există evaluări

- Matematicas Aplicadas A La Biologia PDFDocument177 paginiMatematicas Aplicadas A La Biologia PDFdievdÎncă nu există evaluări

- 11 Bioquimica 1Document74 pagini11 Bioquimica 1dolomaniaÎncă nu există evaluări

- Introduccion A Biologia para PrincipiantesDocument18 paginiIntroduccion A Biologia para PrincipiantesPaulina LizzethÎncă nu există evaluări

- Celula PDFDocument24 paginiCelula PDFAndrea ChinchillaÎncă nu există evaluări

- 09 Protocolo ARP ICMPDocument5 pagini09 Protocolo ARP ICMPronnycamachoÎncă nu există evaluări

- Componentes de La Placa BaseDocument60 paginiComponentes de La Placa Basethesky36Încă nu există evaluări

- Arquitectura FluxDocument265 paginiArquitectura FluxrafaÎncă nu există evaluări

- Instalacion de SistemaDocument14 paginiInstalacion de SistemaEduard CruxxÎncă nu există evaluări

- Carta de Bienvenida PDFDocument1 paginăCarta de Bienvenida PDFskynet621Încă nu există evaluări

- Usando Linux para Arreglar Un USB RotoDocument20 paginiUsando Linux para Arreglar Un USB RotoBladimir MancíaÎncă nu există evaluări

- Introduccion A JSPDocument36 paginiIntroduccion A JSPNicolasÎncă nu există evaluări

- Edu Ciaa NXPDocument4 paginiEdu Ciaa NXPJuan NevilleÎncă nu există evaluări

- Mantenimiento Correctivo y Preventivo de Una PCDocument40 paginiMantenimiento Correctivo y Preventivo de Una PCShanira Lisset RamirezÎncă nu există evaluări

- Trabajo de Implementacion de Reloj DigitalDocument10 paginiTrabajo de Implementacion de Reloj DigitalKevin QuistialÎncă nu există evaluări

- s01 Tema Introducción Al MainframeDocument22 paginis01 Tema Introducción Al MainframealdoÎncă nu există evaluări

- J ToolbarDocument3 paginiJ ToolbarAlejandro JahueyÎncă nu există evaluări

- Ide MatlabDocument2 paginiIde MatlabJosue AlmeidaÎncă nu există evaluări

- Tutorial Crear y Aplicar Un Mapa de Des Plaza Mien To para Modelar TejasDocument10 paginiTutorial Crear y Aplicar Un Mapa de Des Plaza Mien To para Modelar TejasDiego Andres Giraldo GomezÎncă nu există evaluări

- Tratamiento Multimedia en Java Con JMF - Carlos Prades Del Valle PDFDocument32 paginiTratamiento Multimedia en Java Con JMF - Carlos Prades Del Valle PDFJosé Luis Haro VeraÎncă nu există evaluări

- La Computadora y Sus PartesDocument4 paginiLa Computadora y Sus PartesMango MoritaÎncă nu există evaluări

- Mod - 02 - Pagina Web de Activacion y Licenciamiento de BVMS - 061716Document24 paginiMod - 02 - Pagina Web de Activacion y Licenciamiento de BVMS - 061716FranciscoÎncă nu există evaluări

- Estructuras de Control VBADocument4 paginiEstructuras de Control VBAJosé Luis Barreto MoralesÎncă nu există evaluări

- Guia TP 2010Document78 paginiGuia TP 2010Gastón SivoriÎncă nu există evaluări

- EPE POO Ejercicio de Herencia PolimorismoDocument14 paginiEPE POO Ejercicio de Herencia PolimorismoAlex CruzÎncă nu există evaluări

- Clases 15-20 Unidad 4 Método SimplexDocument18 paginiClases 15-20 Unidad 4 Método SimplexLeticia TisnadoÎncă nu există evaluări

- Investigacion Documental Sobre Los Paradigmas de InvestigacionDocument16 paginiInvestigacion Documental Sobre Los Paradigmas de InvestigacionVictør RkøÎncă nu există evaluări

- Manual de Administración de Linux - Steve Shah PDFDocument655 paginiManual de Administración de Linux - Steve Shah PDFLorenzoVaniaÎncă nu există evaluări

- Optimizar Las Consultas en Visual BasicDocument6 paginiOptimizar Las Consultas en Visual BasicvarroasÎncă nu există evaluări

- PR Cticas de CySDocument3 paginiPR Cticas de CySEzequielÎncă nu există evaluări

- Desarrollo de Un Sistema de Alarma Contra Incendios Utilizando Raspberry Pi y Arduino UnoDocument8 paginiDesarrollo de Un Sistema de Alarma Contra Incendios Utilizando Raspberry Pi y Arduino UnoKevin Llanos0% (1)

- Códigos de Error de SQLDocument14 paginiCódigos de Error de SQLJoser Icard OrojoÎncă nu există evaluări

- Novia 7 Vs Esposa 1Document16 paginiNovia 7 Vs Esposa 1Novatin83100% (1)

- Mecanismos de SeguridadDocument12 paginiMecanismos de SeguridadAlbeleidyÎncă nu există evaluări

- Infraestructura Red y Servicios CIPFP MislataDocument99 paginiInfraestructura Red y Servicios CIPFP Mislatajribes7Încă nu există evaluări