Documente Academic

Documente Profesional

Documente Cultură

Assemble Ur

Încărcat de

ImAdDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Assemble Ur

Încărcat de

ImAdDrepturi de autor:

Formate disponibile

Langage machine : assembleur 8086

Eric

Eric

Garcia

Garcia

2002

2002

IUT GTR, Montbliard

Architectures des ordinateurs

Cours 4

Rfrences

Rfrences

http://lifc.univ-fcomte.fr/~teifreto/ASI-Cours/index.htm

http://icps.u-strasbg.fr/~vivien/Enseignement/Archi-2001-

2002/Cours.pdf

http://asi.insa-rouen.fr/enseignement/siteUV/se/cours.html

http://www-gtr.iutv.univ-paris13.fr/Equipe/viennet/Enseignement/

http://www.lifl.fr/~simplot/ens/archi/

http://worldserver.oleane.com/heissler

Plan

Plan

Architecture dun processeur Architecture dun processeur

Processeur 8086 Processeur 8086

Pile et Procdures Pile et Procdures

Systmes dexploitation et appels systmes Systmes dexploitation et appels systmes

Assembleur Assembleur

UAL : Rappel

UAL : Rappel

Unit charge

Des oprations arithmtiques :

ADD (+), SUB (-), MUL (*), DIV (:), INC (+ 1), DEC (- 1)

Des oprations logiques :

AND, OR, XOR, NOT, CMP

LSL, LSR, ASR (dcalages)

Architecture de

Architecture de

Von Neuman

Von Neuman

Chemin des donnes

Chemin des donnes

Les composants

Les composants

Registres

Adresse, Donne

INST, IP, SP , constantes (0, 1, ...), Registres A, B, C,

Registres tampons (TampA, TampB)

Registre des drapeaux de l'UAL (Flags)

2 Bus

Signaux de commande

Bus 1 : entre (RO), sortie (AI, TA, TB)

UAL : M (slection de Donne ou TampA), C (choix de

l'opration), FI (mise jour des Flags)

Bus 2 : sortie (DI I, RI)

Lecture/ criture : DI E , DO

Squencement

Squencement

des actions

des actions

Exemple :

Reg A Reg A + Reg B Signaux

Actions :

Transfert (Bus 1) Reg A Tamp A RO

10

, TA

Transfert (Bus 1) Reg B Tamp B RO

11

, TB

Choix UAL (C= 100, M= 0, Flags) C

2

C

1

C

0

,M, FI

Transfert (Bus 2) UAL Reg A RI

10

Une micro- instruction = ensemble des actions faisant fonctionner

une fois le chemin de donnes

- instruction

- instruction = 5 sous- cycles:

1. Transfert n 1 par le Bus 1

2. Transfert n 2 par le Bus 1

3. Opration UAL

4. Transfert rsultat par le Bus

2 (+ observation des FLAGS)

5. Accs la mmoire (READ

/ WRITE)

- programmes (1)

1. Faire laddition de 2 registres et mettre le rsultat dans lun des

deux

ex : IP IP + Reg1

10: TampA IP ; TampB Reg1 ; UAL TampA+ TampB ; IP UAL;

(signaux: RO

1

,TA ; RO

4

,TB ; C= 100 , M= 0 , FI ; RI

1

)

2. Faire des sauts conditionnels :

Conditions possibles = FLAGS en sortie de l UAL (Bus 2)

ex : Si RegA= 0 aller en 30

10: TampA RegA ; TampB . Reg0 ; UAL . TampA+ TampB; on ZF jmp 30 ;

(signaux: RO

10

,TA ; RO

3

,TB ; C= 100 , M= 0 , FI ; )

Il faut faire une opration pour calculer ZF mais UAL TampA n en est pas une

- programmes (2)

3. Envoyer le contenu dune case mmoire dadresse XX dans un

registre : (Hypothse: ladresse XX est dans un autre registre)

ex : RegA [RegB]

il faut commencer par mettre RegB dans Adresse et dclencher une

opration de lecture (Un accs la mmoire (READ / WRITE) prend 2

cycles)

10: Adresse RegB ; ; ; ; READ

(signaux: AI , TB ; ; ; ; DI

E

)

11: ; ; ; ; READ

la valeur est ensuite disponible dans Donne . Pour l envoyer dans un

autre registre, il faut passer par l UAL

12: ; ;UAL Donne ; RegA UAL ;

(signaux: ; ; C= 001, M= 1 ; RI

10

)

Optimisation

Occuper les bus le + possible :

ex : RegA [RegB]

10: Adresse RegB ; ; ; ; READ

11: ; ; ; ; READ

12: ; ; UAL Donne ; RegA UAL ;

IP IP + Reg1

13: TampA IP ; TampB Reg1; UAL TampA+ TampB; IP UAL;

Ici, on peut faire les 2 oprations en mme temps

10: Adresse RegB ; ; ; ; READ

11: TampA IP ; TampB Reg1 ; UAL TampA+ TampB ; IP UAL ; READ

12: ; ; UAL Donne ; RegA UAL ;

Lunit de commande

Lunit de commande excute les oprations suivantes :

Lecture du code de lopration

Lecture des arguments

Traitement

Sauvegarde du rsultat

Passage linstruction suivante

-programme de lecture du code de lopration (lopration

effectuer est en mmoire ladresse IP)

- lecture de l opration

0: Adresse IP ; ; ; ; READ

- on en profite pour passer la case mmoire suivante

1: TampA IP ; TampB Reg1 ; UAL TampA+ TampB ; IP UAL ; READ

- excution du -programme correspondant lopration

2: ; ; UAL Donne ; INST UAL, jmp -Prog[ INST];

Exemple 1

Add RegA, XX (RegA RegA + [XX])

1. L UC lit le codop de Add RegA dans la mmoire et dclenche le -

programme correspondant (0: 1: 2:)

2. Excution du -programme[ Add RegA, XX]

2. 1 : Lecture de largument XX en mmoire

lecture de la valeur XX en mmoire (INST [IP])

lecture de la valeur situe ladresse XX (Donne [INST])

2.2 : Traitement de lopration (RegA RegA + Donne)

2.3 : Sauvegarde du rsultat

2.4 : Passage l instruction suivante (IP IP + 1)

Exemple 1: code

- lecture de l opration

0: Adresse IP ; ; ; ; READ

- on en profite pour passer la case mmoire suivante

1: TampA IP ; TampB Reg1 ; UAL TampA+ TampB ; IP UAL ; READ

- excution du -programme correspondant lopration

2: ; ; UAL Donne ; INST UAL, jmp -Prog[ INST];

- lecture de la valeur de XX en mmoire

20: Adresse IP ; ; ; ; READ

21: TampA IP ;TampB Reg1 ; UAL TampA+ TampB ; IP UAL ; READ

22: ; ; UAL Donne ; INST UAL ;

- lecture de la valeur situe ladresse XX

23: Adresse INST ; ; ; ; READ

24: ; ; ; ; READ

Traitement de lopration (RegA RegA + Donne)

25: ; TampPRegA ;UAL Donne+TampB ;RegA UAL, jmp 0

;

Exemple 2

JZ xx (va en IP+ xx+ 1 si le rsultat de l UAL est nul)

1. L UC lit le codop de J Z dans la mmoire et dclenche le -

programme correspondant (0: 1: 2:)

2. Excution de -programme[ J Z XX]

2. 1 : Lecture de l argument XX en mmoire (Donne [IP])

2. 2 : Traitement de l opration (Test sur ZF, IP IP+ 1+ xx)

(2.3 : Sauvegarde du rsultat)

2. 4 : Passage l instruction suivante si la condition n est pas

ralise

Exemple 2 : code

1. L UC lit le codop de J Z dans la mmoire et dclenche le -

programme correspondant (0: 1: 2:)

0: Adresse IP ; ; ; ; READ

1: TampA IP ; TampB Reg1 ; UAL TampA+ TampB ; IP UAL ; READ

2: ; ; UAL Donne ; INST UAL, jmp -Prog[ INST];

2. Excution de -programme[ J Z XX]

2. 1 : Lecture de l argument XX en mmoire (Donne [IP])

2. 2 : Traitement de l opration (Test sur ZF, IP IP+ 1+ xx)

(2.3 : Sauvegarde du rsultat)

2. 4 : Passage l instruction suivante si la condition n est pas

ralise

30: Adresse IP ; ; ; on ZF jmp 32 ; READ

31: TampA IP ; TampB Reg1 ; UAL TampA+ TampB ; IP UAL, jmp 0 ;

32: TampA IP ; TampB Reg1 ; UAL TampA+ TampB ; IP UAL ; READ

33: ; TampB IP ; UAL Donne+ TampB ; IP UAL, jmp 0 ;

Code opration : assembleur

Programme en langage machine 80486 implant ladresse mmoire

0100H

A1 01 10 03 06 01 12 A3 01 14

Ce programme additionne le contenu de deux cases mmoire et range le

rsultat dans une troisime

Voici une transcription langage symbolique du programme complet.

L'adresse de dbut de chaque instruction est indique gauche (en

hexadcimal).

Adresse Contenu MP Langage Symbolique Explication en francais

0100 A1 01 10 MOV AX, [0110] Charger AX avec le contenu

de 0110.

0103 03 06 01 12 ADD AX, [0112] Ajouter le contenu de 0112

a AX (resultat dans AX).

0107 A3 01 14 MOV [0114],AX Ranger AX en 0114.

Code opration : assembleur

Symbole Code Op. Octets

MOV AX, valeur B8 3 AX valeur

MOV AX, [ adr ] A1 3 AX contenu de l'adresse adr.

MOV [ adr ], AX A3 3 range AX l'adresse adr.

ADD AX, valeur 05 3 AX AX +valeur

ADD AX, [ adr ] 03 06 4 AX AX +contenu de adr.

SUB AX, valeur 2D 3 AX AX - valeur

SUB AX, [ adr ] 2B 06 4 AX AX - contenu de adr.

SHR AX, 1 D1 E8 2 dcaleAX droite.

On utilise des programmes spciaux, appels assembleurs,

pour traduire automatiquement le langage symbolique en code

machine.

Fonctionnement de lUC

L UC possde un registre spcial pour stocker la -instruction

en cours

Autre reprsentation (1)

Autre reprsentation (2)

Fonctionnement de lUC

A partir du registre de -instruction, il faut gnrer les signaux

de commande de lUAL dans un ordre prcis

Squencement des oprations

Chaque partie de -INST est relie un DCD (ou un DMX) qui

dclenchera le bon signal de commande, au bon moment :

Ex : R3 = registre destination de la sortie de lUAL par le Bus 2

(DI I , RI 0 RI 15 )

Signal dhorloge CK

CK i = Sous- cycles de CK correspondants aux sous-cycles

des -instructions

Une frquence d'horloge d'un microprocesseur 500MHz

donne des cycles lmentaires de 2 nanosecondes.

Schma de lunit de commande

Schma de lunit de commande

Lorsquune instruction arrive dans RI, son Codop est envoy

dans une table de conversion qui indique ladresse du -

Programme correspondant.

Ce -Programme est excut ligne par ligne : chaque -

instruction est envoye dans le registre de -instruction o

sont gnrs squentiellement les signaux de commande de l

UAL

Schma

MMI, RMI et MCO

MMI ou mmoire de micro-instructions = lment central de la

logique de contrle

RMI (son registre associ) contient une micro instruction (tps t)

La MMI, gnralement une mmoire morte, contient toutes les

micro-instructions qui sont ncessaires au processeur pour

excuter les instructions du langage machine.

MCO, ou compteur ordinal du microprogramme : Il s'agit d'un

registre qui contient l'adresse de la prochaine micro instruction

excuter c'est--dire celle qui doit tre place dans le RMI,

seul lieu o une micro instruction peut agir sur le circuit de

donnes.

Niveaux de programmation

Technologies de processeurs

CISC (Intel 8086, Pentium, Motorola)

Complex Instruction Set Computer : calculateur jeu d'instructions

complexe. Caractrise les microprocesseurs qui disposent d'un jeu

tendu d'instructions avec de nombreux modes d'adressage. La plupart

ne sert que dans des cas relativement rares. Ces instructions complexes

ncessitent d'tre micro-codes et s'excutent donc en plusieurs cycles.

RISC : IBM/Motorola (PowerPC),SUN (Supersparc), DIGITAL (Alpha)

Reduced Instruction Set Computer : calculateur jeu d'instructions

rduit. En utilisateur un jeu d'instructions plus rduit que la technologie

CISC, les processeurs RISC peuvent disposer d'un jeu d'instructions

entirement cabl (donc sans microcode) ce qui permet une excution

des instructions en un cycle.

La mmoire cache

Depuis pas mal d'annes, les circuits de mmoire ne sont plus

assez rapides pour suivre la cadence des microprocesseurs

on intercale entre le microprocesseur et la mmoire RAM, une autre

mmoire allant la mme vitesse que le microprocesseur

celle-ci est de taille assez rduite car elle cote bien plus cher que la

mmoire RAM standard

souvent, il y a deux caches, un pour le programme et un pour les

donnes

Augmentation de la taille des bus dadresses et de donnes

Le micro-processeur est aliment plus vite

Bus dadresse 32 ou 64 bits = architecture 32 ou 64 bits

Le cache

processeur cache

80386 0

80486 1 cache interne 8Ko

pentium 1 cache interne donne 8 Ko et 1 cache interne instructions 8 Ko

pentium2 1 cache interne donne 16 Ko et 1 cache interne instructions 16 Ko

1 cache externe 256 Ko commun au 2 caches internes

pentium3 1 cache interne donne 16 Ko et 1 cache interne instructions 16 Ko

1 cache externe 256 Ko commun au 2 caches internes

Le Pipeline

Un pipeline est compos de plusieurs tages

chacun de ces tages est ddi un traitement particulier

Dans un processeur sans pipeline, les instructions sont

excutes les unes aprs les autres

il ne rentrera une nouvelle instruction dans le pipeline que lorsque

l'instruction prcdente est passe par tous les tages et est termine

le processeur n'utilise qu'un seul tage la fois, donc les autres

tages sont inactifs.

Avec un processeur 5 tages sans pipeline

Le Pilpeline

But : utiliser tous les tages en mme temps

lorsqu'une instruction est dans un tage, 4 autres instructions sont

en cours de traitement.

grce au dbit de la mmoire cache de niveau 1 les instructions

peuvent s'enchaner suffisamment vite pour que le pipeline soit

constamment aliment.

Processeurs superscalaires

Un microprocesseur est de type superscalaire quand il intgre

plus d'une unit entire (ALU) en con cur.

les deux units sont indpendantes et fonctionnent en parallle,

chacune se charge d'excuter une instruction sur deux.

Il est ainsi possible d'excuter deux instructions par cycle d'horloge.

Coprocesseurs mathmatiques

J usqu'au 386, celui-ci tait parfois assist par un coprocesseur

mathmatique optionnel permettant d'accrotre les capacits de

calcul en virgule flottante (trs

utilis par les tableurs et les logiciels de traitement graphique).

Aujourdhui, ce coprocesseur fait partie intgrante du CPU.

Efficacit architecturale

Croissance du nombre dinstructions excutes par cycle

dhorloge

Processeur

Nb d'i nstructi ons

par cycl e d'horl oge

i386 1/8

i486 1/2

Pentium 1

Pentium Pro 1,5

P4 2,5

Plan

Plan

Architecture dun processeur Architecture dun processeur

Processeur 8086 Processeur 8086

Pile et Procdures Pile et Procdures

Systmes dexploitation et appels systmes Systmes dexploitation et appels systmes

Assembleur Assembleur

Processeurs 80x86

Micro-processeurs 80x86 quipent les PC et compatibles

Premiers PC (dbut 80) = 8086, micro-processeur 16 bits

Puis 80286, 80386, 80486, Pentium

Augmentation de la frquence dhorloge, de la largeur des bus

dadresses et de donnes

Ajout de nouvelles instructions et de registres

Compatibilit ascendante

Un programme crit dans le langage machine du 286 peut

sexcuter sur un 386 (linverse est faux)

En TP on utilisera un assembleur 8086 et on excutera le

programme sur les Pentium de lIUT

Caractristiques du 8086

Bus de donnes : 16 bits

Bus dadresse : 20 bits

Registres : 16 bits

4 accumulateurs 16 bits

Accumulateur (AX)

Base (BX)

Counter (CX)

Accumulateur auxiliaire (DX)

Registres accessibles sous forme de 2 info 8 bits

AX se dcompose en AH (poids fort) et AL (poids faible de

AX)

Caractristiques du 8086

4 accumulateurs 16 bits

AX, BX, CX ,DX

Registres dindex :

Pointeur dinstruction (IP)

Index source ou destination(SI, DI)

Pointeur de Pile ou de base (SP, BP)

3+1 registres segment :

Segment de code (CS) : contient le prog en cours dexcution

Segment data (DS) : contient les donnes du programme

Segment stack (SS) : contient des donnes particulires

Extra Segment (ES)

Segmentation de la mmoire

Largeur du bus dadresse = 20 bits

Possibilit dadressage mmoire = 2

20

= 1 Mo

Le pointeur dinstruction fait 16 bits

Possibilit dadresser 2

16

= 64 Ko (ce qui ne couvre pas la mmoire)

On utilise deux registres pour indiquer une adresse au processeur

Chaque segment dbute l'endroit spcifi par un registre spcial

nomm registre segment.

Le dplacement permet de trouver une information l'intrieur du

segment.

CS:IP : lecture du code dune instruction (CS registre segment et IP

dplacement)

DS : accs aux donnes (MOV AX,[1045] = lecture du mot mmoire

dadresse DS:1045H)

Segmentation de la mmoire

Registres de dplacement = slectionner une information dans un

segment.

Dans le segment de code CS : le compteur de programme IP joue

ce rle. CS:IP permet d'accder une information dans le segment

de code.

Dans les segments de DS : les deux index SI ou DI jouent ce rle.

Le dplacement peut tre aussi une constante. DS:SI ou DS:DI

permettent d'accder une information dans le segment de

donnes.

Dans le segment de pile SS le registre SP (stack pointer) et BP

(base pointer) jouent ce rle. SS:SP ou SS:BP permettent d'accder

une information dans le segment de pile.

J eu dinstruction (1)

Instruction daffectation : MOV

(Transfert CPU Mmoire)

Instructions arithmtiques : INC (incrmentation)

(Opration Acc / Donne) : DEC (dcrementation)

: ADD (addition)

: SUB (soustraction)

: CMP (soustraction sans

sauvegarde)

: NEG

Instructions logiques : NOT, OR, XOR

: AND, TEST (= AND sans

sauvegarde)

: SHL (SHR), SAL (SAR)

: ROL (ROR), RCL (RCR)

J eu dinstruction (2)

Branchement : J MP

Branchements conditionnels : J E/ J Z (J NE/ J NZ) : J ump if

zero

: J O (J NO) : J ump if overflow

: J S (J NS) : J ump if sign

Comparaison de valeurs

CMP AX, BX suivi d un test :

(entiers naturels) (complment 2)

AX > BX ? J A ( >= J AE) J G (J GE)

AX < BX ? J B (J BE) J L (J LE)

Branchements

Le processeur excute une instruction en mmoire puis passe

celle qui suit en mmoire : squentiel

Besoin de faire rpter au processeur une suite dinstructions

Besoin de dclencher une action qui dpend dun test

Utilisation dune instruction de branchement ou saut

On indique au processeur ladresse de la prochaine instruction

On distingue deux catgories de branchements

le saut est toujours effectu (sauts inconditionnels)

il est effectu seulement si une condition est vrifie (sauts

conditionnels).

Rappel sur le registre IP

Le registre IP du processeur conserve l'adresse de la prochaine

instruction excuter

Le processeur effectue les actions suivantes pour chaque

instruction :

1. lire et dcoder l'instruction l'adresse IP;

2. IP IP + taille de l'instruction;

3. excuter l'instruction.

Pour modifier le droulement normal d'un programme

l'excution de l'instruction doit modifier la valeur de IP

c'est ce que font les instructions de branchement.

Sauts inconditionnels

Principale instruction de saut inconditionnel = JMP

L'oprande de J MP est un dplacement, c'est dire une valeur

qui va tre ajoute IP. L'action effectue par JMP est :

IP = IP + dplacement

Le dplacement est un entier relatif sur code 8 bits. La valeur du

dplacement est :

dplacement = adr. instruction vise - adr. instruction suivante

Sauts inconditionnels : exemple

Exemple : le programme suivant crit indfiniment la valeur 0

l'adresse 0140H.

La premire instruction est implante l'adresse 100H.

Adresse Contenu MP Langage Symbolique Explication en franais

0100 B8 00 00 MOV AX, 0 met AX a zro

0103 A3 01 40 MOV [140], AX crit l'adresse 140

0106 EB FC JMP 0103 branche en 103

0107 xxx -> instruction jamais excute

Le dplacement est ici gal FCH, c'est dire -4 (=103H-107H).

Indicateurs

Les instructions de branchement conditionnels utilisent les

indicateurs,

bits spciaux positionns par l'UAL aprs certaines oprations.

nous tudierons ici les indicateurs nomms ZF, CF, SF et OF.

ZF : Zero Flag

Cet indicateur est mis 1 lorsque le rsultat de la dernire opration

est zro. Sinon, ZF est positionn 0.

CF : Carry Flag

C'est l'indicateur de report (retenue). Il est positionn par les

instructions ADD, SUB et CMP (entiers naturels).

CF = 1 s'il y a une retenue

Indicateurs (suite)

SF : Sign Flag

SF est positionn 1 si le bit de poids fort du rsultat d'une addition ou

soustraction est 1; sinon SF=0. SF est utile lorsque l'on manipule des

entiers relatifs, car le bit de poids fort donne alors le signe du rsultat.

OF : Overflow Flag (Indicateur de dbordement)

OF=1 si le rsultat d'une addition ou soustraction donne un nombre qui

n'est pas codable en relatif dans l'accumulateur (par exemple si l'addition

de 2 nombres positifs donne un codage ngatif).

CMP = SUB, mais ne stocke pas le rsultat de la soustraction

(positionner les indicateurs)

CMP AX, 5 : ZF =1 si AX contient 5, et ZF =0 si AX 5.

Sauts conditionnels : exemples

JE Jump if Equal (ou J Z)

saut si ZF = 1;

JNE Jump if Not Equal (ou J NZ)

saut si ZF = 0;

JG Jump if Greater

saut si ZF = 0 et SF = OF;

JLE Jump if Lower or Equal

saut si ZF=1 ou SF = OF;

JS (JNS) Jump if Sign

saut si SF=1;

JA Jump if Above

saut si CF=0 et ZF=0;

JBE Jump if Below or Equal

saut si CF=1 ou ZF=1.

JB Jump if Below

saut si CF=1.

JO (J NO) Jump if Overflow

saut si OF=1

Dcalage et rotations

Dcalage vers la gauche ou vers la droite les bits de

l'accumulateur.

oprations utilises pour dcoder bit bit des donnes

ou pour diviser ou multiplier rapidement par une puissance de 2.

En effet : dcaler AX de n bits vers la gauche revient le multiplier

par 2

n

De mme, un dcalage vers la droite revient diviser par 2

n

.

Ces oprations peuvent oprer sur les registres AX ou BX (16

bits) ou sur les registres de 8 bits AH, AL, BH et BL.

SHL, SHR, ROL, ROR, RCL, RCR

Dcalage

SHL registre, 1 (Shift Left)

Dcale les bits du registre d'une position vers la gauche. Le bit de

gauche est transfr dans l'indicateur CF. Les bits introduits droite sont

zro.

SHR registre, 1 (Shift Right)

Comme SHL mais vers la droite. Le bit de droite est transfr dans CF.

SHL et SHR peuvent tre utilis pour multiplier/diviser des entiers

naturels (et non des relatifs car le bit de signe est perdu)

Rotations

ROL registre, 1 (Rotate Left)

Rotation vers la gauche : le bit de poids fort passe droite, et est aussi

copi dans CF. Les autres bits sont dcals d'une position.

ROR registre, 1 (Rotate Right)

Comme ROL, mais droite.

Dcalage et rotations

RCL registre, 1 (Rotate Carry Left)

Rotation vers la gauche en passant par l'indicateur CF. CF prend la place

du bit de poids faible; le bit de poids fort part dans CF.

RCR registre, 1 (Rotate Carry Right)

Comme RCL, mais vers la droite.

RCL et RCR sont utiles pour lire bit bit le contenu d'un registre

7

.

Oprations logiques

3 oprateurs logiques : ET, OU et OU exclusif.

jamais propagation de retenue lors de ces oprations (chaque bit du

rsultat est calcul indpendamment des autres)

Oprations sont de la forme : OR destination, source

destination : registre ou emplacement mmoire (adresse) o doit

tre plac le rsultat.

source : constante (adressage immdiat), registre (adressage

implicite), ou adresse (adressage direct).

OR AX, FF00 ; AX <- AX ou FFOO

OR AX, BX ; AX <- AX ou BX

OR AX, [1492] ; AX <- AX ou [1492]

Oprations logiques

OR destination, source (OU : 1 ou 0 =1 ; 1 ou 1 = 1)

OR est souvent utilis pour forcer certains bits 1. Par exemple

aprs OR AX, FF00, l'octet de poids fort de AX vaut FF, tandis que

l'octet de poids faible est inchang.

AND destination, source (ET : 1 et 1 = 1 )

AND est souvent utilis pour forcer certains bits 0. Aprs AND AX,

FF00, l'octet de poids faible de AX vaut 00, tandis que l'octet de

poids fort est inchang.

XOR destination, source (OU EXCLUSIF : 1 xor 1 = 0)

XOR est souvent utilis pour inverser certains bits. Aprs XOR AX,

FFFF, tous les bits de AX sont inverss

Codage

Les instructions et leurs oprandes (paramtres) sont stocks en

mmoire principale

La taille totale d'une instruction (nombre de bits ncessaires pour la

reprsenter en mmoire) dpend du type d'instruction et aussi du

type d'oprande.

Chaque instruction est toujours code sur un nombre entier

d'octets, afin de faciliter son dcodage par le processeur. Une

instruction est compose de deux champs :

le code opration, qui indique au processeur quelle instruction

raliser;

le champ oprande qui contient la donne, ou la rfrence une

donne en mmoire (son adresse).

Codage

Selon la manire dont la donne est spcifie, c'est dire selon

le mode d'adressage de la donne, une instruction sera code

par 1, 2, 3 ou 4 octets.

Nous distinguerons ici quatre modes d'adressage :

Implicite

immdiat

direct

relatif

Types dadressage

Adressage implicite ou par registre

ADD AX, BX

INC AX

Pas daccs mmoire pour les oprandes

L'instruction contient seulement le code opration, sur 1 ou 2 octets.

L'instruction porte sur des registres ou spcifie une opration sans

oprande

Types dadressage

Adressage immdiat

ADD AX, valeur

1 accs mmoire pour lire la valeur

Le champ oprande contient la donne (une valeur constante sur 1 ou 2

octets).

Exemple : ``Ajouter la valeur 5 AX''. Ici l'oprande 5 est code sur 2 octets

puisque l'opration porte sur un registre 16 bits (AX).

Types dadressage

Adressage direct

ADD AX, [adresse]

2 accs mmoire : adresse puis valeur

Le champ oprande contient l'adresse de la donne en mmoire

principale sur 2 octets.

Attention : dans le 80x86, les adresses sont toujours manipules sur 16

bits, quelle que soit la taille relle du bus.

Exemple : ``Placer dans AX la valeur contenue l'adresse 130H''.

Types dadressage

Adressage relatif ou index

ADD AX, [adresse+index]

MOV AX, [SI+1]

2 accs mmoire

Ce mode d'adressage est utilis pour certaines instructions de

branchement.

Le champ oprande contient un entier relatif cod sur 1 octet, nomm

dplacement, qui sera ajout la valeur courante de IP.

Plan

Plan

Architecture dun processeur Architecture dun processeur

Processeur 8086 Processeur 8086

Pile et Procdures Pile et Procdures

Systmes dexploitation et appels systmes Systmes dexploitation et appels systmes

Assembleur Assembleur

Code opration : assembleur

Programme en langage machine 80486 implant ladresse mmoire

0100H

A1 01 10 03 06 01 12 A3 01 14

Ce programme additionne le contenu de deux cases mmoire et range le

rsultat dans une troisime

Voici une transcription langage symbolique du programme complet.

L'adresse de dbut de chaque instruction est indique gauche (en

hexadcimal).

Adresse Contenu MP Langage Symbolique Explication en francais

0100 A1 01 10 MOV AX, [0110] Charger AX avec le contenu

de 0110.

0103 03 06 01 12 ADD AX, [0112] Ajouter le contenu de 0112

a AX (resultat dans AX).

0107 A3 01 14 MOV [0114],AX Ranger AX en 0114.

Code opration : assembleur

Symbole Code Op. Octets

MOV AX, valeur B8 3 AX valeur

MOV AX, [ adr ] A1 3 AX contenu de l'adresse adr.

MOV [ adr ], AX A3 3 range AX l'adresse adr.

ADD AX, valeur 05 3 AX AX + valeur

ADD AX, [ adr ] 03 06 4 AX AX + contenu de adr.

SUB AX, valeur 2D 3 AX AX - valeur

SUB AX, [ adr ] 2B 06 4 AX AX - contenu de adr.

SHR AX, 1 D1 E8 2 dcale AX droite.

On utilise des programmes spciaux, appels assembleurs,

pour traduire automatiquement le langage symbolique en code

machine.

Processus dassemblage

3 phases :

1. Saisie du code source avec un diteur de texte

2. Compilation du code source

3. dition des liens

permet de lier plusieurs codes objets en un seul

excutable

permet d inclure des fonctions prdfinies dans des

bibliothques

Assembleur : NASM

Assembleur : NASM

Val equ12

Var1 db69

Var2 dw0FFFFh

Tab resb100

[BITS 16]

[ORG 0x0100]

[SEGMENT .text]

BEGIN:

jmp START

FIN:

mov ax, 0x4C00

int 0x21

START:

mov [Var1], 3

jmp FIN

En

En

-

-

tte

tte

[BITS16] : indique au compilateur quon travaille en

mode 16 bits (programme DOS)

[ORG 0x100] : le programme est charg en mmoire

partir de ladresse 0x100h (programme .com)

[SEGMENT .text] : dclaration du segment dans lequel

on travaille, dans un programme .com : 1 seul segment

pour le code et les donnes

[int 0x20] : Interruption = appel systme pour rendre la

main au dos

Variables

Variables

DB : Variable 8 bits

DW: Variable 16 bits

EQU : Constante

RESB : Variable 8 bits (tableau)

RESW : Variable 16 bits (tableau)

BYTE : Taille d'une variable mmoire 8 bits

WORD : Taille d'une variable mmoire 16 bits

Etiquette : adresse dune mthode/ branchement

Reprsentation mmoire : .

Reprsentation mmoire : .

com

com

CS, DS, SS

Header DOS

100h

SP

Programme

Variables

IP

64 Ko

Fichier .

Fichier .

com

com

Un seul segment de 64 Ko pour les donnes le

programme et la pile

.exe : on peut avoir un segment pour chaque

Au dbut du programme

IP pointe sur ladresse 100h du segment (header DOS)

CS, DS, SS pointent au dbut

SP pointe la fin (tte de pile) : attention que votre pile

ncrase pas votre programme ou vos donnes

Exemple de programme NASM

Exemple de programme NASM

[BITS 16]

[ORG 0x100]

[SEGMENT .text]

mov AX,0x13

int 0x10

mov AX,0xA000

mov ES,AX

mov DI,6720

boucle:

mov byte [ES:DI],5

add DI,321

cmp DI,12000

jb boucle

int 0x20

Plan

Plan

Architecture dun processeur Architecture dun processeur

Processeur 8086 Processeur 8086

Pile et Procdures Pile et Procdures

Systmes dexploitation et appels systmes Systmes dexploitation et appels systmes

Assembleur Assembleur

Pile

Pile

Structure de rangement de donnes

dfinie dans un segment de mmoire particulier (.exe) ou

dans le mme que le code et les donnes (.com)

fonctionnement LIFO (Last In, First Out)

Comment y accder :

adresse du dernier lment pos : SS:SP

empiler : PUSH Reg16 (registre 16 bits)

dpiler : POP Reg16 (registre 16 bits)

La pile augmente vers les adresses faibles

PUSH : SP SP- 2, POP : SP SP+ 2

Pile : exemple dutilisation (1)

Pile : exemple dutilisation (1)

PUSH registre

empile le contenu du registre sur la pile.

POP registre

retire la valeur en haut de la pile et la place dans le registres

spcifi.

Exemple : transfert de AX vers BX en passant par la pile.

PUSH AX ; Pile <- AX

POP BX ; BX <- Pile

Note : cet exemple n'est pas trs utile, il vaut mieux employer

MOV AX, BX.)

Pile : exemple dutilisation (2)

Pile : exemple dutilisation (2)

La pile est souvent utilise pour sauvegarder

temporairement le contenu des registres :

;AX et BX contiennent des donnes a conserver

PUSH AX

PUSH BX

MOV BX, truc ; on utilise AX

ADD AX, BX ; et BX

POP BX ; rcupre l'ancien BX

POP AX ; et l'ancien AX

On voit que la pile peut conserver plusieurs valeurs.

La valeur dpile par POP est la dernire valeur empile;

c'est pourquoi on parle ici de pile LIFO (Last In First Out,

Premier Entr Dernier Sorti).

Pile : registres SS et SP

Pile : registres SS et SP

Le registre SS (Stack

Segment) = registre segment qui

contient l'adresse du segment de

pile courant (16 bits de poids fort

de l'adresse). Il est normalement

initialis au dbut du programme

et reste fix par la suite.

Le registre SP (Stack Pointer)

contient le dplacement du

sommet de la pile (16 bits de

poids faible de son adresse).

PUSH POP

SP

16 bits

Pile : registres SP

Pile : registres SP

L'instruction PUSH effectue les oprations suivantes :

SP SP - 2

[SP] valeur du registre 16 bits.

Notons qu'au dbut (pile vide), SP pointe ``sous'' la pile

L'instruction POP effectue le travail inverse :

registre destination [SP]

SP SP + 2

Si la pile est vide, POP va lire une valeur en dehors de

l'espace pile, donc imprvisible.

Pile : registres SP

Pile : registres SP

16 bits

Emplacement

libre

SP

SP-2

PUSH POP

Adresses

Croissantes

Procdures (1)

Procdures (1)

Dclaration dune procdure :

nous utiliserons une tiquette ou label pour dfinir le dbut et

le nom dune procdure

Appel de la procdure dans le programme

CALL NEAR label

...

CALL NEAR affiche

affiche :

MOV AH,9

INT 0x21

RETN

Procdures (2)

Procdures (2)

Comment lunit de traitement arrive-t-elle retourner au

programme principal la fin de la procdure ?

Au moment de lappel de la fonction, ladresse de

linstruction suivante est sauvegarde dans la pile :

sauvegarde de IP

A la fin de la procdure, l Unit de Traitement rcupre les

valeurs sauvegardes pour retourner au programme principal

RETN = dpilement de IP

Passage de paramtres

Passage de paramtres

2 mthodes de passage de paramtres :

par registre

par la pile

Passage de paramtres par registre :

les paramtres dentre de la procdure sont mis dans des

registres avant lappel de la procdure

les paramtres de sortie sont aussi rangs dans des

registres

avantage = rapidit

inconvnients = peu de registres

Passage par registre

Passage par registre

;Procdure

Moyenne :

Add AX, BX

SHR AX, 1

RETN

;programme principal

...

Mov AX, N1

Mov BX, N2

Call Near Moyenne

Mov Res, AX

...

Retn = dpilement de IP

pour retourner au

programme principal

Passage par la pile (1)

Passage par la pile (1)

Les paramtres dentre sont empils avant lappel de la

procdure

Les paramtres de sortie sont dpils par le programme

principal

avantage = portabilit

inconvnients = rcupration des

paramtres plus lourde

;Procdure

Moyenne :

PUSH BP

Mov BP, SP

Mov AX, [BP+4]

Add AX, [BP+6]

SHR AX, 1

Mov [BP+ 6], AX

POP BP

Retn 2

;programme

...

PUSH N1

PUSH N2

Call Near Moyenne

POP Res

...

Passage par la pile (2)

Passage par la pile (2)

volution de la pile

A quoi sert BP ?

BP = rfrence de la pile au dbut de la procdure

permet davoir une rfrence fixe pour rcuprer les

paramtres

ici : [BP+ 4] pour N2 et [BP+ 6] pour N1

Passage par la pile (3)

Passage par la pile (3)

Sauvegarde du rsultat et nettoyage de la pile

Rappels : Registres de segment

Rappels : Registres de segment

Nom Taille Fonction

Cs (Code Segment)16 bits Mmorise le segment o se trouve le code en

cours d'excution (ne peut pas tre modifi par

le programme)

Ds (Data Segment) 16 bits Mmorise le segment o se trouve les

donnes du programme.

Ss (Stack Segment)16 bits Mmorise le segment o se trouve la pile de

donnes du programme

Es (Extra Segment) 16 bits Ce segment peut tre utilis pour faire ce que

l'on veut. Par exemple, il peut pointer sur la

mmoire cran.

Rappels : Registres de travail

Rappels : Registres de travail

Nom Taille Fonction

Ax (Accumulateur) 16 bits On l'utilise gnralement pour des oprations

arithmtiques, telles que MUL (multiplication)

ou DIV (division). Ax peut se diviser en deux

sous-registres de 8 bits. Ah reprsente les 8

premiers bits, et Al les 8 derniers.

Bx (Base) 16 bits Bx est utilis lors de l'accs une zone

mmoire sous forme de tableau, il reprsente

l'indice de ce tableau. Par exemple, on crira

Mov Dx, Es:[Bx]. Bx peut se diviser en deux

sous-registres de 8 bits. Bh reprsente les 8

premiers bits, et Bl les 8 derniers.

Rappels : Registres de travail

Rappels : Registres de travail

Nom Taille Fonction

Cx (Compteur) 16 bits Lors de l'appel d'instructions comme REP

(rpter) ou LOOP (boucle), c'est le registre

Cx qui est lu Cx peut se diviser en deux sous-

registres de 8 bits. Ch reprsente les premiers

bits, et Cl les 8 derniers.

Dx (Donnes) 16 bits Ce registre est gnralement utilis pour

stocker des donnes provisoires. Dx peut se

diviser en deux sous-registres de 8 bits. Dh

reprsente les 8 premiers bits, et D les 8

derniers.

Rappels : Registres d'offset

Rappels : Registres d'offset

( combiner avec une adresse de segment)

Nom Taille Fonction

Si (Source Index) 16 bits Lors d'oprations sur les chanes de

caractres, comme MOVSB ou SCASB,

Ds:[Si] dsigne la variable 'source'.

Di (Dest Index) 16 bits Lors d'oprations sur les chanes de

caractres, comme MOVSB ou SCASB,

Es:[Di] dsigne la variable 'destination'.

Bp (Base Pointeur) 16 bits Bp a un rle proche de celui de Bx, mais il est

gnralement utilis avec le segment de pile

(Ss:[Bp]).

Rappels : Registres d'offset

Rappels : Registres d'offset

( combiner avec une adresse de segment)

Nom Taille Fonction

Ip (Instruction Point)16 bits Cs:[Ip] indique la prochaine instruction

excuter. Tout comme Cs, Ip ne peut tre

manipul par le programme excut.

Sp (Stack Pointeur) 16 bits Ss:[Sp] indique le dernier lment de la pile.

Chaque opration PUSH (empiler) ou POP

(dpiler) modifie le registre Sp.

Exemple de programme NASM

Exemple de programme NASM

[BITS 16]

[ORG 0x100]

[SEGMENT .text]

PILE PROC

Plan

Plan

Architecture dun processeur Architecture dun processeur

Processeur 8086 Processeur 8086

Pile et Procdures Pile et Procdures

Systmes dexploitation et appels systmes Systmes dexploitation et appels systmes

Assembleur Assembleur

Interprteur et compilateur (1)

Interprteur et compilateur (1)

On distingue grossirement deux familles de langages

informatique

les langages interprts

les langages compils

Un programme en langage interprt va tre traduit au fur et

mesure de son excution par un interprteur

interprteur : programme charg de dcoder chaque

instruction du langage et d'excuter les actions correspondantes

Programmes compils : traduction en langage machine a

lieu une fois pour toute.

Le compilateur (traducteur) traduit chaque instruction du

langage en une suite d'instructions en langage machine

Interprteur et compilateur (2)

Interprteur et compilateur (2)

Les programmes compils s'excutent ainsi plus rapidement

que les programmes interprts

La traduction est dj faite

Mais on perd en souplesse de programmation, car les types de

donnes doivent tre connus au moment de la compilation

Compilateur = traduit un programme source crit dans un

langage de haut niveau (C) en un autre programme dans un

langage de bas niveau (par exemple l'assembleur)

Opration de traduction complexe

Compilateurs = programmes sophistiqus

Principaux langages

Principaux langages

Les principaux langages compils sont :

C/C++ : programmation systme et scientifique

ADA : logiciels embarqus

Cobol : gestion

Fortran : calcul scientifique

Pascal : enseignement

Quelques langages interprts :

BASIC : bricolage

LISP, Prolog : Intelligence Artificielle

Python : programmation systme, Internet

J ava : applets internet

MATLAB : calcul scientifique

LISP, J ava ou Python : une premire phase de compilation vers un

langage intermdiaire (bytecode), qui sera lui mme interprt.

Compilation du C

Compilation du C

Traduction en assembleur des programmes en langage C

Le dtail de cette traduction (ou compilation) dpend

Compilateur utilis

Systme d'exploitation (DOS, Windows, UNIX,...).

Taille des types : exemple int (16 ou 32 bits)

Modle de mmoire utilis (pointeurs sur 16 ou 32 bits,

donnes et code dans des segments diffrents ou non, etc.)

Exemple : compilateur Turbo C++ version 3 sous DOS

(entiers de 16 bits et le modle de mmoire small )

Gnre directement du code objet (fichier .OBJ ) partir

d'un fichier source en langage C

Il est cependant possible de demander l'arrt de la

compilation pour obtenir du langage assembleur (fichier .ASM)

C et assembleur

C et assembleur

Introduction dinstructions assembleur dans des

programmes en langage C (ou C++).

Programme non portable, car le langage assembleur

diffre d'un type d'ordinateur l'autre

Pour un programme utilisant les ressources matrielles

d'une machine : plus confortable d'crire un programme C

contenant quelques lignes d'assembleur que de tout

crire en assembleur.

Exemple avec

Turbo C++/TASM

void main(void) {

int A = 20;

asm{

MOV AX, A

SHL AX, 1

}

printf(AX =%d\n,_AX);

}

Ce programme affiche 40.

Systme dexploitation

Systme dexploitation

OS : Operating System : le programme permettant

d'utiliser les circuits qui ont t cbls.

Soit entirement en ROM

Soit un code de boot en ROM se chargeant de placer en

RAM le reste de l'OS partir de la disquette ou du DD

Souvent, une ROM de boot contient nanmoins la partie

de l'OS la plus primitive: le BIOS.

But de l'OS = dcharger le programme des tches

rptitives et de bas niveau.

Gain de temps lors du dveloppement programmes

Pas se soucier du fonctionnement de la circuiterie

lectronique

Systme dexploitation

Systme dexploitation

Le systme dexploitation doit soccuper de :

l excution des commandes dentre/ sortie

la gestion de la mmoire

la gestion des fichiers

la multi- programmation ( multi- tche )

Comment excuter plusieurs programmes la fois ?

Et si ces programmes veulent tous accder l imprimante

en mme temps ?

Et sils doivent changer des informations ?

Comment excuter un seul programme avec plusieurs

processeurs ?

la scurit (gestion des accs,)

Le SE doit aussi fournir :

un langage de commande

divers utilitaires (compilateurs, diteurs, outils, )

une interface graphique pour lutilisateur

Systme dexploitation

Systme dexploitation

Windows 95/ 98, Windows NT (Microsoft) :

processeurs 80x86

OS/ 2 (IBM)

MacOS (Apple) :

processeurs 68000 puis PowerPC

UNIX = famille de SE :

Versions payantes gnralement spcialises un type

de machine :

SunOS/ Solaris (Sun)

AIX (IBM)

HP/ UX (HP)

Versions libres :

LINUX : 80x86, 68000, PowerPC, Sparc

Prsentation du BIOS

Prsentation du BIOS

BIOS (Basic Input Output System) : partie de l'OS du plus

bas niveau

oprations trs primitives: lecture du clavier, affichage cran en

mode texte, accs simplifi au lecteur de disquette et au disque

dur, accs au ports srie et parallle.

Le programme du BIOS se trouve en mmoire morte (ROM)

une mmoire gardant son contenu lorsque l'on interrompt son

alimentation lectrique

Chaque modle de PC est vendu avec une version du BIOS

adapt sa configuration matrielle.

Fonctions du BIOS

Fonctions du BIOS

BIOS librairie de fonctions

Chaque fonction effectue une tche bien prcise (par exemple

afficher un caractre donn sur l'cran)

L'appel de l'une de ces fonctions = appel systme

Fonctions du BIOS procdures appeles avec l'instruction

CALL

il a t prvu de pouvoir modifier le comportement du BIOS en

cours d'utilisation (par exemple pour grer un nouveau

priphrique)

Code du BIOS en ROM = non modifiable

Le BIOS tant diffrent d'un ordinateur l'autre, les adresses

des fonctions changent...

Vecteurs dinterruption (1)

Vecteurs dinterruption (1)

Problme rsolu par l'utilisation d'une table d'indirection = la

table des vecteurs d'interruptions

table est place en RAM : contient les adresses (en ROM ou en

RAM) des fonctions du BIOS

implante partir de l'adresse 00000000H (premire case

mmoire)

elle est initialise par le BIOS lui mme au moment du dmarrage

du PC (boot).

Adresse contenu

0000 adresse de la premire fonction du BIOS

0004 adresse de la deuxime fonction du BIOS

...

Vecteurs dinterruption

Vecteurs dinterruption

Chaque lment de la table occupe 4 octets (adresse 32 bits).

table 256 lments (1Ko).

exemple : si l'on sait que la fonction du BIOS qui affiche un

caractre est la 33ime, on va l'appeler en lisant la 33ime ligne de

la table, puis en allant excuter les instructions l'adresse trouve :

Adresse contenu

...

0084H F1234560H (car 4x33 = 84H).

...

La table des vecteurs d'interruptions contient des valeurs

diffrentes pour chaque version de BIOS

peut tre modifie pour pointer sur du code en mmoire

principale, modifiant alors le BIOS existant.

Interruptions

Interruptions

Unit de Traitement excute squentiellement les

instructions ou effectue des sauts programms (J MP,

CALL)

Il existe des situations o l U. T. est droute de

sa tche :

Reset : signal envoy au processeur pour un (re-)

dmarrage

Exceptions (interruptions internes) : dbordement de

pile, dpassement de capacit, div /0,

Appels systmes (int. logicielles) : appels du

programme lui- mme int 21h

Interruptions physiques (int. externes) : appels dautres

priphriques

Interruptions logicielles : INT n

Interruptions logicielles : INT n

L'instruction INT n permet d'appeler la n-ime

fonction de la table des vecteurs d'interruptions.

n est un entier compris entre 0 et 255 (1 octet), car il y a

256 vecteurs d'interruptions dans la table (ex: Int 21h )

L'instruction INT n est semblable l'instruction CALL

sauf que l'adresse de destination est donne par la table

des vecteurs d'interruptions

que les indicateurs sont automatiquement sauvegards

sur la pile.

ladresse de retour complte (32 bits) doit tre empile

car le traitant dinterruption nest pas ncessairement dans

le mme segment de code que le programme

Interruptions : droulement

Interruptions : droulement

Le droulement de INT n se passe comme suit :

1. sauvegarde les indicateurs du registre d'tat sur la pile

(les indicateurs sont regroups dans un mot de 16 bits);

2. sauvegarde CS et IP sur la pile;

3. CS et IP sont chargs avec la valeur lue l'adresse 4 n,

n tant le paramtre de INT. L'excution continue donc au

dbut du traitant d'interruption.

Interruptions : fonctionnement

Interruptions : fonctionnement

Lorsque linterruption est dclenche, l U. T. doit

excuter un bout de programme prcis : le traitant de

linterruption.

l U. T. doit savoir o se trouve l adresse (CS: IP) du traitant numro n

Cette information est stocke en mmoire (0000: 0000 0000: 03FFh)

Appels systme

Appels systme

Le systme DOS (Disk Operating System) repose sur le

BIOS,

il appelle les fonctions du BIOS pour interagir avec le matriel

Les fonctions du DOS s'utilisent comme celles du BIOS, via

des vecteurs d'interruptions

fonctionnalits de plus haut niveau que le BIOS (entres/sorties,

ouverture de fichiers sur disque, etc.)

Les fonctions du DOS s'appellent l'aide du vecteur 21H

La valeur du registre AH permet d'indiquer quelle est la fonction

que l'on appelle : MOV AH, numero_fonction INT 21H

fonction 4CH du DOS = terminer un programme et de revenir

l'interprteur de commandes DOS : MOV AH, 4CH INT 21H

Fonctions du BIOS

Fonctions du BIOS

INT Fonction

0 Division par 0 appel automatiquement lors de

div. par 0

5 Copie d'cran

10H cran gestion des modes vido

12H Taille mmoire

13H Gestion disque dur (initialiser, lire/crire secteurs)

14H Interface srie

16H Clavier (lire caractre, tat du clavier)

Fonctions du DOS

Fonctions du DOS

Numro Fonction

01H Lecture caractre met le code ascii lu dans AL

02H Affiche caractre code ascii dans registre DL

09H Affiche chane de car DX=adresse dbut chane,

termine par '$'

0BH Lit tat clavier met AL=1 si caractre, 0 sinon.

Ce programme lit un caractre au clavier et l'affiche en majuscule :

MOV AH, 01H ; code fonction DOS

INT 21H ; attente et lecture d'un caractre

AND AL, 11011111b ; passe en majuscule

MOV DL, AL ; MOV AH, 02H ; code fonction affichage

INT 21H ; affiche le caractre

Exemple

Exemple

Affichage d'un octet en binaire : afficher la valeur contenue dans un

registre 8 bits (BL).

L'ide est d'utiliser un masque BL AND 10000000 pour tester le bit de

gauche, et de dcaler BL gauche pour parcourir ainsi tous les bits.

movBL, 10 ; on teste leprogavec BL=10

movCX,8 ; compteur de boucle

masque: Test BL, 10000000b

J NZ bit1

bit0: MovDL,"0"

jmpaffiche

bit1: MovDL,"1"

affiche: movAH,2 ; affichage

int 21h

SHL BL,1

Loopmasque

fin:

movah,4Ch

int 21h

S-ar putea să vă placă și

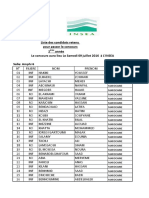

- Concours2016 2ème Ro IfDocument4 paginiConcours2016 2ème Ro IfImAdÎncă nu există evaluări

- Apprendre Le Langage HTMLDocument29 paginiApprendre Le Langage HTMLjaspe100% (1)

- JAVADocument4 paginiJAVAMelina MarineÎncă nu există evaluări

- Connexion BDDDocument1 paginăConnexion BDDImAdÎncă nu există evaluări

- SQL IgiDocument108 paginiSQL IgiImAdÎncă nu există evaluări

- Hibernate Reference 3.3.1Document348 paginiHibernate Reference 3.3.1jack11609Încă nu există evaluări

- StéganoDocument12 paginiStéganoImAdÎncă nu există evaluări

- Mastersem DsDocument5 paginiMastersem DsImAdÎncă nu există evaluări

- QCM 2005 CorrDocument3 paginiQCM 2005 CorrKawtar L AzaarÎncă nu există evaluări

- Fiche D Evaluation-1Document1 paginăFiche D Evaluation-1ImAdÎncă nu există evaluări

- Appel Candid MST 2Document2 paginiAppel Candid MST 2ImAdÎncă nu există evaluări

- Stri2016 5Document3 paginiStri2016 5ImAdÎncă nu există evaluări

- Partage CNXDocument1 paginăPartage CNXImAdÎncă nu există evaluări

- Assembleur I8086Document90 paginiAssembleur I8086Emna Ben HammoudaÎncă nu există evaluări

- Systéme D'exploitationDocument30 paginiSystéme D'exploitationKhSawÎncă nu există evaluări

- Cours Algo SDDocument149 paginiCours Algo SDImAdÎncă nu există evaluări

- Circuit Electrique en Regime ContinuDocument5 paginiCircuit Electrique en Regime ContinuImAdÎncă nu există evaluări

- Fiche Technique MIPDocument10 paginiFiche Technique MIPQmine LaaraisÎncă nu există evaluări

- SuitesDocument22 paginiSuitesZakaria AsbaiÎncă nu există evaluări

- TP 1Document8 paginiTP 1ImAdÎncă nu există evaluări

- Cours MecaniqueDocument43 paginiCours Mecaniqueerrairachid100% (2)

- TD2-Structure Interne TerreDocument1 paginăTD2-Structure Interne TerreImAdÎncă nu există evaluări

- Cours MecaniqueDocument43 paginiCours Mecaniqueerrairachid100% (2)

- Fic 00008Document5 paginiFic 00008ImAdÎncă nu există evaluări

- Cours MecaniqueDocument43 paginiCours Mecaniqueerrairachid100% (2)

- VTADocument89 paginiVTAImAdÎncă nu există evaluări

- Chimie en Solution MipDocument18 paginiChimie en Solution MipImAdÎncă nu există evaluări

- QCMDocument41 paginiQCMImAd67% (3)

- Cour de Chimie en SolutionDocument20 paginiCour de Chimie en SolutionIhsan Mokhlisse100% (28)

- ArduinoDocument16 paginiArduinoالفتى الخجولÎncă nu există evaluări

- FileDocument57 paginiFileAnonymous JIjLxKYApNÎncă nu există evaluări

- Chapitre 2 - La Programmation en AssembleurDocument17 paginiChapitre 2 - La Programmation en AssembleurHasintsoa rljÎncă nu există evaluări

- Modes AdressageDocument8 paginiModes AdressageEL AFOUÎncă nu există evaluări

- Cours+Exs AlgoDocument59 paginiCours+Exs AlgoMarcelin SoukroumdeÎncă nu există evaluări

- TD 1Document5 paginiTD 1EL AFOU67% (3)

- Archi PDFDocument241 paginiArchi PDFKinda Mia SalouaÎncă nu există evaluări

- 01 Cours JavaDocument10 pagini01 Cours JavaBrahim El GamaneÎncă nu există evaluări

- Cours Compilation ISIMS S1 PDFDocument45 paginiCours Compilation ISIMS S1 PDFSamy NaifarÎncă nu există evaluări

- Architectures Logicielles Et MatériellesDocument587 paginiArchitectures Logicielles Et Matériellesmehrez essafiÎncă nu există evaluări

- Correct !Document5 paginiCorrect !farok100% (2)

- Correction TD2 ArchitectureDocument8 paginiCorrection TD2 ArchitectureDhafer MezghaniÎncă nu există evaluări

- Cours 1 - IntroductionDocument18 paginiCours 1 - Introductionϟ KaiZyX ϟÎncă nu există evaluări

- Delphi Perfectionnement PDF FreeDocument50 paginiDelphi Perfectionnement PDF FreeGustavo CampanalesÎncă nu există evaluări

- TP21inf IndustrielDocument8 paginiTP21inf IndustrielWijdane GuradaÎncă nu există evaluări

- tp2 EnnonceDocument11 paginitp2 EnnonceKhawla mimiÎncă nu există evaluări

- Cours8 GIF1001 H12Document20 paginiCours8 GIF1001 H12Abdelhamid SaighiÎncă nu există evaluări

- AII Marocetude - Com Introduction Aux Microprocesseurs EXAMEN PRATIQUE 1Document7 paginiAII Marocetude - Com Introduction Aux Microprocesseurs EXAMEN PRATIQUE 1Oualid HarroudÎncă nu există evaluări

- SSTIC2017-French-Article-desobfuscation Binaire Reconstruction de Fonctions Virtualisees-Salwan Potet BardinDocument24 paginiSSTIC2017-French-Article-desobfuscation Binaire Reconstruction de Fonctions Virtualisees-Salwan Potet BardinJuliana PucciniÎncă nu există evaluări

- Cours 3A DEE MicroControleur PDFDocument21 paginiCours 3A DEE MicroControleur PDFDiavolo Rossonero del Milan100% (1)

- Part5 r1Document214 paginiPart5 r1ngt881Încă nu există evaluări

- Cours VBADocument37 paginiCours VBAImadeddine Grouh100% (1)

- Chapitre 3 Notions Sur Les Instruction de L'ordinateurDocument71 paginiChapitre 3 Notions Sur Les Instruction de L'ordinateuramal.benabdelghaffarÎncă nu există evaluări

- Structures de Don NeesDocument56 paginiStructures de Don NeesNakoniloh SoroÎncă nu există evaluări

- Cours Assembleur 8086 PDFDocument63 paginiCours Assembleur 8086 PDFالورود جنةÎncă nu există evaluări

- Les ShellcodesDocument11 paginiLes ShellcodesouestlechatdememeÎncă nu există evaluări

- ALMO Sujets TD TPDocument30 paginiALMO Sujets TD TPSonnySmithÎncă nu există evaluări

- Algorithmique Et Turbo-PascalDocument25 paginiAlgorithmique Et Turbo-PascalIbrahim RanaoÎncă nu există evaluări

- Langage D'assemblage Du MIPS R3000Document27 paginiLangage D'assemblage Du MIPS R3000Moujahed Gassoumi100% (2)

- Part 1 PDFDocument273 paginiPart 1 PDFAbdelhalim BoujemâaÎncă nu există evaluări