Documente Academic

Documente Profesional

Documente Cultură

CMOS Translinear Cells

Încărcat de

SumitChoudharyDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

CMOS Translinear Cells

Încărcat de

SumitChoudharyDrepturi de autor:

Formate disponibile

Proceedings of 2014 RAECS UIET Panjab University Chandigarh, 06 - 08 March, 2014

978-1-4799-2291-8/14/$31.00 2014 IEEE

A Digitally Controlled Floating Resistor Using

CMOS Translinear Cells

Priya Aggarwal

*

, Vandana mittal

*

, Mohammad A Maktoomi

*

, Mohammad S Hashmi

*

*Electronic Systems Group, IIIT Delhi, New Delhi, India

iRadio Lab, University of Calgary, Calgary, Alberta, Canada

Email: {priya13132, vandana13162, ayatullahm, mshashmi} @iiitd.ac.in

Abstract A CMOS based digitally controlled floating

resistor (DCFR) is proposed using translinear cells. The proposed

DCFR consists of two CMOS translinear cells along with a

CMOS current-division network (CDN). The proposed circuit is

designed in 0.35um technology and works at power supply of

1.6V. DCFR is analyzed as well as SPICE simulation along with

MATLAB is used to verify the proposed design. An application of

proposed DCFR is shown in a high pass filter.

Keywords CMOS; Floating resistance; Translinear

circuits; Current mode circuits; Current division network

I. INTRODUCTION

Passive resistor has high tolerance and large footprint on

chip; therefore there is lot of interest in their realization using

active elements [1]. Literature survey reveals that there are

two ways to realize such resistor: one is based on standard

blocks like operational trans-conductance amplifier (OTA),

current conveyor (CC) and differential difference current

conveyor (DDCC), etc [1-8], and other is their transistor level

design [9-14]. Making these resistors tunable adds flexibility

into the system employing them [1]. Since, in low voltage

design there is a limit on allowable tuning range; digital

control is a more attractive solution and is an active area of

research [15-19]. In this paper a new digitally controlled

CMOS floating resistor using two translinear cells is proposed.

A current division network (CDN) of [20] is used in

this paper to achieve digital control. It produces an output

current in accordance with the applied input bit pattern.

Translinear cell and current division network along with their

schematics are briefly discussed in Section II. In Section III,

the proposed DCFR is discussed. Results obtained using

LTspice and MATLAB appears in section IV.

II. BASIC CONCEPTS

A. CMOS Translinear Cell

Translinear circuit which was proposed by Barrie Gilbert

in 1975 [21], is one of the current mode circuits which is very

useful in analog circuits. It has been used in formation of

many circuits like in BJT based floating resistor [12], current

conveyor [2] etc. The current mode approach is frequently

used in many of the analog design.In translinear circuit

transconductance is linearly proportional to the external input

current [12]. This property has further been used to realize the

DCFR. Translinear circuit can be implemented with the help

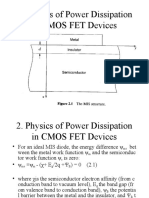

of bipolar junction transistors [21] or CMOS [22]. A

simplified structure of a CMOS translinear cell is shown in

Fig.1.

Fig. 1. CMOS translinear circuit

In this circuit M3-M4 - PMOS transistors and M1-M2 -NMOS

transistors are matched individually. All the transistors are

biased in their saturation region. Reference current I

o

provides the drain current to transistors M1 and M3. Whereas

the drain current of M2 and M4 is varied by i

x

which in turn

depends on the input difference voltage, v

xy

.

Since, equal DC current flows into M1 and M3,

0

y

i = (1)

A KCL at node B yields:

4 2 x

i i i = (2)

Since all MOSFETs are biased in saturation,

x

i is given by

[22]:

2

0

2

2

p p p p ox n n n n

x xy xy ox

p n p n

W W

C W W

i V V I C

L L L L

= + +

(3)

Where

n

and

p

are the electron and hole mobility,

respectively. / p p W L and / n n W L are the aspect ratios of

PMOS and NMOS matched transistors.

To remove the second order term in Eq. (2), the condition is:

p p n n

p n

W W

L L

=

(4)

Due to condition in (4), Eq.(3) will reduced to

0

2

p p

n n

x xy ox

p n

W

W

i V I C

L L

= +

(5)

This shows I-V characteristics of translinear cell is linear and

the linearity constant is known as transconductance which can

be formulated as:-

0

2

p p

x n n

m ox

xy p n

W

i W

g I C

v L L

= = +

(6)

It is to be noted from (6) that transconductance varies with the

input reference current

o

I .

B. Current Division Network (CDN)

CDN is similar in function to an R/2R or capacitive ladder

which is used to obtain binary weighted currents[23]. A MOS

based CDN has advantage of lesser chip area. CDN from

[20] is shown in the Fig.2 for reference.

Fig. 2. A 3-bit CDN [20]

CDN of Fig. 2 accept an input current I

in

and provides binary

weighted currents I

o1

and I

o2

, given by

1 o in

I I = (7)

2

(1 )

o in

I I = (8)

0

1

2

2

n

i

i n

i

a

=

=

(9)

The current I

in

is equally divided

into two halves one going

into the next cell and other going into the parallel MOS which

are controlled by the digital bits applied. Finally, the current

controlled by the digital bits is combined which gives one

current output named I

01

and similarly the current controlled

by complemented bits is combined and named as I

02

.

III. PROPOSED CMOS BASED DCFR

The proposed floating resistor appears in Fig. 3. It is

MOS version of its bipolar counterpart reported in [12].

Transistors M4-M7 and M10-M14 are the part of translinear

circuits. All the other transistors are part of current mirrors

which helps in injecting bias current I

b

in the translinear

circuit pair. V

12

is the differential input voltage. All the

transistors are in the saturation region. From symmetry of the

circuit:

1 2

i i = (10)

Also, from (6)

1 0 1 2

2 ( )

p p

n n

ox

p n

W

W

i I C v v

L L

= +

(11)

Hence from (10) and (11), the equivalent differential input

resistance is given by:

0

1

2

eq

p p

n n

ox

p n

R

W

W

I C

L L

=

+

(12)

Fig. 3. Proposed floating current controlled positive resistance using two

mixed translinear cell

From (12) it is obvious that resistance value may be easily

tuned with input bias current.

In order to make the proposed CMOS floating resistor

digitally controlled, a CDN network discussed in the previous

section is used as shown in the block diagram of Fig. 4. Since,

CDN has two outputs I

o1

and I

o2

, one of the outputs is

connected with the bias current terminal of the floating resistor

and other output is connected to ground as shown in the Fig. 5.

Fig. 4. Block diagram of DCFR

Fig. 5. Complete diagram of DCFR

IV. SIMULATION RESULTS

Aspect ratios of transistors in Fig. 3 appear in Table 1.

First, the floating resistor of Fig.3 is simulated using LTspice-

IV, which is a SPICE simulator provided by Linear

Technology. A 0.35um CMOS technology file has been used

for the simulation purpose. The power supply voltage V

dd

and

V

ss

are 1.6V and -1.6V, respectively. Biasing current, I

b

is

swept from 35A to 200A with a step of 25A. Fig.6 shows

the corresponding output which verifies the claim that realized

impedance may be tuned using the bias current.

TABLE I. ASPECT RATIOS OF THE PROPOSED CMOS DCFR

W/L ratio ( m / m ) Corresponding transistors

10/2 M1,M2,M8,M15

60/0.35 M6,M7,M11,M14

20/0.35 M4,M5,M10,M13

30/2 M3, M9,M12

Line which cuts the y axis at the highest point (near -80uA

y-mark) corresponds to I

b

=35A. For this value

transconductance (slope) is lowest among all which is also

evident from the mathematical result given in (12).

Fig. 6. I-V characteristic of proposed floating resistor

In order to show the digital control of the floating resistor,

circuit of Fig. 5 is simulated by keeping a fixed bias current of

200A. For all the transistors in CDN aspect ratio is W/L= 2.8

/0.7 in m . Fig. 7 shows the LTspice generated plot when

imported in MATLAB. According to three input bit patterns

different value of transconductance ( slope) are obtained

which greatly matches with the analytical result of (12).

-0.05 -0.04 -0.03 -0.02 -0.01 0 0.01 0.02 0.03 0.04 0.05

-3

-2

-1

0

1

2

3

x 10

-4

Differential input , v

1

-v

2

(in volt)

C

u

r

r

e

n

t

,

i

1

(

i

n

A

m

p

)

001

010

011

100

101

110

111

Fig. 7.Simulation showing I-V characteristics of circuit in Fig. 5 .

In order to show utility of the proposed DCFR, a first order

high pass filter shown in Fig. 8 is simulated in LTspice and

Fig. 9 shows the exported plot in MATLAB for various input

bit combinations [10, 15].

Fig. 8. A first order HPF employing the proposed DCFR

v

1

-v

2

i

1

=-i

2

Decreasing I

b

10

3

10

4

10

5

10

6

10

7

10

8

10

9

-100

-90

-80

-70

-60

-50

-40

-30

-20

-10

0

Frequncy (in Hz)

G

a

i

n

(

i

n

d

B

s

)

Fig. 9 Response of the HPF containing DCFR

The value of C1=10pF and bias current I

b

is fixed at

200uA. It is seen from Fig. 9 that for different applied bit

pattern, the value of R

eq

is changing and thus the cut-off

frequency of the filter.

V. CONCLUSION

A digitally controlled CMOS based DCFR was proposed

in this paper .The proposed circuit was realized using cascade

connection of CMOS translinear cell and CMOS ladder

current division network.. The proposed DCFR produces

different values of resistance in accordance with the applied

bit pattern for a given value of bias current. The proposed

circuit was verified with the help of LTspice and MATLAB

software. Finally, to show usefulness of the proposed idea a

first order high pass filter employing the DCFR was design

and verified.

REFERENCES

[1] E. Ozalevli, P.E .Hasler, A tunable floating gate CMOS resistor for

low- power and low voltage application, Procedings IEEE

International Symposium on Circuits and Systems(ISCAS), 2006 .

[2] Alain Fabre, Omar Saaid, Francis Wiest, and Christophe Boucheron

High Frequency Applications Based on A new Current Controlled

Conveyor IEEE Transactions On Circuits And Systems-I: Fundamental

Theory And Applications, Vol. 43, No. 2, February 1996

[3] Wandee Petchmaneelumka, Prasit Julsereewong, and Vanchai

Riewruja, Positive/Negative Floating Resistor Using OTAs,

International Conference on Control, Automation and Systems 2008.

[4] M. Kumngern, CMOS tunable positive/ negative floating Resistor

using OTAS, IEEE fourth international conference on Computational

Intelligence, Communication Systems and Networks(CICSyN),2012.

[5] M. Kumngern, Voltage Controlled floating resistor using differential

difference amplifier, IEEE international conference on Electrical

engineering and Informatics (ICEEI) ,2011.

[6] Montree KUMNGERN, Usa TORTEANCHAI, Kobchai DEJHAN,

Voltage-Controlled Floating Resistor Using DDCC Radioengineering,

vol. 20, no. 1, april 2011.

[7] H.O.Elwan ,A.M. Soliman ,Novel CMOS differential voltage current

conveyor and its applicationsIEE Proc -Circuits Devices SyJt , Vol 144,

No 3, June 1997.

[8] A.A. El-Adawy, A.M. Soliman and H.O. Elwan, Low-voltage digitally

controlled CMOS current conveyor, Int. J. Electron. Commun.

(AEU),vol.56, no.3, pp.137-144, 2002.

[9] Sezai Alper TEKN, Hamdi ERCAN , Mustafa ALI, Novel Low

Voltage CMOS Current Controlled Floating Resistor Using Differential

Pair Radioengineering, Vol. 22, No. 2, , pp. 428433, June 2013.

[10] Rishikesh PANDEY, Maneesha GUPTA, FGMOS Based Voltage-

Controlled Grounded Resistor Radioengineering, Vol. 19, No. 3, , pp.

428433, Sept 2010.

[11] Remzi Arslanalp, Erkan Yuce, Abdullah T. Tola, Low-component

count BJT technology-based current controlled tunable resistors and

their applications IET Circuits Devices Syst., 2013, Vol. 7, Iss. 1, pp.

2130.

[12] Raj Senani, Abdhes K. Singh and Vinod K. Singh, A new floating

current-controlled positive resistance using mixed translinear cells,

IEEE Transactions on circuits and systems -II, express briefs ,vol. 51,

No.7, July 2004.

[13] E. Ozalevli, P.E .Hasler, Design of a CMOS floating- gate resistor for

highly linear amplifier and multiplier applications, Procedings IEEE

Custom integrated Circuits Conference , 2005.

[14] Sompong Wisetphanichkij, Atiporn Binthawihok and Kobehai Dejhan,

A New Adjustable Grounded/Floating Resistance Circuit with Enhanced

Dynamic Range Based on Mixed-Translinear Loops , Proceedings of

ISCIT2005.

[15] Mohd. Samar Ansari, Multiphase sinusoidal oscillator with digital

control, in Proc. International Conference on Power, Control and

Embedded Systems (ICPCES-2010), Allahabad., 2010.

[16] Danucha PRASERTSOM , Worapong TANGSRIRAT , Wanlop

SURAKAMPONTORN, Low-Voltage Digitally Controlled Current

Differencing Buffered Amplifier 2008 IEEE.

[17] Soliman A. Mahmoud, Low Voltage High Current Gain CMOS

Digitally Controlled Fully Differential CCII 2005 IEEE.

[18] Hussain A. Alzaher, A CMOS Highly Linear Digitally Programmable

Active-RC Design Approach IEEE TRANSACTIONS ON CIRCUITS AND

SYSTEMS-----I: REGULAR PAPERS, VOL. 58, NO. 11, NOVEMBER 2011

[19] S. A. Mahmoud, M. A. Hashiesh, A. M. Soliman, Low voltage digitally

controlled fully differential current conveyor.,IEEE Trans. on Circuits

and Systems I, 2005, vol. 52, p. 2055-2064.

[20] Soliman Mahmoud, Eman Soliman, Novel CCII-based Field

Programmable Analog Array and its Application to a Sixth-Order

Butterworth LPF Radioengineering, VOL. 22, NO. 2, JUNE 2013.

[21] B. Gilbert, Translinear circuits: A proposed classification,

Electron.Lett., vol. 11, pp. 14-- -16, 1975.

[22] Roungsan Chaisricharoen, Boonruk Chipipop,BoonchareonSirinaovakul,

CMOS CCCII: Structures,characteristics,and considerations, Int. J.

Electron. Commun. (AE) 64 (2010) 540557.

[23] Tuna B.Tarim and Mohammed Ismail, Statistical Design of a 10 bit

Current Division Network,Analog integrated Circuits and Signal

processing , 29, 221-229, 2001 Kluwer Academic Publishers.

Manufactured in the Netherlands.

S-ar putea să vă placă și

- CMOS PortDocument46 paginiCMOS PortZali100% (1)

- Level Shifter PDFDocument6 paginiLevel Shifter PDFKAMARUDHEEN KPÎncă nu există evaluări

- Lecture 12 SRAMDocument37 paginiLecture 12 SRAMSachin MalikÎncă nu există evaluări

- Ec1401 Vlsi DesignDocument18 paginiEc1401 Vlsi DesignChaitanya PrabhuÎncă nu există evaluări

- LC Ladder Matching NetworksDocument33 paginiLC Ladder Matching NetworksCarriceiros TourÎncă nu există evaluări

- Fully Differential CMOS Voltage AmplifierDocument16 paginiFully Differential CMOS Voltage AmplifierAjit Narwal0% (1)

- Design High Speed, Low Noise, Low Power Two Stage CMOSDocument5 paginiDesign High Speed, Low Noise, Low Power Two Stage CMOSsanjeevsoni64Încă nu există evaluări

- Ansoft Designer Harmonic BalanceDocument9 paginiAnsoft Designer Harmonic BalanceAbdul Kadir Ramos FaisalÎncă nu există evaluări

- CMFB DesignDocument4 paginiCMFB Designaminkhan83Încă nu există evaluări

- Design of High Speed & Power Optimized Sense Amplifier Using Deep Nano CMOS VLSI TechnologyDocument8 paginiDesign of High Speed & Power Optimized Sense Amplifier Using Deep Nano CMOS VLSI TechnologyIJRASETPublicationsÎncă nu există evaluări

- CMOS Design RulesDocument21 paginiCMOS Design Rulesrakheep123Încă nu există evaluări

- Ee 215 ADocument8 paginiEe 215 AArjun Singhal100% (1)

- Eric Thesis SlidesDocument43 paginiEric Thesis SlidesHumberto JuniorÎncă nu există evaluări

- EC2 Exp2 F09Document17 paginiEC2 Exp2 F09Nurul Hanim HashimÎncă nu există evaluări

- Willson MirrorDocument7 paginiWillson Mirrorsandeep_mastiÎncă nu există evaluări

- Design of A Fully Differential High-Speed High-Precision AmplifierDocument10 paginiDesign of A Fully Differential High-Speed High-Precision Amplifierkirkland1337Încă nu există evaluări

- Mod1VLSI TECHNOLOGY1Document65 paginiMod1VLSI TECHNOLOGY1Jomon VargheseÎncă nu există evaluări

- Preventing Latch Up - NationalDocument2 paginiPreventing Latch Up - Nationalkvpk_vlsiÎncă nu există evaluări

- Performance Analysis of A Low-Power High-Speed Hybrid 1-Bit Full Adder Circuit Using Cmos Technologies Using CadanceDocument8 paginiPerformance Analysis of A Low-Power High-Speed Hybrid 1-Bit Full Adder Circuit Using Cmos Technologies Using CadanceAnonymous kw8Yrp0R5r100% (1)

- Self Biased High Performance Folded Cascode Cmos OpampDocument6 paginiSelf Biased High Performance Folded Cascode Cmos OpampArvind MishraÎncă nu există evaluări

- Analysis of Sense Amplifier Circuit Used in High Performance & Low Power SramDocument5 paginiAnalysis of Sense Amplifier Circuit Used in High Performance & Low Power SramGJESRÎncă nu există evaluări

- Amplifier Project GradDocument5 paginiAmplifier Project Gradمحمد قاسم نفل سميرÎncă nu există evaluări

- Level 54 Bsim4Document13 paginiLevel 54 Bsim4Georgios SarrisÎncă nu există evaluări

- Cmos Two Stage OpamppublishedDocument5 paginiCmos Two Stage Opamppublisheddeepak pandeyÎncă nu există evaluări

- Two-Stage Operational Amplifier Design Using Gm/Id MethodDocument7 paginiTwo-Stage Operational Amplifier Design Using Gm/Id Methodabhinav kumarÎncă nu există evaluări

- MIM Cap ModelDocument4 paginiMIM Cap ModelDuc DucÎncă nu există evaluări

- A Seminar Report On Vlsi FloorplanningDocument17 paginiA Seminar Report On Vlsi FloorplanningPARAG100% (1)

- Principles of Electronic Communication Systems: Third Edition Louis E. Frenzel, JRDocument25 paginiPrinciples of Electronic Communication Systems: Third Edition Louis E. Frenzel, JRDave DemoritoÎncă nu există evaluări

- Vlsi Design Test and TestabilityDocument17 paginiVlsi Design Test and TestabilitySuravarapu ArunaÎncă nu există evaluări

- MMIC Design, Part 2 - ProcessingDocument23 paginiMMIC Design, Part 2 - ProcessingVishal IyerÎncă nu există evaluări

- Design of Two-Stage Operational Amplifier: Shahin Shah (12116053), Abhinav Singhal (12116001)Document2 paginiDesign of Two-Stage Operational Amplifier: Shahin Shah (12116053), Abhinav Singhal (12116001)Shahin ShahÎncă nu există evaluări

- Design of 12-Bit DAC Using CMOS TechnologyDocument5 paginiDesign of 12-Bit DAC Using CMOS TechnologysanthoshÎncă nu există evaluări

- Filter ThesisDocument123 paginiFilter ThesisNeha GuptaÎncă nu există evaluări

- Chapter 4Document100 paginiChapter 4khgvouy hvogyflÎncă nu există evaluări

- Physics and Modelling of Microelectronic Devices: BITS PilaniDocument31 paginiPhysics and Modelling of Microelectronic Devices: BITS PilaniSmriti RaiÎncă nu există evaluări

- Low Power Techniques For VLSI DesignDocument6 paginiLow Power Techniques For VLSI DesignjainatinÎncă nu există evaluări

- Final ThesisDocument85 paginiFinal ThesiskrishnavadlamudiÎncă nu există evaluări

- Modified Dual-Coupled Linear Congruential Generator Based Pseudorandom Bit GeneratorDocument11 paginiModified Dual-Coupled Linear Congruential Generator Based Pseudorandom Bit GeneratorGanesamoorthy BÎncă nu există evaluări

- 4G WirelessDocument4 pagini4G Wirelessaminkhan83Încă nu există evaluări

- Low Power, High Performance PMOS Biased Sense AmplifierDocument9 paginiLow Power, High Performance PMOS Biased Sense AmplifierIJRASETPublicationsÎncă nu există evaluări

- Analog Ic Design Biomedical PDFDocument162 paginiAnalog Ic Design Biomedical PDFCainãÎncă nu există evaluări

- Network Theory Formula Notesdoc 17Document24 paginiNetwork Theory Formula Notesdoc 17Manish KushwahaÎncă nu există evaluări

- Low Voltage CMOS SAR ADC DesignDocument68 paginiLow Voltage CMOS SAR ADC DesignAyush SukaniÎncă nu există evaluări

- Power Electronics Slides and Notes DC ConvertersDocument40 paginiPower Electronics Slides and Notes DC ConvertersAnoop MathewÎncă nu există evaluări

- Cmos ReportDocument25 paginiCmos ReportNaveen KumarÎncă nu există evaluări

- A 180 NM Low Power CMOS Operational Amplifier: Ketan J. Raut R. Kshirsagar A. BhagaliDocument4 paginiA 180 NM Low Power CMOS Operational Amplifier: Ketan J. Raut R. Kshirsagar A. BhagaliAnika TahsinÎncă nu există evaluări

- Advanced Communication Lab Manual: Visvesvaraya Technological UniversityDocument46 paginiAdvanced Communication Lab Manual: Visvesvaraya Technological UniversityPunith Gowda M B100% (2)

- Design Considerations For System-Level ESD Circuit ProtectionDocument6 paginiDesign Considerations For System-Level ESD Circuit Protectionmincingthought6612Încă nu există evaluări

- Gpdk090 DRM PDFDocument128 paginiGpdk090 DRM PDFShobhit GargÎncă nu există evaluări

- Physics of Power Dissipation in CMOS FET DevicesDocument70 paginiPhysics of Power Dissipation in CMOS FET DevicesPunith Gowda M BÎncă nu există evaluări

- Continuous-Time OTA-C Filters: Advantages: OTA-C Filters Have The Advantages of High Frequency or Wide BandwidthDocument12 paginiContinuous-Time OTA-C Filters: Advantages: OTA-C Filters Have The Advantages of High Frequency or Wide BandwidthAshraf DeenÎncă nu există evaluări

- A CMOS Bandgap Reference Circuit With Sub-1V OperationDocument5 paginiA CMOS Bandgap Reference Circuit With Sub-1V Operationbooky_mookyÎncă nu există evaluări

- Question PDFDocument12 paginiQuestion PDFjushwanth100% (1)

- WCNDocument102 paginiWCNVinaY ChowdaryÎncă nu există evaluări

- Lect08 GM ID Sizing MethodDocument55 paginiLect08 GM ID Sizing MethodAmith NayakÎncă nu există evaluări

- Design and Implementation of High Gain, High Bandwidth CMOS Folded Cascode Operational Transconductance AmplifierDocument5 paginiDesign and Implementation of High Gain, High Bandwidth CMOS Folded Cascode Operational Transconductance AmplifierChristian Montano GalvezÎncă nu există evaluări

- Mentor Graphics Lab ManualDocument27 paginiMentor Graphics Lab ManualHavi KosuruÎncă nu există evaluări

- mOS PDFDocument48 paginimOS PDFDebasish KerrÎncă nu există evaluări

- Effects of Threading Dislocations On Drain Current Dispersion and Slow Transients in Unpassivated Algan/Gan/Si Heterostructure Field-Effect TransistorsDocument6 paginiEffects of Threading Dislocations On Drain Current Dispersion and Slow Transients in Unpassivated Algan/Gan/Si Heterostructure Field-Effect TransistorsSumitChoudharyÎncă nu există evaluări

- Microelectronics ReliabilityDocument6 paginiMicroelectronics ReliabilitySumitChoudharyÎncă nu există evaluări

- High-Resolution X-Ray Diffraction Analysis of Alxga1-Xn/Inxga1-Xn/Gan On Sapphire Multilayer Structures: Theoretical, Simulations, and Experimental ObservationsDocument14 paginiHigh-Resolution X-Ray Diffraction Analysis of Alxga1-Xn/Inxga1-Xn/Gan On Sapphire Multilayer Structures: Theoretical, Simulations, and Experimental ObservationsSumitChoudharyÎncă nu există evaluări

- Microelectronics Reliability: Shubhankar Majumdar, Ankush Bag, Dhrubes BiswasDocument7 paginiMicroelectronics Reliability: Shubhankar Majumdar, Ankush Bag, Dhrubes BiswasSumitChoudharyÎncă nu există evaluări

- EDC Lec 34Document6 paginiEDC Lec 34SumitChoudharyÎncă nu există evaluări

- Hierarchical Assembly-Molecules To MammalsDocument14 paginiHierarchical Assembly-Molecules To MammalsSumitChoudharyÎncă nu există evaluări

- Altec Lansing 807-8A User ManualDocument2 paginiAltec Lansing 807-8A User ManualinboardÎncă nu există evaluări

- TSS - Unit VI - Cellular Telephone ConceptsDocument16 paginiTSS - Unit VI - Cellular Telephone ConceptsMrunmayeeÎncă nu există evaluări

- Atmel 42129 SAM D20 DatasheetDocument653 paginiAtmel 42129 SAM D20 Datasheethunter73Încă nu există evaluări

- SAP Mobile PDFDocument31 paginiSAP Mobile PDFsatyendra singhÎncă nu există evaluări

- Digital Logic Design: Dr. M. Najam Ul Islam PHD Electrical EngineeringDocument26 paginiDigital Logic Design: Dr. M. Najam Ul Islam PHD Electrical EngineeringS.M.Abbas Zadi.Încă nu există evaluări

- Corona: VisualDocument6 paginiCorona: VisualKARAM ZAKARIAÎncă nu există evaluări

- Revision History: Schematics IndexDocument16 paginiRevision History: Schematics IndexCarlos Ramirez GraweÎncă nu există evaluări

- Cooling of Chips by NanotechnologyDocument16 paginiCooling of Chips by NanotechnologyRupavathi PaulÎncă nu există evaluări

- Motorised Valves: 290 SeriesDocument4 paginiMotorised Valves: 290 SeriesARUN VISHWAKARMAÎncă nu există evaluări

- Communication Module I-LB+Document9 paginiCommunication Module I-LB+GiangDoÎncă nu există evaluări

- 1mdb02005-En en Reg 216 Reg 216 Compact Generator ProtectionDocument14 pagini1mdb02005-En en Reg 216 Reg 216 Compact Generator ProtectionhtkaraÎncă nu există evaluări

- Service Manual: 6 - Piece Home Theater SystemDocument24 paginiService Manual: 6 - Piece Home Theater SystemAlph MegaÎncă nu există evaluări

- Story Response - Story Overturning Moment: ETABS 2016 16.2.1 License # 1YEW8663HWFXMH9Document2 paginiStory Response - Story Overturning Moment: ETABS 2016 16.2.1 License # 1YEW8663HWFXMH9manish mehtaÎncă nu există evaluări

- Owner's Manual: - Save - Important Safety InstructionsDocument8 paginiOwner's Manual: - Save - Important Safety Instructionsgerardo Glez RiveraÎncă nu există evaluări

- Neuromorphic Computing-Seminar ReportDocument20 paginiNeuromorphic Computing-Seminar ReportArti PatleÎncă nu există evaluări

- Cadyce Catalog 2018Document34 paginiCadyce Catalog 2018Mayur MahajanÎncă nu există evaluări

- Power Meter With LoadDocument3 paginiPower Meter With LoadkhalidÎncă nu există evaluări

- Instructions For Flashlight: High Powered Tactical FlashlightDocument1 paginăInstructions For Flashlight: High Powered Tactical FlashlightMarkÎncă nu există evaluări

- What's The Difference Between DOL Start, Star-Delta, Soft Starter and A Variable Speed Drive?Document1 paginăWhat's The Difference Between DOL Start, Star-Delta, Soft Starter and A Variable Speed Drive?asdthuÎncă nu există evaluări

- Mizuho Osi Allegro 6800 Operating Table - User ManualDocument61 paginiMizuho Osi Allegro 6800 Operating Table - User ManualAnthony Lawrence100% (1)

- Toughest Questions For JEE Advanced 2015Document25 paginiToughest Questions For JEE Advanced 2015Avinash Kanaujiya0% (1)

- ..Document2 pagini..eim lenideÎncă nu există evaluări

- ECS 701 Communication Theory Lab Session: Wireless Communication Systems Simulation Using MATLABDocument13 paginiECS 701 Communication Theory Lab Session: Wireless Communication Systems Simulation Using MATLABKhushboo VermaÎncă nu există evaluări

- Bill of Quantities - Feb29Document15 paginiBill of Quantities - Feb29Elmer Soroan BarrerasÎncă nu există evaluări

- Chenming Hu ch7 SlidesDocument43 paginiChenming Hu ch7 SlideseleenaamohapatraÎncă nu există evaluări

- Understanding Changes in IEEE C62.11-2020Document12 paginiUnderstanding Changes in IEEE C62.11-2020Harold NaiborhuÎncă nu există evaluări

- Grounddistancerelays Residualcompensation PDFDocument13 paginiGrounddistancerelays Residualcompensation PDFShahzadmbhattiÎncă nu există evaluări

- Faculty Notes On InterferometryDocument44 paginiFaculty Notes On InterferometryAnything You Could ImagineÎncă nu există evaluări

- Report - CT FinalDocument12 paginiReport - CT FinalArup DasÎncă nu există evaluări