Documente Academic

Documente Profesional

Documente Cultură

DSP Integrated Circuits 3

Încărcat de

brindkowsiTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

DSP Integrated Circuits 3

Încărcat de

brindkowsiDrepturi de autor:

Formate disponibile

8

4

0

1

8

4

0

1

8

4

0

1

8

4

0

1

Reg. No. :

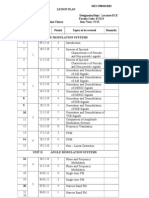

M.E./M.Tech. DEGREE EXAMINATION, JUNE 2011.

Common to M.E. Applied Electronics/M.E. VLSI design

First Semester

252101 DSP INTEGRATED CIRCUITS

(Regulation 2010)

Time : Three hours Maximum : 100 marks

Answer ALL questions.

PART A (10 2 = 20 marks)

1. Mention the advantages and disadvantages of ASIC implementation.

2. Draw the structural description of CMOS XOR gate.

3. What are the features of half-band FIR filter?

4. Draw the signal flow graph in time domain and frequency domain for the

signal equations : ( ) ( ) ( ) 1

2 1 3

+ = n v n av n v and ( ) ( ) n bv n v

3 4

= .

5. Mention the features of FIR filters.

6. What is the need for multirate signal processing?

7. Differentiate Von-Neumann architecture and Harvard architecture.

8. What are the typical applications of systolic and wave front arrays?

9. Represent the decimal number (15/32)10 in signed digit code.

10. How will you convert a twos complement number to CSDC numbers?

Question Paper Code : 31227

8

4

0

1

8

4

0

1

8

4

0

1

8

4

0

1

31227 2

PART B (5 16 = 80 marks)

11. (a) (i) Describe briefly a systematic partitioning technique for the design

of a complex DSP system. (8)

(ii) Identify the logic style and determine the logic function that is

realized by the circuit shown in below figure. (8)

Or

(b) Write short notes on :

(i) Precharge-Evaluation logic

(ii) VLSI process technologies. (8 + 8 = 16)

12. (a) (i) Draw the block diagram for the RLS lattice filter for N = 4. (8)

(ii) State and explain the sampling process of analog signals. (8)

Or

(b) Derive the Cooley Tukey FFT Decimation in Time algorithm for N = 4.

(16)

13. (a) (i) Define Decimation and Interpolation (4)

(ii) Explain Interpolation with an integer factor L. (12)

Or

(b) (i) Explain in detail about Round-off noise. (10)

(ii) Determine the signal to noise ratio for the safely scaled, 16 point

FFT. (6)

8

4

0

1

8

4

0

1

8

4

0

1

8

4

0

1

31227 3

14. (a) Explain in detail about shared memory architectures. (16)

Or

(b) (i) Differentiate multiprocessor architectures and multicomputer

architectures. (8)

(ii) Explain systolic and wave front arrays and its applications. (8)

15. (a) Explain in detail about basic shift accumulator with example. (16)

Or

(b) Simplify the basic serial/parallel multiplier in terms of the number of

D flip-flops and full adders for the coefficient (0.0101)2C.

(i) Draw the logic diagram for the minimized multiplier.

(ii) Determine the required control signals.

(iii) Determine the throughput when the data word length is 12 bits.

(iv) Validate the function of the minimized multiplier by performing a

multiplication with the value ( )

C

x

2

010 . 1 = . (4 + 4 + 4 + 4)

S-ar putea să vă placă și

- CS2204 - Analog and Digital Communication UQBDocument11 paginiCS2204 - Analog and Digital Communication UQBsrisridivineÎncă nu există evaluări

- DSP Integrated Circuits 4Document3 paginiDSP Integrated Circuits 4brindkowsiÎncă nu există evaluări

- Sixth Semester B Tech (Enginee Ing) Degree Examination December 2 10Document2 paginiSixth Semester B Tech (Enginee Ing) Degree Examination December 2 10Abhishek EkÎncă nu există evaluări

- DSP Question BankDocument3 paginiDSP Question BankNaveen HegdeÎncă nu există evaluări

- Question Bank: Subject Code: Subject NameDocument5 paginiQuestion Bank: Subject Code: Subject NamemsurendiranÎncă nu există evaluări

- Ece-Vii-dsp Algorithms & Architecture (10ec751) - AssignmentDocument9 paginiEce-Vii-dsp Algorithms & Architecture (10ec751) - AssignmentMuhammadMansoorGohar100% (1)

- EC2354 - Nov 2011 - AU QP Anna University Exams - VLSIDocument3 paginiEC2354 - Nov 2011 - AU QP Anna University Exams - VLSISHARANYAÎncă nu există evaluări

- Ece Vii DSP Algorithms Architecture 10ec751 Question Paper2Document9 paginiEce Vii DSP Algorithms Architecture 10ec751 Question Paper2Sudheer BabuÎncă nu există evaluări

- Question BanksDocument74 paginiQuestion BanksVidhya GanesanÎncă nu există evaluări

- Digital Signal Processing Question BankDocument4 paginiDigital Signal Processing Question BanksharlisreeÎncă nu există evaluări

- Digital Signal Processing Exam QuestionsDocument8 paginiDigital Signal Processing Exam QuestionsecehodaietÎncă nu există evaluări

- 7 Dec09-Jan10 DSP Al and Arch.Document2 pagini7 Dec09-Jan10 DSP Al and Arch.suresha vÎncă nu există evaluări

- Cusat Ec 6th Sem Question PaperDocument16 paginiCusat Ec 6th Sem Question PaperJinu Madhavan0% (1)

- DSP 2Document2 paginiDSP 2Sudhashree MutuswamyÎncă nu există evaluări

- Microprocessor and Microcontroller Anna University Question PapersDocument3 paginiMicroprocessor and Microcontroller Anna University Question PapersthennishaÎncă nu există evaluări

- Third Homework AssignmentDocument4 paginiThird Homework AssignmentTara Shankar ChakrabortyÎncă nu există evaluări

- University Question Papers - VLSIDocument26 paginiUniversity Question Papers - VLSIVijayÎncă nu există evaluări

- (3hours) : CompulsoryDocument7 pagini(3hours) : CompulsorySaima ZainabÎncă nu există evaluări

- Embedded Signal Processing QuestionsDocument14 paginiEmbedded Signal Processing QuestionsManu SeaÎncă nu există evaluări

- Anna University Digital Signal Processing Question BankDocument6 paginiAnna University Digital Signal Processing Question Banks.ranjithÎncă nu există evaluări

- Ece-Vii-dsp Algorithms & Architecture (10ec751) - Question PaperDocument9 paginiEce-Vii-dsp Algorithms & Architecture (10ec751) - Question PaperVinay Nagnath JokareÎncă nu există evaluări

- Adsp Model QuestionsDocument5 paginiAdsp Model QuestionsjayangceÎncă nu există evaluări

- Model MCDocument2 paginiModel MCAkilen MahalingamÎncă nu există evaluări

- DSP 10 Marks Assignment Compulsory For All PDFDocument2 paginiDSP 10 Marks Assignment Compulsory For All PDFrajÎncă nu există evaluări

- Question Paper Code:: Reg. No.Document2 paginiQuestion Paper Code:: Reg. No.Monica NareshÎncă nu există evaluări

- Jntu Vlsi Systems DesignDocument5 paginiJntu Vlsi Systems Design9010469071Încă nu există evaluări

- 07a80406 DspprocessorsandarchitecturesDocument4 pagini07a80406 DspprocessorsandarchitecturesSharanya ThirichinapalliÎncă nu există evaluări

- EE6301 DLC Question Bank Rejinpaul 2Document8 paginiEE6301 DLC Question Bank Rejinpaul 2aruljothiÎncă nu există evaluări

- Digital Signal ProcessingDocument7 paginiDigital Signal ProcessingAhsan MalikÎncă nu există evaluări

- Digital System Design: Provided by Humayra JahanDocument5 paginiDigital System Design: Provided by Humayra JahanZabirÎncă nu există evaluări

- Sathyabama University: Semester: IV Max - Marks: 80Document5 paginiSathyabama University: Semester: IV Max - Marks: 80GAURAVKINHAÎncă nu există evaluări

- Smart Materials, Sensors and ActuatorsDocument2 paginiSmart Materials, Sensors and ActuatorsmanojÎncă nu există evaluări

- Microprocessors and Interfacing November Am Rr311903Document8 paginiMicroprocessors and Interfacing November Am Rr311903Nizam Institute of Engineering and Technology LibraryÎncă nu există evaluări

- DellDocument6 paginiDellamu_manuÎncă nu există evaluări

- Question Paper Code:: Reg. No.Document3 paginiQuestion Paper Code:: Reg. No.Joshua DuffyÎncă nu există evaluări

- It 2354Document1 paginăIt 2354Nijin VinodÎncă nu există evaluări

- DLC Model IDocument2 paginiDLC Model IEEE DEPTÎncă nu există evaluări

- Computer Architecture Question BankDocument10 paginiComputer Architecture Question BankMalk Malik0% (1)

- Me 1Document436 paginiMe 1Akshay Mane0% (1)

- Question Paper Code:: Reg. No.Document3 paginiQuestion Paper Code:: Reg. No.Arun KumarÎncă nu există evaluări

- Rr322203 Microprocessors MicrocontrollersDocument8 paginiRr322203 Microprocessors Microcontrollersgeddam06108825Încă nu există evaluări

- Question Paper Code:: (10×2 20 Marks)Document3 paginiQuestion Paper Code:: (10×2 20 Marks)Kumarasabapathy NatarajanÎncă nu există evaluări

- APR2013P21Document63 paginiAPR2013P21qsashutoshÎncă nu există evaluări

- 6th sem.-EC 1358-DSPDocument8 pagini6th sem.-EC 1358-DSPGautham LogarajÎncă nu există evaluări

- Dica Question BankDocument4 paginiDica Question BankOmprakash KuswahaÎncă nu există evaluări

- Answer ALL Questions: PART B (5 X 16 80)Document17 paginiAnswer ALL Questions: PART B (5 X 16 80)Ahmed Eid Abd ElRaoufÎncă nu există evaluări

- rr311903 Microprocessors and InterfacingDocument8 paginirr311903 Microprocessors and InterfacingSRINIVASA RAO GANTAÎncă nu există evaluări

- BE 2008 Electronics&Telecommunication PDFDocument71 paginiBE 2008 Electronics&Telecommunication PDFcontrasterÎncă nu există evaluări

- Computer Architecture Question BankDocument10 paginiComputer Architecture Question BankaniprahalÎncă nu există evaluări

- Ec 1401 Vlsi DesignDocument2 paginiEc 1401 Vlsi DesignsubhazÎncă nu există evaluări

- Microprocessor and MicrocontrollerDocument2 paginiMicroprocessor and MicrocontrollerDarwin100% (1)

- Advanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionDe la EverandAdvanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionÎncă nu există evaluări

- LTE Signaling: Troubleshooting and Performance MeasurementDe la EverandLTE Signaling: Troubleshooting and Performance MeasurementÎncă nu există evaluări

- Chipless Radio Frequency Identification Reader Signal ProcessingDe la EverandChipless Radio Frequency Identification Reader Signal ProcessingÎncă nu există evaluări

- Programmable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysDe la EverandProgrammable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysÎncă nu există evaluări

- From GSM to LTE-Advanced Pro and 5G: An Introduction to Mobile Networks and Mobile BroadbandDe la EverandFrom GSM to LTE-Advanced Pro and 5G: An Introduction to Mobile Networks and Mobile BroadbandÎncă nu există evaluări

- Digital Signal Processing: Instant AccessDe la EverandDigital Signal Processing: Instant AccessEvaluare: 3.5 din 5 stele3.5/5 (2)

- Radio Frequency Identification and Sensors: From RFID to Chipless RFIDDe la EverandRadio Frequency Identification and Sensors: From RFID to Chipless RFIDÎncă nu există evaluări

- Embedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesDe la EverandEmbedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesÎncă nu există evaluări

- ECE ARR Time TableDocument59 paginiECE ARR Time TablebrindkowsiÎncă nu există evaluări

- LP - CT - Iv Sem EceDocument5 paginiLP - CT - Iv Sem EcebrindkowsiÎncă nu există evaluări

- Mod 1-CT QPDocument1 paginăMod 1-CT QPbrindkowsiÎncă nu există evaluări

- LP DPSD (It)Document4 paginiLP DPSD (It)brindkowsiÎncă nu există evaluări

- Ece 5-8th Sem SyllabusDocument113 paginiEce 5-8th Sem SyllabusSanthosh KarthiÎncă nu există evaluări

- Model Exam - I Ns (IV Ece A&b)Document2 paginiModel Exam - I Ns (IV Ece A&b)brindkowsiÎncă nu există evaluări

- DSP 1Document2 paginiDSP 1Tina PrakashÎncă nu există evaluări

- Fundamental AntennasDocument147 paginiFundamental Antennasbrindkowsi100% (1)

- For AwpDocument65 paginiFor AwpbrindkowsiÎncă nu există evaluări

- POM SyllabusDocument1 paginăPOM SyllabusbrindkowsiÎncă nu există evaluări

- Math10 LAS Set 1 Week 1 4Document39 paginiMath10 LAS Set 1 Week 1 4Burner StuffÎncă nu există evaluări

- M1: Numerical Methods Intro Discrete Algebra Accuracy ErrorsDocument40 paginiM1: Numerical Methods Intro Discrete Algebra Accuracy ErrorsCollano M. Noel RogieÎncă nu există evaluări

- 0580 w10 Ms 11Document4 pagini0580 w10 Ms 11Subah SowaidiÎncă nu există evaluări

- Advanced General Mathematics Worked Answers Enhanced Edition NO COPY WRITE INFRINGEMENT INTENDEDDocument418 paginiAdvanced General Mathematics Worked Answers Enhanced Edition NO COPY WRITE INFRINGEMENT INTENDEDNatasha Pettet50% (4)

- Diagnostic Test in Math /40: Ateneo de Manila High School - Tulong-Dunong TutoringDocument5 paginiDiagnostic Test in Math /40: Ateneo de Manila High School - Tulong-Dunong TutoringAntonio Luis BanzonÎncă nu există evaluări

- Opearational ManagementDocument3 paginiOpearational Managementtejasrai0% (1)

- Kfccalmt9709 - Exam Paper - 200508 - Maths p3 - Trial Exam - TaylorDocument5 paginiKfccalmt9709 - Exam Paper - 200508 - Maths p3 - Trial Exam - TaylorRyan TanÎncă nu există evaluări

- Chapter 01 (Sets) : MCQ'sDocument2 paginiChapter 01 (Sets) : MCQ'sFazeel Raza ButtÎncă nu există evaluări

- Chemistry 531 The One-Dimensional Random WalkDocument11 paginiChemistry 531 The One-Dimensional Random WalkBJI ALUMNIÎncă nu există evaluări

- Integration ConceptDocument34 paginiIntegration ConceptJANELLA ALVAREZÎncă nu există evaluări

- Finite Element Analysis: Constant Strain Triangle (CST)Document33 paginiFinite Element Analysis: Constant Strain Triangle (CST)Daniyal965Încă nu există evaluări

- ANSYS Tutorial - Design Optimization in DX - EDRDocument10 paginiANSYS Tutorial - Design Optimization in DX - EDRNithyanandan NarayanasamyÎncă nu există evaluări

- 13 Permutaion CombinationDocument58 pagini13 Permutaion CombinationyeahbabyÎncă nu există evaluări

- Innovative Lesson TemplateDocument12 paginiInnovative Lesson Templategeena123100% (1)

- Finding Fibonacci Patterns in NatureDocument8 paginiFinding Fibonacci Patterns in NatureJoann Delos santosÎncă nu există evaluări

- Monte Carlo Simulations ExcelDocument164 paginiMonte Carlo Simulations Exceljijo morijoÎncă nu există evaluări

- IMAGE PROCESSING NUMERICAL QUESTIONS SOLVEDDocument40 paginiIMAGE PROCESSING NUMERICAL QUESTIONS SOLVEDAshish Kumar SahuÎncă nu există evaluări

- Zeta Polynomials and The Mobius Function : Europ. CombinatoricsDocument6 paginiZeta Polynomials and The Mobius Function : Europ. CombinatoricsJhon Bladimir Caicedo PortillaÎncă nu există evaluări

- Berry Phase and PolarizationDocument173 paginiBerry Phase and PolarizationchanchalÎncă nu există evaluări

- Module 4 Review of Basic Probabilities and Probability RulesDocument44 paginiModule 4 Review of Basic Probabilities and Probability RulesqueenbeeastÎncă nu există evaluări

- 03-00-MBD StudyGuide Book Januar2015 PDFDocument311 pagini03-00-MBD StudyGuide Book Januar2015 PDFAmaro Calderon EduardoÎncă nu există evaluări

- Quadratic Equations PuzzleDocument3 paginiQuadratic Equations PuzzleNicholas Yates86% (7)

- Lesson Plan: Boolean Algebra and Logic GatesDocument57 paginiLesson Plan: Boolean Algebra and Logic GatesRoman MiaÎncă nu există evaluări

- Third Term Exam-Wps Office-5Document5 paginiThird Term Exam-Wps Office-5Shonekan KhadijahÎncă nu există evaluări

- Logic and Sets: Clast Mathematics CompetenciesDocument40 paginiLogic and Sets: Clast Mathematics CompetenciesmiyumiÎncă nu există evaluări

- Design and Performance Comparison of VariableDocument5 paginiDesign and Performance Comparison of VariableMarK VasquezÎncă nu există evaluări

- What is Game Theory? Exploring Strategic Decision-MakingDocument5 paginiWhat is Game Theory? Exploring Strategic Decision-Makingcursofisica paratodosÎncă nu există evaluări

- Chemistry Chapter 1Document47 paginiChemistry Chapter 1Madison CraterÎncă nu există evaluări

- Alfred Rupert Hall - Scientific Revolution 1500-1800 - The Formation of The Modern Scientific Attitude (1954)Document415 paginiAlfred Rupert Hall - Scientific Revolution 1500-1800 - The Formation of The Modern Scientific Attitude (1954)Mónica MondragónÎncă nu există evaluări

- The Five Attributes of Successful SchoolsDocument13 paginiThe Five Attributes of Successful SchoolsJanet AlmenanaÎncă nu există evaluări