Documente Academic

Documente Profesional

Documente Cultură

Low Power 64bit Multiplier Design by Vedic Mathematics

0 evaluări0% au considerat acest document util (0 voturi)

12 vizualizări4 paginiInternational Journal of Application or Innovation in Engineering & Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org

Volume 3, Issue 4, April 2014 ISSN 2319 - 4847

Titlu original

IJAIEM-2014-04-30-114

Drepturi de autor

© © All Rights Reserved

Formate disponibile

PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentInternational Journal of Application or Innovation in Engineering & Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org

Volume 3, Issue 4, April 2014 ISSN 2319 - 4847

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

12 vizualizări4 paginiLow Power 64bit Multiplier Design by Vedic Mathematics

International Journal of Application or Innovation in Engineering & Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org

Volume 3, Issue 4, April 2014 ISSN 2319 - 4847

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 4

International Journal of Application or Innovation in Engineering& Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org

Volume 3, Issue 4, April 2014 ISSN 2319 - 4847

Volume 3, Issue 4, April 2014 Page 393

Abstract

ALU is the heart of any processor or the any complex system .To increase the speed of any system, it is required to increase the

speed of ALU, but with low power consumption and for that portable life is required .VLSI designing techniques are the source to

reengineering any digital electronics circuitry. In this paper a low power 64 bit ALU is designed using VERILOG .Low power

consumption is achieved with Vedic multiplier and energy recovery adder .As multiplier and adder are the most important

functioning part of ALU .The speed of ALU is mainly depend on functioning of adder and multiplier. The idea to design Low

power ALU is adopted from Vedic Mathematics. for this purpose Urdhva Tiryakbhyam Sutra is used from Vedic mathematics, due

to that the complexity of circuit will reduce and power also get reduced.

Keywords Vedic mathematics ,Urdhva Tiryakbhyam Sutra ,Vedic multiplier

1. INTRODUCTION

Today ,energy crises is the main problem facing by the worldwide technologies. So, reducing the power consumption of

any circuitry is the main task to overcome the energy crises problem. Ever increasing demand of technology required the

processors to handle challenging and complex processes, results in to an assembling the number of processor cores on the

single IC. But also the load on the processor not reduced in the generic system. For this purpose it have to implement

main processor with co-processor to perform some specific operation like numeric computation, signal processing,

Graphics etc.

Now a days, increasing demands of gadgets like laptops and tablets forcing the technology to develop the low power

consuming and high speed processors. ALU is the heart of any processor. The speed of any processor is mainly depend on

the computational time required to complete any task in the ALU. The speed of the ALU is mainly depend on its internal

block functioning. Following fig.1 shows the basic blocks of the ALU. Amongst them the speed of ALU is mainly

depends on the functioning of adder and multiplier. Adder and multiplier are the main fundamental blocks inside the

ALU, on which its speed is depend. So implementing the high speed adder and multiplier to increase the speed of ALU is

necessary.

Multiplier is the slowest element in the system. So optimizing its area and increasing its speed is the major designing

task. This project work is deals with Designing of low power ALU by Vedic Mathematics. Vedic Mathematics technique

is used to implement first the Vedic multiplier of 64 bit to implement 64 bit ALU. For the calculation of multiplication

Vedic sutra is used. An existing marginal algorithm or architecture can be designed by inserting new technology through

a change at implementation level of design.

Vedic Mathematics

Vedic mathematics is the ancient system used for doing fast calculations in the mathematics. It is used in India from an

ancient times. It is the gift for fast processing of mathematics calculations to this world from ancient stages. By using

Low Power 64bit Multiplier Design by Vedic

Mathematics

Pranali Thakre

1

, Dr. Sanjay Dorle

2

, Prof. Vipin Bhure

3

1,2

Electronics & Communication Engineering, GHRAET, RTMN University, Nagpur, India

2

Electronics Engineering GHRCE, Autonomous Institute, Nagpur, India

International Journal of Application or Innovation in Engineering& Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org

Volume 3, Issue 4, April 2014 ISSN 2319 - 4847

Volume 3, Issue 4, April 2014 Page 394

Vedic mathematics for computation of algorithms of the coprocessor will reduce the computational time, complexity,

power, area, etc. Vedic mathematics is based on the 16 sutras of Vedas, which are described below. This system is more

simpler and faster than the modern mathematics. Thats why we must be thankful to Jagadguru Swami Sri Bharati

Krishna Tirthaji Maharaj who introduce Vedic mathematics and acknowledge the work of various people on Vedic

mathematics. The 16 sutras of Vedic mathematics are described below with their meanings in alphabetical order.

1) (Anurupye) Shunyamanyat- If one is in ratio, the other is zero

2) Chalana-Kalanabyham-Differences and Similarities

3) Ekadhikina Purvena-By one more than previous

4) Ekanyunena Purvena-By one less than the previous

5) Gunakasamuchyah-The factors of the sum is equal to the sum of the factors

6) Gunitasamuchyah-The product of the sum is equal to the sum of product

7) Nikhilam Navatashcaramam Dashatah-All from 9 and the last from 10

8) Paraavartya Yojayet-Transpose and adjust

9) Puranapuranabyham-By the completion or noncompletion

10) Sanalana Vyavakalanabhyam-By addition and by substraction

11) Shesanyankena Charamena-The remainders by the last digit

12) Shunyam Saamyasamuccaye-When the sum is the same tha sum is zero

13) Sopaantyadvayamantyam-The ultimate and twice the penultimate

14) Urdhva-triyakbyham-Vertically and crosswise

15) Vyashtisamansthih-Part and whole

16) Yaavadunam-Whatever the extent of its deficiency.

2. LITERATURE REVIEW

A. According to Anvesh Kumar, Ashish Raman, they gave the idea that Vedic sutras should be used to design the ALU.

They suggest two sutras for the designing ofALU, Nikhilam Sutra,Urdhva triyakbyham Sutra. Multiply Accumulate

block is extensibly used here. Multiplication algorithmis implemented using Verilog HDL. The multiplication

algorithm is applying here only for 2 digit and 3 digit. The result is simulated using modelsim simulator.

B. According to V Jayaprakashan, V S Kanchana Bhaaskaran,this paper anlyses the use of an ancient mathematical

approach for building an ALU. The arrangement of adders at architectural level is the main focus of this work. In

this paper 4bit array multiplier is compared with 4bit Vedic multiplier and simulation is done in Spice Simulator.

I. Proposed Ttechnique

Urdhva Triyakbyham Sutra:

The sutras in Vedic mathematics helps to do almost all types of numeric calculations in easy and fast manner. This sutra

is typically used for the multiplication purpose, applicable to all types of multiplication. Any bit binary number can be

multiplied quickly by using this sutra. The meaning of this sutra is vertically and crosswise. Given below summarize the

general process of the working of the Urdhva triykbyham sutra. For that we have consider here two number A and B

having digits AH and AL for A number and BH and BL for number. The result is in the form R0,R1,R2 and each time

International Journal of Application or Innovation in Engineering& Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org

Volume 3, Issue 4, April 2014 ISSN 2319 - 4847

Volume 3, Issue 4, April 2014 Page 395

carry is added in to each product i.e.C0,C1,C2. So there will no carry propagation occur in the result due to which delay

will be minimized.

By using this sutra the carry will not propogated up to the higher level,each time it will added to the product term,so time

required to propogate carry up to higher level will be minimized. By designing this 2bit multiplier we have to design the

64 bit multiplier. Following block diagram shows the diagram for 64bit Vedic multiplier.in the following fig shows the

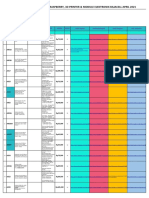

block diagram,RTL view and technology schematic and output waveform of 64bit Vedic multiplier.

FIG.2 : BLOCK DIAGRAM OF 64BIT VEDIC MULTIPLIER

FIG.3 : RTL VIEW OF 64BIT VEDIC MULTIPLIER

FIG.4 : SCHEMATIC REPRESENTATION OF 64BIT VEDIC MULTIPLIE

International Journal of Application or Innovation in Engineering& Management (IJAIEM)

Web Site: www.ijaiem.org Email: editor@ijaiem.org

Volume 3, Issue 4, April 2014 ISSN 2319 - 4847

Volume 3, Issue 4, April 2014 Page 396

FIG.5 : OUTPUT WAVEFORM

3. Conclusions

The study in the paper shows the use of Vedic mathematics for designing the low power ALU. This paper presents the

implementation of Vedic multiplier with the use of Urdhva triykbyham sutra,due to which carry will not propogated up

to higher level, so propagation delay for higher number multiplication will reduce. So the speed of the multiplier will

also increased. According to the above discussion it is most important issue to increase the speed and decrease the area

of the multiplier,as it is the most important element in any of the processor or system. An implementation of Vedic

mathematic techniques in designing of multiplier greatly improve the system performance and can be extended to

reconfigurable architecture.

REFERENCES

[1] Anvesh kumar, Ashish raman, Low Power ALU Design by Ancient Mathematics, 978-1-4244-5586-7/10, 2010 IEEE.

[2] V J ayaprakasan, S Vijayakumar, V S Kanchana Bhaaskaran,Evaluation of the Conventional vs. Ancient Computation

methodology for Energy Efficient Arithmetic Architecture,978-1-61284-764-1/11,2011 IEEE.

[3] Vaijyanath Kunchigi,Linganagouda Kulkarni,Subhash Kulkarni,32 Bit MAC Unit design usingusing vedic

multiplier,ECC,J NTU,2013

[4] Kumar, A.; Raman, A.; Low power ALU design by ancient mathematics, Computer and Automation Engineering (ICCAE),2010

The 2nd International Conference Publication Year: 2010 , Page(s): 862 865.

[5] Vaijyanath Kunchigi, Linganagouda Kulkarni, Subhash Kulkarni,32-Bit Mac Unit Design Using Vedic Multiplier,International

J ournal of Scientific and Research Publications, Volume 3,Issue 2,February 2013.

[6] [6]J agadguru Swami Sri Bharati Krisna Tirthaji Maharaja, Vedic Mathematics Sixteen Simple Mathematical Formulae fromthe Veda,1965.

[7] Sumita Vaidya and Deepak Dandekar, Delay-Power Performance comparison of Multipliers in VLSI Circuit Design, International J ournal of

Computer Networks & Communications (IJ CNC), Vol.2, No.4, pp 47-56, J uly 2010

AUTHOR

Pranali R. Thakre received BE degree in the year of 2012 in Electronics Engineering from

Smt.Radhikatai Pandav College of Engineering.Now pursuing in M-Tech (VLSI)IInd year from

Raisoni Acadomy of Engineering & Technology at MIDC Hingna.

S-ar putea să vă placă și

- Vedic Algorithms To Develop Green Chips For FutureDocument3 paginiVedic Algorithms To Develop Green Chips For FutureeditorijsaaÎncă nu există evaluări

- PG Students Seminar-234Document20 paginiPG Students Seminar-234Sp SwainÎncă nu există evaluări

- ASIC Design of A High Speed Low Power Circuit For Factorial Calculation Using Ancient Vedic MathematicsDocument10 paginiASIC Design of A High Speed Low Power Circuit For Factorial Calculation Using Ancient Vedic MathematicsNeem PlantÎncă nu există evaluări

- Design, Implementation and Performance Analysis of An Integrated Vedic Multiplier ArchitectureDocument7 paginiDesign, Implementation and Performance Analysis of An Integrated Vedic Multiplier ArchitectureAbhijeet KumarÎncă nu există evaluări

- Urdhva Triyakbhyam Sutra: Application of Vedic Mathematics For A High Speed Multiplier R. Senapati and B. K. Bhoi Volume - 1, Number - 1 Publication Year: 2012, Page(s) : 59 - 66Document8 paginiUrdhva Triyakbhyam Sutra: Application of Vedic Mathematics For A High Speed Multiplier R. Senapati and B. K. Bhoi Volume - 1, Number - 1 Publication Year: 2012, Page(s) : 59 - 66International Journal of Creative Mathematical Sciences and TechnologyÎncă nu există evaluări

- Implementation of Multiplier Using Vedic AlgorithmDocument5 paginiImplementation of Multiplier Using Vedic AlgorithmDwarakaManeekantaAddagiriÎncă nu există evaluări

- Implementation of An Efficient Multiplier Based On Vedic Mathematics Using EDA ToolDocument5 paginiImplementation of An Efficient Multiplier Based On Vedic Mathematics Using EDA TooltechiealyyÎncă nu există evaluări

- VLSI Implementation of Vedic Multiplier Using Urdhva - Tiryakbhyam Sutra in VHDL Environment: A NoveltyDocument8 paginiVLSI Implementation of Vedic Multiplier Using Urdhva - Tiryakbhyam Sutra in VHDL Environment: A NoveltyInternational Organization of Scientific Research (IOSR)Încă nu există evaluări

- Literature Survey: Preyesh Dalmia Et Al (2018)Document3 paginiLiterature Survey: Preyesh Dalmia Et Al (2018)yuvaraaj aletiÎncă nu există evaluări

- DSP Operation Using Vedic MathematicsDocument78 paginiDSP Operation Using Vedic Mathematicsnaveen mÎncă nu există evaluări

- Energy Efficient Approximate 8-Bit Vedic MultiplierDocument15 paginiEnergy Efficient Approximate 8-Bit Vedic MultiplierIJRASETPublicationsÎncă nu există evaluări

- Implementation of An Efficient Multiplier Based On Vedic Mathematics Using EDA ToolDocument5 paginiImplementation of An Efficient Multiplier Based On Vedic Mathematics Using EDA Toolrbangaram_1Încă nu există evaluări

- Low Power Square and Cube Architectures Using Vedic Sutras: G L, C - V R, R GDocument4 paginiLow Power Square and Cube Architectures Using Vedic Sutras: G L, C - V R, R GAshishKumarÎncă nu există evaluări

- Design and Analysis of An Efficient 16-Bit MultiplierDocument6 paginiDesign and Analysis of An Efficient 16-Bit MultiplierChandra shekara mnÎncă nu există evaluări

- Implementation of High Performance Binary Squarer: Pradeep M C, Ramesh SDocument7 paginiImplementation of High Performance Binary Squarer: Pradeep M C, Ramesh SAbhijeet KumarÎncă nu există evaluări

- Design and Implementation of FPGA Based 64-Bit MAC Unit Using VEDIC Multiplier and Reversible Logic GatesDocument8 paginiDesign and Implementation of FPGA Based 64-Bit MAC Unit Using VEDIC Multiplier and Reversible Logic GatesAmruth GhodkeÎncă nu există evaluări

- Design and Implementation of High Speed 32 Bit Vedic Arithmetic Unit On FPGADocument25 paginiDesign and Implementation of High Speed 32 Bit Vedic Arithmetic Unit On FPGAAshish Phuse100% (2)

- Area and Speed Wise Superior Vedic Multiplier For FPGA Based Arithmetic CircuitsDocument6 paginiArea and Speed Wise Superior Vedic Multiplier For FPGA Based Arithmetic CircuitsInternational Journal of computational Engineering research (IJCER)Încă nu există evaluări

- PJCTTDocument5 paginiPJCTTSharmila ReddyÎncă nu există evaluări

- A 32 BIT MAC Unit Design Using Vedic MultiplierDocument6 paginiA 32 BIT MAC Unit Design Using Vedic MultiplierdycsteiznÎncă nu există evaluări

- Design of 32 Bit Vedic Multiplier Using Carry Look Ahead AdderDocument5 paginiDesign of 32 Bit Vedic Multiplier Using Carry Look Ahead AdderGRD JournalsÎncă nu există evaluări

- Design of High Speed Vedic Multiplier Using Vedic Mathematics TechniquesDocument5 paginiDesign of High Speed Vedic Multiplier Using Vedic Mathematics TechniquesPramod KumarÎncă nu există evaluări

- Design and Implementation of 8 Bit Asynchronous MicrocontrollerDocument5 paginiDesign and Implementation of 8 Bit Asynchronous MicrocontrollerShakeel RanaÎncă nu există evaluări

- Design and Implementation of High Speed Vedic Multiplier Using Brent Kung Adder On FPGADocument4 paginiDesign and Implementation of High Speed Vedic Multiplier Using Brent Kung Adder On FPGAIJSTEÎncă nu există evaluări

- Reference 5Document12 paginiReference 5Ramesh NairÎncă nu există evaluări

- FPGA and ASIC Vedic MultiplierDocument4 paginiFPGA and ASIC Vedic MultiplierJagannath KbÎncă nu există evaluări

- Journal RefDocument8 paginiJournal RefANAND P RÎncă nu există evaluări

- Implemenation of Vedic Multiplier Using Reversible GatesDocument10 paginiImplemenation of Vedic Multiplier Using Reversible GatesCS & ITÎncă nu există evaluări

- 4Th Semesterproject Report On ALUDocument13 pagini4Th Semesterproject Report On ALUpop peeÎncă nu există evaluări

- Vedic Mathematics Based Research PaperDocument4 paginiVedic Mathematics Based Research Paperarushi_somaniÎncă nu există evaluări

- A Complete Mathematical Modeling, SimulationDocument15 paginiA Complete Mathematical Modeling, Simulationosama1928Încă nu există evaluări

- An Efficient Bit Reduction Binary Multiplication Algorithm Using Vedic MethodsDocument4 paginiAn Efficient Bit Reduction Binary Multiplication Algorithm Using Vedic MethodsShubham MishraÎncă nu există evaluări

- Design and Simulation of Power Efficient Traffic Light Controller (PTLC)Document6 paginiDesign and Simulation of Power Efficient Traffic Light Controller (PTLC)MasSla NerrazuriÎncă nu există evaluări

- A Complete Mathematical Modeling, Simulation and Computational Implementation of Boost Converter Via MATLAB/SimulinkDocument15 paginiA Complete Mathematical Modeling, Simulation and Computational Implementation of Boost Converter Via MATLAB/SimulinkSado KubsaÎncă nu există evaluări

- MBE ReportDocument25 paginiMBE ReportasreemadhuriÎncă nu există evaluări

- Design For 4-Bit Vedic Multiplier Using VHDL ModuleDocument12 paginiDesign For 4-Bit Vedic Multiplier Using VHDL Modulekathik goudÎncă nu există evaluări

- I Ji Scs 04112102Document4 paginiI Ji Scs 04112102WARSE JournalsÎncă nu există evaluări

- Researchpaper Design of ALU Using Reversible Logic Based Low Power Vedic MultiplierDocument5 paginiResearchpaper Design of ALU Using Reversible Logic Based Low Power Vedic MultiplierSwetha VanamÎncă nu există evaluări

- VLSI Circuits Power Estimation PDFDocument63 paginiVLSI Circuits Power Estimation PDFkiwangogÎncă nu există evaluări

- Implementation of 2-Bit Multiplier Circuit Using Pass Transistor LogicDocument10 paginiImplementation of 2-Bit Multiplier Circuit Using Pass Transistor LogicIJRASETPublicationsÎncă nu există evaluări

- Ijert Ijert: Performance Evaluation and Comparison of Multipliers Using Vedic AlgorithmsDocument5 paginiIjert Ijert: Performance Evaluation and Comparison of Multipliers Using Vedic AlgorithmsRajesh BathijaÎncă nu există evaluări

- ThesisDocument76 paginiThesisSantosh Kumar0% (1)

- An Efficient Design of 16 Bit MAC Unit Using Vedic MathematicsDocument4 paginiAn Efficient Design of 16 Bit MAC Unit Using Vedic MathematicsRami ReddyÎncă nu există evaluări

- Finalpublishedpaperoriginal PDFDocument10 paginiFinalpublishedpaperoriginal PDFSwetha VanamÎncă nu există evaluări

- Optimized High Performance Multiplier Using Vedic MathematicsDocument6 paginiOptimized High Performance Multiplier Using Vedic MathematicsPradeepÎncă nu există evaluări

- Fast Combinational Architecture For A Vedic DividerDocument5 paginiFast Combinational Architecture For A Vedic DividerkopperundeviÎncă nu există evaluări

- IJMET 09 10 014ggggggggggggggDocument11 paginiIJMET 09 10 014ggggggggggggggAhmad AlasadiÎncă nu există evaluări

- Fdocuments - in - Review Paper On High Speed Karatsuba Multiplier and Vedic MultiplicationDocument5 paginiFdocuments - in - Review Paper On High Speed Karatsuba Multiplier and Vedic MultiplicationMahi BodanapuÎncă nu există evaluări

- Performance Analysis of Vedic Multiplier in Hardware Implementation of Biomedical ApplicationsDocument4 paginiPerformance Analysis of Vedic Multiplier in Hardware Implementation of Biomedical ApplicationsInternational Journal of Innovative Science and Research TechnologyÎncă nu există evaluări

- Design of Area, Power and Delay Efficient High-Speed MultipliersDocument8 paginiDesign of Area, Power and Delay Efficient High-Speed MultipliersInternational Journal of Engineering and TechniquesÎncă nu există evaluări

- 51 - DesignDocument10 pagini51 - DesignSamÎncă nu există evaluări

- Stanley AssignmentDocument6 paginiStanley AssignmentTimsonÎncă nu există evaluări

- Application of Vedic Mathematics in Computer ArchitectureDocument6 paginiApplication of Vedic Mathematics in Computer ArchitectureInternational Journal of Research in Engineering and Science100% (1)

- 109EC0240Document56 pagini109EC0240rohitha avulaÎncă nu există evaluări

- IET Computers Digital Tech - 2023 - TavakolaeeDocument14 paginiIET Computers Digital Tech - 2023 - Tavakolaeebalasaravanan0408Încă nu există evaluări

- Development of A Simple Interactive Laboratory Exercise For Teaching The Principles of Velocity and Position EstimationDocument13 paginiDevelopment of A Simple Interactive Laboratory Exercise For Teaching The Principles of Velocity and Position EstimationGoran MiljkovicÎncă nu există evaluări

- Vlsi Implementation of 32 Bit Unsigned Multiplier Using An Efficient Claa and CslaDocument4 paginiVlsi Implementation of 32 Bit Unsigned Multiplier Using An Efficient Claa and CslaInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Comparative Analysis of Multiplier in Quaternary Logic: Shweta Hajare, Dr.P.K.DakholeDocument6 paginiComparative Analysis of Multiplier in Quaternary Logic: Shweta Hajare, Dr.P.K.DakholeDivya MokaraÎncă nu există evaluări

- Introduction to Quantum Computing & Machine Learning Technologies: 1, #1De la EverandIntroduction to Quantum Computing & Machine Learning Technologies: 1, #1Încă nu există evaluări

- Experimental Investigations On K/s Values of Remazol Reactive Dyes Used For Dyeing of Cotton Fabric With Recycled WastewaterDocument7 paginiExperimental Investigations On K/s Values of Remazol Reactive Dyes Used For Dyeing of Cotton Fabric With Recycled WastewaterInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Detection of Malicious Web Contents Using Machine and Deep Learning ApproachesDocument6 paginiDetection of Malicious Web Contents Using Machine and Deep Learning ApproachesInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- THE TOPOLOGICAL INDICES AND PHYSICAL PROPERTIES OF n-HEPTANE ISOMERSDocument7 paginiTHE TOPOLOGICAL INDICES AND PHYSICAL PROPERTIES OF n-HEPTANE ISOMERSInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Customer Satisfaction A Pillar of Total Quality ManagementDocument9 paginiCustomer Satisfaction A Pillar of Total Quality ManagementInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- An Importance and Advancement of QSAR Parameters in Modern Drug Design: A ReviewDocument9 paginiAn Importance and Advancement of QSAR Parameters in Modern Drug Design: A ReviewInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Analysis of Product Reliability Using Failure Mode Effect Critical Analysis (FMECA) - Case StudyDocument6 paginiAnalysis of Product Reliability Using Failure Mode Effect Critical Analysis (FMECA) - Case StudyInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Study of Customer Experience and Uses of Uber Cab Services in MumbaiDocument12 paginiStudy of Customer Experience and Uses of Uber Cab Services in MumbaiInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Soil Stabilization of Road by Using Spent WashDocument7 paginiSoil Stabilization of Road by Using Spent WashInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Staycation As A Marketing Tool For Survival Post Covid-19 in Five Star Hotels in Pune CityDocument10 paginiStaycation As A Marketing Tool For Survival Post Covid-19 in Five Star Hotels in Pune CityInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- THE TOPOLOGICAL INDICES AND PHYSICAL PROPERTIES OF n-HEPTANE ISOMERSDocument7 paginiTHE TOPOLOGICAL INDICES AND PHYSICAL PROPERTIES OF n-HEPTANE ISOMERSInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Study of Customer Experience and Uses of Uber Cab Services in MumbaiDocument12 paginiStudy of Customer Experience and Uses of Uber Cab Services in MumbaiInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Customer Satisfaction A Pillar of Total Quality ManagementDocument9 paginiCustomer Satisfaction A Pillar of Total Quality ManagementInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Detection of Malicious Web Contents Using Machine and Deep Learning ApproachesDocument6 paginiDetection of Malicious Web Contents Using Machine and Deep Learning ApproachesInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Analysis of Product Reliability Using Failure Mode Effect Critical Analysis (FMECA) - Case StudyDocument6 paginiAnalysis of Product Reliability Using Failure Mode Effect Critical Analysis (FMECA) - Case StudyInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Experimental Investigations On K/s Values of Remazol Reactive Dyes Used For Dyeing of Cotton Fabric With Recycled WastewaterDocument7 paginiExperimental Investigations On K/s Values of Remazol Reactive Dyes Used For Dyeing of Cotton Fabric With Recycled WastewaterInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- An Importance and Advancement of QSAR Parameters in Modern Drug Design: A ReviewDocument9 paginiAn Importance and Advancement of QSAR Parameters in Modern Drug Design: A ReviewInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- The Mexican Innovation System: A System's Dynamics PerspectiveDocument12 paginiThe Mexican Innovation System: A System's Dynamics PerspectiveInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- The Impact of Effective Communication To Enhance Management SkillsDocument6 paginiThe Impact of Effective Communication To Enhance Management SkillsInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Design and Detection of Fruits and Vegetable Spoiled Detetction SystemDocument8 paginiDesign and Detection of Fruits and Vegetable Spoiled Detetction SystemInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Challenges Faced by Speciality Restaurants in Pune City To Retain Employees During and Post COVID-19Document10 paginiChallenges Faced by Speciality Restaurants in Pune City To Retain Employees During and Post COVID-19International Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- A Comparative Analysis of Two Biggest Upi Paymentapps: Bhim and Google Pay (Tez)Document10 paginiA Comparative Analysis of Two Biggest Upi Paymentapps: Bhim and Google Pay (Tez)International Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- A Digital Record For Privacy and Security in Internet of ThingsDocument10 paginiA Digital Record For Privacy and Security in Internet of ThingsInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Performance of Short Transmission Line Using Mathematical MethodDocument8 paginiPerformance of Short Transmission Line Using Mathematical MethodInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Impact of Covid-19 On Employment Opportunities For Fresh Graduates in Hospitality &tourism IndustryDocument8 paginiImpact of Covid-19 On Employment Opportunities For Fresh Graduates in Hospitality &tourism IndustryInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Anchoring of Inflation Expectations and Monetary Policy Transparency in IndiaDocument9 paginiAnchoring of Inflation Expectations and Monetary Policy Transparency in IndiaInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Synthetic Datasets For Myocardial Infarction Based On Actual DatasetsDocument9 paginiSynthetic Datasets For Myocardial Infarction Based On Actual DatasetsInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Advanced Load Flow Study and Stability Analysis of A Real Time SystemDocument8 paginiAdvanced Load Flow Study and Stability Analysis of A Real Time SystemInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- A Deep Learning Based Assistant For The Visually ImpairedDocument11 paginiA Deep Learning Based Assistant For The Visually ImpairedInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Secured Contactless Atm Transaction During Pandemics With Feasible Time Constraint and Pattern For OtpDocument12 paginiSecured Contactless Atm Transaction During Pandemics With Feasible Time Constraint and Pattern For OtpInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Predicting The Effect of Fineparticulate Matter (PM2.5) On Anecosystemincludingclimate, Plants and Human Health Using MachinelearningmethodsDocument10 paginiPredicting The Effect of Fineparticulate Matter (PM2.5) On Anecosystemincludingclimate, Plants and Human Health Using MachinelearningmethodsInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Vmware Vsphere 4: The Best Platform For Building Cloud InfrastructuresDocument5 paginiVmware Vsphere 4: The Best Platform For Building Cloud InfrastructuresAshok Reddy AdurintiÎncă nu există evaluări

- Mach4 G and M Code Reference ManualDocument81 paginiMach4 G and M Code Reference ManualMegi Setiawan SÎncă nu există evaluări

- Production ManagementDocument14 paginiProduction Managementavinasss1963_3707255Încă nu există evaluări

- Chapter 6 - Ion ChannelsDocument12 paginiChapter 6 - Ion ChannelsntghshrÎncă nu există evaluări

- PascalDocument3 paginiPascalsenthilgnmitÎncă nu există evaluări

- Flutter WidgetsDocument14 paginiFlutter Widgetsleyan zahdehÎncă nu există evaluări

- Characterization and Manufacture of Braided Composites For Large Commercial Aircraft StructuresDocument44 paginiCharacterization and Manufacture of Braided Composites For Large Commercial Aircraft StructuresnicolasÎncă nu există evaluări

- Itp582b-515-01-Ib 2Document12 paginiItp582b-515-01-Ib 2Cara & Drei Amazing JourneyÎncă nu există evaluări

- Exam I: Turabo University School of Engineering Department of Mechanical Engineering MEEN 621 Boundary LayersDocument2 paginiExam I: Turabo University School of Engineering Department of Mechanical Engineering MEEN 621 Boundary LayersJoseph O. Camacho IrizarryÎncă nu există evaluări

- Catalog Produk Arduino Rajacell Ver10.4 - End - UserDocument192 paginiCatalog Produk Arduino Rajacell Ver10.4 - End - UserSanto SetiawanÎncă nu există evaluări

- Programa A4Q Selenium Tester FoundationDocument3 paginiPrograma A4Q Selenium Tester FoundationAdrian MazgaÎncă nu există evaluări

- Product and Service DesignDocument17 paginiProduct and Service DesignRahul KhannaÎncă nu există evaluări

- CAPTAIN250DITEINCOMPLETEAug 2020Document15 paginiCAPTAIN250DITEINCOMPLETEAug 2020billal toufik BendjimaÎncă nu există evaluări

- Comparative Analysis of Public and Private Educational Institutions: A Case Study of District Vehari-PakistanDocument10 paginiComparative Analysis of Public and Private Educational Institutions: A Case Study of District Vehari-PakistannithyaÎncă nu există evaluări

- Viking Bladder Tanks - enDocument11 paginiViking Bladder Tanks - enVINOD PAULÎncă nu există evaluări

- TEMPLATE School Data Analysis Report 1st Periodic TestDocument3 paginiTEMPLATE School Data Analysis Report 1st Periodic TestDaisy Reyes CayabyabÎncă nu există evaluări

- Unbound Base Courses and Ballasts Rev 0Document19 paginiUnbound Base Courses and Ballasts Rev 0MohamedOmar83Încă nu există evaluări

- CSBS Syllabus Book 01 11 2021 1Document117 paginiCSBS Syllabus Book 01 11 2021 1PRITHVI P. K SEC 2020Încă nu există evaluări

- SequencesDocument6 paginiSequencessundarismails544Încă nu există evaluări

- Miscellaneous Measurements: and ControlsDocument50 paginiMiscellaneous Measurements: and ControlsJeje JungÎncă nu există evaluări

- PartIII Semiconductor at Equilibrium PrintDocument22 paginiPartIII Semiconductor at Equilibrium PrintK.bhogendranathareddy KuppireddyÎncă nu există evaluări

- FM Testbank Ch08Document6 paginiFM Testbank Ch08David LarryÎncă nu există evaluări

- PVD PreloadingDocument104 paginiPVD PreloadingAkriti Kothiala100% (1)

- Fiber Series CTCDocument31 paginiFiber Series CTCJorge GaitanÎncă nu există evaluări

- Urban Transportation PlanningDocument10 paginiUrban Transportation PlanningkiranÎncă nu există evaluări

- Python GUI Programming With Tkinter Deve-31-118 Job 1Document88 paginiPython GUI Programming With Tkinter Deve-31-118 Job 1Shafira LuthfiyahÎncă nu există evaluări

- Jurnal Teknologi Technoscientia Issn: 1979-8415 Vol. 5 No. 2 Februari 2013Document7 paginiJurnal Teknologi Technoscientia Issn: 1979-8415 Vol. 5 No. 2 Februari 2013DENNIHERÎncă nu există evaluări

- Siddartha Institute of Science and Technoloy, Puttur: Seminar On Audio SpotlightingDocument19 paginiSiddartha Institute of Science and Technoloy, Puttur: Seminar On Audio SpotlightingRasiÎncă nu există evaluări

- Comentarios-103 - Parte I - English PDFDocument89 paginiComentarios-103 - Parte I - English PDFSakthivel VÎncă nu există evaluări

- Unit 3 Study Guide and ExercisesDocument2 paginiUnit 3 Study Guide and ExercisesTuan NguyenÎncă nu există evaluări