Documente Academic

Documente Profesional

Documente Cultură

Applying The DAC08: Integrated Circuits

Încărcat de

kondoritoclDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Applying The DAC08: Integrated Circuits

Încărcat de

kondoritoclDrepturi de autor:

Formate disponibile

Philips

Semiconductors

AN101

Applying the DAC08

1988 Dec

INTEGRATED CIRCUITS

Philips Semiconductors Application note

AN101 Applying the DAC08

2 1988 Dec

Reference Amplifier Setup

The DAC08 Series are multiplying D-to-A converters in which the

output current is the product of a digital number and the input

reference current. The reference current may be fixed or may vary

from nearly zero to +4.0mA. The full-scale output current is a linear

function of the reference current and is given by this equalization

where I

REF

=I

14

.

I

FS

+

255

256

x I

REF

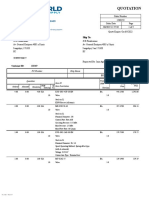

In positive reference applications shown in Figure 1, an external

positive reference voltage forces current through R14 into the V

REF

(+) terminal (Pin 14) of the reference amplifier. Alternatively, a

negative reference may be applied to V

REF

(-) at Pin 15, shown in

Figure 2. Reference current flows from ground through R14 into

V

REF

(+) as in the positive reference case. This negative reference

connection has the advantage of a very high impedance presented

at Pin 15. The voltage at Pin 14 is equal to and tracks the voltage at

Pin 15 due to the high gain of the internal reference amplifier. R15

(nominally equal to R14) is used to cancel bias current errors. R15

may be eliminated with only a minor increase in error.

Bipolar references may be accommodated by offsetting V

REF

or Pin

15 as shown in Figure 3. The negative common-mode range of the

reference amplifier is given by the following equation:

V

CM

* + V * ) (I

REF

@ 1kW) ) 2.5V

When a DC reference is used, a reference bypass capacitor is

recommended. A 5.0V TTL logic supply is not recommended as a

reference. If a regulated power supply is used as a reference, R14

should be split into 2 resistors with the junction bypassed to ground

with a 0.1F capacitor.

For most applications, a +10.0V reference is recommended for

optimum full-scale temperature coefficient performance. This will

minimize the contributions of reference amplifier V

OS

and TCV

OS

.

For most applications, the tight relationship between I

REF

and I

FS

will eliminate the need for trimming I

REF

. If required, full-scale

trimming may be accomplished by adjusting the value of R14, or by

using a potentiometer for R14. An improved method of full-scale

trimming which eliminates potentiometer TC effects is shown in

Figure 4.

Using lower values of reference current reduces negative power

supply current and increases reference amplifier negative

common-mode range. The recommended range for operation with a

DC reference current is +0.2mA to +4.0mA.

The reference amplifier must be compensated by using a capacitor

from Pin 16 to V-. For fixed reference operation, a 0.01F capacitor

is recommended. For variable reference applications, see section

entitled Reference Amplifier Compensation for Multiplying

Applications.

Multiplying Operation

The DAC08 Series provides excellent multiplying performance with

an extremely linear relationship between I

FS

and I

REF

over a range

of 4mA to 4A. Monotonic operation is maintained over a typical

range of I

REF

from 100A to 4.0mA.

Reference Amplifier Compensation for Multiplying

Applications

AC reference applications will require the reference amplifier to be

compensated using a capacitor from Pin 16 to V-. The value of this

capacitor depends on the impedance presented to Pin 14. For R14

values of 1.0, 2.5 and 5.0k, minimum values of C

C

are 15, 37 and

75pF. Larger values of R14 require proportionately increased values

of C

C

for proper phase margin.

For fastest multiplying response, low values of R14 enabling small

C

C

values should be used. If Pin 14 is driven by a high impedance

such as a transistor current source, none of the preceding values

will suffice and the amplifier must be heavily compensated, which

will decrease overall bandwidth and slew rate. For R14=1k and

CC=15pF, the reference amplifier slews at 4mA/s enabling a

transition from I

REF

=0 to I

REF

=2mA in 500ns.

V

REF

()

I

REF

V

REF

(+)

R

REF

(R14)

R

15

B

1

B

2

B

3

B

4

B

5

B

6

B

7

B

8

I

O

1

0

V

LC

V V COMP

C

C

V+ 0.1F

V

1F

5 6 7 8 9 10 11 12

4

2

1 13 16 3

15

14

MSB LSB

DAC08

I

FS

[ )

V

REF

R

REF

x

255

256

I

O

) I

O

+ I

FS

for all logic states

For fixed reference, TTL operation typical values are:

V

REF

= +10.000V, R

REF

= 5,000, R15 R

REF

C

C

= 0.01F, V

LC

= 0V (ground)

NOTES:

SL00681

Figure 1. Basic Positive Reference Operation

Operation with pulse inputs to the reference amplifier may be

accommodated by an alternate compensation scheme shown in

Figure 5. This technique provides lowest full-scale transition times.

Full-scale transition (0 to 2mA) occurs in 120ns when the equivalent

impedance at Pin 14 is 200 and C

C

=0. This yields a reference

slew rate of 16mA/s, which is relatively independent of R

IN

and V

IN

values.

Logic Inputs

The DAC08 design incorporates a logic input circuit which enables

direct interface to all popular logic families and provides maximum

noise immunity. This feature is made possible by the large input

swing capability, 2A logic input current and completely adjustable

logic threshold voltage. For V-=-15V, the logic inputs may swing

between -11V and +18V. This enables direct interface with +15V

CMOS logic, even when the DAC08 is powered from a +5V supply.

Minimum input logic swing is given by the following equation:

V * ) (I

REF

@ 1kW) ) 2.5V

The logic threshold may be adjusted over a wide range by placing

an appropriate voltage at the logic threshold control in (Pin 1, V

LC

).

Figure 6 shows the relationship between V

LC

and V

TH

over the

temperature range, with V

TH

nominally 1.4 above V

LC

. For TTL and

DTL interface, simply ground Pin 1. When interfacing ECL, an

I

REF

=1mA is recommended. For interfacing other logic families, see

Figure 7. For general setup of the logic control circuit, it should be

noted that Pin 1 may source up to 200A. External circuitry should

be designed to accommodate this current.

Philips Semiconductors Application note

AN101 Applying the DAC08

1988 Dec 3

R14

14

15

4

2

R15

I

O

I

0

DAC08

V

REF

R

REF

SL00682

Figure 2. Basic Negative Reference Operation

+V

REF

I

REF

R

REF

I

IN

R

IN

14

15

DAC08

V

IN

R

REF

14

15

DAC08

V

REF

V

IN

HIGH INPUT

IMPEDANCE

R15; OPTIONAL

SL00683

Figure 3. Accommodating Bipolar References

2mA

14

15

DAC08

LOW T.C.

4.5k

I

REF

()

1V

APPROX.

5K

50K

PTO

10V

SL00684

Figure 4. Recommended Full-Scale Adjustment Circuit

Fastest settling times are obtained when Pin 1 sees a low

impedance. If Pin 1 is connected to a 1k divider, for example, it

should be bypassed to ground by a 0.01F capacitor.

Analog Output Currents

Both true and complemented output sink currents are provided,

where I

O

+I

O

=I

FS

. Current appears at the true output when a 1 is

applied to each logic input. As the binary count increases, the sink

current at Pin 4 increases proportionally, in the fashion of a positive

logic D-to-A converter. When a 0 is applied to any input bit, that

current is turned off at Pin 4 and turned on at Pin 2. A decreasing

logic count increases I

O

as in a negative or inverted logic D-to-A

converter. Both outputs may be used simultaneously. If one of the

outputs is not required it must still be connected to ground or to a

point capable of sourcing I

FS

. Do not leave an unused output pin

open.

Both outputs have an extremely wide voltage compliance enabling

fast direct current-to-voltage conversion through a resistor tied to

ground or other voltage source. Positive compliance is 36V above V-

and is independent of the positive supply. Negative compliance is

given by the equation:

V * ) (I

REF

@ 1kW) ) 3.0V

Note that lower values of I

REF

will allow a greater output

compliance.

The dual outputs enable double the usual peak-to-peak load swing

when driving loads in quasi-differential fashion. This feature is

especially useful in cable driving, CRT deflection and in other

balanced applications such as balanced-bridge A/D circuits, as well

as driving center-tapped coils and transformers.

V

REF

OPTIONAL RESISTOR

FOR OFFSET INPUTS

R

IN R

REF

REQ

200

R

p

NO

CAP

14

15

16

4

2

OV

SL00685

Figure 5. Pulsed Reference Operation

Power Supplies

The DAC08 operates over a wide range of power supply voltages

from a total supply of 9V to 36V. When operating at supplies of 5V

or less, I

REF

1mA is recommended.

Low reference current operation decreases power consumption and

increases negative compliance, reference amplifier negative

common-mode range, negative logic input range, and negative logic

threshold range. Consult the various figures for guidance. For

example, operation at -4.5V with I

REF

=2mA is not recommended

because negative output compliance would be reduced to near zero.

Operation from lower supplies is possible; however, at least 8V total

must be applied between Pins 2 and 4, and Pin 3 to insure turn-on

of the internal bias network.

Symmetrical supplies are not required, as the DAC08 is quite

insensitive to variations in supply voltage. Battery operation is

feasible as no ground connection is required; however, an artificial

ground may be useful to insure logic swings, etc., remain between

acceptable limits.

Power consumption may be calculated by this equation:

P

D

+ (I )) (V )) ) (I )) (V *) ) (I

REF

)(V *)

A useful feature of the DAC08 design is that supply current is

constant and independent of input logic states. This is useful in

cryptographic applications and further serves to reduce the size of

the power supply bypass capacitors.

Temperature Performance

The linearity and monotonicity specifications of the DAC08 are

guaranteed to apply over the entire rated operating temperature

Philips Semiconductors Application note

AN101 Applying the DAC08

1988 Dec 4

range. Full-scale output current drift is low, typically 10ppm/C with

zero-scale output current and drift essentially negligible compared to

LSB.

2.0

1.8

1.6

1.4

1.2

1.0

0.8

0.6

0.4

0.2

0

50 0 +50 +100 +150

TEMPERATURE (+C)

V

V

(

V

)

T

H

L

C

SL00686

Figure 6. V

TH

V

LC

vs Temperature

Full-scale output drift performance will be best with +10.0V

references, as V

OS

and TCV

OS

of the reference amplifier will be

very small compared to 10.0V. The temperature coefficient of the

reference resistor R14 should match and track that of the output

resistor for minimum overall full-scale drift. Settling times of the

DAC08 decrease approximately 10% at -55C, and an increase of

about 15% at +125C is typical.

Settling Time

The DAC08 is capable of extremely fast settling times (typically

70ns at I

REF

=2.0mA).

Judicious circuit design and careful board layout must be employed

to obtain full performance potential during testing and application.

The logic switch design enables propagation delays of only 35ns for

each of the 8 bits. Settling time to within LSB is therefore 35ns, with

each progressively larger bit taking successively longer. The MSB

settles in 70ns, thus determining the overall settling time of 70ns.

Settling to 6-bit accuracy requires about 55 to 60ns. The output

capacitance, including the package, is approximately 15pF.

Therefore, the output RC time constant dominates settling time if R

L

>500.

Settling time and propagation delay are relatively insensitive to logic

input amplitude and rise and fall times due to the high gain of the

logic switches. Settling time also remains essentially constant for

I

REF

values down to 1.0mA, with gradual increases for lower I

REF

values. The principal advantage of higher I

REF

values lies in the

ability to attain a given output level with lower load resistors, thus

reducing the output RC time constant.

Measurement of settling time requires the ability to accurately

resolve 4A. Therefore, a 1k load is needed to provide adequate

drive for most oscilloscopes. The settling time fixture of Figure 8

uses a cascade design to permit driving a 1k load with less than

5pF of parasite capacitance at the measurement node. At I

REF

values of less than 1.0mA, excessive RC damping of the output is

difficult to prevent while maintaining adequate sensitivity. However,

the major carry from 01111111 to 10000000 provides an accurate

indicator of settling time. This code change does not require the

normal 6.2 time constants to settle to within 0.2% of the final value;

thus, settling time may be observed at lower values of I

REF

.

The DAC08 switching transients or glitches are very low and may be

further reduced by small capacitive loads at the output at a minor

sacrifice in settling time.

Fastest operation can be obtained by using short leads, minimizing

output capacitance and load resistor values, and by adequate

bypassing at the supply, reference and V

LC

terminals. Supplies do

not require large electrolytic bypass capacitors as the supply current

drain is dependent of input logic states. 0.1F capacitors at the

supply pins provide full transient performance.

+5V CMOS

V

TH

= 5.0V

TTL, DTL

V

TH

= +1.4V

DAC08

V

LC

V

TH

= V

LC

+1.4V

+15V CMOS, HTL, HNIL

V

THY

= +7.6V

+12V

TO

+15V 10k

V

LC

6.2V

ZENER 6.2k

+15V

9.1k

V

LC

0.1F

PMOS

V

TH

= 0V

IN4148

V

LC

10k

5V

TO

10V

+5V CMOS

V

TH

= 2.8V

V

LC

IN4148

+10V

6.2k

V

LC

0.1F

3.6k

1.3

k

3.9k

10K ECL

V

TH

=1.29V

2N3904

IN4148

V

LC

1k

5.2V

DAC08

SL00687

Figure 7. Interfacing With Various Logic Families

Philips Semiconductors Application note

AN101 Applying the DAC08

1988 Dec 5

FOR TRUNON, V

L

2.7V

FOR TURN OFF, V

L

= 0.7V

V

L

+5V

.1F

.4V

0V

0V

V

OUT

1xPROBE

.4V 15k

1k

.1

F

.1F

50F

1k

MINIMUM

CAPACITANCE

V

CL

0.7V

2k 100k

15V

TO D.U.T.

V

IN

R

REF

+V

REF

R15

+15V15V

I

OUT

.1F

.1F

.01F

5 6 7 8 9 10 11 12

4

2

16 3 13

15

14

DAC08

SL00688

Figure 8. Settling Time Measurement

TYPICAL APPLICATIONS

B

1

B

2

B

3

B

4

B

5

B

6

B

7

B

8

I

O

4

2

MSB LSB

DAC08

I

O

I

REF

= 2.000mA

14

E

O

5.000

5.000

E

O

Full-scale

Full-scale LSB

Half-scale + LSB

Half-scale

Half-scale LSB

Zero-scale + LSB

Zero-scale

B

1

B

2

B

3

B

4

B

5

B

6

B

7

B

8

I

O

(mA) I

O

(mA) E

O

E

O

1

1

1

1

0

0

0

1

1

0

0

1

0

0

1

1

0

0

1

0

0

1

1

0

0

1

0

0

1

1

0

0

1

0

0

1

1

0

0

1

0

0

1

1

0

0

1

0

0

1

0

1

0

1

1

0

1.992

1.984

1.008

1.000

0.992

0.008

0.000 1.992

1.984

1.000

0.992

0.984

0.008

0.000

0.000

0.040

4.960

5.000

5.040

9.920

9.960 0.000

0.040

4.920

4.960

5.000

9.920

9.960

SL00689

Figure 9. Basic Unipolar Negative Operation

Philips Semiconductors Application note

AN101 Applying the DAC08

1988 Dec 6

TYPICAL APPLICATIONS (Continued)

I

O

I

O

4

2

DAC08

I

REF

()

= 2.000mA

+10,000

10k 10k

E

O

E

O

4

DAC08

I

REF

()

= 2.000mA

+10,000

10k 10k

E

O

Pos full-scale

Pos full-scale LSB

Zero-scale + LSB

Zero-scale

Zero-scale LSB

Neg full-scale + LSB

Neg full-scale

B

1

B

2

B

3

B

4

B

5

B

6

B

7

B

8

E

O

E

O

1

1

1

1

0

0

0

1

1

0

0

1

0

0

1

1

0

0

1

0

0

1

1

0

0

1

0

0

1

1

0

0

1

0

0

1

1

0

0

1

0

0

1

1

0

0

1

0

0

1

0

1

0

1

1

0 +10.000

+9.920

+0.080

0.000

0.080

9.840

9.920 +10.000

+9.920

+0.160

+0.080

0.000

9.840

9.920

SL00690

Figure 10. Basic Bipolar Output Operation

I

O

4

2

DAC08

I

O

V

REF

5.0k

+ 10,000V

6.0k

5.0k

5.0k

E

O

+

NE530

Pos full-scale

Pos full-scale LSB

(+) Zero-scale

() Zero-scale

Neg full-scale + LSB

Neg full-scale

B

1

B

2

B

3

B

4

B

5

B

6

B

7

B

8

E

O

1

1

1

0

0

0

1

1

0

1

0

0

1

1

0

1

0

0

1

1

0

1

0

0

1

1

0

1

0

0

1

1

0

1

0

0

1

1

0

1

0

0

1

0

0

1

1

0 9.920

9.840

0.040

+0.040

+9.840

+9.920

SL00691

Figure 11. Symmetrical Offset Binary Operation

4

2

DAC08

E

O I

O

I

O

+

NE530

R

L

For complementary output (operation as negative logic DAC), connect

inverting input of op amp to I

O

(Pin 2); connect I

O

(Pin 4) to ground.

NOTE:

SL00692

Figure 12. Positive Low Impedance Output Operation

4

2

DAC08

E

O

I

O

I

O

+

NE530

R

L

0 TO I

FS

R

L

I

FS

I

REF

255

256

For complementary output (operation as negative logic DAC), connect

inverting input of op amp to I

O

(Pin 2); connect I

O

(Pin 4) to ground.

NOTE:

SL00693

Figure 13. Negative Low Impedance Output Operation

Philips Semiconductors Application note

AN101 Applying the DAC08

1988 Dec 7

ANALOG

INPUT

START

SCHOTTKY

TTL

LOGIC

FAST

COMPARATOR

+

DAC08

ENDOFENCODE

8BIT

OUTPUT

SL00694

Figure 14. Low Cost 8-Bit 1s A-to-D Converter

10V

REFERENCE

15V +15V

01F

3.0M

I

O

I

O

DAC08

C

C

5k

5k

B

1

B

2

B

3

B

4

B

5

B

6

B

7

B

8

16 3 13

2

4

14

15

5 6 7 8 9 1011121

ANALOG

INPUT

0 TO 10V

5,000K

3

10V

8

7

2

4

1

1K

NE527

10V

2 9

10

1

3 4 5 6 11 12 13 14

SERIAL

OUTPUT

START

CONVERSION

COMPLETE

TTL CLOCK

INPUT 2.25MHz

Connect start to conversion complete for continuous conversions.

NOTE:

SL00695

Figure 15. 3 IC Low Cost A-to-D Converter

Output is directly proportional to positive power supply.

NOTE:

13 14 15 1

10

20

40

80

V

MSD

5 6 7 8 9 10 11 12

3

DACO8

16 2

4

15V

.01F

+15V

.01F

V

LC

I

O

13 14 16 11

44 16

I

O

I

O

8K

+15V

V

LC

RI

7.5K

+1%W

RI

7.5K

1%W

2 3

5 6 7 8 9 101112

I

O

6

4

2

1

LSD

DAC08 V

2

3

NE530

7

6

4 0 TO 9.9V

IN 0.1V STEPS

15V

V

FS

9.9V FOR

(1001 1001) CODE

SL00696

Figure 16. Low Cost 2-Digit BCD DAC

+15V 15V

01F

DAC08

B

1

B

2

B

3

B

4

B

5

B

6

B

5

16 3 13

2

4

14

15

5 6 7 8 9 10 1112 1

NE530

DAC08

2

4

14

15

1

01F

+10V

0V

10V

R1

INPUT

R7

14K

R4

MSB

+5%

100

pF

R2

+15V

2

3

7

6

E

O

4

15V

R3

5 6 7 8 9 1011 12

13 16 3

LSB

B

7

B

8

B

6

01F

15V +15V

1. R1 = R2 = R3

2. R4 = R5

3. E

O

DC to 20kHz = 5V

4. E

O

DC to 10kHz = 10V

NOTES:

Bipolar input offset

binary output

Performs 2 quadrant

multiplications AC input

controls output polarity

SL00697

Figure 17. DC-Coupled Digital Attenuator/

Programmable Gain Amplifier

Philips Semiconductors Application note

AN101 Applying the DAC08

1988 Dec 8

1. Bipolar output is symmetrical around zero, adjustable peak-to-peak amplitude.

2. For triangle wave, count up to full, reverse and count down.

3. For positive-going sawtooth, count up to full, clean, repeat.

4. For negative-going sawtooth, count down, clean, repeat.

NOTES:

5. For other waveforms, use a ROM programmed with the desired function.

10V

REFERENCE

DAC08

2

4

14

15

1

5 6 7 8 9 1011 12

13 16 3

01F

15V +15V

CLOCK INPUT

AMPLITUDE

CONTROL

5K

5K

8BIT UP/DOWN

COUNTER

74191N

I

O

I

O

S (+)

S ()

R1

5K

15V

R1 = R2

+.05%

MISMATCH

E

O

15V

R2

5K

01F

NE530

01F

SL00698

Figure 18. High-Speed Waveform Generator

S-ar putea să vă placă și

- DAC0808 8-Bit D/A Converter: Literature Number: SNAS539ADocument14 paginiDAC0808 8-Bit D/A Converter: Literature Number: SNAS539AomÎncă nu există evaluări

- UC2842 Philips AN1272 PDFDocument7 paginiUC2842 Philips AN1272 PDFupali01Încă nu există evaluări

- Designing With ReferencesDocument12 paginiDesigning With Referencesantares71Încă nu există evaluări

- Phase Control IC With Overload Limitation For Tacho Applications U211BDocument29 paginiPhase Control IC With Overload Limitation For Tacho Applications U211BescalucioÎncă nu există evaluări

- AN166 Basic feedback theoryDocument5 paginiAN166 Basic feedback theorySourik BharÎncă nu există evaluări

- Iraudamp1 PDFDocument22 paginiIraudamp1 PDFamijoski6051Încă nu există evaluări

- UC3842 current mode controller application noteDocument7 paginiUC3842 current mode controller application noteCui BapÎncă nu există evaluări

- AN-1525 Single Supply Operation of The DAC0800 and DAC0802: Application ReportDocument6 paginiAN-1525 Single Supply Operation of The DAC0800 and DAC0802: Application ReportYasin ArslanÎncă nu există evaluări

- Ic Applications Lab NewDocument12 paginiIc Applications Lab NewSandy RonaldoÎncă nu există evaluări

- Speed Control IC for Motors with Tacho FeedbackDocument11 paginiSpeed Control IC for Motors with Tacho FeedbackAlex FierăscuÎncă nu există evaluări

- Low-Power Design Technique For Flash A/D Converters Based On Reduction of The Number of ComparatorsDocument4 paginiLow-Power Design Technique For Flash A/D Converters Based On Reduction of The Number of ComparatorspablonchoteÎncă nu există evaluări

- Principles Applications ICL7660Document10 paginiPrinciples Applications ICL7660Juan F. RamosÎncă nu există evaluări

- Lm331 AppnoteDocument8 paginiLm331 AppnoteEward KenÎncă nu există evaluări

- V/F Converter Ics Handle Frequency-To-Voltage Needs: The Art of CompromiseDocument8 paginiV/F Converter Ics Handle Frequency-To-Voltage Needs: The Art of CompromiseAlim SheikhÎncă nu există evaluări

- LM3914 Dot Bar Display Driver GuideDocument16 paginiLM3914 Dot Bar Display Driver GuideHelton AmorimÎncă nu există evaluări

- Op-Amps As Ac Amplifers: Capacitor-Coupled Voltage FollowerDocument7 paginiOp-Amps As Ac Amplifers: Capacitor-Coupled Voltage FollowerNisha Kotyan G RÎncă nu există evaluări

- KDAS OPAMP APPLICATIONsDocument24 paginiKDAS OPAMP APPLICATIONsKingshuk GuptaÎncă nu există evaluări

- Regenerative Powerdump Circuit PDFDocument4 paginiRegenerative Powerdump Circuit PDFCarlos Gabriel EstergaardÎncă nu există evaluări

- Opamp Linear Device 1300847494 PDFDocument12 paginiOpamp Linear Device 1300847494 PDFNini FarribasÎncă nu există evaluări

- ADC10D040 Dual 10-Bit, 40 MSPS, 267 MW A/D Converter: General Description FeaturesDocument28 paginiADC10D040 Dual 10-Bit, 40 MSPS, 267 MW A/D Converter: General Description FeaturesskiziltoprakÎncă nu există evaluări

- AN-1525 Single Supply Operation of The DAC0800 and DAC0802: Application ReportDocument7 paginiAN-1525 Single Supply Operation of The DAC0800 and DAC0802: Application Reporttidjani86Încă nu există evaluări

- Applications of Balanced ModulatorDocument5 paginiApplications of Balanced ModulatorSomeshwar GaddalaÎncă nu există evaluări

- Tone Control TDA1524ADocument2 paginiTone Control TDA1524AElias Oliveira E SilvaÎncă nu există evaluări

- Experiment No-1: Aim:-Low Resistance Using Kelvin Double BridgeDocument21 paginiExperiment No-1: Aim:-Low Resistance Using Kelvin Double BridgegnathblÎncă nu există evaluări

- LM317 AppnoteDocument6 paginiLM317 AppnoteLucas Matías JuarezÎncă nu există evaluări

- IC 741 Op Amp Specifications and ApplicationsDocument90 paginiIC 741 Op Amp Specifications and ApplicationsAhmed Al MansurÎncă nu există evaluări

- Analog-To-Digital and Digital-To-Analog Converters - Electronics PostDocument6 paginiAnalog-To-Digital and Digital-To-Analog Converters - Electronics PostDurga DeviÎncă nu există evaluări

- U 211 B 2Document21 paginiU 211 B 2tavobeckerÎncă nu există evaluări

- Iraudamp 1Document22 paginiIraudamp 1luizcpimentaÎncă nu există evaluări

- Parameters of OPAMP:: Io dc1 dc2Document14 paginiParameters of OPAMP:: Io dc1 dc2Dhiyagu DhamotharaswamyÎncă nu există evaluări

- Chapter 8Document40 paginiChapter 8UMMU MARDHIAH ABDUL HALIMÎncă nu există evaluări

- Closed Loop Speed Control of PMDC MotorDocument6 paginiClosed Loop Speed Control of PMDC MotorVignesh WaranÎncă nu există evaluări

- M62301SP, FP: Description Pin Configuration (Top View)Document9 paginiM62301SP, FP: Description Pin Configuration (Top View)roozbehxoxÎncă nu există evaluări

- Schematic Diagram and OperationDocument5 paginiSchematic Diagram and OperationHarishÎncă nu există evaluări

- Sbea 001Document18 paginiSbea 001firstbook1Încă nu există evaluări

- IRISMPS4 Reference Design Technical SpecificationsDocument17 paginiIRISMPS4 Reference Design Technical Specificationssa920189Încă nu există evaluări

- 6283-Article Text-16473-1-10-20140217Document8 pagini6283-Article Text-16473-1-10-20140217ivasi ivasiÎncă nu există evaluări

- Op Amp ParameteresDocument23 paginiOp Amp ParameteresNimish PrabhakarÎncă nu există evaluări

- Open Loop Phase Control Circuit: DescriptionDocument7 paginiOpen Loop Phase Control Circuit: DescriptionMuhammad NajibÎncă nu există evaluări

- Driver L297 + L6203Document2 paginiDriver L297 + L6203TatiiieleeeÎncă nu există evaluări

- Lic May-June 2017Document15 paginiLic May-June 2017santhosh sekarÎncă nu există evaluări

- Practical Operational AmplifierDocument14 paginiPractical Operational AmplifierSatyajit MukherjeeÎncă nu există evaluări

- Unit 4 NotesDocument26 paginiUnit 4 NotesJohnsi JÎncă nu există evaluări

- Electronics Lab ManualDocument92 paginiElectronics Lab ManualVolodya SmolyakÎncă nu există evaluări

- Class22 and 23 Op Amp-May9-AnnotatedDocument47 paginiClass22 and 23 Op Amp-May9-AnnotatedJagveer MeenaÎncă nu există evaluări

- Wi-Fi Home AutomationDocument23 paginiWi-Fi Home Automationchandru_8Încă nu există evaluări

- Solid State Relays Input Resistor SelectionDocument2 paginiSolid State Relays Input Resistor Selectionthangaraj_icÎncă nu există evaluări

- Opamp Function GeneratorDocument2 paginiOpamp Function GeneratorchethaÎncă nu există evaluări

- Siemens Simoreg KDocument12 paginiSiemens Simoreg Knafeesdelta175% (4)

- Voltage To Frequency Converter Folosind Ci 555 TimerDocument11 paginiVoltage To Frequency Converter Folosind Ci 555 TimerAl ZanoagaÎncă nu există evaluări

- DAC0808 8-Bit D/A Converter: Literature Number: SNAS539ADocument15 paginiDAC0808 8-Bit D/A Converter: Literature Number: SNAS539AYasser Mauricio Flores RamonÎncă nu există evaluări

- CHAP 17 - Linear-Digital ICsDocument30 paginiCHAP 17 - Linear-Digital ICsAli Duraz100% (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Încă nu există evaluări

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Evaluare: 2.5 din 5 stele2.5/5 (3)

- Power Supply Projects: A Collection of Innovative and Practical Design ProjectsDe la EverandPower Supply Projects: A Collection of Innovative and Practical Design ProjectsEvaluare: 3 din 5 stele3/5 (2)

- 172DIP PCB Mount Miniature Reed Relay/: SPDT and DPDT 0.25 Amp RatedDocument2 pagini172DIP PCB Mount Miniature Reed Relay/: SPDT and DPDT 0.25 Amp RatedkondoritoclÎncă nu există evaluări

- SineinverterDocument6 paginiSineinverterVeer GupteÎncă nu există evaluări

- PT 100 InterfaceDocument1 paginăPT 100 InterfacekondoritoclÎncă nu există evaluări

- I2c To Keyboard InterfaceDocument2 paginiI2c To Keyboard InterfacekondoritoclÎncă nu există evaluări

- Interface Guide: At90S C LDocument48 paginiInterface Guide: At90S C LkondoritoclÎncă nu există evaluări

- N Ystem Rogrammer: IcrocontrollersDocument2 paginiN Ystem Rogrammer: IcrocontrollerskondoritoclÎncă nu există evaluări

- Bascom and AVR, InterruptsDocument13 paginiBascom and AVR, InterruptskondoritoclÎncă nu există evaluări

- I2c To LCD InterfaceDocument1 paginăI2c To LCD InterfaceTTM_SOBIÎncă nu există evaluări

- N Ystem Rogrammer: IcrocontrollersDocument2 paginiN Ystem Rogrammer: IcrocontrollerskondoritoclÎncă nu există evaluări

- Chainsaw SparesDocument2 paginiChainsaw SpareswanttobeanmacccÎncă nu există evaluări

- Schott Ky DiodesDocument3 paginiSchott Ky DiodesAmarnath M DamodaranÎncă nu există evaluări

- Anna University International Admissions GuideDocument4 paginiAnna University International Admissions GuideAmir AzeezÎncă nu există evaluări

- Reaffirmed Indian Standards for Water Resources DepartmentDocument2 paginiReaffirmed Indian Standards for Water Resources Departmentjamjam75Încă nu există evaluări

- Adobe 2017 Download LinksDocument4 paginiAdobe 2017 Download LinksDaśhīñg ÆžīÎncă nu există evaluări

- IES Syllabus For Mechanical Engineering IES 2015 Syllabus MEDocument5 paginiIES Syllabus For Mechanical Engineering IES 2015 Syllabus MERohitMishraÎncă nu există evaluări

- GNB Absoltye IIPDocument18 paginiGNB Absoltye IIPFederico Tellez QÎncă nu există evaluări

- Quick install guide for Konica printer control systemDocument2 paginiQuick install guide for Konica printer control systemAsep KurniawanÎncă nu există evaluări

- Section 3Document56 paginiSection 3Fernanda Medeiros CarvalhoÎncă nu există evaluări

- 253 MA Austenitic - High - Temperature - Grades - Datasheet PDFDocument12 pagini253 MA Austenitic - High - Temperature - Grades - Datasheet PDFAbdulÎncă nu există evaluări

- CC 848815325Document76 paginiCC 848815325patopickÎncă nu există evaluări

- UML For Java ProgrammersDocument47 paginiUML For Java ProgrammersRajesh KumarÎncă nu există evaluări

- Space Programming 1Document10 paginiSpace Programming 1Mache SebialÎncă nu există evaluări

- Marine Seawater ValvesDocument8 paginiMarine Seawater ValvesPhornlert WanaÎncă nu există evaluări

- Khatib Dissertation FinalDocument193 paginiKhatib Dissertation FinalMonalisa MohantyÎncă nu există evaluări

- A Design and Analysis of A Morphing Hyper-Elliptic Cambered Span (HECS) WingDocument10 paginiA Design and Analysis of A Morphing Hyper-Elliptic Cambered Span (HECS) WingJEORJEÎncă nu există evaluări

- Chapter 01 - JAVA ProgrammingDocument29 paginiChapter 01 - JAVA ProgrammingsunnyxmÎncă nu există evaluări

- Bill of Quantities: Fifteen-Classrooms ADocument1 paginăBill of Quantities: Fifteen-Classrooms AFritz NatividadÎncă nu există evaluări

- Ups Installation and Maintenance ManualDocument141 paginiUps Installation and Maintenance ManualMuntasir100% (1)

- Cotización FM2Document2 paginiCotización FM2Anonymous 3o4Mwew0Încă nu există evaluări

- Cisco IOS XR Configuration Guide Master IndexDocument66 paginiCisco IOS XR Configuration Guide Master IndexvictorpetriniÎncă nu există evaluări

- Relief/Unloading Valve: Spool, Pilot Operated 200 L/Min (52 Usgpm) - 350 Bar (5000 Psi)Document2 paginiRelief/Unloading Valve: Spool, Pilot Operated 200 L/Min (52 Usgpm) - 350 Bar (5000 Psi)Dragan LazicÎncă nu există evaluări

- Gauss Lab 01Document4 paginiGauss Lab 01Diego Giraldo BoteroÎncă nu există evaluări

- Examples Sheet 2 PDFDocument4 paginiExamples Sheet 2 PDFAbraham SauvingnonÎncă nu există evaluări

- Tensile Test AnalysisDocument8 paginiTensile Test AnalysisNazmul HasanÎncă nu există evaluări

- Philips Flat TV 15PF9936 - LeafletDocument2 paginiPhilips Flat TV 15PF9936 - LeafletVlad FlorescuÎncă nu există evaluări

- Caterpillar Cat 320d 320dl Excavator Parts ManualDocument34 paginiCaterpillar Cat 320d 320dl Excavator Parts ManualSara Sarmiento Echeverry100% (1)

- Daftar Alat TSMDocument2 paginiDaftar Alat TSMagus ImawanÎncă nu există evaluări

- SLVR Cartas PDFDocument18 paginiSLVR Cartas PDFEdgar David Ruelas ClarosÎncă nu există evaluări

- Jockey Pump BrochureDocument8 paginiJockey Pump BrochuregbogboiweÎncă nu există evaluări