Documente Academic

Documente Profesional

Documente Cultură

WWW - Ee.iitm - Ac.in Ee09b044 Wiki Lib Exe Fetch - PHP Media Wiki Coll Notes Digisys

Încărcat de

Amala AdithyhaTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

WWW - Ee.iitm - Ac.in Ee09b044 Wiki Lib Exe Fetch - PHP Media Wiki Coll Notes Digisys

Încărcat de

Amala AdithyhaDrepturi de autor:

Formate disponibile

DIGITAL SYSTEMS

COURSE SUMMARY

-EE Placement Team 2013-14

COUNTERS AND REGISTERS

Register consists of a group of flip-flops with a common clock input.They are used to store

and shift binary data.

Counter is constructed from two or more flip-flops which change states in a prescribed

sequence when input pulses are received.

Counters and registers are sequential circuits.

DESIGN OF BINARY COUNTERS

D=

!

T= "

!

#$or%

&$ample'

CLOCED SE!UENTIAL CIRCUITS

E"am#le1$Anal%&'&()(or the following sequential circuit)find the ne$t state equation or map for each flip-

flop.*sing these construct a state graph and a state table.+hat is the output sequence when the input

sequence is ,=-..--/ Draw the timing diagram.

0olution'

E"am#le 2)$De*'+a't,n ,- &tate .*a#/& an0 ta1le&( '1 sequential circuit has two inputs#,. and ,2% and

one output#3%.The output begins as - and remains a constant value unless one of the following input

sequences occurs.#a% The input sequence ,.,2=-.)-- causes the output to become -)#b% The input

sequence ,.,2=..)-- causes the ouput to become . #c% The input sequence ,.,2=.-)-- causes the

output to toggle.Derive a moore state table.

0olution )

1ssign a state to each possible input#--)-.)..).-% with an output of -)and another state to each input with

an output of ..This gives eight states.

The state table with 4 states to this 5-state table using the state reduction methods.

STATE REDUCTION )

E"am#le)

STATE ASSIGN2ENT )+e try to satisfy as many conditions as possible from the following'

DESIGN OF SE!UENTIAL CIRCUITS

*sing 617#6rogrammable 1rrray 7ogic%

ALGORIT32IC STATE 2AC3INE)

1n 108 chart is a method of describing the sequential operations of a digital system.The chart is

composed of three basic elements'

..0tate bo$'9ndicates a state in the Control 0equence and is rectangular in shape.

2.Decision bo$'Descibes the effect of an input on the control subsystem and has diamond shape.

:.Conditional bo$'The register operations or outputs listed inside the conditional bo$ are generated during

a given state provided the input condition is satisfied.9t has an oval shape.

E"am#le) AS2 BLOC

State 0'a.*am e45'+alent ,- t/e AS2 Bl,c6

ASYNC3RONOUS SE!UENTIAL CIRCUITS

1synchronous sequential circuits donot use clock pulses.The change of internal state occurs when there

is a change in the input variables.

1nalysis &$ample'

Fl,7 Ta1le)

.

;

Race conditions: 1 race condition is said to e$ist in an 1synchronous sequential circuit when two or

more binary state variables change value in response to change in an input variable.9f the final stable

state that the circuit reaches does not depend on the order in which the state variables change)the race is

called a noncritical race.9f it is possible to end up in two or more different stable states)depending on the

order in which the state variables change)then it is a critical race.

+hen a circuit goes through a unique sequence of unstable states)it is said to have a cycle.

P,'nt t, *emem1e* 7/en 0e&'.n'n. A&%nc/*,n,5& &e45ent'al c'*c5't&)

The circuit must be operated in fundamental mode with only one input changing at a time and must be

free of critical races.

Sta1'l't%) The values of < that are equal to y represent stable states .

&$ample of an unstable circuit.

Design example for Asynchronous Sequential Circuit:To design a negative edge triggered T (lip-

(lop.

Ste#& 'n+,l+e0 'n t/e 0e&'.n #*,ce&&)

..De&'.n &#ec'-'cat',n&'The circuit has 2 inputs)T#Toggle% and C #Clock% and one output .The output

state is complemented if T=. and the clock C changes from . to -.&lse the output remains unchanged.

28 P*'m't'+e Fl,7 Ta1le

2

.

:.2e*.'n. ,- t/e Fl,7ta1le

5.Race-F*ee State A&&'.nment'

9.T*an&'t',n Ta1le an0 O5t#5t 2a#'

:.O1ta'n t/e L,.'c D'a.*am'

3a;a*0&'*nwanted switching transients that appear at the output of a circuit because different paths

e$hibit different propagation delays.

3a;a*0& 'n C,m1'nat,*'al C'*c5't&)Condition where a single variable change produces a momentary

output change when no output change should occur.

3a;a*0& 'n Se45ent'al C'*c5't&'9f a momentary incorrect signal is fed back in an 1synchronous

0equential Circuit)it may cause the circuit to go into the wrong stable state.

T%#e& ,- 3a;a*0&'

E"am#le'

Detect',n'+henever the circuit must move from one product term to the other)there is a possibility of a

momentary interval when neither term is equal to .)giving rise to an undesirable - output.

C,**ect',n'

Removed by covering any two minterms that may produce a ha=ard with a product term common

to both.

+hen a Combinatorial circuit is implemented in 0>6 form with 1?D->R or ?1?D gates)the

removal of static-. ha=ard guarantees the removal of static-- ha=ard and dynamic ha=ards.

1nother way to avoid static ha=ards in 1synchronous 0equential Circuits is to implement the

circuit with 0-R 7atches.1 momentary - signal applied to the 0 or R inputs of a ?>R latch will

have no effect on the state of the circuit.

3a;a*0 'n an A&%nc/*,n,5& Se45ent'al C'*c5't8

E&&ent'al /a;a*0&'

Caused by unequal delays along two or more paths that originate from the same input.

>ccurs in asynchronous sequential circuits.

Cannot be corrected by adding redundant gates.

Corrected by ad@usting the amount of delay in the affected path.

EE Placement Team 2013-14

References :

..(undamentals of 7ogic Design by C/a*le& R,t/.

2.Digital Design by 2,**'& 2an,8

S-ar putea să vă placă și

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

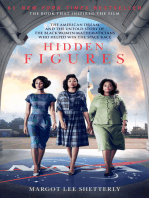

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (73)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- Rhinoceros Command Reference ManualDocument466 paginiRhinoceros Command Reference ManualSyed Raziuddin100% (2)

- Arbor APS STT - Unit 08 - Peace Time Tuning - 25jan2018Document30 paginiArbor APS STT - Unit 08 - Peace Time Tuning - 25jan2018masterlinh2008Încă nu există evaluări

- Introduction To TeradataDocument51 paginiIntroduction To Teradataraghavendra.nieÎncă nu există evaluări

- Saravana Medicals: Pramod Kumar K P Mr. MuthukumarDocument1 paginăSaravana Medicals: Pramod Kumar K P Mr. MuthukumarAmala AdithyhaÎncă nu există evaluări

- TCS Talent Management Solution: Compensation Management User Manual - Release 3.1Document71 paginiTCS Talent Management Solution: Compensation Management User Manual - Release 3.1Amala AdithyhaÎncă nu există evaluări

- TCS Talent Management Solution: Compensation Management User Manual - Release 3.1Document71 paginiTCS Talent Management Solution: Compensation Management User Manual - Release 3.1Amala AdithyhaÎncă nu există evaluări

- WCC CourseFee 2013-14Document2 paginiWCC CourseFee 2013-14Amala AdithyhaÎncă nu există evaluări

- Ti Mend Eight Reg Sevens emDocument11 paginiTi Mend Eight Reg Sevens emPrabakaran PrakashÎncă nu există evaluări

- Unit 1 (IWT)Document9 paginiUnit 1 (IWT)himanshu masihÎncă nu există evaluări

- PROJECT Report EndDocument36 paginiPROJECT Report EndPankaj RoswalÎncă nu există evaluări

- Chapter 7 Project Problem: Noise Equivalent Bandwidth: BackgroundDocument4 paginiChapter 7 Project Problem: Noise Equivalent Bandwidth: BackgroundAndrew WagehÎncă nu există evaluări

- Access VB A TechniquesDocument111 paginiAccess VB A Techniquesusm01Încă nu există evaluări

- Cisco Mobility Express User Guide For Release 8.1 09-11-2016Document64 paginiCisco Mobility Express User Guide For Release 8.1 09-11-2016Phyo Min TunÎncă nu există evaluări

- Switching Delay MathsDocument3 paginiSwitching Delay MathsS M AkashÎncă nu există evaluări

- Openedge 10 Availability GuideDocument25 paginiOpenedge 10 Availability GuideKarÎncă nu există evaluări

- SQL CodesDocument31 paginiSQL CodesSapna Kumari100% (2)

- SLEUTH Training ManualDocument20 paginiSLEUTH Training ManualBiagio Antonio Maionese MaimoneÎncă nu există evaluări

- Java QuestionsDocument118 paginiJava QuestionsPragathees WaranÎncă nu există evaluări

- Vala TutorialDocument56 paginiVala TutorialFelipe Borges50% (2)

- LUF-MDM-002 Informatica MDM Hub Installation and Configuration Guide v01.1Document50 paginiLUF-MDM-002 Informatica MDM Hub Installation and Configuration Guide v01.1cognosindia100% (1)

- GX Developer FX - Beginner's Manual 166391-A (10.05) PDFDocument46 paginiGX Developer FX - Beginner's Manual 166391-A (10.05) PDFAlessandro JesusÎncă nu există evaluări

- Object Oriented Programming: An OverviewDocument27 paginiObject Oriented Programming: An OverviewArun KrishnanÎncă nu există evaluări

- Migrating AK Personalizations: 10-2 Oracle Application Framework Personalization GuideDocument12 paginiMigrating AK Personalizations: 10-2 Oracle Application Framework Personalization GuideHardeep SinghÎncă nu există evaluări

- RouterOS 2 7 ReferenceManualDocument599 paginiRouterOS 2 7 ReferenceManualYala Ngv DesigneÎncă nu există evaluări

- First Year Puc Model Question Paper 2013 New Syllabus: Instructions: Part A I Answer All The Following QuestionsDocument2 paginiFirst Year Puc Model Question Paper 2013 New Syllabus: Instructions: Part A I Answer All The Following QuestionsPrasad C M100% (7)

- Data Entry Oprator Exam-2014 Answer Key Series A Computer Science & Uttarakhand State Related G.SDocument4 paginiData Entry Oprator Exam-2014 Answer Key Series A Computer Science & Uttarakhand State Related G.SSumit SinghÎncă nu există evaluări

- Bca I Year Assignment QuestionsDocument7 paginiBca I Year Assignment QuestionsX FriendÎncă nu există evaluări

- 1Document123 pagini1zayazssÎncă nu există evaluări

- Oracle Performance Tuning SQLTXTplainDocument41 paginiOracle Performance Tuning SQLTXTplainjimmy_sam001Încă nu există evaluări

- Softlogix Simulateur 1789-SIMDocument8 paginiSoftlogix Simulateur 1789-SIMlellb7Încă nu există evaluări

- Training Document For InTouchDocument27 paginiTraining Document For InTouchthakur941264191950% (2)

- Install and Configure Windows 2008 R2 VPNDocument76 paginiInstall and Configure Windows 2008 R2 VPNVîrban DoinaÎncă nu există evaluări

- COA Unit 1Document33 paginiCOA Unit 1Keshav NaganathanÎncă nu există evaluări

- Zen and The Art of PythonDocument43 paginiZen and The Art of PythonSurajkumar HarikumarÎncă nu există evaluări

- CAP 5510: Introduction To Bioinformatics (3 CR) Spring 2006: Tu Thu 11-12:15 in ECS 141Document1 paginăCAP 5510: Introduction To Bioinformatics (3 CR) Spring 2006: Tu Thu 11-12:15 in ECS 141hadymatrixÎncă nu există evaluări