Documente Academic

Documente Profesional

Documente Cultură

Chapter 05 Graphics Accelerator (SGX)

Încărcat de

yiutkmvjkq0 evaluări0% au considerat acest document util (0 voturi)

70 vizualizări8 paginiata de 24 ianuarie a...

1 comentariu

• 13:57 - Barbat impuscat aproape de un poligon militar - cum raspunde MApN

• 13:51 - Cum arata Dr. House in tinerete (Foto)

Mircea Lucescu, misiune imposibila in Turcia? Un italian dezvaluie ce il asteapta la Galatasaray

13:45 - Mircea Lucescu, misiune imposibila in Turcia? Un italian dezvaluie ce il asteapta la Galatasaray

Mircea Lucescu ar putea avea o misiune imposibila in Turcia, daca va ajunge in cele din urma la Galatasaray. Omul care l-a dus pe Roberto Mancini la Istanbul, Nicola Innocentin, a dezvaluit...

• 13:40 - Povesti de succes care te vor ajuta in cariera

• 13:33 - Luis Felipe Scolari, despre penaltiul primit de Brazilia

• 13:26 - Curs euro-leu: Euro isi revine usor, dar ramane sub pragul de 4,40 lei

Drepturi de autor

© © All Rights Reserved

Formate disponibile

PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentata de 24 ianuarie a...

1 comentariu

• 13:57 - Barbat impuscat aproape de un poligon militar - cum raspunde MApN

• 13:51 - Cum arata Dr. House in tinerete (Foto)

Mircea Lucescu, misiune imposibila in Turcia? Un italian dezvaluie ce il asteapta la Galatasaray

13:45 - Mircea Lucescu, misiune imposibila in Turcia? Un italian dezvaluie ce il asteapta la Galatasaray

Mircea Lucescu ar putea avea o misiune imposibila in Turcia, daca va ajunge in cele din urma la Galatasaray. Omul care l-a dus pe Roberto Mancini la Istanbul, Nicola Innocentin, a dezvaluit...

• 13:40 - Povesti de succes care te vor ajuta in cariera

• 13:33 - Luis Felipe Scolari, despre penaltiul primit de Brazilia

• 13:26 - Curs euro-leu: Euro isi revine usor, dar ramane sub pragul de 4,40 lei

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

70 vizualizări8 paginiChapter 05 Graphics Accelerator (SGX)

Încărcat de

yiutkmvjkqata de 24 ianuarie a...

1 comentariu

• 13:57 - Barbat impuscat aproape de un poligon militar - cum raspunde MApN

• 13:51 - Cum arata Dr. House in tinerete (Foto)

Mircea Lucescu, misiune imposibila in Turcia? Un italian dezvaluie ce il asteapta la Galatasaray

13:45 - Mircea Lucescu, misiune imposibila in Turcia? Un italian dezvaluie ce il asteapta la Galatasaray

Mircea Lucescu ar putea avea o misiune imposibila in Turcia, daca va ajunge in cele din urma la Galatasaray. Omul care l-a dus pe Roberto Mancini la Istanbul, Nicola Innocentin, a dezvaluit...

• 13:40 - Povesti de succes care te vor ajuta in cariera

• 13:33 - Luis Felipe Scolari, despre penaltiul primit de Brazilia

• 13:26 - Curs euro-leu: Euro isi revine usor, dar ramane sub pragul de 4,40 lei

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 8

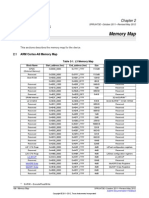

Chapter 5

SPRUH73EOctober 2011Revised May 2012

Graphics Accelerator (SGX)

This chapter describes the graphics accelerator for the device.

Topic ........................................................................................................................... Page

5.1 Introduction .................................................................................................... 184

5.2 Integration ...................................................................................................... 187

5.3 Functional Description ..................................................................................... 189

183 SPRUH73EOctober 2011Revised May 2012 Graphics Accelerator (SGX)

Submit Documentation Feedback

Copyright 20112012, Texas Instruments Incorporated

Introduction www.ti.com

5.1 Introduction

This chapter describes the 2D/3D graphics accelerator (SGX) for the device.

NOTE: The SGX subsystem is a Texas Instruments instantiation of the POWERVR

SGX530 core

from Imagination Technologies Ltd.

This document contains materials that are 2003-2007 Imagination Technologies Ltd.

POWERVR

and USSE are trademarks or registered trademarks of Imagination

Technologies Ltd.

The 2D/3D graphics accelerator (SGX) subsystem accelerates 2-dimensional (2D) and 3-dimensional (3D)

graphics applications. The SGX subsystem is based on the POWERVR

SGX core from Imagination

Technologies. SGX is a new generation of programmable POWERVR graphic cores. The POWERVR

SGX530 v1.2.5 architecture is scalable and can target all market segments from mainstream mobile

devices to high-end desktop graphics. Targeted applications include feature phone, PDA, and hand-held

games.

5.1.1 POWERVR SGX Main Features

2D graphics, 3D graphics, vector graphics, and programming support for GP-GPU functions

Tile-based architecture

Universal scalable shader engine ( USSE) multithreaded engine incorporating pixel and vertex

shader functionality

Advanced shader feature set in excess of Microsoft VS3.0, PS3.0, and OpenGL2.0

Industry-standard API support Direct3D Mobile, OpenGL ES 1.1 and 2.0, OpenVG v1.0.1

Fine-grained task switching, load balancing, and power management

Advanced geometry direct memory access (DMA) driven operation for minimum CPU interaction

Programmable high-quality image anti-aliasing

POWERVR SGX core MMU for address translation from the core virtual address to the external

physical address (up to 4GB address range)

Fully virtualized memory addressing for OS operation in a unified memory architecture

Advanced and standard 2D operations [e.g., vector graphics, BLTs (block level transfers), ROPs

(raster operations)]

32K stride support

5.1.2 SGX 3D Features

Deferred pixel shading

On-chip tile floating point depth buffer

8-bit stencil with on-chip tile stencil buffer

8 parallel depth/stencil tests per clock

Scissor test

Texture support:

Cube map

Projected textures

2D textures

Nonsquare textures

Texture formats:

RGBA 8888, 565, 1555

Monochromatic 8, 16, 16f, 32f, 32int

Dual channel, 8:8, 16:16, 16f:16f

184 Graphics Accelerator (SGX) SPRUH73EOctober 2011Revised May 2012

Submit Documentation Feedback

Copyright 20112012, Texas Instruments Incorporated

www.ti.com Introduction

Compressed textures PVR-TC1, PVR-TC2, ETC1

Programmable support for all YUV formats

Resolution support:

Frame buffer maximum size = 2048 x 2048

Texture maximum size = 2048 x 2048

Texture filtering:

Bilinear, trilinear, anisotropic

Independent minimum and maximum control

Antialiasing:

4x multisampling

Up to 16x full scene anti-aliasing

Programmable sample positions

Indexed primitive list support

Bus mastered

Programmable vertex DMA

Render to texture:

Including twiddled formats

Auto MipMap generation

Multiple on-chip render targets (MRT).

Note: Performance is limited when the on-chip memory is not available.

5.1.3 Universal Scalable Shader Engine (USSE) Key Features

The USSE is the engine core of the POWERVR SGX architecture and supports a broad range of

instructions.

Single programming model:

Multithreaded with 16 simultaneous execution threads and up to 64 simultaneous data instances

Zero-cost swapping in, and out, of threads

Cached program execution model

Dedicated pixel processing instructions

Dedicated video encode/decode instructions

SIMD execution unit supporting operations in:

32-bit IEEE float

2-way 16-bit fixed point

4-way 8-bit integer

32-bit bit-wise (logical only)

Static and dynamic flow control:

Subroutine calls

Loops

Conditional branches

Zero-cost instruction predication

Procedural geometry:

Allows generation of primitives

Effective geometry compression

High-order surface support

External data access:

Permits reads from main memory using cache

185 SPRUH73EOctober 2011Revised May 2012 Graphics Accelerator (SGX)

Submit Documentation Feedback

Copyright 20112012, Texas Instruments Incorporated

Introduction www.ti.com

Permits writes to main memory

Data fence facility

Dependent texture reads

5.1.4 Unsupported Features

There are no unsupported SGX530 features for this device.

186 Graphics Accelerator (SGX) SPRUH73EOctober 2011Revised May 2012

Submit Documentation Feedback

Copyright 20112012, Texas Instruments Incorporated

GFX Subsystem

THALIAIRQ

MPU Subsystem

Interrupts

CORECLK

PRCM

Master

Slave

L3 Fast

Interconnect

L3 Fast

Interconnect

MEMCLK

SYSCLK

/1, /2

pd_gfx_gfx_fclk

pd_gfx_gfx_l3_gclk

PER_CLKOUTM2

(192 MHz)

CORE_CLKOUTM4

(200 MHz)

1

0

www.ti.com Integration

5.2 Integration

Figure 5-1. SGX530 Integration

5.2.1 SGX530 Connectivity Attributes

The general connectivity attributes of the SGX530 are shown in the following table.

Table 5-1. SGX530 Connectivity Attributes

Attributes Type

Power domain GFX Domain

Clock domain SGX_CLK

Reset signals SGX_RST

Idle/Wakeup signals Smart Idle

Initiator Standby

Interrupt request THALIAIRQ (GFXINT) to MPU Subsystem

DMA request None

Physical address L3 Fast slave port

5.2.2 SGX530 Clock and Reset Management

The SGX530 uses separate functional and interface clocks. The SYSCLK is the clock for the slave

interface and runs at the L3F frequency. The MEMCLK is the clock for the memories and master interface

and also runs at the L3F frequency. The CORECLK is the functional clock. It can be sourced from either

the L3F clock (CORE_CLKOUTM4) or from the 192 MHz PER_CLKOUTM2 and can optionally be divided

by 2.

Table 5-2. SGX530 Clock Signals

Clock signal Max Freq Reference / Source Comments

SYSCLK 200 MHz CORE_CLKOUTM4 pd_gfx_gfx_l3_gclk

Interface clock From PRCM

MEMCLK 200 MHz CORE_CLKOUTM4 pd_gfx_gfx_l3_gclk

Memory Clock From PRCM

CORECLK 200 MHz PER_CLKOUTM2 or pd_gfx_gfx_fclk

Functional clock CORE_CLKOUTM4 From PRCM

187 SPRUH73EOctober 2011Revised May 2012 Graphics Accelerator (SGX)

Submit Documentation Feedback

Copyright 20112012, Texas Instruments Incorporated

Integration www.ti.com

5.2.3 SGX530 Pin List

The SGX530 module does not include any external interface pins.

188 Graphics Accelerator (SGX) SPRUH73EOctober 2011Revised May 2012

Submit Documentation Feedback

Copyright 20112012, Texas Instruments Incorporated

Coarse-grain

scheduler

Prog. data

sequencer

Data master

selector

Vertex data

master

Pixel data

master

General-purpose

data master

Universal

scalable

shader

engine

(USSE)

Tiling

coprocessor

Pixel

coprocessor

Multilevel cache

Texturing coprocessor Power

management

control

register

block

SOCIF

BIF

L3 interconnect L3 interconnect

POWERVR

SGX530

sgx-003

MMU

www.ti.com Functional Description

5.3 Functional Description

5.3.1 SGX Block Diagram

The SGX subsystem is based on the POWERVR SGX530 core from Imagination Technologies. The

architecture uses programmable and hard coded pipelines to perform various processing tasks required in

2D, 3D, and video processing. The SGX architecture comprises the following elements:

Coarse grain scheduler

Programmable data sequencer (PDS)

Data master selector (DMS)

Vertex data master (VDM)

Pixel data master (PDM)

General-purpose data master

USSE

Tiling coprocessor

Pixel coprocessor

Texturing coprocessor

Multilevel cache

Figure 5-2 shows a block diagram of the SGX cores.

Figure 5-2. SGX Block Diagram

5.3.2 SGX Elements Description

The coarse grain scheduler (CGS) is the main system controller for the POWERVR SGX architecture. It

consists of two stages, the DMS and the PDS. The DMS processes requests from the data masters and

determines which tasks can be executed given the resource requirements. The PDS then controls the

loading and processing of data on the USSE.

There are three data masters in the SGX core:

The VDM is the initiator of transform and lighting processing within the system. The VDM reads an

189 SPRUH73EOctober 2011Revised May 2012 Graphics Accelerator (SGX)

Submit Documentation Feedback

Copyright 20112012, Texas Instruments Incorporated

Functional Description www.ti.com

input control stream, which contains triangle index data and state data. The state data indicates the

PDS program, size of the vertices, and the amount of USSE output buffer resource available to the

VDM. The triangle data is parsed to determine unique indices that must be processed by the USSE.

These are grouped together according to the configuration provided by the driver and presented to the

DMS.

The PDM is the initiator of rasterization processing within the system. Each pixel pipeline processes

pixels for a different half of a given tile, which allows for optimum efficiency within each pipe due to

locality of data. It determines the amount of resource required within the USSE for each task. It merges

this with the state address and issues a request to the DMS for execution on the USSE.

The general-purpose data master responds to events within the system (such as end of a pass of

triangles from the ISP, end of a tile from the ISP, end of render, or parameter stream breakpoint

event). Each event causes either an interrupt to the host or synchronized execution of a program on

the PDS. The program may, or may not cause a subsequent task to be executed on the USSE.

The USSE is a user-programmable processing unit. Although general in nature, its instructions and

features are optimized for three types of task: processing vertices (vertex shading), processing pixels

(pixel shading), and video/imaging processing.

The multilevel cache is a 2-level cache consisting of two modules: the main cache and the

mux/arbiter/demux/decompression unit (MADD). The MADD is a wrapper around the main cache module

designed to manage and format requests to and from the cache, as well as providing Level 0 caching for

texture and USSE requests. The MADD can accept requests from the PDS, USSE, and texture address

generator modules. Arbitration, as well as any required texture decompression, are performed between

the three data streams.

The texturing coprocessor performs texture address generation and formatting of texture data. It receives

requests from either the iterators or USSE modules and translates these into requests in the multilevel

cache. Data returned from the cache are then formatted according to the texture format selected, and sent

to the USSE for pixel-shading operations.

To process pixels in a tiled manner, the screen is divided into tiles and arranged as groups of tiles by the

tiling coprocessor. An inherent advantage of tiling architecture is that a large amount of vertex data can be

rejected at this stage, thus reducing the memory storage requirements and the amount of pixel processing

to be performed.

The pixel coprocessor is the final stage of the pixel-processing pipeline and controls the format of the final

pixel data sent to the memory. It supplies the USSE with an address into the output buffer and then USSE

returns the relevant pixel data. The address order is determined by the frame buffer mode. The pixel

coprocessor contains a dithering and packing function.

190 Graphics Accelerator (SGX) SPRUH73EOctober 2011Revised May 2012

Submit Documentation Feedback

Copyright 20112012, Texas Instruments Incorporated

S-ar putea să vă placă și

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- Alpine Racer 52in ManualDocument50 paginiAlpine Racer 52in ManualyiutkmvjkqÎncă nu există evaluări

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (400)

- Alpine Racer 46in ManualDocument51 paginiAlpine Racer 46in ManualyiutkmvjkqÎncă nu există evaluări

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Alpine Racer 2 ManualDocument45 paginiAlpine Racer 2 ManualyiutkmvjkqÎncă nu există evaluări

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- Alpine Racer InstallDocument21 paginiAlpine Racer InstallyiutkmvjkqÎncă nu există evaluări

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- AceDriver OperationDocument98 paginiAceDriver OperationyiutkmvjkqÎncă nu există evaluări

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- Aim For Cash ManualDocument74 paginiAim For Cash ManualyiutkmvjkqÎncă nu există evaluări

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Uk - FTSE Index CalculationDocument34 paginiUk - FTSE Index Calculationedzhang111Încă nu există evaluări

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- AceDriver InstallationDocument31 paginiAceDriver InstallationyiutkmvjkqÎncă nu există evaluări

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- Chapter 04 Programmable Real-Time Unit and Industrial Communication Subsystem (PRU-ICSS)Document2 paginiChapter 04 Programmable Real-Time Unit and Industrial Communication Subsystem (PRU-ICSS)yiutkmvjkqÎncă nu există evaluări

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (74)

- Chapter 06 InterruptsDocument195 paginiChapter 06 InterruptsyiutkmvjkqÎncă nu există evaluări

- Chapter 02 Memory MapDocument11 paginiChapter 02 Memory MapyiutkmvjkqÎncă nu există evaluări

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Chapter 03 ARM MPU SubsystemDocument12 paginiChapter 03 ARM MPU SubsystemkzillaÎncă nu există evaluări

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- 00 Cover & ContentsDocument152 pagini00 Cover & ContentsyiutkmvjkqÎncă nu există evaluări

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- 00 Read This FirstDocument1 pagină00 Read This FirstyiutkmvjkqÎncă nu există evaluări

- 00 Cover & ContentsDocument152 pagini00 Cover & ContentsyiutkmvjkqÎncă nu există evaluări

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- DLD MCQ WebsiteDocument43 paginiDLD MCQ WebsiteShoaibakhtar AkhtarkaleemÎncă nu există evaluări

- 04 Mid-Term Report FormatDocument25 pagini04 Mid-Term Report FormatNationalinstituteDsnrÎncă nu există evaluări

- 113 Service Manual - Travelmate 2200 2700 Aspire 1670Document137 pagini113 Service Manual - Travelmate 2200 2700 Aspire 1670Soporte Tecnico Buenos AiresÎncă nu există evaluări

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- M4 AtxDocument4 paginiM4 AtxLuis E AlvaradoÎncă nu există evaluări

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- 64Mb Synchronous DRAM Specification: A3V64S40GTPDocument40 pagini64Mb Synchronous DRAM Specification: A3V64S40GTPJeferson AndradeÎncă nu există evaluări

- Exercise 1Document3 paginiExercise 1Kaka Hiếu100% (1)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- Assignment 3 Attempt Any 5 Question and Submit It On BB Submission Is 15 Jan, 2022Document5 paginiAssignment 3 Attempt Any 5 Question and Submit It On BB Submission Is 15 Jan, 2022EakanshÎncă nu există evaluări

- Chapter 10 Serial PortDocument37 paginiChapter 10 Serial Portanses1000Încă nu există evaluări

- Chipscope Ibert Virtex5 GTXDocument7 paginiChipscope Ibert Virtex5 GTXAbdul Salim NÎncă nu există evaluări

- FUSIONDocument11 paginiFUSIONRodrigoHuamanÎncă nu există evaluări

- 3vsb Should Be Volts Motherboard - Google SearchDocument2 pagini3vsb Should Be Volts Motherboard - Google Searchoff emÎncă nu există evaluări

- Eee421: Power Electronics: Power Semiconductor Devices: MOSFETDocument9 paginiEee421: Power Electronics: Power Semiconductor Devices: MOSFETRafat ShamsÎncă nu există evaluări

- Digital System Design Using Verilog December 2011Document1 paginăDigital System Design Using Verilog December 2011Vinayaka HmÎncă nu există evaluări

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- C Amit Siemens GE ComparisonsDocument13 paginiC Amit Siemens GE ComparisonsNaveen KumarÎncă nu există evaluări

- A55F-M4 V1.0 - Manual PDFDocument72 paginiA55F-M4 V1.0 - Manual PDFcomando2009Încă nu există evaluări

- Designing With The 80C51BH - Application Note AP252 - 27006802Document28 paginiDesigning With The 80C51BH - Application Note AP252 - 27006802anon_3859610210% (1)

- Sun Fire X4140 Service Diagnostic GuideDocument80 paginiSun Fire X4140 Service Diagnostic GuidePeterÎncă nu există evaluări

- E2234 P5nsli PDFDocument124 paginiE2234 P5nsli PDFSIGOYROSÎncă nu există evaluări

- 3.1 Addressing Modes: ECP2036 Microprocessors System and Interfacing Chapter 3: The 8051 Instruction SetDocument6 pagini3.1 Addressing Modes: ECP2036 Microprocessors System and Interfacing Chapter 3: The 8051 Instruction SetSwetha ChinnikannuÎncă nu există evaluări

- Bus ArbitrationDocument13 paginiBus ArbitrationParas ChughÎncă nu există evaluări

- Power PC and Intel's EvolutionDocument22 paginiPower PC and Intel's EvolutionohmsresistanceÎncă nu există evaluări

- Vanttl PDFDocument48 paginiVanttl PDFmarioasensicollantesÎncă nu există evaluări

- 80 C 535Document56 pagini80 C 535MÜhammadFIkriÎncă nu există evaluări

- Unit 4 (4.1) Micropgm Control-FinalDocument10 paginiUnit 4 (4.1) Micropgm Control-FinalSahil KukrejaÎncă nu există evaluări

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- HP6622 SupplyDocument161 paginiHP6622 SupplyMikre23Încă nu există evaluări

- Sensors and MeasurementsDocument8 paginiSensors and Measurementsvasanthmech092664Încă nu există evaluări

- 8085 Architecture: Microcomputer, Microprocessors & Microcontroller Inside The MicroprocessorDocument44 pagini8085 Architecture: Microcomputer, Microprocessors & Microcontroller Inside The MicroprocessorJai Narayan GuptaÎncă nu există evaluări

- Uart - Project PresentationDocument23 paginiUart - Project PresentationGagandeep VirdiÎncă nu există evaluări

- 8051 Interfacing LCD 16x2Document14 pagini8051 Interfacing LCD 16x2Imran Shaukat100% (3)

- IntelDocument10 paginiIntelvarudhinich0% (1)