Documente Academic

Documente Profesional

Documente Cultură

Pulse & Digital Circuits Lab Manual

Încărcat de

Kcbalaji ChinnathambuDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Pulse & Digital Circuits Lab Manual

Încărcat de

Kcbalaji ChinnathambuDrepturi de autor:

Formate disponibile

MADANAPALLE INSTITUTE OF TECHNOLOGY &

SCIENCE

MADANAPALLI

ANGALLU, MADANAPALLE 517 325

PULSE AND DIGITAL CIRCUITS

LABORATORY MASTER MANUAL

DEPARTMENT

OF

ELECTRONICS & COMMUNICATION ENGINEERING

JULY- 2013

Faculty in Charge: HOD, ECE:

P.R.Ratna Raju .K, Department of ECE, MITS Page 1

MADANAPALLE INSTITUTE OF

TECHNOLOGY &SCIENCE,

Department of ECE

PULSE AND DIGITAL CIRCUITS

STUDENT LAB MANUAL

Prepared By

Mr. P.R.RATNA RAJU.K, M.Tech,

Asst. Professor,

Department of ECE,

MITS.

P.R.Ratna Raju .K, Department of ECE, MITS Page 2

JAWAHARLAL NEHRU

TECHNOLOGICAL UNIVERSITY ANANTAPUR

Electronics and Communication Engineering

(9A04506) PULSE & DIGITAL CIRCUITS LAB

(Common to ECE, E Con E, EIE)

B.Tech III-I Sem. (E.C.E.)

Minimum Twelve experiments to be conducted:

1. Linear wave shaping.

2. Non Linear wave shaping Clippers.

3. Non Linear wave shaping Clampers.

4. Transistor as a switch.

5. Study of Logic Gates & Some applications.

6. Study of Flip-Flops & some applications.

7. Sampling Gates.

8. Astable Multivibrator.

9. Monostable Multivibrator.

10. Bistable Multivibrator.

11. Schmitt Trigger.

12. UJT Relaxation Oscillator.

13. Bootstrap sweep circuit.

14. Constant Current Sweep Generator using BJT.

Equipment required for Laboratories:

1. RPS - 0 30 V

2. CRO - 0 20 M Hz.

3. Function Generators - 0 1 M Hz

4. Components

5. Multi Meters

P.R.Ratna Raju .K, Department of ECE, MITS Page 3

PULSE AND DIGITAL CIRCUITS LAB

LIST OF EXPERIMENTS

1. Linear wave shaping.

2. Non Linear wave shaping Clippers.

3. Non Linear wave shaping Clampers.

4. Transistor as a switch.

5. Study of Logic Gates & Some applications.

6. Study of Flip-Flops & some applications

7. Sampling Gates.

8. Astable Multivibrator.

9. Monostable Multivibrator.

10. Bistable Multivibrator.

11. Schmitt Trigger.

12. UJT Relaxation Oscillator.

Additional Experiments:

13. TTL NAND GATE

14. ECL NOR GATE

Advanced Experiments:

15. CMOS NAND GATE,

16.CMOS TRANSMISSION GATE

P.R.Ratna Raju .K, Department of ECE, MITS Page 4

EXP.NO DATE Experiment Name Page No Remarks

1 Linear wave shaping.

2 Non Linear wave shaping Clippers.

3 Non Linear wave shaping Clampers.

4 Transistor as a switch.

5 Study of Logic Gates & Some

applications.

6 Study of Flip-Flops & some

applications

7 UJT Relaxation Oscillator.

8 Astable Multivibrator.

9 Monostable Multivibrator.

10 Bistable Multivibrator.

11 Schmitt Trigger.

12 Sampling Gates.

13

TTL NAND GATE

14

ECL NOR GATE

15

CMOS NAND GATE

16

CMOS TRANSMISSION GATE

P.R.Ratna Raju .K, Department of ECE, MITS Page 5

1. LINEAR WAVESHAPING

A.INTEGRATOR

AIM: To Design RC integrator circuit, calculate rise times theoretically, observe the

response of RC integrator circuit for a square wave input for different time constants

i) RC>>T ii) RC = T iii) RC<<T and to determine rise time for RC<<T

APPARATUS:

S.No Name of the

component/Equipments

Specification Quantity

1. Resistors 100 1

1k 1

10K 1

2. Capacitors 0.1uf 1

3. Bread board 1

4. Connecting wires 1 Bunch

5. Function generator 1

6. CRO 1

CIRCUIT DIAGRAM:

Figure 1: RC Integrator circuit

P.R.Ratna Raju .K, Department of ECE, MITS Page 6

MODEL WAVE FORMS:

OBSERVATIONS:

V

i

(volts) R(K) C( F) RC(m sec) T(m sec) V

o

(volts)

DESIGN:

1. Choose T = 1msec.

2. Select C = 0.1F.

3. For RC = T; select R.

4. For RC >> T; select R.

5. For RC << T; select R.

P.R.Ratna Raju .K, Department of ECE, MITS Page 7

THEORY:

PROCEDURE:

1. Connect the circuit as shown in the figure1.

2. Connect the function generator at the input terminals and CRO at the output

terminals of the circuit.

3. Apply a square wave signal of frequency 1 KHz at the input. (T = 1 msec.)

4. Observe the output waveform of the circuit for different time constants.

5. Calculate the rise time for low pass filter and compare with the theoretical

values.

6. For low pass filter select rise time (t

r

) = 2.2 RC (theoretical). The rise time is

defined as the time taken by the output voltage to rise from 0.1 to 0.9 of its

final value.

PRECAUTIONS:

1. Connections should be tight.

2. Take care when biasing the supply.

RESULT:

VIVA QUESTIONS:

1. What is high pass circuit under what condition it acts as a differentiator?

2. What is low pass circuit under what condition it acts as a integrator?

3. Show theoretically how you get a triangular wave when a square wave is

given to an integrator?

4. What happens when a sine wave is applied to a differentiator or integrator

circuit?

5. What are different applications of a differentiator?

6. What are different applications of a integrator?

7. What is the ideal value of phase shift offered by an RC circuit?

P.R.Ratna Raju .K, Department of ECE, MITS Page 8

Integrator output with RC 1msec

P.R.Ratna Raju .K, Department of ECE, MITS Page 9

1 (B) .DIFFERENTIATOR

AIM: Design RC differentiator circuit, calculate percentage of tilt, observe the

response of the circuit for a square input with different time constants

i) RC>>T ii) RC = T iii) RC<<T and to determine percentage tilt for RC = T

APPARATUS:

S.No Name of the

component/Equipments

Specification Quantity

1. Resistors 100 K 1

1k 1

10K 1

2. Capacitors 0.1uf 1

3. Bread board 1

4. Connecting wires 1 Bunch

5. Function generator 1

6. CRO 1

CIRCUIT DIAGRAM:

Figure 2: RC Differentiator circuit

P.R.Ratna Raju .K, Department of ECE, MITS Page 10

MODEL WAVE FORMS:

OBSERVATIONS:

V

i

(volts) R(K) C( F) RC(m sec) T(m sec) V

o

(volts)

DESIGN:

1. Choose T = 1msec.

2. Select C = 0.1F.

3. For RC = T; select R.

4. For RC >> T; select R.

5. For RC << T; select R.

P.R.Ratna Raju .K, Department of ECE, MITS Page 11

THEORY:

PROCEDURE:

1. Connect the circuit as shown in the figure2.

2. Connect the function generator at the input terminals and CRO at the output

terminals of the circuit.

3. Apply a square wave signal of frequency 1 KHz at the input. (T = 1 msec.)

4. Observe the output waveform of the circuit for different time constants.

5. Calculate the %tilt for high pass filter and compare with the theoretical values.

6. % *100

2

T

Tilt

RC

= %

'

1 1

% *100

( / 2)

V V

Tilt

V

(

=

(

(theoretical)

'

1 1

% *100

( / 2)

V V

Tilt

V

(

=

(

% (practical)

PRECAUTIONS:

1. Connections should be tight.

2. Take care when biasing the supply.

RESULT:

Differentiator output at RC=1m sec.

P.R.Ratna Raju .K, Department of ECE, MITS Page 12

2 . NON-LINEAR WAVE SHAPING - CLIPPERS

AIM: Design, obtain voltage transfer characteristics, plot input and output

waveforms for different clipping circuits with different reference voltages and to

verify the responses of

(I) Shunt diode positive voltage clipper to clip at 1.6V.

(II) Shunt diode negative voltage clipper to clip at -0.4V.

(III) series diode positive voltage clipper to clip at 1V.

(IV) series diode negative voltage clipper to clip at 1V

(V) A two level voltage clipper to clip at +3.6V and -3.6 V

APPARATUS:

S.No Name of the

component/Equipments

Specification Quantity

1. Resistors 1k 1

2. Diodes 1N4007 2

3. Bread board 1

4. Connecting wires 1 Bunch

5. Function generator 1

6. CRO 1

7. Regulated Power Supply 1

P.R.Ratna Raju .K, Department of ECE, MITS Page 13

CIRCUIT DIAGRAMS:

1. Shunt diode positive clipper

Figure :1

DC Transfer characteristics:

Input& output waveforms:

P.R.Ratna Raju .K, Department of ECE, MITS Page 14

2. Shunt diode negative clipper

Figure : 2

DC Transfer characteristics:

Input& output waveforms:

P.R.Ratna Raju .K, Department of ECE, MITS Page 15

3. Series diode positive clipper

Figure :3

DC Transfer characteristics:

Input& output waveforms:

P.R.Ratna Raju .K, Department of ECE, MITS Page 16

4. Series diode negative clipper

Figure :4

DC Transfer characteristics:

Input& output waveforms:

P.R.Ratna Raju .K, Department of ECE, MITS Page 17

5. Two level clipper

Figure:5

DC Transfer characteristics:

Input& output waveforms:

P.R.Ratna Raju .K, Department of ECE, MITS Page 18

THEORY:

PROCEDURE:

1. Connect the circuit as shown in the figure 1.

2. Connect the function generator at the input terminals and CRO at the output

terminals of the circuit.

3. Apply a sine wave signal of frequency 1 KHz, Amplitude greater than the

reference voltage at the Input and observe the output waveforms of the circuits.

4. Repeat the procedure for remaining circuits.

PRECAUTIONS:

1. Connections should be tight.

2. Take care when applying proper supply.

RESULT:

IVA QUESTIONS:

1. Define clipping?

2. What are the applications of clippers?

3. Define peak inverse voltage of diode?

4. What are the other names for the clippers?

5. Explain the clipping process?

P.R.Ratna Raju .K, Department of ECE, MITS Page 19

3. NON-LINEAR WAVESHAPING - CLAMPERS

AIM: Design following clamper circuits, verify output waveforms and plot them.

(I) Positive clamper (II) Negative clamper. (III) Positive clamper with a +2V,

(IV) Negative clamper with a -2V.

APPARATUS:

1. Diode 1N4001 1 No

2. Capacitor 0.1 F

3. Resistor - 1K O

4. Function Generator

5. RPS

6. CRO

CIRCUIT DIAGRAMS:

1. POSITIVE CLAMPER

Input& output waveforms:

P.R.Ratna Raju .K, Department of ECE, MITS Page 20

2. NEGATIVE CLAMPER

Input& output waveforms:

3 POSITIVE CLAMPER with 2V

P.R.Ratna Raju .K, Department of ECE, MITS Page 21

Input& output waveforms:

4.NEGATIVE CLAMPER WITH -2V

Input& output waveforms:

P.R.Ratna Raju .K, Department of ECE, MITS Page 22

THEORY:

PROCEDURE:

1. Connections are made as per the circuit diagram.

2. I/P signal is applied to the circuit with the amplitude of 4v p-p and 1 KHz

frequency.

3. The AC / DC push button switch of CRO is to be kept in DC mode.

4. Note down the o/p amplitude for each and every circuit.

5. The O/P waveforms are to be drawn on the graph sheet.

RESULT:

VIVA QUESTIONS:

1. Define clipping?

2. Define clamping?

3. Define peak inverse voltage of diode?

4. Draw the o/p wave forms for

1. +ve clamper

2. ve clamper

5. What are the other names for the clamper?

6. What are the applications of clampers?

7. Explain the clipping process?

P.R.Ratna Raju .K, Department of ECE, MITS Page 23

4.TRANSISTOR AS A SWITCH

AIM: Design a switch using BJT to switch LED, and observe the waveform, note

down Vce, Vbe ON & Voff values.

APPARATUS:

S.No Name of the component Specification Quantity

1. Resistors 1

2.4k 1

2. Transistor BC 107 1

3. Bread board 1

4. Connecting wires 1 Bunch

5. Function generator 1

6. CRO 1

7. Dual Regulated Power supply (0-30) V DC 1

8. LED 1

CIRCUIT DIAGRAMS:

Figure:1

P.R.Ratna Raju .K, Department of ECE, MITS Page 24

MODEL WAVE FORMS:

OBSERVATIONS:

V

BE

(Volts) V

CE

(Volts) V

CB

(Volts)

1.When Transistor is ON

2. When Transistor is OFF

DESIGN :I

c max

= , V

BE

= , V

CE

(sat)

= , V

cc

=

R

c min

= V

CC

/ Ic max=

I

CS

= (V

CC

V

CE

(sat)

) / Rc =

I

B

= I

CS

/ h

fe

=(V

i

-V

BE

)/R

B=

(h

fe

= )

R

B

= ( V

i

V

BE

) / I

B=

THEORY:

P.R.Ratna Raju .K, Department of ECE, MITS Page 25

PROCEDURE :

1. Connect the circuit as shown in the figure 1.

2. Connect 5V power supply to VCC and 0V to the input terminals.

3. Measure the voltage (a) across collector to emitter terminals, (b) across

collector to base terminals and (c) Base to emitter terminals.

4. Connect 5V to the input terminals.

5. Measure the voltage (a) across collector to emitter terminals, (b) across

collector to base terminals and (c) Base to emitter terminals.

6. Observe that the LED glows when the input terminals are supplied with 0 volts.

The LED will NOT glow when the input voltage is 5V.

7. Remove the load (1kand LED) and DC power supply (connected between

RB and Gnd.). Now connect a function generator to the input terminals.

8. Apply Square wave of 1 KHz, V (p-p) is 5V

9. Observe the waveforms at the input terminals and across collector and ground.

10. Plot the waveform on a graph sheet. Note the inversion of the signal from input to

output.

RESULT:

VIVA QUESTIONS:

1. What are the different switching times of a transistor?

2. Define ON time of a transistor?

3. Define OFF time of a transistor?

4. Explain how transistor acts as a switch?

5. Define delay time (td), raise time (tr), saturation time (ts) and fall time (tf) of a

transistor?

P.R.Ratna Raju .K, Department of ECE, MITS Page 26

5. STUDY OF LOGIC GATES & SOME APPLICATIONS

STUDY OF LOGIC GATES

AIM: To verify the truth tables of AND, OR, NOT, NAND, NOR, and EX-OR

gates.

APPARATUS:

1. Bread board IC trainer

2. IC74LS08 (AND)

3. IC74LS32 (OR)

4. IC 74LS04 (NOT)

5. IC74LS00 (NAND)

6. IC74LS02 (NOR)

7. IC74LS86 (EX-OR)

8. Patch cards

CIRCUIT DIAGRAM

AND GATE IC OR GATE IC

NOT GATE IC NAND GATE IC

P.R.Ratna Raju .K, Department of ECE, MITS Page 27

NOR GATE IC EX-OR GATE IC

OBSERVATIONS:

AND GATE

OR GATE

A B Y

0 0

0 1

1 0

1 1

NAND GATE NOR GATE

EX-OR GATE EX-NOR GATE

THEORY:

A B Y

0 0

0 1

1 0

1 1

A B Y

0 0

0 1

1 0

1 1

A B Y

0 0

0 1

1 0

1 1

A B Y

0 0

0 1

1 0

1 1

A B Y

0 0

0 1

1 0

1 1

P.R.Ratna Raju .K, Department of ECE, MITS Page 28

PROCEDURE:

1. +5V DC is applied at VCC (pin no:14) of each IC w.r.t. ground(pin no:7).

2. I/ps are applied (at pin nos 1 &2) and o/p is taken from (pin no:3).

3. I/ps are applied from toggle switches and o/p is observed at o/p indicators.

PRECAUTIONS:

1. Avoid loose connections on Breadboard.

2. Take care while making connections with NOT and NOR gates.

RESULT:

P.R.Ratna Raju .K, Department of ECE, MITS Page 29

5(b) APPLICATIONS

HALF ADDER, FULL ADDER AND HALF SUBTRACTOR

AIM: Design Half Adder, Full Adder and Half subtractor and verify truth table

practically.

APPRATUS:

i. IC 7432-- OR gate

ii. IC 7408--AND gate

iii. IC 7404NOT gate

iv. IC 7486EX-OR gate

v. Bread board IC trainer

vi. Patch cards

CIRCUIT DIAGRAMS:

Half adder:

Full adder:

P.R.Ratna Raju .K, Department of ECE, MITS Page 30

Half Subtractor:

THEORY:

PROCEDURE:

Half adder:

1. All the connections are made as per the circuit diagram.

2. Inputs are applied from logic inputs and outputs are observed at the output

indicators.

3. The truth table of half adder is verified.

Half Subtractor:

1. All the connections are made as per the circuit diagram.

2. Inputs are applied from logic inputs and outputs are observed at the output

indicator.

3. The truth table of half sub tractor is verified.

Full Adder:

1. All the connections are made as per the circuit diagram

2. Inputs are applied from logic inputs and outputs are observed at the output

indicator

3. The truth table of full adder is verified.

P.R.Ratna Raju .K, Department of ECE, MITS Page 31

TRUTH TABLES:

Half Adder:

Half Subtractor:

Full Adder:

INPUTS OUTPUTS

A B C SUM CARRY

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

PRECAUTIONS:

1. Connections should be correct.

2. Pin numbers should be identified properly.

RESULT:

INPUTS OUTPUTS

A B SUM CARRY

0 0

0 1

1 0

1 1

INPUTS OUTPUTS

A B DIFFERENCE BORROW

0 0

0 1

1 0

1 1

P.R.Ratna Raju .K, Department of ECE, MITS Page 32

VIVA QUESTIONS:

1. What is meant by half adder?

2. What is meant by full adder?

3. What is meant by half subtractor?

4. What is meant by 1s complement?

5. What is meant by 2s complement?

6. Why do you prefer 2s complement in computers?

7. What is Boolean expression for full adder sum and carry?

8. What is the advantage of look ahead carry adder?

9. Design full adder by using half adders?

10. What is the disadvantage of look ahead carry adder?

P.R.Ratna Raju .K, Department of ECE, MITS Page 33

6. STUDY OF FLIP FLOPS & SOME APPLICATIONS

STUDY OF FLIP FLOPS USING ICS

AIM: To construct and verify the truth tables of SR flip flop, JK flip flop, D and T

flip - flop.

APPRATUS:

i. IC 7473 JK flip flop

ii. IC 7400NAND gate

iii. IC 7404 NOT gate

iv. Patch cards

v. Connecting wires

vi. IC bread board trainer

CIRCUIT DIAGRAMS:

i) S-R FLIP-FLOP using NAND gate

ii) S-R FLIP-FLOP using NOR gate

P.R.Ratna Raju .K, Department of ECE, MITS Page 34

iii) J-K FLIP- FLOP

iv) D FLIP- FLOP

v) T FLIP- FLOP

P.R.Ratna Raju .K, Department of ECE, MITS Page 35

TRUTH TABLES:

S-R FLIP-FLOP:

Q(t) Inputs Outputs

Q(t+1) S R

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

J-K FLIP-FLOP:

Q(t) Inputs Outputs

Q(t+1) J K

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

D- FLIP-FLOP:

Q(t) D Q(t+1)

0 0

0 1

1 0

1 1

P.R.Ratna Raju .K, Department of ECE, MITS Page 36

T- FLIP-FLOP:

Q(t) T Q(t+1)

0 0

0 1

1 0

1 1

PIN DIAGRAM:

THEORY:

PROCEDURE:

1. The input S, R is given to NAND gates and clock pulse is applied between

the other two terminals and NAND gates.

2. The input of the one NAND gate is connected to the other gate and vice

versa to form SR latch.

3. The output of the NAND gate whose input is S, is connected to the input

of the other NAND gate.

4. The output of the NAND gate whose input is R, is connected to the input

of the other NAND gate whose output is Q

1

.

P.R.Ratna Raju .K, Department of ECE, MITS Page 37

J K flip-flop:

1. Connections are made as per the circuit diagram.

2. The inputs J

1

and K

1

are given to the pin numbers 14 and 3 of IC 7473.

3. Clock pulse CP1 is applied at the pin 1.

4. V

cc

and ground connections are given to the pin 4 and 11.

5. The outputs Q

1

and Q

1

bar are connected to pin 12 and 13.

D flip-flop

1. Connections are made per the circuit diagram.

2. A NOT gate is connected between the inputs J and K.

3. From JK flip flop we can obtain the D flip flop.

T flip-flop

1. Connections are made as per the circuit diagram.

2. From J K flip flop, we can obtain the T flip-flop by shorting the two inputs

J and K.

RESULT:

P.R.Ratna Raju .K, Department of ECE, MITS Page 38

6 (b) APPLICATIONS OF FLIP- FLOPS

AIM:

Design a synchronous counter using JK FF to count up to 6, and verify its truth

table..

APPARATUS:

1. J-K flip-flop(IC 7473)

2. AND gate(IC 7408)

3. Patch cards

4. Bread board trainer

5. Connecting wires

LOGIC DIAGRAM:

TRUTH TABLE

PRESENT STATE NEXT STATE OUT PUT

Q

A

Q

B

Q

C

Q

A

Q

B

Q

C

J

A

K

A

J

B

K

B

J

C

K

C

J

A

= K

A

= J

B

= K

B

= J

C

= K

C

=

P.R.Ratna Raju .K, Department of ECE, MITS Page 39

THEORY:

PROCEDURE:

1. Connect the circuit as per logic diagram shown.

2. Switch ON the Kit and note down the output.

3. Verify output sequence with truth table.

PRECAUTIONS:

1. Connections should be made carefully.

2. ICs and flip-flops should be handled carefully.

RESULT:

VIVA QUESTIONS:

1. What does meant by memory?

2. Define sequential circuits?

3. Define combinational circuits?

4. What is the difference between RS and JK flip flops

P.R.Ratna Raju .K, Department of ECE, MITS Page 40

7. UJT RELAXATION OSCILLATOR

AIM:

Design UJT relaxation oscillator at 200Hz, verify response and plot waveforms.

APPARATUS:

1. Bread board trainer

2. UJT 2N 2646

3. Resistors-(4.7k O ,47O,330O)

4. DRB

5. Capacitors-(0.1f)

6. CRO

7. Regulated power supply(0-30V)

8. Connecting wires

CIRCUIT DIAGRAM:

P.R.Ratna Raju .K, Department of ECE, MITS Page 41

MODEL WAVE FORMS:

THEORY:

THEORITICAL CALCULATIONS:

T = R

T

C

T

ln(1/(1-n) )

n = (V

P

- V

D

)/V

BB

Let =0.56 ,R

T

=24.7Kohm ,C

T

=0.1microfarad Then T=

P.R.Ratna Raju .K, Department of ECE, MITS Page 42

PROCEDURE:

1. Connections are made as per the circuit diagram.

2. The Output V

o

is noted, time period is also noted.

3. The theoretical time period should be calculated.

4. T=R

T

C

T

ln(1/1-n)

5. The Output at base 1 and base 2 should note.

6. Graph should be plotted and waveforms are drawn for V

0

, V

B1

,V

B2

.

PRECAUTIONS:

1. Connections should be tight.

2. UJT terminals are identified properly.

3. Readings can not be exceeding the limits.

RESULT:

VIVA QUESTIONS:

1. Draw the circuit symbol of double sided diode?

2. Define intrinsic-standoff ratio?

3. Define peak voltage?

4. Define valley voltage?

5. Mention the names for negative resistances devices?

P.R.Ratna Raju .K, Department of ECE, MITS Page 43

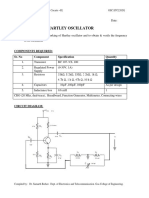

8. ASTABLE MULTIVIBRATOR

AIM: Design astable multivibrator to run at 1K Hz frequency and to observe the

response at base and collector points of the transistors and plot them.

APPARATUS:

1. Function generator.

2. Resistors (2.2 kO, 15 kO) (2 nos.)

3. Capacitors (0.047 F) (2nos.)

4. CRO

5. RPS (0-30 V)

6. Bread board

7. Connecting wires

CIRCUIT DIAGRAM:

P.R.Ratna Raju .K, Department of ECE, MITS Page 44

MODEL WAVEFORMS:

THEORY:

PROCEDURE:

1. All the connections are made as per the circuit diagram.

2. Different voltages are measured at base and collector points of two transistors

w.r.t ground as VC1, VC2, VB1 and VB2.

3. All the waveforms are plotted on the graph sheet, the amplitudes and time

periods are noted down.

4. Theoretical values of amplitudes and time periods are compared with practical

values.

P.R.Ratna Raju .K, Department of ECE, MITS Page 45

PRECAUTIONS:

1. Connections should be tight.

2. Should take care when applying proper supply.

RESULT:

VIVA QUESTIONS:

1. Define stable state of a transistor?

2. Define semi-stable state of transistor?

3. What are the other names of Astable Multivibrator?

4. Explain the operation of a Astable Multivibrator?

5. How many stable states and semi-stable states present in the Astable

Multivibrator?

6. Draw the waveforms of VC1 and VC2 of a Astable Multivibrator?

7. What is the formula for the theoretical value of T in Astable Multivibrator?

P.R.Ratna Raju .K, Department of ECE, MITS Page 46

9. MONOSTABLE MULTIVIBRATOR

AIM: Design a monostable multivibrator using transistors to generate a pulse with

500 sec and to observe the response at base and collector points of the transistors and

plot them.

APPARATUS:

1. Transistors BC107 (2 nos)

2. Breadboard trainers

3. Resistors 1kO , 10kO , 100kO

4. Capacitors 0.047F (2 nos)

5. CRO

6. Connecting wires

7. R.P.S

CIRCUIT DIAGRAM:

P.R.Ratna Raju .K, Department of ECE, MITS Page 47

MODEL WAVEFORMS:

THEORY:

THEORITICAL CALCULATIONS:

PROCEDURE:

1. Connections are made as per the circuit diagram.

2. The voltages are measured at collector and base terminals w.r.t ground by

giving the VBB of 1.5v through the 100k O resistor and the wave forms are

drawn as VC1, VC2, VB1, VB2.

3. The amplitudes and time periods of all the waveforms are noted down.

P.R.Ratna Raju .K, Department of ECE, MITS Page 48

RESULT:

VIVA QUESTIONS:

1. What are the other names of Monostable Multivibrator?

2. How many stable and semi stable states present in the Monostable

Multivibrator?

3. Explain the operation of Monostable Multivibrator?

4. What is the theoretical value of T ?

5. What is the name of base capacitor and what is the purpose of base capacitor?

P.R.Ratna Raju .K, Department of ECE, MITS Page 49

10. BISTABLE MULTIVIBRATOR

AIM: To understand the working of Bistable Multivibrator using transistors.

APPARATUS:

1. Transistors - BC107 (2 nos)

2. Breadboard trainer

3. Resistors (2.2 kO ,15 kO ,100 kO)

4. CRO

5. Capacitors - 0.047F (2 nos)

6. Connecting wires

7. R.P.S

CIRCUIT DIAGRAM:

P.R.Ratna Raju .K, Department of ECE, MITS Page 50

MODEL WAVEFORMS:

P.R.Ratna Raju .K, Department of ECE, MITS Page 51

THEORY:

PROCEDURE:

1. Connections are made as per the circuit diagram.

2. Without keeping the base resistances and with base resistances measure the

voltages at base and collector points of the two transistors T1 and T2 as VC1,

VB1 and VC2, VB2 respectively.

3. By applying the triggering voltage of 1.5V at the base terminals measure the

time period and amplitude of the waveform.

4. All the graphs are drawn on the graph sheet.

RESULT:

VIVA QUESTIONS:

1. What are the other names of Bistable Multivibrator?

2. How many stable and semi stable states present in the Bistable Multivibrator?

3. Explain the operation of Bistable Multivibrator?

4. What is the theoretical value of T?

5. What is the name of base capacitor and what is the purpose of base capacitor?

P.R.Ratna Raju .K, Department of ECE, MITS Page 52

11. SCHMITT TRIGGER

AIM: Design a Schmitt trigger circuit using transistors with UTP = 5.2V, and LTP

=3.8V. Vcc= 12V, Rc2= 1K, Rc1= 4K Rs= 1K Vbeon= 0.6V, Vbe sat= 0.8,

Re= 3K, and observe the waveforms, plot it.

APPARATUS:

1. Breadboard trainer

2. Function generator

3. Transistors BC107 - (2 nos)

4. Resistors (820O, 1.2kO , 1kO (2nos), 10kO, 150O )

5. Capacitors (0.047 F)

6. Function generator

7. CRO

8. R.P.S

CIRCUIT DIAGRAM:

P.R.Ratna Raju .K, Department of ECE, MITS Page 53

MODEL WAVE FORMS:

THEORY:

THEORITICAL CALCULATIONS:

PROCEDURE:

1. Connections are made as per the circuit diagram.

2. Fixed the i/p voltage 10v p-p at 1 KHz frequency.

3. The o/p voltage was taken at the collector point of transistor T2. w.r.t the

ground applying the bias voltage 12V.

4. The magnitudes of UTP and LTP are noted. By observing waveform on CRO.

PRECAUTIONS:

1. Connections should be tight.

2. Should take care when biasing proper supply.

RESULT:

P.R.Ratna Raju .K, Department of ECE, MITS Page 54

VIVA QUESTIONS:

1. Define upper trigger potential?

2. Define lower trigger potential?

3. Define hysterisis?

4. What are the other names of Schmitt trigger?

5. For any type of i/p what is the o/p of a Schmitt trigger?

6. Explain the operation of a Schmitt trigger?

7. What is the theoretical value of UTP?

8. What is the theoretical value of LTP?

P.R.Ratna Raju .K, Department of ECE, MITS Page 55

12. SAMPLING GATES

AIM: To construct and verify the response of sampling gate by using diode.

APPARATUS:

1. Function generator

2. CRO

3. Connecting wires

4. Resistors(1 K, 10 K)

5. Capacitor (0.047F)

6. Diode 1N4007

CIRCUIT DIAGRAM:

MODEL WAVEFORMS:

P.R.Ratna Raju .K, Department of ECE, MITS Page 56

THEORY:

PROCEDURE:

1. Connect the circuit as per circuit diagram

2. Applying both inputs (signal input and control input) simultaneously to the

circuit.

3. Repeat the second step by varying input signal and putting the control signal

fixed.

4. Note down the output waveforms for various range of input signals

PRECAUTIONS:

1. Connections should be tight.

2. Take care when applying the control signal.

RESULT:

VIVA QUESTIONS:

1. What is sampling gate?

2. Define control signal?

3. What is the other name for the control signal?

4. What is the difference between logic gates and sampling gates?

5. What is the necessity of the sampling gate?

P.R.Ratna Raju .K, Department of ECE, MITS Page 57

13. TTL NAND GATE

AIM: Simulate standard TTL NAND GATE in Multisim and find out transfer

characteristics. Estimate Noise margins, propagation delay, fan out and fan in.

APPARATUS:

Multisim

CIRCUIT DIAGRAM:

Standard TTL circuit Diagram.

Theory:

Procedure:

1. Connect the circuit as shown in circuit diagram.

2. Apply V1 & V2 individually and note down output voltage.

3. Tie V1 and V2 together, perform DC analysis and obtain DC transfer

characteristics.

4. Findout Noise margin from DC transfer characteristics.

5. Apply a clock signal at input and obtain transient response.

6. From the transient response calculate propagation delay.

P.R.Ratna Raju .K, Department of ECE, MITS Page 58

DC TRASFER CHARACTERISTICS:

Transient response:

Result:

P.R.Ratna Raju .K, Department of ECE, MITS Page 59

14. ECL NOR GATE

AIM: Simulate standard ECL NOR GATE in Multisim and find out transfer

characteristics. Estimate Noise margins, propagation delay, fan out and fan in.

APPARATUS:

Multisim

CIRCUIT DIAGRAM:

Fig: ECL NOR GATE

Theory:

P.R.Ratna Raju .K, Department of ECE, MITS Page 60

Procedure:

1. Connect the circuit as shown in circuit diagram.

2. Apply V1 & V2 individually and note down output voltage.

3. Tie V1 and V2 together, perform DC analysis and obtain DC transfer

characteristics.

4. Find out Noise margin from DC transfer characteristics.

5. Apply a clock signal at input and obtain transient response.

6. From the transient response calculate propagation delay.

Result:

S-ar putea să vă placă și

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Încă nu există evaluări

- 110 Waveform Generator Projects for the Home ConstructorDe la Everand110 Waveform Generator Projects for the Home ConstructorEvaluare: 4 din 5 stele4/5 (1)

- ECLDocument65 paginiECLAnonymous eWMnRr70qÎncă nu există evaluări

- Electronics—From Theory Into Practice: Pergamon International Library of Science, Technology, Engineering and Social StudiesDe la EverandElectronics—From Theory Into Practice: Pergamon International Library of Science, Technology, Engineering and Social StudiesEvaluare: 5 din 5 stele5/5 (2)

- Expt 5 - Wein Bridge Oscillator (2020)Document3 paginiExpt 5 - Wein Bridge Oscillator (2020)samarthÎncă nu există evaluări

- Power ElectronicsDocument83 paginiPower ElectronicsSreekanth SurendrenÎncă nu există evaluări

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1De la EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Evaluare: 4.5 din 5 stele4.5/5 (3)

- Electronic Devices and Circuits Lab NewDocument86 paginiElectronic Devices and Circuits Lab NewleevasusanÎncă nu există evaluări

- Electronics – From Theory Into Practice: Applied Electricity and Electronics DivisionDe la EverandElectronics – From Theory Into Practice: Applied Electricity and Electronics DivisionEvaluare: 5 din 5 stele5/5 (1)

- Expt 9 - Astable-Multivibrator (2020)Document5 paginiExpt 9 - Astable-Multivibrator (2020)samarth100% (1)

- Analog Circuits and Simulation LabDocument77 paginiAnalog Circuits and Simulation LableevasusanÎncă nu există evaluări

- Expt 7 - Hartley Oscillator (2020)Document4 paginiExpt 7 - Hartley Oscillator (2020)samarthÎncă nu există evaluări

- Pulse & Digital Circuits Lab Manual 3Document61 paginiPulse & Digital Circuits Lab Manual 3Suda KrishnarjunaraoÎncă nu există evaluări

- PDC Lab ManualDocument71 paginiPDC Lab Manualswapnadeepika100% (3)

- PDC Lab ManualDocument68 paginiPDC Lab Manualnama varapuÎncă nu există evaluări

- Analog Electronics LAB ManualDocument52 paginiAnalog Electronics LAB ManualPrahlad ReddyÎncă nu există evaluări

- Rajkiya Engineering College Kannauj: Electronic Circuit Design (REC 752)Document10 paginiRajkiya Engineering College Kannauj: Electronic Circuit Design (REC 752)Manjeet SinghÎncă nu există evaluări

- 117766110-PDC-Lab-Manual 4Document46 pagini117766110-PDC-Lab-Manual 4Suda KrishnarjunaraoÎncă nu există evaluări

- Linear Integrated Circuits (Lic'S) Laboratory Manual: Iii / Iv B.E (Ece), I - SemesterDocument52 paginiLinear Integrated Circuits (Lic'S) Laboratory Manual: Iii / Iv B.E (Ece), I - SemesterArun JyothiÎncă nu există evaluări

- Eca Lab-Min PDFDocument87 paginiEca Lab-Min PDFAkashita SharmaÎncă nu există evaluări

- Expt 4 RC Phase Shift Oscillator (2020)Document4 paginiExpt 4 RC Phase Shift Oscillator (2020)samarthÎncă nu există evaluări

- PDC Lab Full 2Document57 paginiPDC Lab Full 2Suda KrishnarjunaraoÎncă nu există evaluări

- Lab Manual EC II Format 2Document53 paginiLab Manual EC II Format 2nishavs100% (1)

- PDC Lab ManualDocument46 paginiPDC Lab ManualKumar Goud.K90% (10)

- Edc Lab Manuals1Document78 paginiEdc Lab Manuals1sowmiyaÎncă nu există evaluări

- Ec II Lab Manual (2013 2014)Document85 paginiEc II Lab Manual (2013 2014)surendhar1987Încă nu există evaluări

- Electronic Circuits & Logic Design Laboratory: Lab ManualDocument61 paginiElectronic Circuits & Logic Design Laboratory: Lab ManualSrihari Y.sÎncă nu există evaluări

- Analog System Design ExperimentsDocument27 paginiAnalog System Design ExperimentsAnsh BhaganiaÎncă nu există evaluări

- ECD Lab NEC 752Document17 paginiECD Lab NEC 752Ravindra Kumar0% (1)

- LINEAR INTEGRATED CIRCUITS Question BankDocument17 paginiLINEAR INTEGRATED CIRCUITS Question BankDeepak SantÎncă nu există evaluări

- ECD Lab NEC 752Document17 paginiECD Lab NEC 752pcjoshi02Încă nu există evaluări

- EPC BEC303 List of ExpsDocument51 paginiEPC BEC303 List of Expskaranphutane2254Încă nu există evaluări

- Experiment No. 4 Design of Square Wave Generator Using Op-Amp IC 741Document22 paginiExperiment No. 4 Design of Square Wave Generator Using Op-Amp IC 741aditi rajanÎncă nu există evaluări

- Lakireddy Bali Reddy College of Engineering (Document9 paginiLakireddy Bali Reddy College of Engineering (raman yarramilliÎncă nu există evaluări

- Eee312 Eee282 Lab7 Spring2015Document6 paginiEee312 Eee282 Lab7 Spring2015vognarÎncă nu există evaluări

- ECA ManualDocument50 paginiECA ManualkrajenderreddyÎncă nu există evaluări

- Ec 303Document2 paginiEc 303jeetendrasidhiÎncă nu există evaluări

- Ee2304 Lab ManualDocument49 paginiEe2304 Lab ManualSohail KhanÎncă nu există evaluări

- Power Electronics Lab ManualDocument49 paginiPower Electronics Lab ManualNeelakanth BenakalÎncă nu există evaluări

- Ic ApplicationsDocument37 paginiIc ApplicationsAllanki Sanyasi RaoÎncă nu există evaluări

- 5 SwydoverviewDocument54 pagini5 SwydoverviewAnand KumarÎncă nu există evaluări

- Department of Electrical & Electronics Engineering: Class Section Code-Subject Name of The FacultyDocument2 paginiDepartment of Electrical & Electronics Engineering: Class Section Code-Subject Name of The Facultyv srinivasÎncă nu există evaluări

- PDC NewDocument80 paginiPDC NewChinnianjali03 Chinnianjali03Încă nu există evaluări

- Kings: Question BankDocument11 paginiKings: Question BankpootommyÎncă nu există evaluări

- ENA - Lab - Manual (Update 17-4-2019) PDFDocument76 paginiENA - Lab - Manual (Update 17-4-2019) PDFMuhammad SaadÎncă nu există evaluări

- ST - Joseph College of Engineering: SriperumbudurDocument45 paginiST - Joseph College of Engineering: SriperumbudurSuryaÎncă nu există evaluări

- Ee 2254 Lic Int - 3Document2 paginiEe 2254 Lic Int - 3Ryan MillerÎncă nu există evaluări

- ECD Lab EEC 752Document17 paginiECD Lab EEC 752juhi99360% (5)

- I C and Pulse and Digital Circuits LabvbDocument81 paginiI C and Pulse and Digital Circuits LabvbGarry MehrokÎncă nu există evaluări

- Linear Wave Shaping: Department of Electronics and Communication EngineeringDocument0 paginiLinear Wave Shaping: Department of Electronics and Communication EngineeringanishadandaÎncă nu există evaluări

- EC - Lab Manul With Viva Questions and AnswersDocument83 paginiEC - Lab Manul With Viva Questions and AnswerssunandaalurÎncă nu există evaluări

- Background: 1.1 Theory About The Power ElectronicsDocument51 paginiBackground: 1.1 Theory About The Power ElectronicsEngr Syed Bilal AliÎncă nu există evaluări

- Syllabus EC321Document2 paginiSyllabus EC321Sudheer KumarÎncă nu există evaluări

- Beee Exp 7Document8 paginiBeee Exp 7aman vermaÎncă nu există evaluări

- Ec8461 Cd&si LabDocument86 paginiEc8461 Cd&si LabReena RajÎncă nu există evaluări

- EDC Model Qs Paper - 2Document7 paginiEDC Model Qs Paper - 2VigneshÎncă nu există evaluări

- EE1152Document5 paginiEE1152Saranya PrabhuÎncă nu există evaluări

- PDC Lab Updated 1Document63 paginiPDC Lab Updated 1deepa reddyÎncă nu există evaluări

- Pulse & Digital Circuits Lab Manual PDFDocument61 paginiPulse & Digital Circuits Lab Manual PDFKarunakar Reddy MÎncă nu există evaluări

- Embed Lab Manual 4-1Document30 paginiEmbed Lab Manual 4-1Karunakar Reddy M100% (1)

- Ijetr021783 PDFDocument2 paginiIjetr021783 PDFKarunakar Reddy MÎncă nu există evaluări

- Ijetr021783 PDFDocument2 paginiIjetr021783 PDFKarunakar Reddy MÎncă nu există evaluări

- 1001fb-Precision Op Amp (Photodiodes)Document16 pagini1001fb-Precision Op Amp (Photodiodes)nevdullÎncă nu există evaluări

- DC To DC Converter Basics - National SemiDocument62 paginiDC To DC Converter Basics - National Semi양영주Încă nu există evaluări

- 22 Deborah Chung's Apparent Negative ResistanceDocument5 pagini22 Deborah Chung's Apparent Negative ResistanceKarunakar Reddy MÎncă nu există evaluări