Documente Academic

Documente Profesional

Documente Cultură

Microcontroladores HC08

Încărcat de

kkkkkkkkkkkk0 evaluări0% au considerat acest document util (0 voturi)

152 vizualizări22 paginiEste documento introduce a los estudiantes a los microcontroladores HC08 de Freescale, describiendo su arquitectura interna, modelo de programación, modos de direccionamiento e instrucciones. Explica que un microcontrolador es un dispositivo electrónico integrado que incluye CPU, memoria y entradas/salidas, y se utiliza comúnmente para controlar dispositivos electrónicos. Describe los componentes típicos de un microcontrolador como CPU, memoria, reloj, puertos I/O y periféricos de comunicación y temporización.

Descriere originală:

Titlu original

Microcontroladores_HC08

Drepturi de autor

© © All Rights Reserved

Formate disponibile

PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentEste documento introduce a los estudiantes a los microcontroladores HC08 de Freescale, describiendo su arquitectura interna, modelo de programación, modos de direccionamiento e instrucciones. Explica que un microcontrolador es un dispositivo electrónico integrado que incluye CPU, memoria y entradas/salidas, y se utiliza comúnmente para controlar dispositivos electrónicos. Describe los componentes típicos de un microcontrolador como CPU, memoria, reloj, puertos I/O y periféricos de comunicación y temporización.

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

152 vizualizări22 paginiMicrocontroladores HC08

Încărcat de

kkkkkkkkkkkkEste documento introduce a los estudiantes a los microcontroladores HC08 de Freescale, describiendo su arquitectura interna, modelo de programación, modos de direccionamiento e instrucciones. Explica que un microcontrolador es un dispositivo electrónico integrado que incluye CPU, memoria y entradas/salidas, y se utiliza comúnmente para controlar dispositivos electrónicos. Describe los componentes típicos de un microcontrolador como CPU, memoria, reloj, puertos I/O y periféricos de comunicación y temporización.

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 22

Circuitos Digitales III

Revisin de los Microcontroladores HC08 de Freescale

Revisin 0.02

Luis Germn Garca M.

INTRODUCCIN

Este documento introduce al estudiante en el mundo de los microcontroladores familia

HC08 de Freescale Semiconductors, indicando como es el funcionamiento interno, el

modelo de programacin, los modos de direccionamiento y el conjunto de instrucciones. Al

finalizar, cada persona, junto con las charlas presenciales, estar en capacidad de disear

programas para esta familia de MCUs.

MICROCONTROLADORES

Un microcontrolador es un dispositivo electrnico que incluye las tres unidades funcionales

de un computador: CPU, memoria y unidades de entrada y salida. Normalmente, un

microcontrolador se considera como un computador integrado en un solo chip pero con

unas prestaciones bastante reducidas, siendo ste optimizado para una aplicacin especfica.

Este dispositivo se utiliza como unidad de control en un gran nmero de aparatos

electrnicos tales como T.V., lavadoras, neveras, reproductores de mp3/CD, equipos de

sonido, pantallas LCD, equipos mdicos, celulares, entre otros.

Un procesador tradicional depende de otros circuitos integrados para la realizacin de

diversas tareas, siendo simplemente la unidad central de proceso la que controla o gobierna

todo el sistema, siendo adems de propsito general. Un microcontrolador incluye,

adicional a la CPU, una pequea cantidad de memoria y una serie de perifricos de E/S,

pudindose construir un dispositivo electrnico con l, junto con unos cuantos elementos

adicionales, obviamente para una aplicacin especfica.

Los componentes tpicos de un MCU son:

Unidad central de procesamiento o CPU. Normalmente con unas prestaciones muy

reducidas a las de un procesador tradicional.

Memoria tanto de programa como de datos. La cantidad es bastante reducida, lo

suficiente para manejar una aplicacin especfica. Se incluye memoria RAM, OTP,

EPROM, EEPROM y FLASH.

Generador de reloj para el funcionamiento y sincrona de todo el MCU.

Perifricos de E/S tales como:

o Puertos de Entrada/Salida.

o Interrupciones externas.

o Conversores A/D y D/A.

o Generadores de base de tiempo.

o Comunicacin serial mediante UARTs, SPI, I

2

C, USB, CAN, LIN.

o Temporizadores de propsito especfico, captura de eventos y generadores de seal

PWM.

o Controladores de LCD grficos y de caracteres.

o Otros perifricos.

Normalmente, los fabricantes disean diferentes familias de MCUs, cada una especializada

en una aplicacin diferente.

Existen muchos fabricantes de MCUs en el mundo, a continuacin se indican algunas de

ellas con las diferentes familias.

ATMEL

AVR

Intel 8 y 16 bits

8XC42

MCS96

Microchip. Fabricante de los famosos PICs, los cuales ofrecen buenas prestaciones a un

precio bajo.

Gama baja 12Cxx de 12 bits

Gama media 12Fxx, 16Cxx y 16Fxx de 14 bits

Gama alta 18Cxx y 18Fxx de 16 bits

Motorola, ahora Freescale

8 bits: 68HC05, 68HC08, 68HC11

16 bits: 68HC12, 9S12, 9S12X, 68HC16

32 bits: MCUs ColdFire v3

ARQUITECTURA HC08

Todos los microcontroladores HC08 incluyen como unidad central de procesamiento la

CPU08, la cual tiene un modelo de programacin bien definido y un conjunto de

instrucciones para su manipulacin. La diferencia entre un MCU HC08 y otro radica en los

perifricos que posee y la cantidad de memoria.

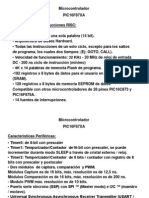

Caractersticas de la CPU08

Compatibilidad con la familia HC05.

Apuntador de pila (SP) de 16 bits con instrucciones para su manipulacin.

Registro ndice (H:X) de 16 bits con instrucciones para manipular tanto la parte alta

como la parte baja.

Frecuencia de bus mxima de 8 MHz.

Espacio de memoria para programa/datos de 64 kbytes.

16 modos de direccionamiento.

Movimiento de datos memoria a memoria (pgina cero) sin usar el acumulador.

Multiplicacin de 8-bit por 8-bit y divisin de 16-bit por 8-bit.

Manejo de aritmtica BCD.

Modelo de Programacin

Acumulador (A): Registro de 8 bits de propsito general usado por la CPU para mantener

operandos y resultados de operaciones aritmticas y no aritmticas.

ndice (H:X): Registro de 16 bits utilizado para indexar o direccionar el espacio de

memoria de 64 kbytes de la CPU. La parte alta del registro se llama H y la parte baja se

llama X y existen instrucciones para la manipulacin de cada uno de ellos.

Apuntador de pila (SP): Registro de 16 bits que contiene la direccin de la RAM referida

a la posicin libre del Stack del Sistema. Despus de un RESET, el SP es llevado a $00FF

para mantener compatibilidad con la familia HC05. La direccin del SP se decrementa

cuando un dato es almacenado en el Stack, mientras que si un dato es tomado desde all

entonces la direccin del SP se incrementa. El SP siempre apunta a una direccin de

memoria vaca y deber moverse dentro de la memoria RAM de la CPU.

Contador de programa (PC): Registro de 16 bits que contiene la direccin de la siguiente

instruccin a ser ejecutada. Normalmente, la direccin contenida en el PC se incrementa

automticamente cada que una instruccin u operando es buscado, sin embargo, una

instruccin de salto absoluto o relativo, de subrutina o de interrupcin, cargan en el PC la

direccin donde el PC debe saltar.

Cdigos de condicin (CCR): Registro de 8 bits que contiene la mscara global de

interrupcin adems de cinco banderas que indican el resultado de la instruccin que se

acaba de ejecutar. Para esta familia, puede denominarse el registro de estado de la CPU.

Las banderas son:

Overflow: Esta bandera se pone en 1 cuando el resultado de la ltima operacin ha

arrojado un overflow en complemento a dos.

Acarreo intermedio: Esta bandera se pone en 1 cuando ocurre un acarreo entre los bits

3 y 4 del acumulador en una operacin ADD o ADC. til para operaciones aritmticas

BCD.

Negativo: Esta bandera se pone en 1 cuando una operacin aritmtica o lgica arroja

un resultado negativo.

Cero: Esta bandera se pone en 1 cuando una operacin aritmtica o lgica arroja un

resultado igual a 0.

Acarreo/Prestado: Esta bandera se pone en 1 cuando una operacin de adicin

produce un acarreo del bit 7 del acumulador o cuando una operacin de substraccin

requiere de prstamo.

Mscara de interrupcin: Cuando I est en 1, todas las interrupciones enmascarables

quedan deshabilitadas (mscara puesta), en caso contrario quedan habilitadas.

Funcionamiento interno de la CPU

La CPU08 bsicamente est dividida en dos bloques principales: Unidad de Control y

Unidad de Ejecucin. La primera contiene una mquina de estados finita con lgica de

sincronizacin y control. Las salidas de sta controlan la segunda unidad, la cual contiene

una ALU, registros e interfaz al bus de direcciones/datos.

Internamente, la CPU utiliza cuatro fases de reloj para conformar lo que se denomina un

ciclo de ejecucin de la CPU o simplemente ciclo de bus, el cual tiene un periodo igual al

periodo de la frecuencia del bus, siendo 4 veces el periodo del cristal/oscilador externo. La

frecuencia de bus es la frecuencia del cristal, oscilador externo o salida del mdulo PLL

dividido por 4.

4 4 4 4 _

1

_

CGMVCLK

f

f

CGMXCLK f

f

Bus Ciclo

PLL MODULO

BUS

EXT

BUS

= = = = =

Internamente los MCUs tienen un mdulo encargado de generar/manipular la seal de reloj.

CGMXCLK hace referencia a la frecuencia de entrada al mdulo, la cual proviene

directamente del oscilador/cristal externo. CGMVCLK es la frecuencia generada por el

mdulo PLL en los MCUs que disponen de l.

Consideraciones sobre la pila de la CPU08

La pila del sistema es una zona de memoria RAM direccionada por el apuntador de pila o

SP, la cual sirve para almacenar informacin temporalmente. El SP siempre est apuntando

a una direccin limpia de la pila o stack.

La CPU utiliza la pila para:

Almacenar el contenido del PC cuando se hace un llamado a subrutina (BSR o J SR) con

el fin de poder retornar cuando ella finalice, es decir, cuando se encuentre la instruccin

RTS (Return of Subrutine).

Almacenar el contenido del PC y varios de los registros del modelo de programacin

cuando se produce una interrupcin de manera que se pueda retomar la ejecucin del

programa en donde esta se present. La finalizacin de una subrutina de atencin a

interrupcin se da cuando se ejecuta la instruccin RTI (Return of Interrupt).

Adicionalmente, el programador utiliza la pila para:

Almacenar informacin temporal cuando est realizando operaciones aritmticas.

Enviar parmetros a las subrutinas.

Retornar parmetros desde una subrutina.

La CPU08 ofrece un conjunto de instrucciones que permiten manipular el apuntador de pila

SP con el fin de poder colocar/tomar datos en/desde la pila, incluso, el programador en

cualquier momento podr reubicar la posicin del SP haciendo uso de la instruccin txs

(transferir H:X a SP). Por compatibilidad con la familia HC05 el apuntador de pila arranca

en la direccin de memoria $00FF.

La pila en la CPU08 trabaja como una memoria LIFO (ltimo en entrar primero en salir)

siendo necesario tener presente este concepto a todo momento.

Ejemplo sobre el funcionamiento del apuntador de pila

Para comprender mejor el funcionamiento de la pila o Stack vea el siguiente ejemplo:

Teniendo a SP con el valor $00FF, se hace uso de la instruccin BSR para llamar la

subrutina ANY, dicha subrutina al comienzo guarda en la pila el valor del registro A,

debido a que necesita operar con este registro de manera temporal y no quiere afectar el

valor que previamente tiene. Al finalizar, antes de la instruccin RTS, se restaura el valor

de A desde la pila. Observe como el SP va cambiando en cada caso.

XX $00FE

Vaco (Empty) $00FF

Valor de 8 bits Direccin

XX $00FE

Vaco (Empty) $00FF

Valor de 8 bits Direccin

SP

Antes del llamado a la

subrutina ANY usando bsr

Vaco (Empty) $00FD

PCH $00FE

PCL $00FF

Valor de 8 bits Direccin

Vaco (Empty) $00FD

PCH $00FE

PCL $00FF

Valor de 8 bits Direccin

SP

Despus de la instruccin

BSR. Se almacena el valor del

PC donde se debe retornar

Vaco (Empty) $00FC

Registro A $00FD

PCH $00FE

Valor de 8 bits Direccin

Vaco (Empty) $00FC

Registro A $00FD

PCH $00FE

Valor de 8 bits Direccin

SP

Despus de ejecutar la

instruccin PSHA dentro de la

subrutina ANY

XX $00FC

Vaco (Empty) $00FD

PCH $00FE

Valor de 8 bits Direccin

XX $00FC

Vaco (Empty) $00FD

PCH $00FE

Valor de 8 bits Direccin

SP

Despus de ejecutar la

instruccin PULA dentro de la

subrutina ANY

XX $00FE

Vaco (Empty) $00FF

Valor de 8 bits Direccin

XX $00FE

Vaco (Empty) $00FF

Valor de 8 bits Direccin

SP

Despus de ejecutar la

instruccin RTS desde ANY

para retornar

Cada que se almacena un valor en la pila, el SP se decrementa en una unidad mientras que

cuando se toma un valor de la pila, el SP se incrementa en una unidad. Piense por ejemplo,

que pasara si la subrutina no recupera el valor de A antes de la instruccin RTS,

obviamente el valor que se cargar en el PC no ser igual a PC =PCH:PCL si no PC =

A:PCH, lo cual llevar a una ejecucin incorrecta. Algunas veces los registros que se

almacenan en la pila no se necesitan restaurar, en este caso para llevar al SP a la posicin

correcta debe usarse la instruccin AIS n, donde n es el nmero de posiciones a sumarle o

restarle a SP. En el caso anterior, si no se usa la instruccin PULA, entonces es necesario

utilizar AIS 1 antes de RTS para evitar un problema con el valor del PC.

RESETS E INTERRUPCIONES EN LOS HC08

La CPU ejecuta instrucciones de manera secuencial, sin embargo, en muchas aplicaciones

es necesario ejecutar un conjunto de instrucciones en respuesta a una peticin hecha por un

perifrico, la cual, normalmente se hace de manera asncrona con el programa que

actualmente se est ejecutando. El Reset y las interrupciones son excepciones propias de la

CPU08. Al conjunto de instrucciones que se deben ejecutar en respuesta a una peticin de

este tipo se denomina subrutina de atencin a la excepcin, la cual es llamada por la CPU

despus de procesar la excepcin o evento.

El reset es requerido para llevar al MCU a un estado conocido, cargando el PC

normalmente con la direccin de la primera instruccin del programa. Una interrupcin es

un evento de hardware asociado a un perifrico que requiere establecer comunicacin con

la CPU, evitando que este ltimo necesite estar sondendolo (polling) a todo momento. En

los MCU HC08, cada perifrico puede generar una o varias interrupciones, las cuales son

atendidas por la CPU siempre que la mscara global est deshabilitada, incluso, cada fuente

de interrupcin tiene tambin su propia mscara de interrupcin, pudindose

habilitar/deshabilitar usando los registros de estado y control del perifrico en cuestin.

Cada fuente de interrupcin en el MCU tiene una prioridad asignada (ver en la hoja de

datos de cada MCU) siendo el Reset el de mayor prioridad (nmero 0). Adicionalmente,

cuando un perifrico dentro del MCU genera condicin de interrupcin, una bandera de uno

de los registros de estado y control se pondr en 1 indicando dicha condicin. Esta

bandera debe limpiarse cuando se ejecuta la subrutina de atencin a la excepcin o si no, la

CPU ejecutar indefinidamente tal subrutina.

En el procesamiento de una excepcin por parte de la CPU08 se tienen los siguientes pasos:

1. Enmascaramiento

El Reset no es enmascarable, as que cuando este se presente, la CPU08 deber

reconocerlo sin importar que otra interrupcin este siendo servida, el resto de

interrupciones son enmascarables, es decir, pueden habilitarse o deshabilitarse. El Bit I

del registro de cdigos de condicin (CCR) controla la mscara global de interrupcin

como se mencion anteriormente y se puede manipular con las instrucciones CLI (Clear

I) y SEI (Set I) para habilitar/deshabilitar las interrupciones enmascarables

respectivamente. Una interrupcin ser entonces reconocida por la CPU cuando tanto la

mscara global como la mscara del perifrico que la gener estn deshabilitadas (sin

mscara).

2. Reconocimiento por parte de la CPU

Un Reset es reconocido de manera asncrona (con respecto a la ejecucin de las

instrucciones) en el momento en que se presenta, al igual que las fuentes de reset

internas, excepto un reset por instruccin ilegal o por direccionamiento ilegal, los

cuales, junto con las interrupciones son reconocidos de manera sncrona por parte de la

CPU.

Todas las interrupciones son reconocidas por la CPU08 en el ltimo ciclo de ejecucin

de la instruccin actual (no confundir con la ltima fase de reloj de cada ciclo de

mquina) y por lo tanto ninguna instruccin es suspendida si se presenta un evento de

estos. En caso de presentarse una interrupcin justo en el ltimo ciclo de la instruccin

actual, ella ser reconocida en el ltimo ciclo de la siguiente instruccin.

3. Evaluacin de prioridad

Debido a que varias interrupciones, incluido el reset, se pueden presentar al mismo

tiempo, la CPU08 debe evaluar la prioridad de cada una de ellas para as determinar

cual debe procesarse en el momento y cuales debe postergar. Las prioridades de las

fuentes de interrupcin son fijas, teniendo al reset con la prioridad ms alta, el resto

depende de cada MCU. Una vez la interrupcin se haya servido, la CPU08 evala de

nuevo las prioridades de las interrupciones previamente postergadas para pasar a

procesar la que siga en la lista y as sucesivamente hasta que todas sean servidas. La

CPU08 puede manejar un total de 128 fuentes de interrupcin independientes.

4. Almacenamiento del contexto actual del sistema en la pila

Debido a que una interrupcin puede presentarse en cualquier momento dando lugar a

la ejecucin de una subrutina de atencin a excepcin, es necesario que la CPU08

almacene el contenido de varios de los registros para recuperarlos cuando la

interrupcin se haya servido y poder as retomar la ejecucin previa a la excepcin.

Automticamente, la CPU almacena en la pila del sistema los siguientes registros: PCL

(parte baja del PC), PCH (parte alta del PC), X (parte baja del registro H:X), A

(acumulador), CCR (cdigos de condicin).

Para tener mayor claridad observe la siguiente grfica. Suponga que el contenido del SP

es $01FE, adems no olvide que las direcciones de memoria son de 16 bits pero la

cantidad de bits a almacenar en cada direccin es de 8.

$01F9

CCR $01FA 5

A $01FB 4

X $01FC 3

PCH $01FD 2

PCL $01FE 1

Orden de

almacenamiento

Registro almacenado Direccin

$01F9

CCR $01FA 5

A $01FB 4

X $01FC 3

PCH $01FD 2

PCL $01FE 1

Orden de

almacenamiento

Registro almacenado Direccin

SP

Note que la parte alta del registro H:X (H) no se almacena en la pila del sistema, por lo

tanto si en la subrutina de atencin a excepcin se requiere utilizar este registro, es

necesario sacarle manualmente una copia en la pila y luego restaurarla al final antes de

la instruccin RTI, para eso existen las instrucciones PSHH y PULH.

5. Bsqueda del vector apropiado para llamar la subrutina de atencin a la excepcin

Una vez realizado los pasos anteriores, la CPU podr ejecutar la subrutina de atencin a

excepcin asociada apoyndose en los vectores de excepcin. Los vectores de

excepcin son un conjunto de direcciones de memoria donde en cada uno se almacena

la direccin de la primera instruccin de la subrutina que se debe ejecutar. Cada vector

est conformado por dos posiciones de memoria consecutivas con el fin de poder

almacenar un valor de 16 bits (direccin de memoria).

Cada fuente de interrupcin tiene un vector asociado y se puede ver en la hoja de datos

del MCU. Es necesario mediante programacin almacenar en la direccin de cada

vector que se requiera, la direccin de la primera instruccin de la subrutina de atencin

a excepcin asociada, de manera que, al procesarla, el PC sea cargado con ese valor y

por lo tanto se pueda ejecutar la ISR (Interrupt Service Routine).

El vector de RESET est ubicado en las direcciones $FFFE-$FFFF. En estas dos

direcciones se debe almacenar la direccin de la primera instruccin que debe ejecutar

la CPU cuando se de la orden de Reset.

6. Suspender el procesamiento de nuevas interrupciones

Automticamente, cuando la CPU procesa una excepcin y habindole sacado una

copia al registro CCR, ella procede a colocar en 1 lgico, el bit I del CCR, en otras

palabras, deshabilita todas las interrupciones enmascarables. Lo anterior se hace para

evitar que la subrutina de atencin a interrupcin sea suspendida por el procesamiento

de otra interrupcin. Cada fuente de interrupcin dispone de un bit en determinado

registro, el cual es utilizado para indicar la condicin de peticin de interrupcin. La

CPU, al procesar la excepcin, se fija cuales de esos bits de peticin de interrupcin

estn activos y procede a evaluar la prioridad para ejecutar la subrutina adecuada, sin

embargo, si la mscara global o la del perifrico est habilitada, entonces la CPU no

tiene en cuenta esa peticin de interrupcin en el momento. Colocando I en 1, la CPU

no procesa nuevas excepciones hasta que I vuelva a tener un 0, evento que se da

cuando la ISR finaliza con la instruccin RTI y por lo tanto se recupera el valor original

del CCR. En tal momento, las peticiones de interrupcin que se hicieron durante la

ejecucin de la ISR son evaluadas nuevamente y una nueva ISR es ejecutada. Si la ISR

olvida limpiar el bit de peticin de interrupcin, es decir, si el programador no limpia la

bandera de peticin en la ISR, entonces tal subrutina se ejecutar indefinidamente as no

se den nuevas peticiones realmente.

Subrutina de atencin a excepcin/interrupcin

Una vez la CPU haya procesado la excepcin, pasar a ejecutar la denominada subrutina de

atencin a excepcin de acuerdo a la configuracin del vector asociado. Es muy importante

tener en cuenta varias consideraciones sobre esta subrutina:

La CPU mientras est ejecutando una subrutina de atencin a interrupcin no puede

atender otras interrupciones. La razn de esto es que automticamente cuando la CPU

procesa una excepcin, este pone en 1 la bandera I del CCR. Al finalizar la subrutina

de atencin a interrupcin, la CPU restaura el registro CCR desde la pila, llevndose de

nuevo el valor de I a 0. No se recomienda usar la instruccin CLI dentro de la

subrutina de atencin a interrupcin ya que la subrutina actual podra ser temporalmente

suspendida.

En caso de usar el registro H en la subrutina, es necesario sacarle una copia a este

registro al comienzo de la subrutina usando la pila. No olvide restaurarlo al final antes

de la instruccin RTI. Para almacenar H en la pila haga uso de PSHH, mientras que

para restaurarlo utilice PULH.

Toda subrutina de atencin a interrupcin debe ser lo ms corta posible con el fin de

permitir un rpido procesamiento de otras peticiones de interrupcin.

Cuando un perifrico hace una peticin de interrupcin, ste activa una bandera,

normalmente en uno de sus registros de estado y control. Dicha bandera debe ser

limpiada siguiendo las recomendaciones del manual durante la ejecucin de la

subrutina, ya que en caso de no hacerlo, la peticin permanecer y la subrutina se

ejecutar indefinidamente.

Toda subrutina de este tipo debe finalizar con la instruccin RTI, con el fin de retomar

la ejecucin del programa justo donde se dio el evento de interrupcin, as como una

subrutina normal debe finalizar con la instruccin RTS.

Ms sobre el enmascaramiento

En el momento de utilizar la instruccin CLI para poner a I en 0, la CPU08 pasar a

procesar de inmediato la interrupcin que haya realizado peticin antes del ltimo ciclo de

esta instruccin, evitando temporalmente ejecutar la siguiente instruccin a ella, incluso si

se trata de SEI.

Fuentes de Reset

La CPU08 maneja varios tipos de reset, uno externo y cinco internos, a continuacin se da

una breve descripcin de ellos.

Reset externo: Consiste de un PIN activo en bajo con PullUp interno que permite llevar

al MCU a un estado conocido cuando el pin es llevado a 0 lgico.

Reset interno Illegal OpCode: Cuando en memoria existe un cdigo de operacin ilegal

que se trata de ejecutar, la CPU automticamente se reinicia.

Reset interno Illegal Address: Cuando se trata de direccionar una zona de memoria no

implementada, la CPU automticamente se reinicia.

Reset interno WatchDOG: Cuando el contador del perro guardin se desborda debido a

que existe una condicin anmala en el programa (un loop infinito que evita que

mediante software se limpie el contador), la CPU automticamente se reinicia.

Reset interno LVI: Si se detecta una cada de voltaje en el pin de alimentacin del

MCU, la CPU automticamente se reinicia.

Reset interno PowerOnReset: En el momento de darle energa a la CPU (es decir,

cuando VDD pasa de 0V a 3V 5V), la CPU automticamente se reinicia.

MODOS DE DIRECCIONAMIENTO

La MCU dispone de 16 tipos de direccionamiento para un acceso ms flexible a los datos.

A continuacin se enuncian dichos modos:

Inherente.

Inmediato.

Directo.

Extendido.

Indexado, sin offset.

Indexado, 8-bit offset.

Indexado, 16-bit offset.

Stack pointer, 8-bit offset.

Stack pointer, 16-bit offset.

Relativo.

Memoria a memoria (cuatro modos):

o Inmediato a directo.

o Directo a directo.

o Indexado a directo con post-incremento.

o Directo a indexado con post-incremento.

Indexado con post-incremento.

Indexado, 8-bit offset con post-incremento.

Antes de comenzar a ver los diferentes modos de direccionamiento, es importante tratar el

tema del cdigo de operacin u OpCode.

Cdigo de Mquina de la CPU HC08

Cada instruccin est en capacidad de poner a funcionar las diferentes unidades internas de

la CPU (Control y Ejecucin) para tomar los operandos de registros/memoria, procesar la

informacin y finalmente almacenar los resultados en registros/memoria. Cada instruccin

es representada por un cdigo de operacin u OpCode (cdigo binario), el cual la unidad de

control toma, decodifica y de acuerdo al valor del cdigo prepara la unidad de ejecucin

para llevar a cabo la tarea correspondiente, donde una de las primeras labores ser tomar los

operandos de memoria de acuerdo al modo de direccionamiento empleado. Cada

instruccin (por ejemplo ADD) puede hacer uso de varios modos de direccionamiento y por

lo tanto debe existir una forma de decirle a ella que emplee uno determinado, para esto la

misma instruccin podr manejar varios OpCodes dependiendo de los modos de

direccionamiento que soporte. Ahora bien, la informacin suministrada por el OpCode no

es suficiente debido a que algunos modos de direccionamiento requieren de informacin

adicional tales como el operando, ubicacin del operando, etc. y por lo tanto se necesita de

uno o varios bytes adicionales para completar determinada operacin. El OpCode junto con

los bytes adicionales conforman el denominado Cdigo de Mquina y el tamao en bytes

dependen de la instruccin y el modo de direccionamiento empleado. Todos los cdigos de

operacin tienen un tamao de un byte excepto los cdigos asociados al modo de

direccionamiento Stack Pointer, el cual tiene un tamao de 2 bytes. De acuerdo a este

tamao y a la informacin necesaria para el modo de direccionamiento, se podr tener

cdigos de mquina de hasta 4 bytes, las cuales se vern ms adelante cuando se expliquen

los diferentes modos de direccionamiento.

La instruccin ADD toma un operando de memoria y lo suma con el valor del registro A.

Para diferentes modos de direccionamiento observe que el cdigo de operacin es diferente.

Siempre, en un cdigo de mquina, el primer (o primeros) byte es el cdigo de operacin,

seguido de los bytes complementarios como informacin para el modo de direccionamiento

empleado:

Instruccin M. D. OpCode Adicin

Cdigo de

Mquina

ADD #$45 Inmediato AB 1 AB45

ADD $50 Directo BB 1 BB50

ADD $FE00 Extendido CB 2 CBFE00

ADD ,X Indexado FB 0 FB

ADD $45,X Indexado, offset 8 bits EB 1 EB45

ADD $79F4,X Indexado, offset 16 bits DB 2 DB79F4

ADD $30,SP StackPointer, offset 8 bits 9EEB 1 9EEB30

ADD $A47B,SP StackPointer, offset 16 bits 9EDB 2 9EDBA47B

M. D. Inherente

Este tipo de instrucciones no tienen operandos asociados, ellas actan directamente sobre

los registros de la CPU llevndoles un valor conocido o haciendo transferencia de uno a

otro. Debido a que no se tiene la necesidad de direccionar la memoria para obtener algn

operando, el cdigo de mquina de estas instrucciones est conformado solo por el OpCode

de la instruccin, siendo de solo un byte el tamao en memoria de este tipo de

instrucciones. En la notacin en lenguaje ensamblador, tales instrucciones aparecen sin

operandos, simplemente la instruccin.

Machine Label Operacin Operando Comentario

Code

A657 LDA #$57 ;A =$57

AB45 ADD #$45 ;A =$9C

72 DAA ;A =$02, Decimal Adjust Accumulator

M. D. Inmediato

El operando en estas instrucciones est contenido en los bytes que siguen al OpCode.

Propiamente estos bytes son el operando y no la direccin donde se ubica el operando. En

cdigo ensamblador este modo de direccionamiento se indica anteponiendo al valor

inmediato el caracter #.

El valor inmediato est limitado a uno o dos bytes dependiendo del registro que la

instruccin est empleando (H:X, A, etc.). El cdigo de mquina para este modo de

direccionamiento esta conformado por el OpCode ms uno o dos bytes del valor inmediato,

siendo entonces de 2 3 bytes.

Machine Label Operacin Operando Comentario

Code

5F START CLRX ;X=0

8C CLRH ;H=0

AF01 TAG AIX #1 ;(H:X)=(H:X)+1

65FFFF CPHX #$FFFF ;Comparar H:X hasta que llegue a $FFFF

26F9 BNE TAG ;Saltar a TAG mientras HX no sea $FFFF

20F5 BRA START ;Iniciar otra vez

M. D. Directo y Extendido

Similar al modo de direccionamiento absoluto de otros procesadores, en donde a la

instruccin se le entrega la direccin efectiva del operando. En la CPU HC08, el mapa de

memoria tiene un rango de direcciones de $0000 a $FFFF, teniendo la denominada pgina

cero en el rango de direcciones $0000 a $00FF. En este rango, el byte de mayor peso

siempre es $00 y por lo tanto no es necesario indicarlo cuando se va a acceder a un dato que

est en dicha zona de memoria, lo que implica un ahorro de ella y a la vez una ejecucin

ms rpida. El modo de direccionamiento directo implica acceder al rango $0000 a $00FF y

por lo tanto un cdigo de mquina para este modo solo necesita de dos bytes, uno para el

OpCode y otro para el byte de menor peso de la direccin de memoria ubicada en la pgina

cero. La instruccin usando este modo asume que el byte de mayor peso es $00. La razn

por la cual la RAM o parte de ella as como la mayora de registros de la CPU estn

ubicados en la pgina cero es con el fin de poder emplear este modo de direccionamiento

que finalmente ayuda a ahorrar memoria y adems lleva a tener una ejecucin ms rpida

como se indic anteriormente.

El modo de direccionamiento extendido permite acceder a cualquiera de las direcciones del

rango de memoria $0000 a $FFFF, lo cual lleva a que el cdigo de mquina sea en este

caso de 3 bytes, uno para el OpCode y otros dos para la direccin de 16 bits.

Cabe notar que la mayora de ensambladores, cuando encuentran una direccin absoluta,

son capaces de determinar el modo de direccionamiento directo o extendido y por lo tanto

establecen el cdigo de mquina apropiado. Por ejemplo, si usted indica la instruccin

ADD $0047, automticamente el ensamblador genera un cdigo de mquina que har uso

del modo de direccionamiento directo y no del extendido. Sin embargo, un programa

ensamblador puede asumir errneamente que una direccin dada en el rango $0000-$00FF

se debe acceder con el modo de direccionamiento extendido y por lo tanto no utiliza el

modo de direccionamiento directo que es ms rpido y eficiente.

En ensamblador, este modo de direccionamiento aparece como un valor absoluto,

correspondiente a la direccin donde se lee o donde se escribe, no utiliza #, este es solo

para direccionamiento inmediato.

Machine Label Operacin Operando Comentario

Code

RAM EQU $50 ;Direccin de la RAM

ROM EQU $6E00 ;Direccin de la ROM

ORG RAM ;Ubicarse en la RAM

TEMP RMB 2 ;Reservar 2 bytes

ORG ROM ;Ubicarse en la ROM

5F START CLRX

8C CLRH

3550 STHX TEMP ;TEMP=(H:X)=0

455555 LDHX #$5555 ;(H:X)=$5555

3550 STHX TEMP ;TEMP=$5555

7550 BAD CPHX RAM ;RAM=temp

26FC BNE BAD

20F1 BRA START

Se puede ver que STHX y CPHX solo usan dos bytes en memoria: Uno para el OpCode y

otro para la direccin debido a que se est utilizando la pgina cero del MCU. TEMP es una

etiqueta que tiene realmente la direccin de memoria $50 Por qu?

Machine Label Operacin Operando Comentario

Code

ORG $50 ;Iniciar en $50

FCB $FF ;$50=$FF

5F CLRX

BE50 LDX $0050 ;Cargar X desde la pgina cero

ORG $6E00 ;Iniciar en $6E00

FCB $FF ;$6E00=$FF

5F CLRX

CE6E00 LDX $6E00 ;Cargar X por fuera de la pgina cero

Se puede ver que la instruccin LDX en este cdigo tiene dos OpCodes diferentes segn el

modo de direccionamiento empleado (directo y extendido).

M. D. Indexado, sin offset

Para este modo de direccionamiento, el dato est en memoria en el rango $0000 a $FFFF.

La direccin efectiva del operando es el contenido del registro ndice H:X. El cdigo de

mquina para este modo est conformado simplemente por el OpCode y por lo tanto el

tamao es de un byte. En ensamblador la notacin aparece como INSTRUCCIN ,X.

M. D. Indexado, 8-bit offset

Para este modo de direccionamiento, el dato est en memoria en el rango $0000 a $FFFF.

La direccin efectiva del operando es el contenido del registro ndice H:X sin signo sumado

con un offset de 8 bits sin signo que se especifica junto con la instruccin. El cdigo de

mquina para este modo est conformado por el OpCode y el desplazamiento de 8 bits,

teniendo un tamao total de dos bytes. Este modo de direccionamiento se emplea

normalmente para acceder a datos que estn dentro de una tabla de n datos ubicada en

memoria. H:X ser el elemento k que se desea acceder y el offset de 8 bits ser la direccin

base de la tabla, la cual solo podr estar en una de las primeras 256 direcciones de la

memoria. En ensamblador, la notacin aparece como INSTRUCCIN offset8bits,X.

M. D. Indexado, 16-bit offset

Para este modo de direccionamiento, el dato est en memoria en el rango $0000 a $FFFF.

La direccin efectiva del operando es el contenido del registro ndice H:X sin signo sumado

con un offset de 16 bits sin signo que se especifica junto con la instruccin. El cdigo de

mquina para este modo est conformado por el OpCode y el desplazamiento de 16 bits,

teniendo un tamao total de tres bytes. Este modo de direccionamiento se emplea

normalmente para acceder a datos que estn dentro de una tabla de n datos ubicada en

memoria. H:X ser el elemento k que se desea acceder y el offset de 16 bits ser la

direccin base de la tabla. En ensamblador, la notacin aparece como INSTRUCCIN

offset16bits,X.

La siguiente es una tabla de 4 elementos con direccin base $1000. Para acceder al valor

F4, H:X debe tener un 2 y el desplazamiento ser $1000. Si se quiere acceder al valor 07,

simplemente se le suma 1 a H:X y se deja el mismo desplazamiento. Puede emplearse de

manera genrica una porcin de cdigo que recorra toda la tabla,

incrementando/decrementando el valor de H:X y dejando el desplazamiento fijo.

Direccin ndice Contenido

$1000 0 45

$1001 1 2E

$1002 2 F4

$1003 3 07

Machine Label Operacin Operando Comentario

Code

FC JMP ,X ;Sin offset

;Salta a la direccin apuntada por H:X

EC35 JMP $35,X ;8 Bit Offset

;Salta a la direccin apuntada por H:X +$35

DCA035 JMP $A035,X ;16 Bit Offset

;Salta a la direccin apuntada por H:X +$A035

M. D. Stack Pointer, 8-Bit Offset

Similar al indexado pero el registro base es SP y no H:X, el offset o desplazamiento es de

8-bits sin signo. El OpCode para este modo de direccionamiento es de 2 bytes y por lo tanto

el cdigo de mquina tendr un tamao de 3 bytes. En ensamblador, la notacin aparece

como INSTRUCCIN offset8bits,SP.

M. D. Stack Pointer, 16-Bit Offset

Similar al indexado pero el registro base es SP y no H:X, el offset o desplazamiento es de

16-bits sin signo. El OpCode para este modo de direccionamiento es de 2 bytes y por lo

tanto el cdigo de mquina tendr un tamao de 4 bytes. En ensamblador, la notacin

aparece como INSTRUCCIN offset16bits,SP.

Machine Label Operacin Operando Comentario

Code

450100 LDHX #$0100

94 TXS ;Reset Stack Pointer

;to $00FF

A620 LDA #$20 ;A=$20

9EE710 STA $10,SP ;$10F=$20

9E6B10FC LP: DBNZ $10,SP,LP ;8-Bit offset Por qu?, ver M.D. Relativo

450100 LDHX #$0100

94 TXS ;Reset Stack Pointer

;to $00FF

9ED60250 LDA $0250,SP ;16-Bit offset, cargar A, con el contenido

;de la direccin $34F

M. D. Relativo

Modo de direccionamiento empleado en las instrucciones de salto condicional e

incondicional, adems en la instruccin de salto relativo a subrutina. La direccin efectiva

es la suma del contenido del PC (Registro base, relativo) con un valor de desplazamiento de

8 bits con signo. La instruccin de salto evala una condicin, si esta es verdadera, el PC se

carga con la direccin efectiva previamente calculada, en caso contrario el PC toma la

direccin de la siguiente instruccin al salto condicional o incondicional. En caso de un

salto incondicional (BRA BSR), el PC siempre ser cargado con la direccin efectiva sin

evaluar condiciones. El programa ensamblador es capaz de inferir el valor de 8 bits que se

le debe sumar al PC para calcular la direccin efectiva y en caso de tenerse un

desplazamiento negativo, entonces el valor se almacenar en complemento a dos. Si la

condicin es verdadera, el PC podr moverse en torno a l en un rango de -128 a 127.

El cdigo de mquina para este modo de direccionamiento est conformado por el OpCode

y el valor relativo de 8 bits con signo, tenindose un tamao de 2 bytes. Si esta instruccin

adicionalmente emplea a la vez otro modo de direccionamiento, entonces, al tamao se le

debe sumar los bytes adicionales del modo en cuestin. Consulte las instrucciones DBNZ,

BRSET, BRCLR. La notacin en lenguaje ensamblador es INSTRUCCIN

etiqueta_salto direccin absoluta

Machine Label Operacin Operando Comentario

Code

A601 TAG LDA #1 ;A=1

A1FE CMP #-2 ;Comparar con -2

91FA BLT TAG ;Salta si el valor de A es menor que -2

20FE HERE BRA HERE ;Salta siempre a HERE

M. D. Memoria a Memoria

Existe un total de 4 modos de direccionamiento Memoria a Memoria que permiten

transferir datos de manera rpida hacia/desde la pgina cero, muy til en la inicializacin de

perifricos, variables, entre otros. Estos modos de direccionamiento solo pueden emplearse

con la instruccin MOV.

Memoria a Memoria: Inmediato a Directo

Machine Label Operacin Operando Comentario

Code

6E22F0 4-Cyc MOV #$22,$F0 ;Posicin $F0=$22

Memoria a Memoria: Directo a Directo

Machine Label Operacin Operando Comentario

Code

4EF0F1 5-Cyc MOV $F0,$F1 ;Posicin $F1 =Posicin $F0

Memoria a Memoria: Indexado a Directo con post-incremento

Machine Label Operacin Operando Comentario

Code

7E18 MOV X+,$25 ;Mueve el dato apuntado por H:X a la direccin $25

;y post-incrementa H:X

Memoria a Memoria: Directo a Indexado con post-incremento

Machine Label Operacin Operando Comentario

Code

5E18 MOV $25,X+ ;Mueve el dato existente en $25 a la direccin

;apuntada por H:X y post-incrementa H:X

M. D. Indexado con Post-Incremento

Similar al indexado sin offset pero con post-incremento de H:X.

M. D. Indexado 8-Bit offset, con Post-Incremento

Similar al indexado 8-Bit offset adems de post-incremento de H:X.

Machine Label Operacin Operando Comentario

Code

7102 LOOP CBEQ X+,TAG ;Sin offset

615002 LOOP2 CBEQ $50,X+,TG1 ;8Bit Offset

INSTRUCCIONES

El manual de referencia de la CPU HC08 detalla claramente cada una de las instrucciones

que l soporta. En esta seccin se clasifican las instrucciones por funcionamiento para una

fcil ubicacin en el manual cuando se requiere desarrollar determinada operacin.

Adicionalmente se realizan algunas aclaraciones sobre temas como: saltos absolutos,

relativos, subrutinas, entre otros.

Clasificacin

Control del Programa

Conjunto de instrucciones que permiten cambiar el flujo del programa, es decir, cargar en el

PC la direccin de memoria de una instruccin diferente a la de la siguiente instruccin que

se debera ejecutar normalmente. Existen diferentes tipos de stas instrucciones:

condicionales (relativo), incondicionales (relativo y absoluto) y salto a subrutina (relativo y

absoluto).

Saltos absolutos y relativos

El MCU HC08 as como muchos Microprocesadores y Microcontroladores manejan

instrucciones de salto condicional e incondicional de manera absoluta o relativa. Una

instruccin de salto condicional evala una o varias de las banderas de algn registro y de

acuerdo a esto toma la accin de cargar en el PC una direccin diferente a la de la siguiente

instruccin consecutiva. Las instrucciones de salto incondicional cargan en el PC la

direccin donde el flujo de programa debe seguir sin la necesidad de evaluar alguna

condicin. Este tipo de instrucciones pueden cargar en el PC un valor relativo (con respecto

a l u otro registro) o un valor absoluto. Para la CPU08, el valor relativo es un valor

constante de 8 bits con signo que se le suma al contenido del PC para obtener la direccin

efectiva donde el programa debe saltar. Un valor absoluto se refiere a la direccin efectiva

que se va a cargar en el PC para cambiar el flujo del programa.

Saltos a subrutina relativos y absolutos

En los programas es comn realizar diversas operaciones sobre un conjunto de operandos y

obtener de ellos un conjunto de resultados. Como ejemplo, vea la funcin y=sen(x),

dependiendo del valor de x se tiene un valor de y. Para este caso se puede hacer una

porcin de cdigo que tome el valor x y se obtenga as el valor de y correspondiente. Hacer

fragmentos de cdigo para cada uno de los posibles valores que x puede tomar no tiene

sentido y por lo tanto se recurre a lo que se llama una rutina, la cual es un conjunto de

instrucciones que toman uno o varios valores, operan con ellos y arrojan uno o varios

resultados. En la ejecucin del programa, debe existir la forma de saltar a la rutina para que

procese el valor de x y entregue el valor de y correspondiente, de manera que las

instrucciones siguientes al llamado lo puedan usar. Que se requiere entonces para hacer lo

anterior? No es suficiente con ejecutar una instruccin de salto relativo o absoluto, se

necesita almacenar una copia del PC antes de hacer el salto y de esta forma poder retornar

cuando ella finalice. Las instrucciones de salto a subrutina relativo y absoluto (BSR y J SR)

trabajan de manera similar a las ya vistas instrucciones de salto relativo y absoluto, pero

adicionalmente sacan una copia del valor del PC en la pila del sistema antes de realizar el

salto. La rutina entonces har el procesamiento respectivo y finalizar con una instruccin

de salto, denominada retorno de subrutina (RTS), la cual restaura el PC con el valor

previamente almacenado de manera que la ejecucin prosiga en la siguiente instruccin

donde se hizo el salto. La rutina propiamente es considerada una subrutina, ya que hace

parte de un programa o rutina principal.

La siguiente es una lista de las instrucciones que manejan saltos absolutos y relativos en la

CPU

Instruccin Descripcin Relativo Absoluto

BCC Salta si C (acarreo) =0 X

BCS Salta si C (acarreo) =1 X

BEQ Salta si es igual X

BGE Salta si es mayor que o igual (signo) X

BGT Salta si es mayor que (signo) X

BHCC Salta si H (acarreo intermedio) =0 X

BHCS Salta si H (acarreo intermedio) =1 X

BHI Salta si es superior X

BHS Salta si es superior o el mismo X

BIH Salta si IRQ =1 X

BIL Salta si IRQ =0 X

BLE Salta si es menor que o igual (signo) X

BLO Salta si es inferior X

BLS Salta si es inferior o el mismo X

BLT Salta si es menor que (signo) X

BMC Salta si I =0 X

BMI Salta si N (menos/negativo) =1 X

BMS Salta si I =1 X

BNE Salta si no es igual X

BPL Salta si N (mas/positivo)=0 X

BRA Salta siempre X

BRCLR Salta si el bit n en memoria est en 0 X

BRSET Salta si el bit n en memoria est en 1 X

BRN Nunca salta X

BRS Salto a subrutina X

CBEQ Compara y salta si es igual X

DBNZ Salta si despus de decrementar es diferente de cero X

J MP Salta siempre X

J SR Salto a subrutina X

RTI Retorno desde interrupcin

RTS Retorno desde subrutina. Ver J SR y BSR.

STOP Detiene la CPU y el reloj del sistema. I =0

SWI Interrupcin por Software

WAIT Detiene la CPU. I =0

Aritmtica de enteros

La siguiente es una lista de las instrucciones que manejan operaciones aritmticas en la

CPU

Instruccin Operacin

ADC A (A) +(M) +(C). Afecta CCR.

ADD A (A) +(M). Afecta el CCR.

MUL X:A (X) x (A). Multiplica el contenido de X con el de A.

SBC A (A) - (M) - (C). Afecta CCR.

SUB A (A) - (M). Afecta CCR.

DAA Ajuste decimal al acumulador. Afecta el CCR.

DIV A (H:A) (X). H Residuo.

NSA A (A[3:0]:A[7:4]). Usado en conjunto con DAA, no es aritmtica.

Operaciones Lgicas

La siguiente es una lista de las instrucciones que manejan operaciones lgicas en la CPU

Instruccin Operacin

AND A (A) & (M). Afecta CCR.

COM A X M $FF - (A X M). Afecta CCR. Complemento a uno.

EOR A (A) (M).

ORA A (A) | (M). Afecta CCR.

NEG A X M $00 - (A X M). Complemento a dos.

Operaciones de desplazamiento

La siguiente es una lista de las instrucciones que manejan operaciones de desplazamientos

en la CPU

Instruccin Descripcin

ASL Desplaza todos los bits hacia la izquierda (Aritmtica). Afecta CCR

ASR Desplaza todos los bits hacia la derecha (Aritmtica). Afecta CCR

LSL Similar a la instruccin ASL

LSR Desplaza todos los bits hacia la derecha (Lgica). Afecta CCR

ROL Rotan todos los bits hacia la izquierda. Incluye el acarreo C.

ROR Rotan todos los bits hacia la derecha. Incluye el acarreo C.

Manipulacin de bits

La siguiente es una lista de las instrucciones que manipulan bits en memoria

Instruccin Descripcin

BCLR Pone el bit n a 0. No afecta CCR

BSET Pone el bit n a 1. No afecta CCR

CLC Lleva 0 el bit de acarreo C

CLI Lleva 0 el bit de mscara I

SEC Lleva 1 el bit de acarreo C

SEI Lleva 1 el bit de mscara I

Operaciones de toma de decisiones

La siguiente es una lista de las instrucciones que permiten toma de decisiones

Instruccin Operacin

CMP (A) (M). Necesaria para la mayora de instrucciones condicionales.

CPHX (H:X) (M:M +$0001). Similar a CMP.

CPX (X) (M). Similar a CMP.

TST Verifica si el contenido de A, X M es cero o negativo

Manipulacin de registros y memoria

La siguiente es una lista de las instrucciones que manipulan registros y memoria

Instruccin Operacin

AIS SP (SP) +(16 <<M). M se extiende a 16 bits. No afecta CCR.

AIX H:X (H:X) +(16 <<M). M se extiende a 16 bits. No afecta CCR.

CLR A X M $00.

DEC A X M (A X M) - $01

INC A X M (A X M) +$01.

LDA A (M). Carga A con el contenido de M.

LDHX H:X (M:M+$0001). Carga H:X con el contenido de (M:M+$0001).

LDX X (M). Carga X con el contenido de M.

MOV (M) (M). Movimiento memoria a memoria (Solo para la pgina cero)

PSHA Guarda A en la pila del sistema y luego SP =(SP) - $0001

PSHH Guarda H en la pila del sistema y luego SP =(SP) - $0001

PSHX Guarda X en la pila del sistema y luego SP =(SP) - $0001

PULA SP =(SP) +$0001 y luego carga A con el valor actual en la pila.

PULH SP =(SP) +$0001 y luego carga H con el valor actual en la pila.

PULX SP =(SP) +$0001 y luego carga X con el valor actual en la pila.

RSP SP $FF

STA M (A). Carga M con el contenido de A

STHX (M:M +$0001) (H:X). Carga M (2 bytes) con el contenido de H:X

STX M (X). Carga M con el contenido de X

TAP CCR (A). Transfiere A al registro de estado del sistema.

TAX X (A).

TPA A (CCR).

TSX H:X (SP) +$0001

TXA A (X).

TXS SP (H:X) - $0001

MODOS DE BAJO CONSUMO (WAIT - STOP)

Son modos donde el microcontrolador puede ahorra energa ya que no necesita efectuar

ninguna operacin. Se utilizan cuando el tiempo entre eventos que debe realizar el

microcontrolador es muy grande (hablando en trminos de velocidad de un

microcontrolador que puede ser 2.5 MHz o superior).

En un modo de bajo consumo, el reloj de la CPU est desactivado de manera que no ejecuta

ninguna instruccin hasta que se produzca una interrupcin. Normalmente, el programa se

desarrolla para manejar una metodologa de procesamiento ante eventos, de manera que la

CPU est dormida, esperando que uno o varios eventos la despierten y por lo tanto se

empiece a procesar la informacin. Al finalizar el procesamiento, la CPU se vuelve a

dormir a la espera de un nuevo evento.

El modo wait apaga el reloj de la CPU, es decir, cuando se utiliza dicho modo, la CPU no

recibe pulsos de reloj y por lo tanto el valor del PC (Program Counter) permanece estable,

adems, el consumo de energa del micro se reduce. Slo una interrupcin interna o externa

restablecer el reloj de la CPU y lo pondr a trabajar nuevamente. Todos los perifricos

siguen trabajando en este modo de manera que puedan reactivar la CPU.

El modo stop apaga el reloj de la CPU y del bus, es decir, tanto la CPU como la mayora de

perifricos que dependen de una seal de reloj para trabajar quedan deshabilitados. Es un

modo de mayor ahorro de energa donde solo unos pocos perifricos del MCU pueden

despertar a la CPU.

REFERENCIAS

1. Reference Manual. HC08 Central Processor Unit. Motorola/Freescale.

2. Gua didctica del HC08. Silica and Digital DNA de Motorola.

S-ar putea să vă placă și

- 100 circuitos de shields para arduino (español)De la Everand100 circuitos de shields para arduino (español)Evaluare: 3.5 din 5 stele3.5/5 (3)

- Compilador C CCS y Simulador Proteus para Microcontroladores PICDe la EverandCompilador C CCS y Simulador Proteus para Microcontroladores PICEvaluare: 2.5 din 5 stele2.5/5 (5)

- Puesta en marcha de sistemas de automatización industrial. ELEM0311De la EverandPuesta en marcha de sistemas de automatización industrial. ELEM0311Evaluare: 3 din 5 stele3/5 (1)

- Sistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208De la EverandSistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208Încă nu există evaluări

- Iniciación al diseño de circuitos impresos con Altium DesignerDe la EverandIniciación al diseño de circuitos impresos con Altium DesignerÎncă nu există evaluări

- Computadores para bases de datos. IFCT0310De la EverandComputadores para bases de datos. IFCT0310Încă nu există evaluări

- Programación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeDe la EverandProgramación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeÎncă nu există evaluări

- Pic16f887 EntregarDocument171 paginiPic16f887 EntregarErnesto NetoÎncă nu există evaluări

- Curso de Pic (Saber Electronica)Document32 paginiCurso de Pic (Saber Electronica)Rous Lopez Victoria100% (1)

- Comando FOR para Archivos BATDocument19 paginiComando FOR para Archivos BATfelipe_vergara_40Încă nu există evaluări

- Testeo y verificación de equipos y periféricos microinformáticos. IFCT0108De la EverandTesteo y verificación de equipos y periféricos microinformáticos. IFCT0108Încă nu există evaluări

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaDe la EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaÎncă nu există evaluări

- TI040 - Gestión de Bases de Datos y Recursos de Información PDFDocument102 paginiTI040 - Gestión de Bases de Datos y Recursos de Información PDFMervin FerminÎncă nu există evaluări

- Reparación de instalaciones automatizadas. ELEE0109De la EverandReparación de instalaciones automatizadas. ELEE0109Încă nu există evaluări

- Microprocesador 8085Document7 paginiMicroprocesador 8085Percy VillegasÎncă nu există evaluări

- Diapositivas Contramedidas-PenTesting10Document145 paginiDiapositivas Contramedidas-PenTesting10Jesus Espada FloresÎncă nu există evaluări

- UF0852 - Instalación y actualización de sistemas operativosDe la EverandUF0852 - Instalación y actualización de sistemas operativosEvaluare: 5 din 5 stele5/5 (1)

- Configuración de Puertos de e - SDocument30 paginiConfiguración de Puertos de e - Ssofy naranjoÎncă nu există evaluări

- Capitulo 2 Entradas y SalidasDocument22 paginiCapitulo 2 Entradas y SalidasMauricio Cortes CuamatziÎncă nu există evaluări

- 1 - 16F873-BDocument48 pagini1 - 16F873-BJuan Martin Alderete GobbatoÎncă nu există evaluări

- Manual ATMEGA 164PDocument16 paginiManual ATMEGA 164PFrancis SebastianÎncă nu există evaluări

- Pic 16F877Document9 paginiPic 16F877Jave Zabdiel Hernandez MarinÎncă nu există evaluări

- Actividad 5Document9 paginiActividad 5juan mezaÎncă nu există evaluări

- Laboratorio N°3 MicroprocesadoresDocument34 paginiLaboratorio N°3 MicroprocesadoresIshmael AcevedoÎncă nu există evaluări

- PENTIUMDocument8 paginiPENTIUMJessica Aguirre CrespoÎncă nu există evaluări

- Unidad IDocument10 paginiUnidad IJose Manuel Godoy EscribarÎncă nu există evaluări

- Pic 18 F 45506 Ago 2013Document50 paginiPic 18 F 45506 Ago 2013josuemxÎncă nu există evaluări

- Chip PropellerDocument5 paginiChip PropellerTimothy AdamsÎncă nu există evaluări

- El Microprocesador 8085Document11 paginiEl Microprocesador 8085neptuno97Încă nu există evaluări

- Microprocesador - El PIC 16F84Document10 paginiMicroprocesador - El PIC 16F84J84CÎncă nu există evaluări

- Reg Del Pic 16f84Document4 paginiReg Del Pic 16f84Wilzon ChambiÎncă nu există evaluări

- Manual Pic 16F8XDocument19 paginiManual Pic 16F8XsuarockÎncă nu există evaluări

- Manual Basico Microcontroladores PicDocument30 paginiManual Basico Microcontroladores PicIng. C Miguel Navarro.Încă nu există evaluări

- MicrocontroladoresDocument25 paginiMicrocontroladoresRaùl Alejandro Paredes de la CruzÎncă nu există evaluări

- Microcontroladores AT89C5xDocument25 paginiMicrocontroladores AT89C5xMario Fernández RodríguezÎncă nu există evaluări

- Pic 16f628aDocument10 paginiPic 16f628aedison albaÎncă nu există evaluări

- Trabajo Final Informática II - Secuenciador de 16 EfectosDocument27 paginiTrabajo Final Informática II - Secuenciador de 16 EfectosNelson Fortunatti50% (2)

- Estructura de Los Automatas ProgramablesDocument10 paginiEstructura de Los Automatas ProgramablesCristian H VásquezÎncă nu există evaluări

- Conceptos Del MSP430Document21 paginiConceptos Del MSP430Rodolfo AlcantaraÎncă nu există evaluări

- 5SB - Equipo 02 - Diagrama de ProcesadorDocument12 pagini5SB - Equipo 02 - Diagrama de ProcesadorKenshin Ancona PerezÎncă nu există evaluări

- Arquitectura Von NeumannDocument8 paginiArquitectura Von NeumannDaniel Medrano IzquierdoÎncă nu există evaluări

- Tarea2ensambladores e InterpretesDocument5 paginiTarea2ensambladores e InterpretesEstefania Rodriguez SanchezÎncă nu există evaluări

- Procesador de 4 BitsDocument8 paginiProcesador de 4 BitsCandido LpzÎncă nu există evaluări

- Arquitectura Del 68HC11 - EypdcDocument23 paginiArquitectura Del 68HC11 - EypdcGunter BreakÎncă nu există evaluări

- Manual de Microcontroladores PICDocument68 paginiManual de Microcontroladores PICabraham-tellez-5555Încă nu există evaluări

- Manual de Microcontroladores PicDocument68 paginiManual de Microcontroladores PicCristian LandaverdeÎncă nu există evaluări

- MicrocontroladoresDocument16 paginiMicrocontroladoresVicktor RedÎncă nu există evaluări

- Lecciòn 1 Estructura y Caracterìsticas de Un PICDocument8 paginiLecciòn 1 Estructura y Caracterìsticas de Un PICErick 'CzÎncă nu există evaluări

- 3ArqComp - CPUDocument44 pagini3ArqComp - CPUsaraÎncă nu există evaluări

- Estructura Del MicrocontroladorDocument13 paginiEstructura Del MicrocontroladorConcepcion Jeronimo Hernandez0% (1)

- Sistema Minimo Micro 8088Document4 paginiSistema Minimo Micro 8088miguelon04Încă nu există evaluări

- Apuntes Libro AcDocument5 paginiApuntes Libro AcMilagros VegaÎncă nu există evaluări

- Guía Del Pic 16f84Document17 paginiGuía Del Pic 16f84b6dicÎncă nu există evaluări

- Apuntes PicDocument155 paginiApuntes PicAmador Vivar RecarteÎncă nu există evaluări

- Conceptos Del MSP430Document21 paginiConceptos Del MSP430dabren28Încă nu există evaluări

- Memoria y Vectores de ProgramaDocument6 paginiMemoria y Vectores de Programaminejd1Încă nu există evaluări

- 1 - Introducción A Los AVRDocument70 pagini1 - Introducción A Los AVRJaroxxoÎncă nu există evaluări

- Curso de Pic (Saber Electronica) PDFDocument32 paginiCurso de Pic (Saber Electronica) PDFAdan Yohali SánchezÎncă nu există evaluări

- Curso de PICs para AficionadosDocument32 paginiCurso de PICs para AficionadosCarlos BravoÎncă nu există evaluări

- Lógica de CPUDocument5 paginiLógica de CPURafael HernandezÎncă nu există evaluări

- Introduccion A Los Sistemas EmbebidosDocument122 paginiIntroduccion A Los Sistemas EmbebidosAndres Gerardo Fuentes C.Încă nu există evaluări

- Computación Física: Explorando la visión por computadora en la computación físicaDe la EverandComputación Física: Explorando la visión por computadora en la computación físicaÎncă nu există evaluări

- Troubleshooting FortiWeb 6.3Document43 paginiTroubleshooting FortiWeb 6.3Loraine Peralta Herrera100% (1)

- Mirroring en Base de DatosDocument9 paginiMirroring en Base de DatosKNDevsÎncă nu există evaluări

- Cuestionario Jerarquia DirectoriosDocument4 paginiCuestionario Jerarquia DirectoriosLizeth ConuÎncă nu există evaluări

- Conceptos Básicos de ComputaciónDocument9 paginiConceptos Básicos de ComputaciónBryan Andrés Zúñiga RamírezÎncă nu există evaluări

- Modulación y Demodulación QAM, QPSK Y 8-PSK: Jhon Henry Rios Ramirez - Sebastian Gomez CocaDocument4 paginiModulación y Demodulación QAM, QPSK Y 8-PSK: Jhon Henry Rios Ramirez - Sebastian Gomez CocaJhon Henry Rios RamirezÎncă nu există evaluări

- Foro Noticias3d Com Vbulletin Showthread PHP T 440396Document16 paginiForo Noticias3d Com Vbulletin Showthread PHP T 440396p863003Încă nu există evaluări

- Cuestionario Unidad 3Document4 paginiCuestionario Unidad 3Alizer NoxÎncă nu există evaluări

- Cisco Networking Academy - CCNA3 - Examen 7Document3 paginiCisco Networking Academy - CCNA3 - Examen 7renkastle100% (1)

- ABRITES - Commander - For - Nissan - Manual (1) .En - EsDocument19 paginiABRITES - Commander - For - Nissan - Manual (1) .En - EsJose VeraÎncă nu există evaluări

- Fase 4 LinuxDocument12 paginiFase 4 LinuxcarlopezprÎncă nu există evaluări

- Conceptos de UnixDocument59 paginiConceptos de UnixTony KolmeÎncă nu există evaluări

- Extraer Texto de Un PDF Con PythonDocument4 paginiExtraer Texto de Un PDF Con PythonELmer ChaparroÎncă nu există evaluări

- Manual de Soporte para Desarrolladores de SoftwareDocument37 paginiManual de Soporte para Desarrolladores de SoftwareLuis MartínezÎncă nu există evaluări

- Protocolo de Transferencia de HipertextoDocument7 paginiProtocolo de Transferencia de HipertextoClaudio Xavier BorjaÎncă nu există evaluări

- GimnasioDocument8 paginiGimnasiohunterÎncă nu există evaluări

- Apuntes UnidadDocument20 paginiApuntes Unidadegaral81Încă nu există evaluări

- CONSULTA MEDICA Ejemplo de Uso Del MapBD PDFDocument34 paginiCONSULTA MEDICA Ejemplo de Uso Del MapBD PDFPablo ContrerasÎncă nu există evaluări

- 11.5.2.4 Packet Tracer - Configuring A Linksys Router IGDocument11 pagini11.5.2.4 Packet Tracer - Configuring A Linksys Router IGJeison MercadoÎncă nu există evaluări

- Memoria WRDocument6 paginiMemoria WRAxel ParedesÎncă nu există evaluări

- Actividad 2.4Document10 paginiActividad 2.4R Isela Hernandez GuzmanÎncă nu există evaluări

- Actividad 8Document26 paginiActividad 8Cronwell MairenaÎncă nu există evaluări

- Trabajo Symbian CompletoDocument10 paginiTrabajo Symbian CompletoAdryan Ernesto RojasÎncă nu există evaluări

- WINRARDocument4 paginiWINRARMaria Josefina HernandezÎncă nu există evaluări

- Replicación Base de Datos PDFDocument9 paginiReplicación Base de Datos PDFroyer mejiaÎncă nu există evaluări

- INVESTIGACIONDocument9 paginiINVESTIGACIONLuiss baezaÎncă nu există evaluări

- X 25Document21 paginiX 25Bryan Sleyter Patiño MaisancheÎncă nu există evaluări

- Debian Reference - EsDocument272 paginiDebian Reference - EsAa AaÎncă nu există evaluări