Documente Academic

Documente Profesional

Documente Cultură

Decode Mpeg-2 Video With Virtex Fpgas

Încărcat de

Blesson GeorgeTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Decode Mpeg-2 Video With Virtex Fpgas

Încărcat de

Blesson GeorgeDrepturi de autor:

Formate disponibile

by Rick Richmond

Amphion

rick@amphion.com

MPEG-2 is the digital video paradigm of

today. It is at the heart of the Digital Video

Broadcast (DVB) and Advanced Television

Systems Committee (ATSC) standard and

high-definition digital television systems

and DVD-video, which has seen incredible

market growth in recent years.

The widespread adoption of these appli-

cations and systems, coupled with consid-

erable investment by broadcasters and dis-

tributors, indicate that MPEG-2 is going to

be around for a good while to come

despite the emergence of new, even better

video compression algorithms. Future con-

sumer digital applications, in which audio,

video, and data networking technologies

converge, are certain to need built-in

MPEG-2 video capability.

Yet MPEG-2 video is fairly complex and

computationally intensive to decode. The

main features of the algorithm are discrete

cosine transform (DCT)-based compres-

sion and motion estimation techniques.

Until now, decoder implementations for

digital STBs (Set Top Boxes) and DVD-

video players had been the domain of ASIC

implementations or software running on

very powerful processors.

As the sophistication of products like

STBs grows, designs will require ever-

increasing flexibility and ever-decreasing

development time scales. Now, using the

Xilinx Virtex series of FPGAs and a new

intellectual property (IP) core from

Amphion, building MPEG-2 video into

your designs is simple. Amphions CS6651

video decoder, which incorporates an inte-

grated external SDRAM memory con-

troller and display direct memory access

(DMA), is a great example of the Platform

FPGA capability of the Xilinx Virtex series.

This solution allows decoding of MP@ML

MPEG-2 video with NTSC or PAL frame

rates and resolutions.

The MPEG-2 Video Algorithm

MPEG-2 MP@ML video provides a gener-

ic video compression solution for applica-

tions such as satellite, terrestrial, and cable

Amphions CS6651 video decoder

enables the decompression of

video streams in real time.

Decode MPEG-2

Video with

Virtex FPGAs

00 Xcell Journal Spring 2003

Decode MPEG-2

Video with

Virtex FPGAs

Amphions CS6651 video decoder

enables the decompression of

video streams in real time.

television (in DVB and ATSC formats), as

well as optical storage (DVD-video) at

NTSC, PAL, and SECAM resolution and

frame rates.

MPEG-2 video sequences are composed

of three different types of pictures:

Intra coded pictures (I-pictures),

which are compressed using DCT-

based techniques

Predictive coded pictures

(P-pictures), which use motion

compensation to predict the

current picture from a past

reference picture

Bidirectional predictive coded

pictures (B-pictures), which use

predictions from past and

future reference pictures. B-

type pictures are not themselves

used as reference pictures.

DCT-based Compression

In MPEG-2 MP@ML video,

each picture is broken down

into 16x16-sized blocks of lumi-

nance samples, called macro

blocks. These blocks are further

divided into 8x8 blocks. Each

macro block has six blocks in

total: four luminance blocks and two sub

sampled chrominance blocks (a 4:2:0

chrominance format). In the encoding

process, a two-dimensional, 8-point DCT

is applied to each 8x8 block; the resulting

coefficients are quantized using a 64-ele-

ment quantization matrix.

This process reduces amplitude and

increases the number of zero-value coeffi-

cients. The quantized DCT coefficients are

reordered in a zigzag fashion into a one-

dimensional stream, effectively grouping

together runs of zero-valued coefficients

interspersed with non-zeros. This stream of

run-level pairs is then encoded using

Huffman-style variable length codes

(VLCs) based on a statistical model.

Motion Compensation

In predictive and bidirectionally predictive

coded pictures, each macro block may have

a number of pairs of motion vectors. These

specify the horizontal and vertical displace-

shown in Figure 1. The core requires a

minimum clock speed of 27 MHz to

maintain MP@ML decoding rates. Video

elementary streams are accepted into the

core via the byte-wide ES_Data input

port on the elementary stream interface.

Parser

The front end of the core is the video ele-

mentary stream parser. It searches

the syntax of the incoming stream

for start codes at which decoding

may commence. The parser extracts

the various encoding parameters

from the headers, which are used to

direct subsequent decoding. The

remaining variable-length encoded

picture data is passed onto the VLC

decoder.

VLC Decoder

Here, the Huffman-style VLC

picture data is decoded. The out-

puts of this block include DCT

block run-level codes and motion

vectors for motion compensation

of each macro block.

Run-Level Decoding and Inverse

Quantization

The run-level decoder converts run-level

codes from the VLC decoder into com-

plete blocks of 64 quantized DCT coeffi-

cients. These coefficients are then con-

verted from zigzag scan order to natural

row order before being dequantized.

Virtex block RAMs are used to support

the scan conversion operation and the

storage of custom quantization matrices,

which may be sent in the elementary

stream headers.

Inverse DCT

This unit performs the computationally

intensive inverse DCT (IDCT) on the

dequantized 8x8 blocks of DCT coeffi-

cients. Making use of the high-speed on-

chip block RAM, the IDCT unit is capa-

ble of streaming data continuously, trans-

forming in 64 clock cycles an 8x8 block

of DCT coefficients into an 8x8 block of

luminance or chrominance samples or

prediction errors.

ment from the current position at which

the stored reference picture best resembles

the current macro block. The difference (if

any) between the motion-compensated

prediction and the actual image is coded

using the DCT-based techniques described

above. The sum of the predicted samples

and the prediction error give the final

reconstructed macro block.

Decoding MPEG-2 Video

As devices and applications grow in com-

plexity, the Amphion CS6651 MPEG-2

video decoder IP core can be implemented

by taking advantage of the capabilities of

Xilinx Platform FPGAs.

As part of a demonstration system, the

core is implemented in a Xilinx Virtex

XCV800 device. Including extra interfac-

ing glue logic, and PAL/NTSC video

encoder driver logic, the core consumes

fewer than 8,000 slices and 26 block

RAMs. The implementation benefited

greatly from the following features of the

target device:

Ample high-performance block RAM

Fast I/Os

Extensive logic resources.

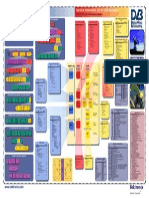

The functional blocks and simplified

interfaces of the Amphion CS6651

MPEG-2 video decoder IP core are

Spring 2003 Xcell Journal 00

Motion Compensation and

Picture Reconstruction

For each macro block in a

P-picture or B-picture, the

motion compensation unit

takes the decoded motion

vectors from the VLC

decoder and translates them

into row and column coor-

dinates for the prediction

samples in the reference

picture. The frame store

memory then requests these

samples and retrieves them

via the SDRAM interface.

The samples are combined

with other prediction sam-

ples, if necessary, to com-

plete the prediction for the

macro block.

The final stage of decod-

ing is to add the prediction

samples to the prediction

error corrections from the

inverse DCT unit and write

the reconstructed samples

into the frame store memo-

ry. If a block has no predict-

ed samples, then the sam-

ples from the inverse DCT

are the final samples and are

passed straight through.

Both motion compensation

and picture reconstruction

employ Virtex block RAMs for buffering

predictions, samples, or prediction errors

and final reconstructed samples.

SDRAM Interface

The frame store memory can be imple-

mented using a commodity PC100 or

better 64-Mb SDRAM part. The

SDRAM interface handles the mapping

of row and column motion compensation

prediction requests and reconstructed

sample writes into linear memory

addresses. Motion compensation places

particular memory bandwidth demands

on the decoder implementation. To

achieve adequate decoding performance,

this unit must then arbitrate between the

other functions, such as the display

DMA, which also access the frame store.

Display DMA

The display DMA unit retrieves decoded

samples from the frame-store memory line-

by-line for display. This unit has a config-

urable double-byte output interface for

luminance and chrominance samples and

can also perform chrominance upsampling

to a 4:2:2 format in the vertical direction.

This interface provides a number of hand-

shake signals and flags (not shown in

Figure 1) to easily allow for the addition of

extra logic, to create sync pulses suitable for

connecting the decoder to a NTSC or PAL

video encoder chip.

Host Interface and Control

Access to internal control, status and

video stream parameter registers within

the core is provided via the host interface.

Simple 32-bit read/write access to the

frame store is also available. In the

demonstration system, a host processor

controls the core to perform special

effects modes such as pause and fast-for-

ward in response to user commands.

Conclusion

MPEG-2 video decoding is likely to be an

important feature of many future products.

The Amphion CS6651 MPEG-2 video

decoder IP core implemented on a single

Xilinx Virtex Platform FPGA delivers

MPEG-2 video decode capability with

integrated SDRAM memory control and

display DMA.

For more information about Amphion

and its CS6651 video decoder, visit

www.amphion.com/cs6651.html.

Applications Software

00 Xcell Journal Spring 2003

ES_Data

8-bits

ES_Valid

ES_Stall

H_Addr

H_DataIn

H_DataOut

22-bits

32-bits

SD_DataOut

P_Data

P_DataAvail

P_DataStrobe

SD_DataIn

32-bits

16-bits

32-bits

Parser

VLC

Decoder

Inverse

Quant &

Run-Level

Decoder

IDCT

Motion

Comp.

Picture

Recon.

SDRAM

I/F

Host I/F

Control

Display

DMA

Figure 1 - Simplified block diagram of Amphion CS6651 MPEG-2 video decoder IP core

S-ar putea să vă placă și

- Atsc 3.0 - Nextgen TVDocument3 paginiAtsc 3.0 - Nextgen TVjohn BronsonÎncă nu există evaluări

- Implementation of A Streaming Camera Using An FPGA and CMOS Image SensorDocument8 paginiImplementation of A Streaming Camera Using An FPGA and CMOS Image SensorPravin WilfredÎncă nu există evaluări

- Embedded Lab: Kgisl Institute of Technology Department of Electronics and CommunicationDocument111 paginiEmbedded Lab: Kgisl Institute of Technology Department of Electronics and CommunicationJeeva NatarajanÎncă nu există evaluări

- Presented By: Priya Raina 13-516Document68 paginiPresented By: Priya Raina 13-516Priya RainaÎncă nu există evaluări

- ATM Terminal Design Based On Figure Print Recognition DocuDocument115 paginiATM Terminal Design Based On Figure Print Recognition DocuPraveen NaiduÎncă nu există evaluări

- Color Detection Using FPGA Based Smart CameraDocument19 paginiColor Detection Using FPGA Based Smart Cameratry199Încă nu există evaluări

- Master-Slave DSP Board for Digital Control SystemsDocument5 paginiMaster-Slave DSP Board for Digital Control Systemsfurious143Încă nu există evaluări

- DVB PosterDocument1 paginăDVB PosterVinay KrÎncă nu există evaluări

- MCES Group ActivityDocument55 paginiMCES Group ActivitykartiksdanÎncă nu există evaluări

- Design of Architecture and FPGA Implementation of A Video EncoderDocument9 paginiDesign of Architecture and FPGA Implementation of A Video EncoderBijoy Kumar UpadhyayaÎncă nu există evaluări

- Final PPT of CCSDS TC SystemDocument38 paginiFinal PPT of CCSDS TC SystemNavakanth Bydeti0% (1)

- Project Report (Sample)Document80 paginiProject Report (Sample)Swapnith VarmaÎncă nu există evaluări

- Raphics Ideo Ubsystem: Subsystem OverviewDocument16 paginiRaphics Ideo Ubsystem: Subsystem OverviewThomas A. EDISSONÎncă nu există evaluări

- DCT-Domain Embedded Memory Compression For Hybrid Video CodersDocument11 paginiDCT-Domain Embedded Memory Compression For Hybrid Video CodersPunit RonadÎncă nu există evaluări

- Video Compression's Quantum Leap: DesignfeatureDocument4 paginiVideo Compression's Quantum Leap: DesignfeaturebengaltigerÎncă nu există evaluări

- DSP Lab 21-09-2021Document78 paginiDSP Lab 21-09-2021POORNIMA PÎncă nu există evaluări

- Data SheetDocument17 paginiData Sheetvijay963Încă nu există evaluări

- Mpeg 1 Part2 VideoDocument107 paginiMpeg 1 Part2 Videomtim360Încă nu există evaluări

- The Novel Broadcast Encryption Method For Large Dynamically Changing User GroupsDocument8 paginiThe Novel Broadcast Encryption Method For Large Dynamically Changing User GroupsRavindra KumarÎncă nu există evaluări

- K L With Advanced Encryption Standard (AES) Receiver/DecoderDocument8 paginiK L With Advanced Encryption Standard (AES) Receiver/DecoderbilarodrigoÎncă nu există evaluări

- Image Capture Using PRP, Csi, and I C: Mc9328Mx21Document18 paginiImage Capture Using PRP, Csi, and I C: Mc9328Mx21Sharmili Nukapeyi NÎncă nu există evaluări

- Chameleon ChipDocument22 paginiChameleon ChipMegna UrsÎncă nu există evaluări

- Edma Controller: Level 1 Programme MemoryDocument5 paginiEdma Controller: Level 1 Programme MemoryAchmad ZuchalÎncă nu există evaluări

- ADPCM ImplementationDocument13 paginiADPCM ImplementationDumitru GheorgheÎncă nu există evaluări

- DSP Lab DemoDocument37 paginiDSP Lab Demosurendraloya99Încă nu există evaluări

- IJCER (WWW - Ijceronline.com) International Journal of Computational Engineering ResearchDocument4 paginiIJCER (WWW - Ijceronline.com) International Journal of Computational Engineering ResearchInternational Journal of computational Engineering research (IJCER)Încă nu există evaluări

- Compressed-Domain Video Watermarking For HDocument4 paginiCompressed-Domain Video Watermarking For HSmit KeniyaÎncă nu există evaluări

- XC Sysgen43Document3 paginiXC Sysgen43YogeeshHtÎncă nu există evaluări

- A Hybrid Transformation Technique For Advanced Video Coding: M. Ezhilarasan, P. ThambiduraiDocument7 paginiA Hybrid Transformation Technique For Advanced Video Coding: M. Ezhilarasan, P. ThambiduraiUbiquitous Computing and Communication JournalÎncă nu există evaluări

- Line BufferDocument11 paginiLine BufferTuan HuynhÎncă nu există evaluări

- Still Image CompressionDocument15 paginiStill Image CompressionDivya PolavaramÎncă nu există evaluări

- Image Compression Using High Efficient Video Coding (HEVC) TechniqueDocument3 paginiImage Compression Using High Efficient Video Coding (HEVC) TechniqueAnonymous gQOifzÎncă nu există evaluări

- Reference Material For EXP - 1Document26 paginiReference Material For EXP - 1Jatin YadavÎncă nu există evaluări

- DSP LabmanualDocument82 paginiDSP LabmanualHemanth SharmaÎncă nu există evaluări

- DSP Lab ManualDocument26 paginiDSP Lab ManualMadhan ReddyÎncă nu există evaluări

- Hardware-Software Codesign Lab ReportDocument15 paginiHardware-Software Codesign Lab ReportvaljokÎncă nu există evaluări

- Chameleon ChipDocument21 paginiChameleon Chip429by3100% (1)

- Design and Verification of High Speed Protocols and Algorithms in Digital Communication Systems Using Verilog and VHDLDocument5 paginiDesign and Verification of High Speed Protocols and Algorithms in Digital Communication Systems Using Verilog and VHDLChristo ElginÎncă nu există evaluări

- Dual Port RAMDocument16 paginiDual Port RAMAbbas Raza ZaidiÎncă nu există evaluări

- Manual For Cycle 1Document193 paginiManual For Cycle 1Seth GreeneÎncă nu există evaluări

- Final Exam Multimedia CommunicationsDocument10 paginiFinal Exam Multimedia CommunicationsArif CupuÎncă nu există evaluări

- II IP Core PSK DemodulatorDocument5 paginiII IP Core PSK DemodulatorfvseverÎncă nu există evaluări

- An1914 PDFDocument56 paginiAn1914 PDFUpama Das100% (1)

- 3-Phase Switched Reluctance Motor Control With Encoder Using DSP56F80xDocument56 pagini3-Phase Switched Reluctance Motor Control With Encoder Using DSP56F80xYusuf Ilker öztürkÎncă nu există evaluări

- Hitachi L37v01e A U l37vr1 l37v01 l37vp01 l42vp01Document68 paginiHitachi L37v01e A U l37vr1 l37v01 l37vp01 l42vp01Kostas AthanasiadisÎncă nu există evaluări

- Begin With C6712Document8 paginiBegin With C6712WinsweptÎncă nu există evaluări

- VLSI ProjectsDocument10 paginiVLSI ProjectsB Naresh Kumar ReddyÎncă nu există evaluări

- Study of Architecture of DSP TMS320C6748Document9 paginiStudy of Architecture of DSP TMS320C6748Varssha BÎncă nu există evaluări

- Complete IC and System Solutions For Advanced DVB-C PlatformsDocument4 paginiComplete IC and System Solutions For Advanced DVB-C PlatformsJorge Armando LaiÎncă nu există evaluări

- ATMEGA32 AND GRAPHICAL LCD BASED PORTABLE OSCILLOSCOPEDocument9 paginiATMEGA32 AND GRAPHICAL LCD BASED PORTABLE OSCILLOSCOPEbhvallabhaneniÎncă nu există evaluări

- Xapp495 S6TMDS Video InterfaceDocument16 paginiXapp495 S6TMDS Video InterfaceNông Văn DânÎncă nu există evaluări

- Intel Corporation - Intel IXP2400 Network Processor - 2nd Generation Intel NPUDocument13 paginiIntel Corporation - Intel IXP2400 Network Processor - 2nd Generation Intel NPUSundar RajanÎncă nu există evaluări

- ON2 VP6 Codec ExplainedDocument7 paginiON2 VP6 Codec ExplainedKannadasan VenugopalÎncă nu există evaluări

- A High Performance CABAC Decoding Architecture WebDocument9 paginiA High Performance CABAC Decoding Architecture WebHemanth KumarÎncă nu există evaluări

- Using The Psoc To Drive The NKK SmartswitchDocument2 paginiUsing The Psoc To Drive The NKK SmartswitchPVPPPÎncă nu există evaluări

- Image Pal Capturing DocumentDocument11 paginiImage Pal Capturing DocumentRajesh KhannaÎncă nu există evaluări

- ReviewDocument10 paginiReviewHarish VermaÎncă nu există evaluări

- Finnish Unified IRD Specifications Ver 4.0Document29 paginiFinnish Unified IRD Specifications Ver 4.0Gautam BalharaÎncă nu există evaluări

- FrequenciasDocument14 paginiFrequenciasSamuel Caetano MerlimÎncă nu există evaluări

- Beginners Guide For 9xxxHD Series 231208 enDocument37 paginiBeginners Guide For 9xxxHD Series 231208 enelgeneral-forokeys7539100% (5)

- IRDETODocument7 paginiIRDETOravigoliÎncă nu există evaluări

- LG 37,42lc2rr-Ml CH Ln62b SMDocument14 paginiLG 37,42lc2rr-Ml CH Ln62b SMHanif Rathore PrinceÎncă nu există evaluări

- ER Panasonic AG-HVX200 ManualDocument68 paginiER Panasonic AG-HVX200 ManualLauren PayanÎncă nu există evaluări

- DivX Plus HD BrochureDocument6 paginiDivX Plus HD BrochureZulhilmi Zimi IzzuddinÎncă nu există evaluări

- Bh7430pb - 2013 LG He Spec Sheet - EngDocument2 paginiBh7430pb - 2013 LG He Spec Sheet - EngOskrScribdÎncă nu există evaluări

- LG, Samsung, Sony and other top brand TVs and monitorsDocument21 paginiLG, Samsung, Sony and other top brand TVs and monitorsRubenÎncă nu există evaluări

- Digital TV Antenna Systems For Homes Handbook 2009 PDFDocument34 paginiDigital TV Antenna Systems For Homes Handbook 2009 PDFDa Harlequin GalÎncă nu există evaluări

- BE IRD 5502 - DatasheetDocument3 paginiBE IRD 5502 - DatasheetBakai BegalievÎncă nu există evaluări

- Vidcoder SettingsDocument6 paginiVidcoder SettingsIon DobreÎncă nu există evaluări

- High Quality, High Density, High Profile H.264 Encoder & DecoderDocument2 paginiHigh Quality, High Density, High Profile H.264 Encoder & DecoderHector CardosoÎncă nu există evaluări

- LCDscreen lg325700Document118 paginiLCDscreen lg325700nickcroweÎncă nu există evaluări

- Sub Decree 42 - Urbanization of Capital City Town and Urban Area - 2015 - EngDocument43 paginiSub Decree 42 - Urbanization of Capital City Town and Urban Area - 2015 - EngKasturi BSCEÎncă nu există evaluări

- Avid Studio 2.0 Ultimate Team VR PassportDocument8 paginiAvid Studio 2.0 Ultimate Team VR PassportAury ThomasÎncă nu există evaluări

- Samsung Bn94-00629q (SCH)Document10 paginiSamsung Bn94-00629q (SCH)gouroukiÎncă nu există evaluări

- DVB Scene33Document16 paginiDVB Scene33MAJLIS DAERAH KERIANÎncă nu există evaluări

- 560HD Spec SheetDocument2 pagini560HD Spec Sheetapi-19808945Încă nu există evaluări

- Owner's Manual: Integrated High Definition LCD TelevisionDocument64 paginiOwner's Manual: Integrated High Definition LCD TelevisionyamaharahÎncă nu există evaluări

- LC 26d4uDocument108 paginiLC 26d4ujdskes100% (1)

- Manual TV Samsung LN55B650Document197 paginiManual TV Samsung LN55B650Luis VieiraÎncă nu există evaluări

- High Definition Digital Satellite & Terrestrial Television Receiver and RecorderDocument2 paginiHigh Definition Digital Satellite & Terrestrial Television Receiver and Recordermohammed ahmedÎncă nu există evaluări

- Ki PlusDocument8 paginiKi PlusScotty BaileyÎncă nu există evaluări

- Ghost Adventures S13e01 Colorado Gold Mine HDTV x264-w4fDocument2 paginiGhost Adventures S13e01 Colorado Gold Mine HDTV x264-w4fAnonymous wISY6CIf8Încă nu există evaluări

- Logo Channel Name Genre: Audio Language(s) Subtitle(s) EPG Freq., Pol., Tr. Package FormatDocument8 paginiLogo Channel Name Genre: Audio Language(s) Subtitle(s) EPG Freq., Pol., Tr. Package FormatVasile TipcuÎncă nu există evaluări

- Hondao OLT EquipmentDocument22 paginiHondao OLT EquipmentYazmani Herrera MarcaÎncă nu există evaluări

- Multiformat SDTV Video Decoder ADV7183B: FeaturesDocument100 paginiMultiformat SDTV Video Decoder ADV7183B: FeaturesFernando PiedadeÎncă nu există evaluări