Documente Academic

Documente Profesional

Documente Cultură

Archi 8086

Încărcat de

Kavitha SubramaniamTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Archi 8086

Încărcat de

Kavitha SubramaniamDrepturi de autor:

Formate disponibile

13EC301-MICROPROCESSOR & INTERFACING

Chapter 2

Software Architecture of the 8088 and 8086 Microprocessors

2.1 Micro architecture o the !0!! a"# !0!$ Microproce%%or%

The micro architecture of a processor is its internal architecture- that is, the circuit

building blocks that implement the software and hardware architectures of the 8088/8086

microprocessors !ue to the need for additional features and higher performance, the

micro architecture of a microprocessor famil" e#ol#es o#er time $n fact, a new micro

architecture is introduced for $ntel%s 8086 famil" e#er" few "ears &ach new generation

of processors 'the 8088/8086, 80(86, 80)86, 80*86 and +entium processors, represents

significant changes in the micro architecture of the 8086

The micro architectures of 8088 and 8086 microprocessors are similar The" both

emplo" parallel processing The" contain two processing units- the bus interface unit

(BIU) and the execution unit (EU). .igure (-/'a, shows the internal architecture of 8088

and 8086 microprocessors

The 01$ connects the microprocessor to e2ternal de#ices 01$ performs following

operations-

/, $nstruction fetching

(, 3eading and writing data of data operands for memor"

), $nputting/outputting data for input/output peripherals

*, And other functions related to instruction and data ac4uisition

!ata transfer takes place o#er the s"stem bus S"stem bus includes an 8-bit bidirectional

data bus for the 8088 '/6 bits for the 8086,, a (0-bit address bus, and the signals need to

control transfers o#er the bus

To implement abo#e functions, the 0$1 contains the segment registers, the instruction

pointer, address generation adder, bus control logic, and an instruction 4ueue The figure

(-/'b, shows the bus interface unit of the 8088/8086 in more detail The 0$1 uses a

mechanism known as an instruction queue to implement pipelined architecture

The e2ecution unit is responsible for decoding and e2ecuting instructions The &1

performs the arithmetic, logic, and shift operations re4uired b" an instructions

The &1 consists of arithmetic logic unit 'A51,, status and control flags, general-purpose

registers, and temporar"-operand registers

2.2 Sot&are Mo#e' o the !0!!(!0!$ Microproce%%or

.igure (-( shows the software architecture of the 8088 microprocessor $t includes /)

/6-bit internal registers- the instruction pointer '$+,, four data registers 'A6, 06, 76,

and !6,, two pointer registers '0+ and S+,, two inde2 registers 'S$ and !$,, and four

segment registers '7S, !S, SS, and &S, $n addition to these registers, there is another

register called status register 'S3,, with nine of its implemented for status and control

flags

Prepare# )*+S.,a-itha & E.Pa#.a/AP(CSE Page /

13EC301-MICROPROCESSOR & INTERFACING

8088 software architecture implements independent memor" and input/output address

spaces Memor" address space is /,0*8,896 '/ Mb"te, in length and the $/: address

space is 68,8)6 b"tes '6*;b"tes, in length

2.3 Me.or* A##re%% Space a"# 0ata Or1a"i2atio"

The 8088%s /Mb"te memor" address space is organi<ed from software point of #iew as

indi#idual b"tes of data stored at consecuti#e addresses o#er range 00000

/6

to .....

/6

Prepare# )*+S.,a-itha & E.Pa#.a/AP(CSE Page (

13EC301-MICROPROCESSOR & INTERFACING

The memor" in an 8088 microcomputer is organi<ed as 8-bit b"tes The 8088 can access

an" two consecuti#e b"tes as a word of data The lower address b"te is called least

significant b"te of the word and the higher address b"te is its most significant b"te

.or efficient use of memor", words of data can be stored at either e#en- or odd-address

word boundar" The least significant bit of the address determines the t"pe of word

boundar" $t this bit is 0, the word is said to be held at an e#en-address boundar"= that is,

a word at e#en-address boundar" corresponds to two consecuti#e b"tes, with the least

significant b"te located at an e#en address

Prepare# )*+S.,a-itha & E.Pa#.a/AP(CSE Page )

13EC301-MICROPROCESSOR & INTERFACING

A word stored at an e#en-address boundar", such as 00000

/6

, 0000(

/6

3 and so on, is said

to be an aligned word That is, all aligned words are located at an address that is multiple

of ( :n the other hand, a word of data stored at an odd-address boundar", such as

0000/

/6

, 0000)

/6 ,

and so on, is called a misaligned word .igure (-8 shows some aligned

and misaligned words of data

>hen e2pressing addresses and data in he2adecimal form, it is common to use the letter

? to specif" the base

The double word is another data form that can be processed b" the 8088 microcomputer

A double word corresponds to four consecuti#e b"tes of data stored in memor"= an

e2ample of double-word is a pointer A pointer is a two-word address element that is

used to access data or code outside the current segment of memor" The word of this

pointer that is stored at the higher address is called the segment base address and the

word at the lower address is called the offset #alue !ouble word of data can be aligned

or misaligned

Prepare# )*+S.,a-itha & E.Pa#.a/AP(CSE Page *

13EC301-MICROPROCESSOR & INTERFACING

A##re%% Ph*%ica' .e.or* A'i1"e# &or#%

00008 ? 0"te 8

00009 ? 0"te 9

>ord

00006 ? 0"te 6 6

>ord

00008 ? 0"te 8 8

>ord

0000* ? 0"te * *

0000) ? 0"te )

>ord

0000( ? 0"te ( (

>ord

0000/ ? 0"te / /

>ord

00000 ? 0"te 0 0

Mi%a'i1"e# &or#%

Fi1ure 2.4 &2amples of aligned and misaligned data words

Prepare# )*+S.,a-itha & E.Pa#.a/AP(CSE Page 8

13EC301-MICROPROCESSOR & INTERFACING

Prepare# )*+S.,a-itha & E.Pa#.a/AP(CSE Page 6

13EC301-MICROPROCESSOR & INTERFACING

2.5 0ata t*pe%

.ollowing are the data t"pes supported b" 8088 microprocessor-

/, 6"%i1"e# i"te1er "u.7er%- each t"pe of integer can be either b"te-wide or

word-wide .igure (-8'a, shows an unsigned b"te integer= this data t"pe can be used

to represent decimal numbers in the range 0 through (88 The unsigned word integer

is shown in figure (-8'b,= it can be used to represent decimal numbers in the range 0

through 68,8)8

MS) 8S)

09 00

:a;

MS) 8S)

014 00

:7;

Fi1ure% 2-! :a; 6"%i1"e# 7*te i"te1er. :7; 6"%i1"e# &or# i"te1er.

(, Si1"e# i"te1er "u.7er%- each t"pe of integer can be either b"te-wide or

word-wide The" are similar to unsigned integer numbers e2cept the most significant

b"te in signed integer data t"pe is a sign bit A <ero in this position identifies a

positi#e number .ig (-@'a, shows a signed b"te integer= this data t"pe can be used

to represent decimal numbers in the range A/(9 to B/(8 The signed word integer is

shown in fig (-@'b,= it can be used to represent decimal numbers in the range

A)(,969 to B)(,968

), )i"ar*-co#e# #eci.a' :)C0; "u.7er%- 07! data can be stored on either

unpacked or packed form $n unpacked 07!, a single 07! digit is stored in four

least significant bits, and the four bits are set to 0 $n packed 07!, two 07!

numbers are stored in a b"te

*, ASCII :A.erica" Sta"#ar# Co#e I"or.atio" I"tercha"1e; - AS7$$ codes can

be processed b" 8088 microprocessor

Prepare# )*+S.,a-itha & E.Pa#.a/AP(CSE Page 9

13EC301-MICROPROCESSOR & INTERFACING

MS) 8S)

09 00

%i1" 7it

:a;

MS) 8S)

014 00

%i1" 7it

:7;

Fi1ure% 2-< :a; Si1"e# 7*te i"te1er. :7; Si1"e# &or# i"te1er.

Prepare# )*+S.,a-itha & E.Pa#.a/AP(CSE Page 8

13EC301-MICROPROCESSOR & INTERFACING

2.4 Se1.e"t Re1i%ter% a"# Me.or* Se1.e"tatio"

$n 8088, the /Mb"tes of memor" is partitioned into 6*;b"te segments A segment

represents an independentl" addressable unit of memor" consisting of 6*; consecuti#e

b"te-wide storage locations &ach segment is assigned a base address that identifies its

starting point-that is, its lowest b"te-storage location

:nl" four of these 6*;b"te segments can be acti#e at a time- the code segment, stack

segment, data segment, and e2tra segment The segments of memor" that are acti#e, as

shown in fig (-/(, are identified b" the #alues of addresses held in the 8088%s four

Prepare# )*+S.,a-itha & E.Pa#.a/AP(CSE Page @

13EC301-MICROPROCESSOR & INTERFACING

internal segment registers- 7S 'code segment,, SS 'stack segment,, !S 'data segment,,

and &S 'e2tra segment, &ach of these registers contains /6-bit base address that points

to the lowest addressed b"te of the segment in memor" .our segments gi#e a ma2imum

of (86;b"tes of acti#e memor" :f this , 6*;b"tes are for code 'program storage,,

6*;b"tes are for a stack, and /(8;b"tes are for data storage

.ig (-/) shows the segmentation of memor"

2.$ 0e#icate#3 Re%er-e#3 a"# Ge"era'-u%e Me.or*

$n 8088 microprocessor, not all /Mb"tes of memor" are a#ailable to user Some memor"

is reser#ed for storage of special functions

Prepare# )*+S.,a-itha & E.Pa#.a/AP(CSE Page /0

13EC301-MICROPROCESSOR & INTERFACING

.ig (-/* shows reser#ed, dedicated-use and general-use parts of the 8088/8086%s

address space Storage locations from 00000

/6

to 000/)

/6

are dedicated and those from

address 000/*

/6

to 0009.

/6

are reser#ed These /(8 b"tes of memor" are used for storage

of the pointers to interrupt ser#ice routines The dedicated part is used for storage of the

pointers for the 8088%s internal interrupts and e2ceptions :n the other hand, the reser#ed

locations are sa#ed for storage of pointers that are used b" the user-defined interrupts

The part of address space labeled open in fig (-/* is general-use memor" and is where

data or instructions of the program are stored

2.9 I"%tructio" Poi"ter

The instruction pointer '$+, is /6 bits in length and identifies the location of the ne2t

word of the instruction code to be fetched from the current code segment of the memor"

The $+ is similar to a program counter but it contains the offset of the ne2t word of

instruction code instead of its actual address This is because the $+ and 7S are both /6

bits in length, but a (0-bit address is needed to access memor" $nternal to the 8088, the

offset in $+ is combined with the current #alue in 7S to generate the address of the

instruction code Therefore, the #alue of the address for the ne2t code access is often

denoted as 7S- $+

2.! 0ata Re1i%ter%

As shown in fig (-(, four general purpose data registers are located within the 8088

!uring program e2ecution, the" are used for temporar" storage of fre4uentl" used

intermediate results Their contents can be read, loaded, or modified through software

An" of the general-purpose data registers can be used as the source or destination of an

operand during an arithmetic operation such as A!!, or a logic operation such as AC!

Prepare# )*+S.,a-itha & E.Pa#.a/AP(CSE Page //

13EC301-MICROPROCESSOR & INTERFACING

The four registers, known as the data registers, are shown in more detail in fig (-/8'a,

The" are referred to as the accumulator register 'A,, the base register '0,, the count

register '7,, and the data register '!, .ig (-/8'b, summari<es the operations

2.< Poi"ter a"# I"#e= Re1i%ter

There are four other general-purpose registers shown in fig (-(- two pointer registers

and two inde2 registers The" are used to store offset addresses An offset address

represents the displacement of a storage location in memor" from the segment base

address in a segment register-that is , the" are used as a pointer or inde2 to select a

specific storage location within a 6*;b"te segment memor" Dalues held in the inde2

registers are used to reference data relati#e to the data segment or e2tra segment register,

and the pointer register are used to store offset addresses of memor" locations relati#e to

the stack segment register

.igure (-/6 shows that the two pointer registers are the stack pointer 'S+, and base

pointer '0+, The #alues in S+ and 0+ are used as offsets from the current #alue of the

SS during the e2ecution of instructions that in#ol#es the stack segment of memor" and

permits eas" access to storage locations in the stack part of memor" 0+ also represents

an offset relati#e to the SS register $t is used to access data within the stack segment of

memor"

The inde2 registers are used to hold offset addresses for instructions that access data

stored in the data segment of the memor" and are automaticall" combined with the #alue

in the !S or &S register during address calculation The inde2 register can also be used

as source or destination registers in the arithmetic and logical operations

Prepare# )*+S.,a-itha & E.Pa#.a/AP(CSE Page /(

13EC301-MICROPROCESSOR & INTERFACING

2.10 Statu% Re1i%ter

The status register, also called the flags register, is /6-bit register with in 8088

This register is shown in more detail in fig (-/9 Cine of its bits are implemented Si2 of

these represent status flags- the carr" flag '7.,, parit" flag '+.,, au2iliar" flag 'A.,, <ero

flag 'E.,, sign flag 'S.,, and o#erflow ':., The logic state of these flags indicates

conditions that are produced as the result of e2ecuting an instruction

The summar" of operation of these flags is gi#en below-

/ The carr" flag '7.,- 7. is set if there is a carr"-out or a borrow-in for the most

significant bit of the result during the e2ecution of an arithmetic instruction

:therwise, 7. is reset

( The parit" flag '+.,- +. is set if the result produced b" the instruction has e#en

parit"-that is, it contains an e#en number of bits at the / logic le#el $f parit" is odd,

+. is reset

) The au2iliar" carr" flag 'A.,- A. is set if there is a carr"-out from the low nibble

into the high nibble or a borrow-in from the high nibble into the low nibble of the

lower b"te in a /6-bit word :therwise, A. is reset

* the <ero flag 'E.,- E. is set if the result of an arithmetic or logic operation is <ero

:therwise, E. is reset

8 the sign flag 'S.,- The MS0 of the result is copied into S. Thus S. is set if the

result is a negati#e number or reset if it is positi#e

6 the o#erflow flag ':.,- >hen :. is set, it indicates that the signed result is out of

range $f the result is not out of range, :. remains reset

The 8088 pro#ides instructions within its instruction set that are able to use these flags

to alter the se4uence in which the program is e2ecuted The other three implemented

flag bits-direction flag '!.,, interrupt enable flag '$.,, and trap flag 'T.,- are control

flags These flags are pro#ided to control functions of 8088 as follows-

/ The trap flag 'T.,- if T. is set, the 8088 goes into the single-step mode of operation

( The interrupt flag '$.,- for 8088 to recogni<e maskable interrupt re4uests at its $CT

$nput, the $. flag must be set >hen $. is reset, re4uests at $CT are ignored and the

maskable interrupt interface is disabled

Prepare# )*+S.,a-itha & E.Pa#.a/AP(CSE Page /)

13EC301-MICROPROCESSOR & INTERFACING

) The direction flag '!.,- the logic le#el of !. determines the direction in which

string operations will occur >hen set, the string instruction automaticall"

decrements the address 3esetting !. causes the string address to be incremented-

that is, data transfers proceed from the high address

2.11 Ge"erati"1 a Me.or* A##re%%

A segment base and an offset describe a logical address in the 8088 microcomputer As

shown in fig (-/8, both the segment base and offset are /6-bit 4uantities since all

registers and memor" locations used in address calculations are /6 bits long The

ph"sical addresses that are used to access memor" are (0 bits in length The generation

of the ph"sical address in#ol#es combining a /6-bit offset #alue that is located in the

instruction pointer= a base register, an inde2 register, or a pointer register and a /6-bit

segment base #alue that is located in one of the segment registers

Prepare# )*+S.,a-itha & E.Pa#.a/AP(CSE Page /*

13EC301-MICROPROCESSOR & INTERFACING

Prepare# )*+S.,a-itha & E.Pa#.a/AP(CSE Page /8

13EC301-MICROPROCESSOR & INTERFACING

The source of the offset #alue depends on which t"pe of memor" reference is taking

place $t can be base pointer '0+, register, base '06, register, source inde2 'S$, register,

destination inde2 '!$, register, or instruction pointer '$+, An offset can e#en be formed

from the contents of se#eral of these registers :n the other hand, the segment base #alue

alwa"s resides in one of the segment registers- 7S, !S, SS, or &S

2.12 The Stac>

The stack is implemented in the memor" of the 8088 microcomputer and is used for

temporar" storage of information such as data or addresses The stack is 6*;b"tes long

and is organi<ed from a software point of #iew as )(;words

Prepare# )*+S.,a-itha & E.Pa#.a/AP(CSE Page /6

13EC301-MICROPROCESSOR & INTERFACING

.ig

(-(( shows that the lowest address word in the current stack is pointed to b" the segment

base #alue in the SS register The contents of the S+ and 0+ registers are used as offsets

into the stack segment of memor"

.rom the figure (-(( we can see that S+ contains an offset #alue that points to a storage

location in the current stack segment The address obtained from the contents of SS and

S+ 'SS-S+, is the ph"sical address of the last storage location in the stack to which data

were pushed This memor" address is known as the top of stack At the microcomputer%s

start-up, the #alue in S+ is initiali<ed to .....

/6

7ombining this #alue with the current

#alue in the SS gi#es the highest address word location in the stack 'SS- ...&

/6

,-that is,

the bottom of the stack

The 8088 can push data and address information onto the stack from its internal registers

or a storage location in memor" !ata transferred to and from the stack are word-wide,

not b"te-wide &ach time a word is to be pushed onto the top of the stack, the #alue in S+

is first automaticall" decremented b" two, and then contents of the register are written

into the stack part of memor"

Prepare# )*+S.,a-itha & E.Pa#.a/AP(CSE Page /9

13EC301-MICROPROCESSOR & INTERFACING

Prepare# )*+S.,a-itha & E.Pa#.a/AP(CSE Page /8

13EC301-MICROPROCESSOR & INTERFACING

2.13 I"put(Output A##re%% Space

The 8088 has separate memor" and input/output '$/:, address space The $/: address

space is the place where $/: interfaces, such as printer and terminal ports, are

implemented .ig (-(8 shows a map of the 8088%s $/: address space This address

range is 00000

/6

to .....

/6

This represents Fust 6*;b"te addresses= therefore, unlike

memor", $/: addresses are onl" /6 bits long &ach of these addresses corresponds to one

b"te-wide $/: port

Prepare# )*+S.,a-itha & E.Pa#.a/AP(CSE Page /@

13EC301-MICROPROCESSOR & INTERFACING

The part of the map from address 00000

/6

through 000..

/6

is referred to as page 0

7ertain of the 8088%s $/: instructions can perform onl" input or output data-transfer

operations to $/: de#ices located in this part of the $/: address space :ther $/:

instructions can input or output data for de#ices an"where in the $/: address space $/:

data transfers can be b"te-wide or word-wide

Prepare# )*+S.,a-itha & E.Pa#.a/AP(CSE Page (0

S-ar putea să vă placă și

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (587)

- Welcome Slides For II & III Yr Students About R17 AmendmentsDocument33 paginiWelcome Slides For II & III Yr Students About R17 AmendmentsKavitha SubramaniamÎncă nu există evaluări

- One Credit Course: Chef Automation & Saas Ii CseDocument4 paginiOne Credit Course: Chef Automation & Saas Ii CseKavitha SubramaniamÎncă nu există evaluări

- Problem Statements FOR HACKATHONDocument4 paginiProblem Statements FOR HACKATHONKavitha SubramaniamÎncă nu există evaluări

- Mobile App ANSWER KEYDocument5 paginiMobile App ANSWER KEYKavitha SubramaniamÎncă nu există evaluări

- Google Classroom DetailsDocument1 paginăGoogle Classroom DetailsKavitha SubramaniamÎncă nu există evaluări

- Cse Board of Studies - 9 AttendanceDocument9 paginiCse Board of Studies - 9 AttendanceKavitha SubramaniamÎncă nu există evaluări

- Cse Board of Studies - 9 AttendanceDocument9 paginiCse Board of Studies - 9 AttendanceKavitha SubramaniamÎncă nu există evaluări

- SAS One CreditDocument23 paginiSAS One CreditKavitha SubramaniamÎncă nu există evaluări

- True B.) False: Sas QuestionsDocument6 paginiTrue B.) False: Sas QuestionsKavitha SubramaniamÎncă nu există evaluări

- SAS One CreditDocument23 paginiSAS One CreditKavitha SubramaniamÎncă nu există evaluări

- Google Classroom DetailsDocument1 paginăGoogle Classroom DetailsKavitha SubramaniamÎncă nu există evaluări

- Lab Arrear List Upto Vi SemDocument205 paginiLab Arrear List Upto Vi SemKavitha SubramaniamÎncă nu există evaluări

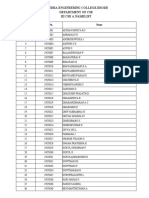

- Nandha Engineering College, Erode Department of Cse Iii Cse A NamelistDocument5 paginiNandha Engineering College, Erode Department of Cse Iii Cse A NamelistKavitha SubramaniamÎncă nu există evaluări

- One Credit Course: Chef Automation & Saas Ii CseDocument4 paginiOne Credit Course: Chef Automation & Saas Ii CseKavitha SubramaniamÎncă nu există evaluări

- Welcome Slides For II & III Yr Students About R17 AmendmentsDocument33 paginiWelcome Slides For II & III Yr Students About R17 AmendmentsKavitha SubramaniamÎncă nu există evaluări

- True B.) False: Sas QuestionsDocument6 paginiTrue B.) False: Sas QuestionsKavitha SubramaniamÎncă nu există evaluări

- Po and Co MappingDocument1 paginăPo and Co MappingKavitha SubramaniamÎncă nu există evaluări

- Nandha Engineering College, Erode Department of Cse Iii Cse A NamelistDocument5 paginiNandha Engineering College, Erode Department of Cse Iii Cse A NamelistKavitha SubramaniamÎncă nu există evaluări

- No.: E Mail ID:: (Can Be Claimed Once But Cannot Be Every Year)Document3 paginiNo.: E Mail ID:: (Can Be Claimed Once But Cannot Be Every Year)Kavitha SubramaniamÎncă nu există evaluări

- Student Databse For Letter GenerationDocument1 paginăStudent Databse For Letter GenerationKavitha SubramaniamÎncă nu există evaluări

- Expected Marks To Attainment 0.7 0.7 0.7 0.7 0.7 1.4 1.4 1.4 1.4 1.4 4.9 7 2.8 4.9 4.9 9.8 9.8Document6 paginiExpected Marks To Attainment 0.7 0.7 0.7 0.7 0.7 1.4 1.4 1.4 1.4 1.4 4.9 7 2.8 4.9 4.9 9.8 9.8Kavitha SubramaniamÎncă nu există evaluări

- NANDHA ENGINEERING COLLEGE CSE ONLINE TESTSDocument4 paginiNANDHA ENGINEERING COLLEGE CSE ONLINE TESTSKavitha SubramaniamÎncă nu există evaluări

- Staff & Class Handling (I, II, III, IV Yr UG-PG)Document1 paginăStaff & Class Handling (I, II, III, IV Yr UG-PG)Kavitha SubramaniamÎncă nu există evaluări

- Co ProcessorDocument42 paginiCo ProcessorKavitha SubramaniamÎncă nu există evaluări

- Nandha Engineering College, Erode-52: Continuous Assessment Test - III 15Cs404 Mobile ComputingDocument2 paginiNandha Engineering College, Erode-52: Continuous Assessment Test - III 15Cs404 Mobile ComputingKavitha SubramaniamÎncă nu există evaluări

- DMA Direct memory access explainedDocument22 paginiDMA Direct memory access explainedKavitha SubramaniamÎncă nu există evaluări

- 80286Document28 pagini80286Kavitha SubramaniamÎncă nu există evaluări

- 8279Document32 pagini8279Kavitha SubramaniamÎncă nu există evaluări

- IOP-Accessing and Communicating with I/O DevicesDocument22 paginiIOP-Accessing and Communicating with I/O DevicesSrikanth PrasadÎncă nu există evaluări

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (119)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- TW MX3D PacketWalkthroughDocument138 paginiTW MX3D PacketWalkthroughviatr0nicÎncă nu există evaluări

- Arc Hi Cad Big Building WhitepaperDocument31 paginiArc Hi Cad Big Building WhitepaperElena Iulia CucoleaÎncă nu există evaluări

- Bulk SMS Messaging and Short Code CampaignDocument2 paginiBulk SMS Messaging and Short Code CampaignBulk SmsÎncă nu există evaluări

- ICT Net - Best Practice BrochureDocument44 paginiICT Net - Best Practice BrochureICTNetworkÎncă nu există evaluări

- SPL MMC 1 BrochureDocument2 paginiSPL MMC 1 BrochureCarlos LazaÎncă nu există evaluări

- Mic 8051Document1 paginăMic 8051DaisyQueenÎncă nu există evaluări

- Adding ECC Custom Fields in CRM Web UI ERP Order Using LORDDocument15 paginiAdding ECC Custom Fields in CRM Web UI ERP Order Using LORDchandrasekhar_sundarÎncă nu există evaluări

- MQ47856 PDFDocument127 paginiMQ47856 PDFDon DonÎncă nu există evaluări

- Index PDFDocument7 paginiIndex PDFSPY VLOGSÎncă nu există evaluări

- High-Availability Load Balancing With The Brocade ServerIron ADXDocument36 paginiHigh-Availability Load Balancing With The Brocade ServerIron ADXom2005Încă nu există evaluări

- Test TCPDocument6 paginiTest TCPTahrkusÎncă nu există evaluări

- Belarc AdvisorDocument5 paginiBelarc Advisorneel gÎncă nu există evaluări

- Pharmacy SystemDocument63 paginiPharmacy Systemsurenderb63% (19)

- Install Software Enabler in VNXDocument7 paginiInstall Software Enabler in VNXarungarg_itÎncă nu există evaluări

- Thales - ToIP TEOZ - White Paper - EN Ed5.0Document28 paginiThales - ToIP TEOZ - White Paper - EN Ed5.0Cristian RozasÎncă nu există evaluări

- 8 K Technology SeminarDocument28 pagini8 K Technology SeminarMahaManthraÎncă nu există evaluări

- Section G5E-Electrical Power - A: Tentative 1 Faculty of Electrical and Computer EngineeringDocument5 paginiSection G5E-Electrical Power - A: Tentative 1 Faculty of Electrical and Computer Engineeringeyob feshaÎncă nu există evaluări

- Sound Editing LAB: Digital Audio WorkstationsDocument11 paginiSound Editing LAB: Digital Audio Workstationsapi-427379542Încă nu există evaluări

- Backdoor MAC Eleanor FinalDocument10 paginiBackdoor MAC Eleanor FinalElias Alboadicto Villagrán DonaireÎncă nu există evaluări

- USSD Center Databook enDocument19 paginiUSSD Center Databook enmail4290Încă nu există evaluări

- TRANS TV On Satelit Telkom 3S 118 DerajatDocument2 paginiTRANS TV On Satelit Telkom 3S 118 DerajatAgam Alfian NazriÎncă nu există evaluări

- Internet of ThingsDocument14 paginiInternet of Thingssol therese cairelÎncă nu există evaluări

- 11unit 3 Data Path ImplementationDocument20 pagini11unit 3 Data Path ImplementationsnÎncă nu există evaluări

- History of computers from abacus to fourth generationDocument4 paginiHistory of computers from abacus to fourth generationAlahin VeraÎncă nu există evaluări

- TestKing 642 975Document5 paginiTestKing 642 975vitthalbÎncă nu există evaluări

- Introduction To Graphics and MultimediaDocument47 paginiIntroduction To Graphics and MultimediafeisalÎncă nu există evaluări

- MNIT Resume StructureDocument3 paginiMNIT Resume StructurePrabhaMeenaÎncă nu există evaluări

- How Does A Data Diode WorkDocument5 paginiHow Does A Data Diode WorkleroÎncă nu există evaluări

- Juniper M5 M10 DatasheetDocument6 paginiJuniper M5 M10 DatasheetMohammed Ali ZainÎncă nu există evaluări

- Designing Embedded Communications Software - SRIDHAR, T PDFDocument245 paginiDesigning Embedded Communications Software - SRIDHAR, T PDFademarhÎncă nu există evaluări