Documente Academic

Documente Profesional

Documente Cultură

Jurnal Kutub Empat

Încărcat de

Muhammad Haekal0 evaluări0% au considerat acest document util (0 voturi)

183 vizualizări7 paginiThis document discusses modeling and design centering of integrated continuous-time filters. It proposes using a two-port transmission line parameter approach for modeling filters, compared to the conventional state-space method. As an example, it models a second-order Butterworth low-pass Gm-C filter with Cochlea architecture operating at 0.5V supply in 0.18um CMOS process. The two-port approach is shown to provide better accuracy than state-space modeling for low voltage design by considering effects like subthreshold operation that state-space neglects.

Descriere originală:

aa

Drepturi de autor

© © All Rights Reserved

Formate disponibile

PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentThis document discusses modeling and design centering of integrated continuous-time filters. It proposes using a two-port transmission line parameter approach for modeling filters, compared to the conventional state-space method. As an example, it models a second-order Butterworth low-pass Gm-C filter with Cochlea architecture operating at 0.5V supply in 0.18um CMOS process. The two-port approach is shown to provide better accuracy than state-space modeling for low voltage design by considering effects like subthreshold operation that state-space neglects.

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

183 vizualizări7 paginiJurnal Kutub Empat

Încărcat de

Muhammad HaekalThis document discusses modeling and design centering of integrated continuous-time filters. It proposes using a two-port transmission line parameter approach for modeling filters, compared to the conventional state-space method. As an example, it models a second-order Butterworth low-pass Gm-C filter with Cochlea architecture operating at 0.5V supply in 0.18um CMOS process. The two-port approach is shown to provide better accuracy than state-space modeling for low voltage design by considering effects like subthreshold operation that state-space neglects.

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 7

I nternational J ournal of Advanced Computer Research (I SSN (print): 2249-7277 I SSN (online): 2277-7970)

Volume-2 Number-4 I ssue-6 December-2012

156

Two-Port Transmission Line Parameters Approach Modeling and Design

Centering of Integrated Continuous-Time Filters

Vasantha M.H.

1

, Tonse Laxminidhi

2

Dept. of Electronics and Communication Engineering

NITK, Surathkal, Mangalore, India.

1

vasant.iitm@gmail .com ,

2

laxminidhi_t@yahoo.com

Abstract

Design centering is one of the important process

followed for the accurate design of integrated

continuous time filters where the filter frequency

response is tuned to match the ideal in presence of

non-idealities such as finite gain of the

OTAs/Opamps and parasitics. One of the efficient

method adopted is the space-mapping where the

filter response is tuned in the model space and the

results are interpreted in the actual filter space

resulting in a time efficient process. This method

demands the filter to be modeled and state-space

approach has been the choice for modeling. This

paper proposes a two- port transmission-line

parameter based approach for modeling a class of

filters. The paper compares the proposed process

with that of the conventional state-space method.

The demonstration is carried out on a 2

nd

order

Butterworth low pass Gm-C filter having Cochlea

architecture. The filter is designed to operate on a

0.5 V supply in 0.18 m standard CMOS process.

The paper brings out the limitations of state-space

based approach for accurate modeling in the regime

of low voltage design and demonstrates how the

proposed two-port parameter based approach can be

used for better accuracy.

Keywords

Design centering, Two-port transmission line,

Continuous-time filters, State-space method, low-voltage

1. Introduction

According to Electronic Design Automation (EDA)

magazine on March 21, 2005[1], analog components

use, on average, 20% of the integrated circuit area

and also reported that 75% of all integrated circuits

would contain analog components. At the same time,

the analog components require around 40% of the

integrated circuits design effort and are responsible

for about 50% of the design re-spins. Analog design

automation is needed to improve the design quality

and reduce the design effort, as more and more

analog circuits are being integrated into ICs along

with digital circuits. In view of these challenges there

is need for a more efficient and reliable design

approach to be followed in the field of analog circuit.

These requirements drive the designers to rely

heavily on CAD in order to reduce the time- to-

design and errors in designing/modeling circuits.

Like in any design cycle, the design of analog circuits

(amplifiers, filters etc. ) starts with a set of

specifications. Architecture is then chosen to meet

the specifications. The initial design of the circuit,

typically, assumes ideal devices/elements. With this

assumption a basic schematic is designed using CAD

tools. However, the actual results from the schematic,

when technology specific circuit elements are used,

will deviate from the ideal. In CMOS circuits the

deviation is normally attributed to finite g

m

r

0

product

of transistors and parasitic capacitors. It becomes

necessary to design center the filter to achieve

response that is in close match with the desired

response even in presence of non-idealities. One such

design-centering technique used for integrated

continuous- time filters is presented in [2].

A simple design centering technique for integrated

continuous time Transconductor-Capacitor (Gm C)

filters is presented in [2]. Due to the fully-differential

architecture, chosen for this filter, the parasitic

capacitances appearing at the integrating nodes with-

respect-to small signal ground have the dominating

effect on the response. The effect of any inter-node

parasitic capacitance is made small by design and a

careful layout technique. The above assumptions

make the design centering process simple which is

I nternational J ournal of Advanced Computer Research (I SSN (print): 2249-7277 I SSN (online): 2277-7970)

Volume-2 Number-4 I ssue-6 December-2012

157

evident from the paper. However, when the filter has

a single ended architecture, for example Cochlea

Architecture [3], the above assumption may not be

valid if the inter node capacitance is a significant

fraction of the integrating capacitor.

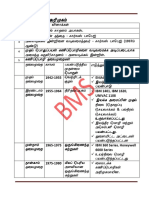

A course model is used for design centering the filter

in [2] and is arrived using state-space approach. The

state- space model of the filter is arrived by writing

down the small-signal equivalent circuit.

Transconductor is modeled as an equivalent circuit

consisting of a tranconductance (g

m

), output

conductance g

0

, input parasitic capacitance C

in

and

output parasitic capacitance C

p

as shown in

Fig.1(a). It is to be noted that while modeling, the

effect of overlap capacitances is neglected and is

assumed that all parasitic capacitances appear in

parallel with the integrating capacitors. If C

n

is the

capacitance value to be present at a given node for a

desired frequency response, it is clear from the

Fig.1(a) that the capacitance to be inserted (C

i

) at

that node can be easily found by subtracting total

parasitic capacitance appearing at that node from Cn .

In presence of gate overlap capacitance (C

c

), the

equivalent circuit of the transconductor can be drawn

as in Fig.1 (b). In such a case the state-space model

of the filter used in [2] will not be accurate enough

due to following reasons- (a) possible frequency

dependent Miller effect (b) addition of parasitic

poles/zeros. It is not possible to adopt the design

centering technique laid down in [2] as it is. In this

paper an attempt is made to address this issue,

especially in the regime of low voltage design.

Scaling dimensions in CMOS technology require

proportional scaling in supply voltage as well [4]. An

important factor concerning analog circuit design is

that the threshold voltage of transistors in future

standard CMOS technologies does not scale with

supply voltage and is projected to remain about 0.25

V [5]. With lower supply voltage, for example 0.5 V,

there exist a voltage headroom issue due to higher

threshold voltage and is found to be critical. In this

situation the transistor may operate in weak

inversion or in subthreshold region. In such a

scenario while modelling circuits one need to

consider subthreshold effects. Therefore the simple

design centering technique proposed in[2] for filter

operating at 3.3 V supply, that use state-space model

is not suitable for circuits operating at low voltage if

one needs to consider sub-threshold effects.

Two port parameter based representation is one of the

methods used to model a linear system. This method

can be readily adopted to model continuous-time

filters as they are assumed to be linear for small-

signal. Two-port transmission line parameter

(ABCDparameter) model is one such method that can

be effectively used for cascaded networks. This

method is simple and has couple of advantages over

other methods. Recent publications [6], [7] showed

that there is increase in the application of two-port

transmission line approach for better understanding

of circuits.

In this work a bulk driven low voltage, low frequency

Continuous- time Cochlea second order Butterworth

low pass filter using Gm -C technique is designed.

The filter is designed to operate at 0.5 V supply [8]

and is used as a test-vehicle to explore the merits of

two-port transmission parameter based modeling over

state-space based approach for design centering the

filter. The rest of paper is organized as follows.

Section 2 details the architecture of Cochlea filter.

Section 3 details the transconductor circuit design for

the realization of 2nd order low pass filter. The state

space approach and two port transmission line

parameter used to build the model of the filter are

given in section 4. In section 5 simulation results are

discussed and conclusions are drawn in section 6.

Figure 1. Equivalent circuit for non-ideal

transconductor (a) Without gate-overlap

capacitance (b) With gate-overlap capacitance

Figure 2. Schematic of Cochlea

Filter

I nternational J ournal of Advanced Computer Research (I SSN (print): 2249-7277 I SSN (online): 2277-7970)

Volume-2 Number-4 I ssue-6 December-2012

158

2. Cochlea filter

The filter designed in this work use G

m

C approach

and Cochlea architecture [3]. The schematic of

second order low pass Cochlea filter is shown in

Fig.2. g

m1

, g

m2

and g

m3

are differential-in single-

ended-out transconductors. C

i1

and C

i2

are the

integrating capacitors. The transfer function V

out

(s)

of the filter can be written as

The Cut-off frequency

0

and the Quality factor Q of

the filter are

It is clear from the expressions that the filter can be

tuned for a given bandwidth

0

and quality factor Q

by proper choice of transconductances and

capacitances. If the transconductors, realized, are

bulk-driven, as is the case with this paper, the

transconductances g

m

in (1), (2) and (3) will be

replaced by bulk-transconductances (g

mb

).

3. Bulk-driven transconductor

The differential-in single-ended-out bulk-driven

transcon- ductor used for the filter realization is

shown in Fig.3.

M

1

and M

2

are the PMOS input transistors and M

3

and M

4

forms NMOS current mirror load. v

ip

and

v

im

are the differential inputs and v

out

as the single-

ended output. The transconductor designed in 180 nm

CMOS process to operate at a power supply of 0.5 V.

The input common mode voltage of the

transconductor is fixed at 0.25 V and the gates of M

1

and M

2

are biased to carry quiescent current of 2 A.

The designed transconductor provide a DC gain of

23.76 dB and has a Unity-Gain-Bandwidth (UGB) of

11.65 MHz.

A Cochlea filter having Butterworth response is

designed using above transconductor for a bandwidth

of 1MHz. The integrating capacitors C

i1

and C

i2

decides the filter cut-off frequency under ideal

conditions if transconductance is fixed as per (2)

and (3). But non-idealities of the OTA like parasitic

capacitance, finite output impedance and finite input

impedance cause the frequency response to deviate

from the Butterworth response. This effect is clearly

seen in the magnitude response of filter shown in Fig.

4. Typically filter response is brought back to ideal or

near ideal by tuning integrating capacitor with the

help of design centering process. Space mapping is

one such technique that is proved to be effective for

G

m

-

C filters [2]. This technique requires the entire

filter to be modelled and as mentioned in the section

1, the state-space model is commonly used.

4. Model of the Cochlea filter

A. State-space approach based model

In order to analyze the limitations of the design

centering process laid down in [2], the Cochlea filter

is modeled in a manner similar to that given in [2].

The Equivalent circuit of the filter considering the

finite output resistance is shown in Fig. 5. At the

Figure 4. Magnitude response of Ideal filter and

Transistor level filter before design centering

Figure 3. Schematic of Bulk driven Transconductor

I nternational J ournal of Advanced Computer Research (I SSN (print): 2249-7277 I SSN (online): 2277-7970)

Volume-2 Number-4 I ssue-6 December-2012

159

intermediate node x, R

x

is the effective resistance

seen at node x and C

x

is the effective capacitance

seen at node x with respect to small signal

ground which includes the total parasitic

capacitances and intended integrating capacitor C

i1

.

Similarly at the output node, c

out

includes parasitic

capacitances and intended integrating capacitor C

i2

.

The state-space representation of the filter is given

by (4) and (5).

x (t) = Ax(t) + Bv

in

(t) (4)

y(t) = [0 1] x(t ) (5)

where, x(t) = [v

x

v

out

]

T

(6)

The state matrix A and the input matrix B of filter are

written as follows.

The model is coded in Matlab. The resistance and

transconductance values are taken from DC operating

point analysis of the transconductor.

The filter is design centered using the approach

proposed in [2]. First, the response is obtained for

transistor level filter by simulating the filter with

integrating capacitors C

i1

and C

i2

computed using (2)

and (3). This response is then space- mapped to state-

space model, where the model is tuned with C

i1

and

C

i2

as variables to get a response that matches

closely with that of ideal. The optimized values C

i1

and C

i2

are used in the transistor level filter. If the

model is accurate, the the actual filter response will

match with that of the model and ideal as well. In

Fig.6 the response of the state-space model of the

filter is compared with that of transistor level filter.

The deviation in the response is an indication that

the model is not accurate. This may be attributed

to the additional parasitic poles and zeros formed by

inter node capacitance in the transconductor and

other secondary effects like sub-threshold effect. For

better accuracy of modeling, the inter node

capacitances and secondary effects have to be taken

into account. For better accuracy every

transconductor in the filer has to be modeled

accurately. i.e. all the intermediate nodes and

parasitics have to be taken into account. For the

transconductor designed in this paper, it has an

intermediate node formed at the common-drain point

of M

1

and M

3

(refer Fig. 3). Therefore, considering

the intermediate node, the small signal model of the

transconductor can be written as in Fig.7.

The Cochlea filter used in this paper uses three

transconductors and resulting in 6 state variables

for the entire filter, while an ideal Cochlea filter

has two integrating nodes (2 state variables). While

modeling the filter, state-space matrices for the

entire filter needs to be written carefully by selecting

the state variable nodes. Analysis of such a complex

circuit on paper is prone to error.

Two demerits are observed in modeling the filter

using state space technique, with respect to small-

signal model of the transconductor.

Due to parasitic capacitances the actual order

of the state space matrix will be more than

that of the ideal situation (i.e without

parasitics). As the order increases, writing

state-space model will require too much

of designers attention and time, which may

lead to error in modeling.

For low voltage supply, for example 0.5 V,

the transistors in the Cochlea filter

designed in this paper operate in sub-

Figure 6 Frequency response of State space model

and transistor level filter after design centering as

proposed in [2]

Figure 5. Equivalent circuit of the Cochlea filter

considering the finite input and output impedance

of the transconductor

I nternational J ournal of Advanced Computer Research (I SSN (print): 2249-7277 I SSN (online): 2277-7970)

Volume-2 Number-4 I ssue-6 December-2012

160

threshold region. Therefore in reality when

modeled it is mandatory to consider sub-

threshold effects for better accuracy. In state-

space technique the filter is modeled using the

small-signal equivalent circuit of the filter. It

is necessary to model the transistors in the

filter circuit by taking sub-threshold region of

operation into account. If sub-threshold

effects are need to be considered, for example

secondary effects such as hot carrier effect,

the model becomes more complicated.

For the Cochlea filter architecture considered in this

paper and for similar architectures, there is need for a

method to model the filter as accurate as possible at

the same time keeping it simple for designers. A

close look at the architecture of the filter reveals that,

it can be considered as cascade of several two-port

networks. It is well known fact that two-port

transmission line (ABCD) parameter representation is

the best suited two- port network model to represent

cascaded two-port networks. It is worth exploring the

usefulness of transmission line parameter modeling

for the filter as an alternative to state- space model.

B. ABCD-parameter approach based model

A close look at the Cochlea filter shown in Fig.2 can

be thought of as a cascade of four two-port networks

as shown in Fig.8. The individual two-port networks

are named as Sub block 1 - Sub block 4 in the figure.

When ABCD-parameters are used to represent two-

port networks, the ABCD model of the cascaded

network can be easily obtained by simply multiplying

ABCD matrices of individual blocks. i.e. if Ai, Bi,

Ci and Di are the ABCD parameters of i

th

Sub-block

in Fig.8, the filter can be represented using ABCD-

parameters as in (7).

The sub blocks 2 and 4 represent the capacitors

and the ABCD-parameter

representation of these blocks is simple and directly

available as given in (8)

The matrix elements for the sub block 1 and sub

block 3 are ratios of either voltage/current to

current/voltage with port 2 open circuit or short

circuit, small signal wise. With the help of cadence

tool these ratios as function of s are found. This

is intern done by finding the poles and zeros of

A(s), B(s), C (s) and D(s) by appropriately open

circuiting or short circuiting port 2 (small-signal

wise). Once the poles and zeros are calculated one

can discard the higher order poles and zeros whose

effect falls out of frequency range of interest, thus

reducing the computation complexity

Using above individual ABCD matrix elements, the

ABCD matrix of entire filter is computed as below.

The transfer function for the filter is V

out

(s)/V

in

(s) for

I

out

(s)=0

This implies

Figure 8.Cascaded two-port network

representation of Cochlea filter

Figure 7. Small-signal equivalent circuit of the

bulk-

driven transconductor with parasitic nodes

I nternational J ournal of Advanced Computer Research (I SSN (print): 2249-7277 I SSN (online): 2277-7970)

Volume-2 Number-4 I ssue-6 December-2012

161

Where

Using Matlab the expression (10) of A

T

can be

evaluated. The computation of matrix elements C

1

and D

1

are not necessary as they are not part of A

T

expression. We are interested in voltage gain of the

filter, therefore the computations of the remaining

matrix elements B

T

, C

T

and D

T

are not required. As

compared to state-space method this method avoids

the time spent with paper and pen in drawing and

analyzing the small-signal equivalent circuit. It is

found to be more accurate compared to the former

method. With the use of CAD, the complexity

involved in the modeling the filter with ABCD-

parameter approach is found to be less, even with

increase in the order of the filter. The frequency

response obtained from the ABCD-parameter based

model the filter and transistor level filter are shown in

Fig.9. It can be inferred from Fig.9 that, the model

response has one-to-one mapping with transistor

level filter response for the entire range of frequency.

Thus it is proved that the ABCD-parameter based

model of the filter is accurate than the simple state-

space model used in [2].

5. Results and discussions

Two models of the filter are obtained, one using

state- space model approach and another using

ABCD-parameter based approach and are used for

design centering of the filter. Responses of the both

models are obtained independently by tuning

integrating capacitors C

i1

and C

i2

, to get response

close to the ideal. So obtained optimized set of

integrating capacitors are used in transistor level

circuits. The response is plotted along with ideal

response in Fig.10. From the inset in the Fig.10 it can

be seen that the proposed two- port model based

approach of design centering gives better accuracy

than the state-space based approach. The small

deviation is due to the fact that the whole process of

design centering attempts to match the response of a

higher order filter (due to parasitics) to that of a

second order filter. Fig.11 shows percentage error of

the responses with respect to ideal. For the filter

design centering using two-port parameter based

approach the maximum error from ideal is found to

be 22 % while for that obtained using state-space

approach is 33 %.

Figure 11. Percentage error with respect to ideal filter for

Transistor level filter tuned with ABCD parameter model

and state-space model

Figure 10. Magnitude response of Transistor level

filter tuned with ABCD model, state-space and

Ideal filter

Figure 9. Magnitude response of ABCD

model and Transistor level filter

I nternational J ournal of Advanced Computer Research (I SSN (print): 2249-7277 I SSN (online): 2277-7970)

Volume-2 Number-4 I ssue-6 December-2012

162

6. Conclusion

In this paper a two-port based modeming is

proposed for design centering continuous time filter

as an alternate to classical state-space model based

approach. Both the proposed and classical method

are used to design center 2

nd

order Butterworth low

pass Cochlea filter designed in 180 nm technology

for a bandwidth of 1 MHz to operate at 0.5 V. The

outcome are compared and is found that two- port

based approach using ABCD-parameter based model,

models the filter accurately compared to simple state-

space based approach. It is also found that the

proposed method gives better accuracy in terms of

the matching of the filter response with ideal when

compared to state-space model based approach.

However the two-port based approach may not be

applicable to all classes of filter especially where

it is not possible to split the filter as cascade of two-

port networks.

References

[1] H. Graeb, Analog Design Centering and Sizing

Springer Verlag, 2007.

[2] T. Laxminidhi and S. Pavan, Efficient Design

Centering of Figh-Frequency Integrated Continuous-Time

Filters, IEEE Transactions on Circuits and Systems I:

Regular Papers,, vol. 54, no. 7, pp. 14811488, 2007.

[3] I. Grech, J. Micallef, G. Azzopardi, and C. Debono, A

0.9 V Wide-Input-Range Bulk-Input CMOS OTA for Gm-

C Filters, Proceedings of the 10

th

IEEE International

Conference on Electronics, Circuits and Systems, ICECS

2003, vol. 2, 2003, pp. 818821.

[4] C. Mead, Scaling of MOS Technology to

Submicrometer Feature Sizes, The Journal of VLSI Signal

Processing, vol. 8, no. 1, pp. 925, 1994.

[5] S. Thompson, MOS scaling: Transistor Challenges for

the 21

st

Century. MIT Microsystems Technology

Laboratories, 1998.

[6] A. Elwakil, Motivating Two-Port Network Analysis

Through Elementary and Advanced Examples,

International Journal of Electrical Engineering Education,

vol. 47, no. 4, pp. 404415, 2010.

[7] J. Choma and W. Chen, Feedback Networks:

Theory and Circuit Applications. World Scientific

Pub. Co. Inc., 2007.

[8] V. Harishchandra and T. Laxminidhi, A 0.5 V, 20 W

pseudo differential 500 kHz Gm-C low pass filter in 0.18

m CMOS technology, Proceedings of International

Conference on Devices, Circuits and Systems (ICDCS).

IEEE, 2012, pp. 7680.

Vasantha M.H. was born in Udupi, South India, in 1977.

Received B.Tech degree in Electrical and Electronics

Engineering from NMAM Institute of

Technology, Nitte, India, in 1998 and

M.Tech degree in Microelectronics and

VLSI design from the Indian Institute of

Technology Madras (IITM), Chennai,

India in 2003. He is currently pursuing

his Ph.D. in the Department of

Electronics and Communication

Engineering, National Institute of

Technology Karnataka (NITK), Surathkal, India.

Tonse Laxminidhi was born in Udupi, South India, in 1975.

He received the B.Tech degree in Electrical and

Electronics Engineering from NMAM Institute of

Technology, Nitte, India, in 1996. In 1998 he received the

M.Tech degree in Industrial Electronics from the National

Institute of Technology-Karnataka

(NITK), Surathkal, India. He obtained

his Ph.D. degree from the Department

of Electrical Engineering, Indian

Institute of Technology, Madras. His

research interests include analog and

mixed mode integrated circuits and

power management circuits. He is

faculty the Department of E&C

Engineering, NITK Surathkal since 1998 and currently

holding the position of Associate Professor.

Authors Photo

S-ar putea să vă placă și

- AnalogCircuitsITO13 PDFDocument128 paginiAnalogCircuitsITO13 PDFmouneshsk83% (6)

- Beginner's Guide To Digital PaintingDocument87 paginiBeginner's Guide To Digital PaintingBrittney Mac GregorÎncă nu există evaluări

- Brochure of Luxoft Automotive Software by Luxoft Software DevelopmentDocument4 paginiBrochure of Luxoft Automotive Software by Luxoft Software DevelopmentluxoftÎncă nu există evaluări

- Design of An ADC Using High Precision Comparator With Time Domain Offset CancellationDocument4 paginiDesign of An ADC Using High Precision Comparator With Time Domain Offset CancellationijtetjournalÎncă nu există evaluări

- Ena Doc 012-2006 PDFDocument15 paginiEna Doc 012-2006 PDFM.Ubaid Ullah Khalid100% (1)

- Simplified Method For Short Circuit CalculationsDocument4 paginiSimplified Method For Short Circuit Calculationshaiob100% (1)

- 190 00837 01 - 02Document36 pagini190 00837 01 - 02Haroon Javed QureshiÎncă nu există evaluări

- Signal Integrity: From High-Speed to Radiofrequency ApplicationsDe la EverandSignal Integrity: From High-Speed to Radiofrequency ApplicationsÎncă nu există evaluări

- Lightning Model For HVDC Transmission Lines: M. You, B. H. Zhang, L. Y. Cheng, Z. Q. Bo, A. KlimekDocument5 paginiLightning Model For HVDC Transmission Lines: M. You, B. H. Zhang, L. Y. Cheng, Z. Q. Bo, A. Klimekqais652002Încă nu există evaluări

- Microwave Treatment in Oil Refining PDFDocument8 paginiMicrowave Treatment in Oil Refining PDFRonikaGoswamiÎncă nu există evaluări

- Minimization Leakage Current of Full Adder Using Deep Sub-Micron CMOS TechniqueDocument7 paginiMinimization Leakage Current of Full Adder Using Deep Sub-Micron CMOS TechniqueInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Realizable Reduction For RC Interconnect Circuits: Corporation, 11400 Burnet TXDocument4 paginiRealizable Reduction For RC Interconnect Circuits: Corporation, 11400 Burnet TXJackyÎncă nu există evaluări

- Simulink Behavioral Modeling of A 10-Bit Pipelined ADCDocument9 paginiSimulink Behavioral Modeling of A 10-Bit Pipelined ADCbhasin_hemantÎncă nu există evaluări

- Low Power-Area Designs of 1bit Full Adder in Cadence Virtuoso PlatformDocument10 paginiLow Power-Area Designs of 1bit Full Adder in Cadence Virtuoso PlatformAnonymous e4UpOQEPÎncă nu există evaluări

- Optimising A D Flip Flop Through Delay and Power Estimation Using An RC Model and Transistor SizingDocument7 paginiOptimising A D Flip Flop Through Delay and Power Estimation Using An RC Model and Transistor SizingSavio SÎncă nu există evaluări

- Geometric Programming Based Power-Delay Optimization Using Transistor-Sizing For Submicron and Deep Submicron CMOS InverterDocument4 paginiGeometric Programming Based Power-Delay Optimization Using Transistor-Sizing For Submicron and Deep Submicron CMOS Invertersuchi87Încă nu există evaluări

- PHD Proposal LUDocument34 paginiPHD Proposal LUTho Mai DucÎncă nu există evaluări

- Iosr Journal c0704011523Document9 paginiIosr Journal c0704011523scsvmvsivakumarÎncă nu există evaluări

- A New Approach To Complex Bandpass Sigma Delta Modulator Design For GPS/Galileo ReceiverDocument7 paginiA New Approach To Complex Bandpass Sigma Delta Modulator Design For GPS/Galileo ReceiverƋniïiƨ TƎinÎncă nu există evaluări

- D 119Document35 paginiD 119Mohammad Ayatullah MaktoomÎncă nu există evaluări

- Interr ConDocument4 paginiInterr Conjubincb2Încă nu există evaluări

- Realizable RLCK Circuit CrunchingDocument6 paginiRealizable RLCK Circuit CrunchingHogo GohÎncă nu există evaluări

- FORTRAN Based ApproachDocument22 paginiFORTRAN Based ApproachGS EKTAÎncă nu există evaluări

- Cmos Fuladers (Pass Transistors) PDFDocument6 paginiCmos Fuladers (Pass Transistors) PDFswathiÎncă nu există evaluări

- Op Amp PaperDocument6 paginiOp Amp PaperSrinivasu IrlapatiÎncă nu există evaluări

- Power Constrained Design Optimization of Analog Circuits Based On Physical Gm/i CharacteristicsDocument7 paginiPower Constrained Design Optimization of Analog Circuits Based On Physical Gm/i CharacteristicsNanda KumarÎncă nu există evaluări

- A 1.8Ghz Cmos: Low-Power Truly-Modular Programmable Divider in Standard TechnologyDocument4 paginiA 1.8Ghz Cmos: Low-Power Truly-Modular Programmable Divider in Standard TechnologyMuhammad_Swilam_2010Încă nu există evaluări

- A Novel Method For Analysis of Power Consumption in VLSI Global InterconnectsDocument12 paginiA Novel Method For Analysis of Power Consumption in VLSI Global InterconnectsPranay KumarÎncă nu există evaluări

- Cmos Comparator ThesisDocument5 paginiCmos Comparator Thesisannemarieolathe100% (1)

- A High-Speed High-Resolution Latch Comparator For Pipeline Analog-to-Digital ConvertersDocument4 paginiA High-Speed High-Resolution Latch Comparator For Pipeline Analog-to-Digital ConvertersJessyÎncă nu există evaluări

- Speed-Power-Accuracy TradeoffDocument8 paginiSpeed-Power-Accuracy TradeoffbackspaceTABÎncă nu există evaluări

- Pipeline Adc Thesis PDFDocument7 paginiPipeline Adc Thesis PDFlauratorrestucson100% (2)

- Design and Analysis of Double Tail Comparator Using Adiabatic LogicDocument7 paginiDesign and Analysis of Double Tail Comparator Using Adiabatic LogicIJSTEÎncă nu există evaluări

- Efficient Carry Select Adder using 0.12μm Technology for Low Power ApplicationsDocument4 paginiEfficient Carry Select Adder using 0.12μm Technology for Low Power ApplicationsUmamahesh MavuluriÎncă nu există evaluări

- A 10-Gb/s CMOS Clock and Data Recovery Circuit With A Half-Rate Linear Phase DetectorDocument8 paginiA 10-Gb/s CMOS Clock and Data Recovery Circuit With A Half-Rate Linear Phase DetectorMahima ArrawatiaÎncă nu există evaluări

- Miniaturized Six-Port Receiver For 60 GHZ Communication ENDocument5 paginiMiniaturized Six-Port Receiver For 60 GHZ Communication ENWalter Santiago Campos ArandaÎncă nu există evaluări

- A High Performance 90 NM CMOS SAR ADC With HybridDocument8 paginiA High Performance 90 NM CMOS SAR ADC With HybridSounakDuttaÎncă nu există evaluări

- Low Power Full AdderDocument6 paginiLow Power Full Adderdurairajmary100% (1)

- Quasi-Floating Gate Based High Precision Current Mirror: D. Rajesh, Dr. N. Raj, Dr. P. John PaulDocument12 paginiQuasi-Floating Gate Based High Precision Current Mirror: D. Rajesh, Dr. N. Raj, Dr. P. John PaulPeter HeinÎncă nu există evaluări

- Optimum Stacked Layout For Analog Cmos IcsDocument4 paginiOptimum Stacked Layout For Analog Cmos IcsHow HwanÎncă nu există evaluări

- Power Constrained Design Optimization of Analog Circuits Based On Physical Gm/i CharacteristicsDocument7 paginiPower Constrained Design Optimization of Analog Circuits Based On Physical Gm/i CharacteristicsAn HoaÎncă nu există evaluări

- Time Interleaved AdcsDocument8 paginiTime Interleaved Adcsmarwen_zÎncă nu există evaluări

- A Review of 0.18-m Full Adder Performances For Tree Structured Arithmetic CircuitsDocument10 paginiA Review of 0.18-m Full Adder Performances For Tree Structured Arithmetic CircuitsChandan KumarÎncă nu există evaluări

- A Novel Charge Recycling Design Scheme Based On Adiabatic Charge PumpDocument13 paginiA Novel Charge Recycling Design Scheme Based On Adiabatic Charge PumpSudhakar SpartanÎncă nu există evaluări

- Design of Efficient N Bit Shift Register Using Optimized D Flip Flop in Quantum Dot Cellular Automata TechnologyDocument10 paginiDesign of Efficient N Bit Shift Register Using Optimized D Flip Flop in Quantum Dot Cellular Automata TechnologyMORIS CUBE TECH AND MORE mmmÎncă nu există evaluări

- A 1.8V 12-Bit 230-MS/s Pipeline ADC in 0.18 M CMOS TechnologyDocument4 paginiA 1.8V 12-Bit 230-MS/s Pipeline ADC in 0.18 M CMOS Technologyfaithfully_fatihÎncă nu există evaluări

- Gm/idDocument10 paginiGm/idAmith NayakÎncă nu există evaluări

- Low Power CAD: Trends and ChallengesDocument24 paginiLow Power CAD: Trends and Challengesjubincb2Încă nu există evaluări

- Research Article: 2.4 GHZ Cmos Power Amplifier With Mode-Locking Structure To Enhance GainDocument5 paginiResearch Article: 2.4 GHZ Cmos Power Amplifier With Mode-Locking Structure To Enhance GainRAJAMOHANÎncă nu există evaluări

- A Mosfet-Only Dac For A General Array Configured Device: E. Montane, G. Hornero, G. Chapinal, J. SamitierDocument5 paginiA Mosfet-Only Dac For A General Array Configured Device: E. Montane, G. Hornero, G. Chapinal, J. SamitierMiguel BrunoÎncă nu există evaluări

- PSCAD EMTDC, FuzzyControl, HVDC Transmission, VoltageDependentCurrentOrderLimit VDCOLDocument9 paginiPSCAD EMTDC, FuzzyControl, HVDC Transmission, VoltageDependentCurrentOrderLimit VDCOLKurniawan Indra LeksanaÎncă nu există evaluări

- AbstractDocument4 paginiAbstractKurushNishanth100% (1)

- Analysis of Pre-Emphasis Techniques For Channels With Higher-Order Transfer FunctionDocument12 paginiAnalysis of Pre-Emphasis Techniques For Channels With Higher-Order Transfer FunctionPraveen KumarÎncă nu există evaluări

- CMOS Full Adder Circuit TopologiesDocument9 paginiCMOS Full Adder Circuit TopologiesAamodh KuthethurÎncă nu există evaluări

- Dmatm: Dual Modified Adaptive Technique Based MultiplierDocument6 paginiDmatm: Dual Modified Adaptive Technique Based MultiplierTJPRC PublicationsÎncă nu există evaluări

- Design of High Performance Dynamic CMOS Circuits in Deep Submicron TechnologyDocument15 paginiDesign of High Performance Dynamic CMOS Circuits in Deep Submicron TechnologyEeshwar Ram JÎncă nu există evaluări

- Low Power Techniques For VLSI DesignDocument6 paginiLow Power Techniques For VLSI DesignjainatinÎncă nu există evaluări

- AnalogDocument8 paginiAnalogAhmed F RahimÎncă nu există evaluări

- JurnaaalllllDocument18 paginiJurnaaalllllANNURUL ATIYATUN TRIMULYA 1Încă nu există evaluări

- Journal Pre-Proof: Microprocessors and MicrosystemsDocument19 paginiJournal Pre-Proof: Microprocessors and MicrosystemsGOBINATH KÎncă nu există evaluări

- A New Model Predictive Control Approach To DC-DC Converter Based On Combinatory OptimizationDocument8 paginiA New Model Predictive Control Approach To DC-DC Converter Based On Combinatory OptimizationChaudhry Fahad Ali FastNUÎncă nu există evaluări

- High-Performance D/A-Converters: Application to Digital TransceiversDe la EverandHigh-Performance D/A-Converters: Application to Digital TransceiversÎncă nu există evaluări

- Power Systems-On-Chip: Practical Aspects of DesignDe la EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardÎncă nu există evaluări

- Enabling Technologies for High Spectral-efficiency Coherent Optical Communication NetworksDe la EverandEnabling Technologies for High Spectral-efficiency Coherent Optical Communication NetworksÎncă nu există evaluări

- Advanced Control of AC / DC Power Networks: System of Systems Approach Based on Spatio-temporal ScalesDe la EverandAdvanced Control of AC / DC Power Networks: System of Systems Approach Based on Spatio-temporal ScalesÎncă nu există evaluări

- Company Profile - Shenzhen Tianshilihe Technology Co.,LtdDocument36 paginiCompany Profile - Shenzhen Tianshilihe Technology Co.,LtdCynthia PanÎncă nu există evaluări

- Sts3000es - Sony FM Stereo TunerDocument128 paginiSts3000es - Sony FM Stereo Tunerjzaw65Încă nu există evaluări

- Motorola JLX Line Extender PDFDocument2 paginiMotorola JLX Line Extender PDFJosé Luis Gualotuña P.Încă nu există evaluări

- BASIC Stamp Manual v2-0Document353 paginiBASIC Stamp Manual v2-0Rogers ArismendiÎncă nu există evaluări

- Vacuum Pump Project PresentationDocument5 paginiVacuum Pump Project PresentationAlexandru Robert DumbravăÎncă nu există evaluări

- Mempower Busduct - PG - EN - 6 - 2012 PDFDocument38 paginiMempower Busduct - PG - EN - 6 - 2012 PDFAbelRamadhanÎncă nu există evaluări

- Smart Cabin For Educational Complex: Prerana More, Vaishnavi Chaudhari & Guided By: Prof. Aarti PawarDocument4 paginiSmart Cabin For Educational Complex: Prerana More, Vaishnavi Chaudhari & Guided By: Prof. Aarti PawarPreranaÎncă nu există evaluări

- RFID Door LockDocument37 paginiRFID Door LockRika HarianyÎncă nu există evaluări

- Make A Ribbon ControllerDocument16 paginiMake A Ribbon ControllerVaclav MullerÎncă nu există evaluări

- JDS2900 Function Generator User ManualDocument17 paginiJDS2900 Function Generator User ManualVivi LazuliÎncă nu există evaluări

- 11th Computer Science Question Bank Volume 1 Tamil MediumDocument49 pagini11th Computer Science Question Bank Volume 1 Tamil MediumSathish Julius100% (1)

- Depapepe Canon 123Document24 paginiDepapepe Canon 123Ratna RubiÎncă nu există evaluări

- MKT053 Fa22-2300 MadrasDocument2 paginiMKT053 Fa22-2300 MadrasrawassatÎncă nu există evaluări

- Number System & Logic GatesDocument24 paginiNumber System & Logic GatesA B Shinde100% (7)

- East Halmahera Ferronickel Development Project (P3Fh Project)Document2 paginiEast Halmahera Ferronickel Development Project (P3Fh Project)nailulfalah17Încă nu există evaluări

- SLP ManualDocument48 paginiSLP ManualJuan Esteban Seguel100% (1)

- Function Generator: 0.002Hz To 2MhzDocument34 paginiFunction Generator: 0.002Hz To 2MhzsebastinÎncă nu există evaluări

- Thinking Robots and A New Type of Robot Assistant: Travelmate RoboticsDocument3 paginiThinking Robots and A New Type of Robot Assistant: Travelmate RoboticsPR.comÎncă nu există evaluări

- Cation ConductivityDocument8 paginiCation ConductivityJayanath Nuwan SameeraÎncă nu există evaluări

- Delta CP2000 M en 20120331Document490 paginiDelta CP2000 M en 20120331vkdanshulÎncă nu există evaluări

- Advanced Power Electronics Corp.: AP2761I-HDocument4 paginiAdvanced Power Electronics Corp.: AP2761I-HAbelito JesusÎncă nu există evaluări

- Thyristor - CaledonDocument4 paginiThyristor - CaledonIDA HAMIDAHÎncă nu există evaluări

- Micro MaxDocument15 paginiMicro MaxNishad NevgiÎncă nu există evaluări

- LynxosDocument4 paginiLynxosRonak DoshiÎncă nu există evaluări