Documente Academic

Documente Profesional

Documente Cultură

AP9212 Jan 2012

Încărcat de

mthillairaniDescriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

AP9212 Jan 2012

Încărcat de

mthillairaniDrepturi de autor:

Formate disponibile

www.vidyarthiplus.

com

www.vidyarthiplus.com Page 1

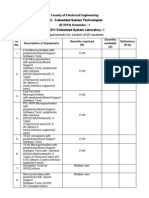

M.E. DEGREE EXAMINATION, JANUARY 2012.

First semester

AP 9212ADVANCED DIGITAL SYSTEM DESIGN

(Common to M.E. VLSI Design)

(Regulation 2009)

Time: Three hours Maximum: 100 marks

Answer ALL the Questions

PART A(10 2 = 20 marks)

1. Differentiate between state table and excitation table.

2. Draw ASM diagram for a serial adder.

3. What is a merger graph? Give example?

4. Differentiate between dynamic and static hazard.

5. State the conditions for faults to be equivalent and for faults to be redundant.

6. What is the significance of using BIST in Digital circuits?

7. Implement F= ABC+ABDC+AD using PLA.

8. What is Programmable Interconnect Point?

9. What is blocking and Non-blocking statement in VHDL?

10. What is a package?

PART B(5 16 = 80 marks)

11. (a) (i) Design a Moore type sequence detector to detect a serial input sequence of 1010.

www.vidyarthiplus.com

www.vidyarthiplus.com Page 2

(ii) Design a mod 5 counter. Use JK flip-Flops. (16)

Or

(b) The Message bits are encoded on a single line x, so as to synchronize with a clock. Bits are encoded

so that 3 or more consecutive 1s or 3 more 0s should never appear on the input line x. An error

indicating sequential circuit is to be designed to indicate an error by generating 1 on the output line

z, coinciding with the third of everysequence of three zeros or three ones. Draw the state diagram for

the logic circuit using D Flip-flops. (16)

12. (a) Design a circuit with primary inputs A and B to give an output Z equal to 1 when A becomes 1 if

B is already 1. Once Z=1 it will remain so until A goes to 0. Draw the Timing diagram, the state

diagram, primitive flow table for designing this circuit. (16)

Or

(b) Design a negative edge triggered T flip-Flop. The circuit has two inputs T and C and one output Q.

The output state is complemented if T=1 and the clock C changes from 1 to 0. Otherwise, under any

other input conditions the output Q remains unchanged.

13. (a) (i) What is a fault? Explain Boolean difference Method of Fault Diagnosis. (8)

(ii) Discuss Compact algorithm. (8)

Or

(b) (i) Discuss the test generation by DFT scheme. (8)

(ii) Explain the path sensitization method. (8)

14. (a)(i) Give the PAL realization of the given function (A, B, C, D, E, F) = m(0, 2, 6, 7, 8, 12, 13)

x(A, B, C, D, E, F) = m(0, 2, 6, 7, 8, 12, 13, 14)

y(A, B, C, D, E, F) = m( 2, 3, 8, 9, 10, 12, 13)

z(A, B, C, D, E, F) = m(1, 3, 6, 9,12, 4) (8)

(ii) Design a BCD to express 3 code convertor and implement using suitable PLA.

Or

(b) (i) Draw and explain the block diagram for XILINX FPGA. (8)

www.vidyarthiplus.com

www.vidyarthiplus.com Page 3

F1 (a, b, c) = (0, 1, 3, 4)

F2 (a, b, c) = (1, 2, 3, 4, 5). (8)

15. (a) (i) Explain Behavioral modeling with a suitable example. (8)

(ii) Design a 8 bit parallel Adder using VHDL. (8)

Or

(b) (i) Design an ALU using VHDL. (10)

(ii) Write a test bench to test a 4 bit counter. (6) (ii) Implement the following Boolean functions using

3x 4 x 2 PLA

S-ar putea să vă placă și

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- Pillcamerappt 150308080209 Conversion Gate01Document14 paginiPillcamerappt 150308080209 Conversion Gate01Dharmalingam MurugesanÎncă nu există evaluări

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Aeee Energy Efficiency Final PDFDocument120 paginiAeee Energy Efficiency Final PDFDharmalingam MurugesanÎncă nu există evaluări

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Prepared By: Debabrat Rath Branch:Ae&I REG NO:1101227119Document21 paginiPrepared By: Debabrat Rath Branch:Ae&I REG NO:1101227119Dharmalingam MurugesanÎncă nu există evaluări

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- Fundamentals of Eeg MeasurementDocument11 paginiFundamentals of Eeg Measurementfiziomar8100% (2)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (400)

- Ee6201 Circuit TheoryDocument2 paginiEe6201 Circuit TheoryDharmalingam MurugesanÎncă nu există evaluări

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- EC6013-Advanced Microprocessors and MicrocontrollersDocument8 paginiEC6013-Advanced Microprocessors and MicrocontrollerswelcometonceÎncă nu există evaluări

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Optical ComputingDocument31 paginiOptical ComputingDharmalingam MurugesanÎncă nu există evaluări

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Communications Systems: The Topics Within This Unit AreDocument56 paginiCommunications Systems: The Topics Within This Unit AreDharmalingam MurugesanÎncă nu există evaluări

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- (DSP - Audio) - Digital Audio Signal Processing - ZolzerDocument1 pagină(DSP - Audio) - Digital Audio Signal Processing - ZolzerDharmalingam MurugesanÎncă nu există evaluări

- Lecture02 TypesDocument18 paginiLecture02 TypesDharmalingam MurugesanÎncă nu există evaluări

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- Ieee Wireless Communication 2015 Matlab Mtech BeDocument11 paginiIeee Wireless Communication 2015 Matlab Mtech BeKommisetty MurthyrajuÎncă nu există evaluări

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (74)

- Inproceedings 2015 14989 2Document5 paginiInproceedings 2015 14989 2Dharmalingam MurugesanÎncă nu există evaluări

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- Photodetector ArraysDocument21 paginiPhotodetector ArraysDharmalingam MurugesanÎncă nu există evaluări

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- 14 06 2014 Vao GsDocument55 pagini14 06 2014 Vao GsDharmalingam MurugesanÎncă nu există evaluări

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- Communications Systems: The Topics Within This Unit AreDocument56 paginiCommunications Systems: The Topics Within This Unit AreDharmalingam MurugesanÎncă nu există evaluări

- Ant Based Intelligent Routing Protocol For MANETDocument6 paginiAnt Based Intelligent Routing Protocol For MANETDharmalingam MurugesanÎncă nu există evaluări

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- Embedded System TechtnologiesDocument3 paginiEmbedded System TechtnologiesDharmalingam MurugesanÎncă nu există evaluări

- AP9212 Jan 2012Document3 paginiAP9212 Jan 2012Dharmalingam MurugesanÎncă nu există evaluări

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)