Documente Academic

Documente Profesional

Documente Cultură

Multiplicador INFO

Încărcat de

Enzo Nicola Sandoval FioriDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Multiplicador INFO

Încărcat de

Enzo Nicola Sandoval FioriDrepturi de autor:

Formate disponibile

LABORATORIO DE MICROELETRONICA

INGENIERIA ELECTRNICA

LABORATORIO N5 SINTESIS CON VHDL DE SISTEMAS SECUENCIALES MODULARES

OSCAR LEONARDO SANDOVAL HIGUERA Cd.: 0160978

JEFFERSON JAIMES BERNATE Cd.: 0161057

I. INTRODUCCION

En la microelectrnica el uso de memorias es muy

utilizado dado que permite usar los recursos disponibles

de menea mucho ms eficiente pues con el uso de esta

los datos se ordenan mediante direcciones establecidos

y el acceso a ellos es mucho ms fcil. Los procesadores

y, valga la redundancia, las memorias de un computador

se construyen a base de ellas interconectndose

mediante buses que transportan desde datos hasta

direcciones y en el caso de tener mas de una memoria

BITS de seleccin que permiten ya sea leer o escribir

sobe una de ellas.

El siguiente informe presenta una sntesis en VHDL de

una memoria esttica de acceso aleatorio en al cual se

guardan datos de una multiplicacin y posteriormente

se accede a ellos mediante comando externos.

II. OBJETIVOS

Desarrollar un a nivel RTL y sintetizarlo

utilizando VHDL

Analizar el funcionamiento de un multiplicador

binario de 4 bits.

Adoptar un algoritmo apropiado para su

implementacin.

Expresar de manera personal los resultados

obtenidos.

III. MARCO TEORICO

Algoritmo de la multiplicacin binaria:

La multiplicacin binaria se puede hacer ya sea,

mediante sumas sucesivas sumando un el multiplicando

tantas veces me lo diga el multiplicador, por el

algoritmo de Booth, o por corrimiento de registros.

El mtodo usado en esta implementacin fue el de

corrimiento de registros debido a que las sumas

sucesivas requieren muchas operaciones y

comprobaciones, el algoritmo de Booth es ms til con

multiplicacin signada.

El mtodo de corrimiento de registros almacena los

datos, tanto el multiplicando como el multiplicador en

registros los cuales se van corriendo y sumando como

se hara en una multiplicacin algebraica normal.

11101111

111011

---------------------

11101111

11101111

00000000

11101111

11101111

11101111

-----------------------------

11011100010101

De esta manera se puede implementar fcilmente un

multiplicador corriendo el multiplicando y sumndolo o

sumando ceros dependiendo del valor de cada bit del

multiplicador.

Memoria SRAM de 2

N

*K

Una SRAM o memoria esttica de acceso aleatorio es un

tipo de memoria basada en semiconductores que es

capaza de mantener los datos (mientras este

alimentada) sin necesidad de circuito de refresco (no se

descargan). Sin embargo, si son memorias voltiles, s

decir que pierden la informacin si se les interrumpe la

alimentacin elctrica.

Figura 1. Esquema Elctrico de una memoria RAM.

LABORATORIO DE MICROELETRONICA

INGENIERIA ELECTRNICA

Estas memorias son de acceso aleatorio, lo que significa

que las posiciones en la memoria pueden ser escritas o

ledas en cualquier orden, independientemente de cul

fuera la ltima posicin de memoria leda o escrita.

Cada bit en una SRAM se almacena en cuatro

transistores, que forman un biestable. Este biestable

tendr dos estados, utilizados para almacenar un 0 o un

1. Se utilizan otros 2 transistores adicionales para

controlar el acceso al biestable durante las operaciones

de lectura y escritura.

IV. EQUIPO NECESARIO

Computador inter (R)

Pentium (R) 4 CPU 3.00 GHZ, 1 GB de RAM

Software de apoyo ISE FUNDATION de Xilinx

Simulador ISE Simulator

FPGA NEXYS 2

V. DESARROLLO DE LA PRACTICA

En la implementacin y diseo de la estructura se tiene

la siguiente Entidad general:

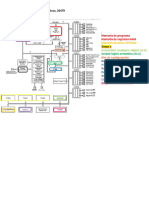

Figura 1. Entidad General de todo el sistema.

Esta Entidad Principal contiene internamente 8

componentes que permiten realizar las operaciones

requeridas segn los objetivos planteados, en la Figura

2 se puede observar la interconexin del sistema:

Figura 2. Componentes Internos del Sistema.

Figura 3. Jerarqua del Diseo Implementado.

De manera general, el sistema multiplica 2 nmeros de

4 bits que almacena en 2 registros de 8bits, guarda

estos datos en la RAM 2

3

*8 en las posiciones de

memoria 0 y 1. Luego se realiza la operacin de

multiplicacin, donde su resultado es guardado en otro

registro, y luego guardado en la posicin 2,.

La informacin se introduce por un teclado matricial de

4x5, el resultado se visualiza en notacin decimal en 4

dgitos del display siete segmentos del FPGA Nexys2.

Para la implementacin de este sistema se implemento

el modulo Dectepuls que permite generar un pulso

por tecla pulsada si importar cunto tiempo se

mantenga la tecla oprimida, de esta manera le facilita al

usuario la introduccin de los datos.

LABORATORIO DE MICROELETRONICA

INGENIERIA ELECTRNICA

Estructura Final

Dentro de estos 8 componentes existe uno vale la pena

resaltar es la EstructuraFinal la cual contiene la Macro-

operacin de la Multiplicacin y asignacin de cada uno

de los datos a la RAM.

Es importante tener en cuenta que para la

implementacin de este diseo se utilizaron dos

unidades de control, una Unidad Esclava y una Unidad

Maestra. La unidad Esclava Unidad_Control se

encarga de realizar la operacin de multiplicacin y

guardar en los registros A, B y C.

Enviando seales de control a la Unidad Maestra

Unidad_Master le informa sobre el avance de las

operaciones, y le indica en qu momento puede

guardar en la RAM, luego la unidad maestra enva

seales de control que le permiten a la unidad esclava

continuar con la operacin de multiplicacin, despus

de haber guardado los dos primeros datos en la RAM.

Cuando la operacin de multiplicacin es completada y

unidad esclava enva una seal de control para que se

guarde ese resultado en la RAM para dar por terminado

el proceso.

La operacin de guardar en la RAM de ejecuta

utilizando un multiplexor Multixrg que permite

seleccionar el dato de cada uno de los registros y

enviarlos a la posicin de memoria requerida.

Figura 4. Jerarqua del Modulo Completo del Sistema

Multiplicador y RAM.

Figura 5. EstructuraFinal y sus Componentes internos.

Multiplicador

ProductoFinal:

El multiplicador se diseo mediante corrimiento y suma

de registros en los cuales se guardan los datos de la

multiplicacin:

Figura 5. Jerarqua del Diseo del Multiplicador.

Figura 6. Mtodo y Pseudocdigo de la Multiplicacin.

LABORATORIO DE MICROELETRONICA

INGENIERIA ELECTRNICA

Como se observa en el pseudocdigo a medida que se

realizan las operaciones se realiza el corrimiento del

registro tantas veces como sea el largo del nmero.

La siguiente carta ASM muestra el algoritmo usado para

realizar la multiplicacin:

Figura 7. Carta ASM de la Multiplicacin.

Figura 8. Procesador de Datos implemento.

Figura 9. Unidad de Control de la Multiplicacin

(Unidad Esclava)

Unidad de Control Maestra

En la unidad de control maestra se envan las seales

que establecen los momentos de operacin de los

dems componentes externos a la multiplicacin, en

este caso a la memoria RAM. Esta controla la escritura

en la RAM permitiendo realizar la operacin de

multiplicacin sin ningn problema.

Los datos de los registro se guardan antes de que la

operacin de multiplicacin sea realizada, debido a que

si se hiciera esto luego los datos de los registro estaran

modificados por efecto de los corrimientos realizados

por la operacin de multiplicacin.

LABORATORIO DE MICROELETRONICA

INGENIERIA ELECTRNICA

Figura 10. Carta ASM de la Unidad de Control Maestra

S0=0; Ya=0; Enram=0; AD=0;

Master

=1?

Si

No

Enram=1; rw=1;

Espera

GuardaA

AD=1;

Enram=1; rw=1;

GuardaB

S0=1; enram=0;

Termina

Pregunta

Done=

1?

Si

No

AD=1;

Enram=1; rw=1;

GuardaC

Aux=1?

Si

No

Contina Siguiente Columna

Espera2

AD=0;

Ya=1; enram=1; rw=0;

Aux=1?

Si

No

enram=1; rw=0;

Aux=1?

Si

No

AD=1;

M1

M2

enram=1; rw=0;

Aux=1?

Si

No

AD=1;

M3

Retorna a

ESPERA

LABORATORIO DE MICROELETRONICA

INGENIERIA ELECTRNICA

S0 => En 1 Le Indica a la Unidad Esclava cuando puede

continuar con la operacin de multiplicacin.

Ya => En 1 Le indica a la Unidad Esclava cuando borre

registros y luego de haber guardado en memoria RAM.

Enram => Habilitador de Memoria RAM.

AD => En 1 incrementa la Posicin de la Memoria RAM

y en 0 inicializa a la posicin 000.

Master=> En 1 le indica a la Unidad Maestra cuando

los datos han sido guardados en los Registros.

Rw=> En 1 indica la Escritura de la RAM y en 0 su

lectura.

Done=> Le indica a la Unidad Maestra que la

multiplicacin ha terminado.

Aux => En 1 el usuario indica que quiere ver lo que sea

ha guardado en memoria RAM.

Componentes para el Usuario:

- BCDCONV

- CONTASEG

- DIVISORA

- MUXDIS

- DETECPULS

Estos componentes permiten visualizar en 1 display

siete segmentos de 4 digitos, los datos ingresados

por el usuario y a la vez el resultado en notacin

decimal.

- BCDCON convierte el dato en los dgitos de 4

bits para decodificar en los siete segmentos.

- CONTASEG decodifica los 4 dgitos de BCDCON

en datos para los displays.

- MUXDIS multiplex los 4 dgitos.

- DIVISORA es el divisor de frecuencia para los

displays.

- DECTEPULS le permite al usuario tener alguno

tecla pulsada sin que esto sea ledo como una

serie de datos para la operacin.

VI. CONCLUSIONES

El uso de memorias resulta de utilidad cuando

se requiere acceder a los datos en cualquier

momento del programa sin necesidad de re

calcular o reingresarlos.

La mejor forma de ingresar datos a una

memoria es a travs de registros los cuales me

almacenan los datos provisionalmente para

moverlos o modificarlos para luego escribirlos

en la posicin de memoria correspondiente.

El diseo a nivel RTL nos permite una

descripcin ms detallada de los algoritmos que

se implementan de manera que los diseos a

base de cata ASM.

En la implementacin de un sistema de esta

magnitud es necesario calcular en trminos de

ciclos de reloj cuanto demora cada

microperacion y macrooperacion para no

utilizar estados de mas en las unidades de

control.

Eventualmente en estos diseos de complejidad

elevada, pueden existir problemas en la

sintetizacin de los mdulos y es necesario,

tener cuidado para evitar conflictos con el

software.

En este tipo de operaciones la velocidad de

procesamiento se puede optimizar

considerablemente, pero es necesario tener en

cuenta que la informacin proveniente del

usuario se realiza a una velocidad cientos de

miles de millones ms lenta que la mxima

velocidad de procesamiento.

LABORATORIO DE MICROELETRONICA

INGENIERIA ELECTRNICA

RECOMENDACIONES

Cuando se tienen perifricos de entrada como

teclados matriciales, es preferible implementar

mdulos programados y cdigos que permitan

al usuario ingresar los datos de manera

cmoda.

Cuando se tienes versiones de Xilinx antiguas en

PCs de ltima generacin con sistemas

operativos nuevos, pueden existir problemas a

la hora de la implementacin, por eso es

recomendable si se trabaja con estas versiones

utilizar PCs con versiones del sistemas

operativos de la misma poca.

Cuando se realizan operaciones de este tipo es

recomendable implementar cada uno de los

mdulos utilizados en el sistema para evitar

problemas al final cuando se tenga el sistema

completo diseado.

VII. BIBLIOGRAFIA

1. http://es.wikipedia.org/wiki/Memoria_de_acce

so_aleatorio

2. - STEPHEN BROWN, ZVONKO VRANESIC.

Fundamentos de Logica Digital con diseo en

VHDL"

S-ar putea să vă placă și

- Multiplicador INFO PDFDocument7 paginiMultiplicador INFO PDFmcnc2Încă nu există evaluări

- Multiplicador INFO PDFDocument7 paginiMultiplicador INFO PDFJeison Dario Palacio MahechaÎncă nu există evaluări

- Reporte Contador 7 SegmentosDocument14 paginiReporte Contador 7 SegmentosSergio Medina MartinezÎncă nu există evaluări

- Informe Memoria 3x4Document10 paginiInforme Memoria 3x4Andresinho SievchenkoÎncă nu există evaluări

- Diagrama de Computadora y Funcionamiento-El Fenómeno CibernéticoDocument8 paginiDiagrama de Computadora y Funcionamiento-El Fenómeno CibernéticoAli SerranoÎncă nu există evaluări

- Componentes Del MicroprocesadorDocument25 paginiComponentes Del Microprocesadorel_cuate1883% (6)

- Resumen Arq de Comp US21Document261 paginiResumen Arq de Comp US21SergioÎncă nu există evaluări

- Unidad 2Document24 paginiUnidad 2Rogelio Anguiano SantosÎncă nu există evaluări

- Exposicion MicrocontroladoresDocument33 paginiExposicion MicrocontroladoresRosita Mtz SÎncă nu există evaluări

- Sanchez - Practica 6Document12 paginiSanchez - Practica 6Edison Sànchez50% (2)

- MANUAL Microcontroladores UTNCDocument20 paginiMANUAL Microcontroladores UTNCJuannita FrysÎncă nu există evaluări

- Microprocesador Z80Document8 paginiMicroprocesador Z80Alissa100% (1)

- Arquitectura Del Microprocesador z80Document9 paginiArquitectura Del Microprocesador z80Nilyan BertiÎncă nu există evaluări

- Un Microprocesador de 8 Bits Z80 PDFDocument85 paginiUn Microprocesador de 8 Bits Z80 PDFVictor Hugo Hernandez100% (1)

- Memorias de Un PLC y Su ClasificaciónDocument5 paginiMemorias de Un PLC y Su ClasificaciónJhory Ore100% (1)

- Arquitectura Von Neumann y HarvardDocument26 paginiArquitectura Von Neumann y HarvardUlivari Alexander GomezÎncă nu există evaluări

- Tarea 2Document4 paginiTarea 2Paulo Damian De La Cruz CardenasÎncă nu există evaluări

- Un Microprocesador de 8 Bits Z80Document85 paginiUn Microprocesador de 8 Bits Z80Sebastián SandovalÎncă nu există evaluări

- Guía Del Pic 16f84Document17 paginiGuía Del Pic 16f84b6dicÎncă nu există evaluări

- Arquitectura de ComputadorasDocument25 paginiArquitectura de ComputadorasMAURICIO JOSE TOLEDO SOLARESÎncă nu există evaluări

- Alu - 8085Document18 paginiAlu - 8085Walter David CunalataÎncă nu există evaluări

- El MicroprocesadorDocument11 paginiEl MicroprocesadorConsuelo MarinÎncă nu există evaluări

- El Microprocesador 8085Document11 paginiEl Microprocesador 8085neptuno97Încă nu există evaluări

- Tema 2Document21 paginiTema 2lucilafr.4739Încă nu există evaluări

- Unidad IDocument10 paginiUnidad IJose Manuel Godoy EscribarÎncă nu există evaluări

- Tema 2 y 3. Resumen de ArquitecturaDocument19 paginiTema 2 y 3. Resumen de Arquitecturaroko112Încă nu există evaluări

- Polanco Luis Miguel Tarea1.Capitulo1Document6 paginiPolanco Luis Miguel Tarea1.Capitulo1Luis miguel PolancoÎncă nu există evaluări

- La Familia MCS51 Modulo I.Document29 paginiLa Familia MCS51 Modulo I.Marco Antonio Manjarrez PalmaÎncă nu există evaluări

- TAREA 1pdfDocument11 paginiTAREA 1pdfjavierÎncă nu există evaluări

- Autoevaluacion 1 MicrocontroladoresDocument8 paginiAutoevaluacion 1 MicrocontroladoresAndres MartínezÎncă nu există evaluări

- Guia Circuito IntegradoDocument8 paginiGuia Circuito IntegradoRoyner GarcíaÎncă nu există evaluări

- Tutorial SimuprocDocument10 paginiTutorial SimuprocIrving Jesus Sanchez CamposÎncă nu există evaluări

- Act 1Document4 paginiAct 1geo.zumeÎncă nu există evaluări

- 2.1 - Estructura Del Microcontrolador ATmega328PDocument12 pagini2.1 - Estructura Del Microcontrolador ATmega328PArantxa NorzagarayÎncă nu există evaluări

- Desarrollo Prueba 2018Document7 paginiDesarrollo Prueba 2018Mauricio VegaÎncă nu există evaluări

- Memoria RamDocument7 paginiMemoria Ramalejandra trujilloÎncă nu există evaluări

- Capitulo2. Arquitectura Del ATmega32 (Español)Document18 paginiCapitulo2. Arquitectura Del ATmega32 (Español)Fortino100% (6)

- Sistema Minimo Micro 8088Document4 paginiSistema Minimo Micro 8088miguelon04Încă nu există evaluări

- Tema 3: Componentes, Estructura y Funcionamiento de La CPUDocument10 paginiTema 3: Componentes, Estructura y Funcionamiento de La CPUfelipeÎncă nu există evaluări

- Texto MicrocontroladoresDocument9 paginiTexto MicrocontroladoresRdy SeSaÎncă nu există evaluări

- Practica1 (SIS-522) RogerMiltonLlanosSotoDocument4 paginiPractica1 (SIS-522) RogerMiltonLlanosSotoR Milton LlanosÎncă nu există evaluări

- Microcontroladores Unidad 2Document13 paginiMicrocontroladores Unidad 2Fredd AlvarezÎncă nu există evaluări

- Regulacion de CargaDocument12 paginiRegulacion de CargaFrank Ayque C.Încă nu există evaluări

- Practica 4de ErasmoDocument8 paginiPractica 4de ErasmoSamantha GaliciaÎncă nu există evaluări

- Apuntes Libro AcDocument5 paginiApuntes Libro AcMilagros VegaÎncă nu există evaluări

- Practica2 - Sistemas Con Microprocesadores IDocument9 paginiPractica2 - Sistemas Con Microprocesadores ILeonardo Daniel VelaÎncă nu există evaluări

- Arquitectura Von NeumannDocument8 paginiArquitectura Von NeumannDaniel Medrano IzquierdoÎncă nu există evaluări

- Apunte - MicrocontroladoresDocument8 paginiApunte - MicrocontroladoresMaximiliano GómezÎncă nu există evaluări

- R Circuito de Disparo Con MicrocontroladoresDocument15 paginiR Circuito de Disparo Con MicrocontroladoresIsidro HernandezÎncă nu există evaluări

- Tema 1 CPUDocument7 paginiTema 1 CPUJak MartinÎncă nu există evaluări

- ObjetivosDocument6 paginiObjetivosManuel Rodrigo Villarreal CastroÎncă nu există evaluări

- Unidad Central de ProcesoDocument22 paginiUnidad Central de ProcesoTanPerÎncă nu există evaluări

- Fase1 E5Document8 paginiFase1 E5Luis EdynÎncă nu există evaluări

- Reporte 2Document6 paginiReporte 2Eduardo NÎncă nu există evaluări

- Informe RamDocument9 paginiInforme RamStalinCazaÎncă nu există evaluări

- UF0852 - Instalación y actualización de sistemas operativosDe la EverandUF0852 - Instalación y actualización de sistemas operativosEvaluare: 5 din 5 stele5/5 (1)

- Programación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeDe la EverandProgramación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeÎncă nu există evaluări

- Reparación de instalaciones automatizadas. ELEE0109De la EverandReparación de instalaciones automatizadas. ELEE0109Încă nu există evaluări

- Operaciones Auxiliares de Mantenimiento de Sistemas Microinformáticos (MF1208_1)De la EverandOperaciones Auxiliares de Mantenimiento de Sistemas Microinformáticos (MF1208_1)Încă nu există evaluări

- UF0853 - Explotación de las funcionalidades del sistema microinformáticoDe la EverandUF0853 - Explotación de las funcionalidades del sistema microinformáticoÎncă nu există evaluări

- Red HFCDocument2 paginiRed HFCEnzo Nicola Sandoval FioriÎncă nu există evaluări

- RoboticaDocument14 paginiRoboticaAlonso Almendras BÎncă nu există evaluări

- Filtros Activos TeoriaDocument53 paginiFiltros Activos TeoriaRomel DreideÎncă nu există evaluări

- Cs 1.1.1.1 29 Enzo SandovalDocument3 paginiCs 1.1.1.1 29 Enzo SandovalEnzo Nicola Sandoval FioriÎncă nu există evaluări

- Proyecto LedDocument43 paginiProyecto LedEnzo Nicola Sandoval FioriÎncă nu există evaluări

- C.O. Conclusion y BibliografiaDocument2 paginiC.O. Conclusion y BibliografiaEnzo Nicola Sandoval FioriÎncă nu există evaluări

- Doc-Tutorial-CDocument122 paginiDoc-Tutorial-CJezXenÎncă nu există evaluări

- Electrónica IndustrialDocument34 paginiElectrónica IndustrialEnzo Nicola Sandoval FioriÎncă nu există evaluări

- Enlaces Por SateliteDocument15 paginiEnlaces Por SateliteApotigma CardenalesÎncă nu există evaluări

- Planos de Las Piezas para Construir Un Brazo Robótico de 5 NivelesDocument3 paginiPlanos de Las Piezas para Construir Un Brazo Robótico de 5 NivelesEnzo Nicola Sandoval FioriÎncă nu există evaluări

- Processing Spa 1Document26 paginiProcessing Spa 1gasparresÎncă nu există evaluări

- C++ E S ExcepcionesDocument28 paginiC++ E S ExcepcionesEnzo Nicola Sandoval FioriÎncă nu există evaluări

- Informe PrevioDocument13 paginiInforme PrevioEnzo Nicola Sandoval FioriÎncă nu există evaluări

- Soberanía Segun Jean BodinDocument2 paginiSoberanía Segun Jean BodinEnzo Nicola Sandoval Fiori67% (3)

- Tema 12b Logica Programable VHDL 2012Document66 paginiTema 12b Logica Programable VHDL 2012Enzo Nicola Sandoval FioriÎncă nu există evaluări

- Manejo de MemoriasDocument19 paginiManejo de MemoriasAzu AguasÎncă nu există evaluări

- FerritasDocument2 paginiFerritasEnzo Nicola Sandoval FioriÎncă nu există evaluări

- Trabajos Microelectronica 2014-1Document4 paginiTrabajos Microelectronica 2014-1Enzo Nicola Sandoval FioriÎncă nu există evaluări

- TEMA 10 - Microprocesador de 8bitsDocument8 paginiTEMA 10 - Microprocesador de 8bitsEnzo Nicola Sandoval FioriÎncă nu există evaluări

- Sistemas de MicroondasDocument3 paginiSistemas de MicroondasEnzo Nicola Sandoval FioriÎncă nu există evaluări

- Instalacion Del Proteus 8 Sp0Document12 paginiInstalacion Del Proteus 8 Sp0Santiago RuizÎncă nu există evaluări

- Suma DecibeliosDocument16 paginiSuma DecibeliosSandoval CarlosÎncă nu există evaluări

- Memoria ROMDocument16 paginiMemoria ROMAndres Vladimir Nuñez TorresÎncă nu există evaluări

- ALUen VHDLDocument10 paginiALUen VHDLAlëx VazquezÎncă nu există evaluări

- Practica Calificada 06Document1 paginăPractica Calificada 06Enzo Nicola Sandoval FioriÎncă nu există evaluări

- Lineas de TransmisionDocument12 paginiLineas de TransmisionEnzo Nicola Sandoval FioriÎncă nu există evaluări

- Manual de Microcontroladores PICDocument68 paginiManual de Microcontroladores PICabraham-tellez-5555Încă nu există evaluări

- FourierDocument37 paginiFourierWilliam GuangasiÎncă nu există evaluări

- Microcontroladores PIC MicrochipDocument23 paginiMicrocontroladores PIC MicrochipAngel RodriguezÎncă nu există evaluări

- Inf Lab 2 FinalDocument12 paginiInf Lab 2 FinalcamiloÎncă nu există evaluări

- Actividad 4 Electronica de PotenciaDocument4 paginiActividad 4 Electronica de PotenciaAngell JuradoÎncă nu există evaluări

- TAREADocument6 paginiTAREAJeison CastilloÎncă nu există evaluări

- Manual de Reparación de PCDocument116 paginiManual de Reparación de PCLeonir CamargoÎncă nu există evaluări

- Introducción A Los Sistemas EmbebidosDocument15 paginiIntroducción A Los Sistemas EmbebidossebaescarzaÎncă nu există evaluări

- Coti 2013-16Document2 paginiCoti 2013-16Lesly Aldunate MontecinosÎncă nu există evaluări

- La ComputadoraDocument20 paginiLa ComputadoraMafer Revilla CenturionÎncă nu există evaluări

- MMXDocument6 paginiMMXarpkarpkÎncă nu există evaluări

- 2023 TP5 - Familias LogicasDocument4 pagini2023 TP5 - Familias LogicasLeo PereiraÎncă nu există evaluări

- Mis Primeros Programas Con PIC16F84A y PIC16F628A PDFDocument31 paginiMis Primeros Programas Con PIC16F84A y PIC16F628A PDFJhonny Wladimir Peñaloza CabelloÎncă nu există evaluări

- Tarjetas SDDocument18 paginiTarjetas SDIvan Salas GomezÎncă nu există evaluări

- Tipos de Memoria RomDocument10 paginiTipos de Memoria RomMaximo RamosÎncă nu există evaluări

- Laboratorio de ComputadorasDocument26 paginiLaboratorio de ComputadorasGabriel RodasÎncă nu există evaluări

- EnsamblajeDocument3 paginiEnsamblajefer1130Încă nu există evaluări

- Puertas de Entrada y SalidaDocument3 paginiPuertas de Entrada y Salidakapri1001100% (1)

- Trabajo de Word Terminado Andrea y PaulaDocument9 paginiTrabajo de Word Terminado Andrea y PaulaandreaypaulaÎncă nu există evaluări

- Actividad de Puntos Evaluables - Escenario 2 - ARQUITECTURA DEL COMPUTADORDocument7 paginiActividad de Puntos Evaluables - Escenario 2 - ARQUITECTURA DEL COMPUTADORRadasMELÎncă nu există evaluări

- Microprocesadores - Unidad de Aprendizaje 1 - Practica Calificada 1Document4 paginiMicroprocesadores - Unidad de Aprendizaje 1 - Practica Calificada 1Amilcar cruzado rodriguezÎncă nu există evaluări

- 1-Diagrama de Contactos (Ladder)Document9 pagini1-Diagrama de Contactos (Ladder)David BaronÎncă nu există evaluări

- Sesion 06 - Diagnostico y Reparacion de Los Componentes de La PCDocument31 paginiSesion 06 - Diagnostico y Reparacion de Los Componentes de La PCComputacionadetalle CADÎncă nu există evaluări

- TFG Blanca De-Angulo Ruiz-Moron 2017 PDFDocument47 paginiTFG Blanca De-Angulo Ruiz-Moron 2017 PDFJuan David GonzalezÎncă nu există evaluări

- Act 6 QUIZ 1Document5 paginiAct 6 QUIZ 1Luis Carlos Mogollón LozanoÎncă nu există evaluări

- Practica 5Document25 paginiPractica 5Mindy Ruiz TrejoÎncă nu există evaluări

- Informe Robo y MicroDocument17 paginiInforme Robo y MicrojefersonÎncă nu există evaluări

- Micro 12f1822 InstruccionesDocument9 paginiMicro 12f1822 InstruccionesKenzo YCÎncă nu există evaluări

- Previo 1 Sist. DigitalesDocument13 paginiPrevio 1 Sist. DigitalesValeria Andrea Nina ArrescurenagaÎncă nu există evaluări

- Familia AvrDocument4 paginiFamilia AvrPepe CamposÎncă nu există evaluări

- Definición de Las Computadoras y Sus ComponentesDocument2 paginiDefinición de Las Computadoras y Sus ComponentesmarcoÎncă nu există evaluări

- Investigación Máquinas de Estado-Ramírez Hernández Ahmed Alí 21010735Document14 paginiInvestigación Máquinas de Estado-Ramírez Hernández Ahmed Alí 21010735Ahmed RamírezÎncă nu există evaluări

- Numeracion y ViñetasDocument2 paginiNumeracion y ViñetasCarlos Bressley Soriano TupiñoÎncă nu există evaluări