Documente Academic

Documente Profesional

Documente Cultură

Cap 5,7

Încărcat de

krlossnTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Cap 5,7

Încărcat de

krlossnDrepturi de autor:

Formate disponibile

Universidad Nacional de Ingeniera. Sulca Carlos.

UNI-FIEE

1

I. TTULO

A. Generacin y Distribucin Del Reloj

i. Restricciones temporales asociadas al reloj.

ii. Estrategias de distribucin del reloj.

iii. Generacin del reloj.

iv. Sincronizacin del reloj. Uso de DPLLs

II. OBJETIVOS

A. Objetivos Generales

El objetivo de este captulo es tratar bsicamente dos temas, la distribucin del reloj, para mejorar un

parmetro importante llamado clock skew para circuitos de altas prestaciones, y el otro tema es la

generacin del reloj ya que de la estabilidad de la frecuencia del reloj depende que el sistema funcione de

forma fiable.

B. Objetivos Especficos

Antes de abordar los dos temas citados en los objetivos generales se aborda el tema de las restricciones

temporales asociadas al reloj que debe llevar todo sistema digital sncrono es estas restricciones se

consideran los retardos ms significativos como el tiempo de set-up y el tiempo de hold. Luego se toca otra

problemtica de los sistemas sncronos que es el parmetro de clock skew y cuyo objetivo especfico es la

solucin o reduccin de este parmetro.

Debido a que una de las causas de la introduccin del clock skew es la diferencia de longitudes de las

lneas de distribucin del reloj entre un punto de entrada del reloj y los biestables a sincronizar, para

solucionar esta problemtica se utilizan diferentes estrategias de distribucin del reloj como por ejemplo la

distribucin mediante estructura en espina o peine, la estructura en H. Otra alternativa de solucin son la

utilizacin de DPLLs dentro de cada circuito integrado.

Otro objetivo especfico es conocer cmo se genera la seal del reloj para los sistemas digitales, este

generador de reloj es un circuito que consiste en un amplificador con realimentacin positiva, y un filtro

muy selectivo en frecuencia. Las oscilaciones son por lo tanto el resultado de un fenmeno de resonancia.

GENERACIN Y DISTRIBUCIN

DEL RELOJ

Sulca Neira Carlos

Krloss2009@gmail.com

Universidad Nacional De Ingeniera

Universidad Nacional de Ingeniera. Sulca Carlos.

UNI-FIEE

2

III. ESTADO DEL ARTE

Uno de los temas de este captulo es el clock skew donde se analizaran los modelos existentes citados en

el captulo asignado en clase luego se realiza una bsqueda intensiva de modelos para la estimacin y

reduccin del clock skew que se encontr en algunos artculos de la IEEE que se adjuntaran en el informe

final y tambin informacin actual en otras pginas de internet.

El otro tema importante del subcaptulo es la generacin de reloj mediante osciladores que tambin se

busc las nuevas tecnologas que se emplean para tal objetivo.

IV. FUNDAMENTOS TERICOS

A. Restricciones temporales asociadas al reloj

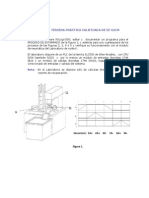

Todo sistema digital en el que intervenga una seal de sincronismo (reloj) tiene unas restricciones

temporales que deben ser cumplidas por las seales que en l participen. Para analizar estas restricciones,

se estudia el biestable sincronizado por flanco de subida que se muestra en la Fig.1. En dicha figura se

observa una configuracin master-slave: dos etapas biestables sincronizadas por nivel conectadas en

cascada, la primera activa por nivel bajo, y la segunda por nivel alto.

Fig. 1 Biestable D en configuracin Master-Slave

En el anlisis que se realiza se deben considerar los retardos ms significativos que intervienen en el

circuito. En primer lugar se encuentra el retardo desde la entrada de datos D de cada etapa biestable hasta

su salida Q, tq, (en la estructura mostrada en la Fig. 1. puede asimilarse al retardo del multiplexor y de los

dos inversores). En segundo lugar estn los retardos que tienen lugar entre la seal externa de reloj y las

seales de sincronismo que de hecho llegan a cada una de las partes biestables, t1 y t2, retardos debidos a

las constantes RC asociadas a cada una de las lneas de distribucin del reloj (que adems pueden ser

diferentes para cada parte biestable) ms el tiempo de respuesta del MUX2 a la seal de seleccin. Sobre el

cronograma de la Fig. 2, nos situamos en el segundo flanco de subida del reloj. En ese instante de tiempo la

seal de datos D vale 1, aunque un tiempo antes vala 0. La pregunta es, esta conmutacin 0 1 de

la seal D cun cerca puede realizarse del flanco de subida del reloj, sin que se vea afectada la lectura

correcta del 1 que pretendemos que sea ledo? Si por simplicidad consideramos en primera instancia unos

retardos t1 y t2 nulos, la respuesta es sencilla: tq. Si conmutamos la entrada D demasiado cerca del flanco

Universidad Nacional de Ingeniera. Sulca Carlos.

UNI-FIEE

3

de reloj 0 1, de forma que la salida de la primera parte biestable an no se haya estabilizado (y tarda

en hacerlo tq), la memorizacin que realice dicha primera parte podra ser incorrecta. Si consideramos unos

tiempos de retardo del reloj no nulos, ese intervalo mnimo de seguridad que hemos de dejar no es ms que

tq - t1. Este intervalo de tiempo se denomina tiempo de set-up.

Fig. 2 Cronograma de funcionamiento de un biestable D

La otra restriccin temporal es el tiempo mnimo que se ha de mantener la entrada activa despus del

flanco de reloj, y se denomina tiempo de persistencia o de hold, th. Para analizarlo utilizaremos tambin la

Fig. 2. Supongamos que en el mismo instante del flanco de subida del reloj conmutamos la seal de entrada

D. Dado que el reloj tarda t1 segundos en llegar a la entrada del multiplexor, la lectura ser errnea. La

seal de entrada ha de mantenerse validada por lo tanto durante un intervalo th = t1. Este anlisis y las

expresiones obtenidas son vlidos slo para la estructura biestable analizada, aunque perfectamente

extrapolable a otras estructuras.

Otra problemtica a tener en cuenta en sistemas sncronos es el clock skew, que no es ms que la posible

diferencia de fase o retardo que puede tener el reloj del sistema en la entrada de distintas puertas. Para

analizarlo utilizaremos la Fig. 3, donde se tienen dos biestables activos por flanco de subida conectados en

cascada y con un retardo de propagacin de los biestables de tq, y se modela la posible diferencia de

retardo en las seales de reloj mediante el retardo tD. Supongamos que dicho retardo tD es mayor que tq.

En tal caso, cuando llegue un flanco de subida al primer biestable y se realice la lectura del dato que en ese

momento se tenga a la entrada, ste se actualizar en Q1 tq segundos despus, pero entonces an no habr

llegado el flanco a la entrada del segundo biestable, llegar tD - tq segundos ms tarde. Y entonces el

segundo biestable leer el dato almacenado en Q1 y lo mostrar en Q2, producindose por lo tanto un

funcionamiento errneo. Sin necesidad de recurrir al caso tan extremo de tener tD > tq, slo con darse que

tq - tD < th, es fcil ver que se incumple el tiempo de persistencia, dndose tambin un funcionamiento

errneo. Y todo ello debido al efecto de tener diferentes retardos para los distintos caminos del reloj del

sistema, esto es, clock skew.

Fig. 3 Estudio del efecto del clock skew mediante dos biestables en cascada

Universidad Nacional de Ingeniera. Sulca Carlos.

UNI-FIEE

4

B. Estrategias de distribucin del reloj

Uno de los puntos clave en el diseo de circuitos lgicos de altas prestaciones es el sistema o estructura

de distribucin de la seal de sincronismo o reloj, y el parmetro ms importante a tener en cuenta es el

clock skew que dicha estructura introduce. En la Fig. 4. se observa una determinada estructura de

distribucin del reloj de un CI, y una de las causas de la introduccin de clock skew: la diferencia de

longitudes de las lneas de distribucin del reloj, entre el punto de entrada del reloj y la localizacin de los

biestables a sincronizar. Existen diferentes posibles opciones a la hora de distribuir la seal de reloj por un

CI. La primera y ms simple consiste sencillamente en realizar la colocacin sin tener en consideracin

especial el reloj, y realizar a continuacin el conexionado (routing) del mismo como si fuera una seal ms.

Esta opcin es la mejor en cuanto a rea requerida y a facilidad de realizacin automtica, pero la peor en

cuanto a clock skew se refiere, por lo que debe descartarse en circuitos rpidos.

Fig. 4 Posible distribucin del reloj en un CI

Otra opcin es la mostrada en la Fig. 5. Se denomina distribucin del reloj mediante estructura en espina

o en peine. La seal de reloj se inyecta por el centro del CI, y se reparte mediante lneas paralelas tal y

como indica la fi gura. Es una estructura regular y sencilla de implementar mediante herramientas CAD,

pero consume ms rea de la estrictamente necesaria y el clock skew que presenta puede ser importante. En

la Fig. 5. Se muestra cmo biestables situados en (1) y en (2) sufriran una diferencia de fase mxima.

sta suele ser la estructura utilizada en CI con estructuras regulares, como FPGAs o DSPs.

Universidad Nacional de Ingeniera. Sulca Carlos.

UNI-FIEE

5

Fig. 5 Distribucin de reloj mediante estructura en peine

Una forma de minimizar el clock skew es haciendo todas las lneas de distribucin del reloj de igual

longitud. Para ello se pueden utilizar estructuras que se repitan tantas veces como sea necesario para

realizar la distribucin del reloj y que aseguren la condicin mencionada, como por ejemplo la estructura en

H que se muestra en la Fig. 6. Puede observarse cmo manteniendo una estructura de distribucin en

forma de H se logra que la distancia entre el inicio de la distribucin del reloj (el punto central de la H

mayor) y los extremos sea constante.

Fig. 6 Distribucin de reloj mediante estructura en H

En la figura mencionada, por ejemplo, en caso de haber realizado la distribucin del reloj mediante una

distribucin espina, la diferencia de fase entre los puntos (1) y (2) hubiera sido considerable, no as en la

estructura de la Fig. 6. La distribucin en H se puede extender a tantos niveles como se quiera, al precio,

eso s, del rea que requiere una distribucin tan especfica. Lo normal es llegar hasta un cierto nmero de

niveles (en la fi gura hay slo dos haches anidadas) y, a partir de ese nivel en el que el clock-skew

remanente se considera tolerable, se realiza la distribucin del reloj de forma convencional. En la Fig. 6,

dentro de cada sector marcado como bloque, se tratara al reloj como una seal ms en cuanto a por dnde

trazar su distribucin (siempre a partir del centro), con lo que el skew mximo sera el de una semidiagonal

de un bloque.

Resumiendo, esta distribucin minimiza el clock skew, pero es de difcil realizacin de forma automtica y

tambin puede necesitar ms conexionado (rea) del estrictamente necesario. Adems del problema relativo

a por dnde se hace llegar el reloj a los biestables, en el tema de distribucin del reloj se debe tener en

cuenta que en CI grandes la capacidad total asociada al reloj (la asociada al conexionado del mismo ms la

asociada a las entradas de reloj de los biestables) puede ser muy elevada.

C. Generacin Del Reloj

El generador de reloj de un sistema digital es un bloque bsico para su buen funcionamiento, ya que de la

estabilidad de la frecuencia del reloj depende que el sistema funcione de forma fiable. De forma genrica,

un generador de reloj es un circuito que consiste en un amplificador con realimentacin positiva, y un filtro

muy selectivo en frecuencia. Las oscilaciones son por tanto el resultado de un fenmeno de resonancia. La

estabilidad en frecuencia de la oscilacin depende, por una parte, del factor de calidad del filtro resonante.

Por otra parte, variaciones en temperatura provocan variaciones en los valores de los componentes que

Universidad Nacional de Ingeniera. Sulca Carlos.

UNI-FIEE

6

forman el filtro, por lo que un segundo factor que influye en la estabilidad de la oscilacin es la

dependencia en temperatura de dichos componentes. Para realizar el filtro resonante se puede pensar en

utilizar componentes discretos (L, C, R). Sin embargo, el valor del factor de calidad Q que se obtiene de

este modo viene limitado por los inductores, y su valor mximo es de alrededor de 300, por lo cual no es

una opcin utilizada. Los osciladores de altas prestaciones se basan en un cristal piezoelctrico conectado

fuera del chip como elemento resonante. Un cristal piezoelctrico responde a una compresin mecnica con

una tensin entre sus extremos, y a una tensin con una compresin mecnica. Por tanto, al aplicar entre

sus extremos una tensin variable, se produce una vibracin, y las caractersticas mecnicas (dimensiones

del cristal, propiedades del material en cuestin) determinan una frecuencia de resonancia. Las ventajas de

esta alternativa son un valor de Q extremadamente alto (del orden de 105) y una buena estabilidad en

temperatura. El material normalmente utilizado como resonador es el cuarzo y los generadores de reloj

basados en materiales piezoelctricos se llaman osciladores de cristal u osciladores de cuarzo. Al

caracterizarse el cristal por una frecuencia de resonancia, se puede modelar como un circuito resonante

equivalente, mostrado en la Fig. 7. Cada cristal tiene unos parmetros equivalentes que corresponden a su

frecuencia de oscilacin y factor de calidad. Con estos parmetros elctricos equivalentes es posible

analizar el circuito oscilador de forma global y optimizar su comportamiento.

Fig. 7 Modelo elctrico de un cristal Piezoelctrico

De entre las diferentes configuraciones posibles de osciladores de cuarzo, una de las ms utilizadas es el

llamado oscilador de Pierce, cuyo esquema se muestra en la Fig. 8. Consiste en un inversor CMOS con una

resistencia de polarizacin que fi ja un punto de trabajo en continua para el cual la ganancia (relacin

salida-entrada) es mxima. Conectando entre los terminales del inversor un cristal de cuarzo, resultarn

oscilaciones de tensin a la frecuencia de resonancia determinada por el cristal. Las dimensiones de los

transistores NMOS

y PMOS y los valores de resistencia de realimentacin y condensadores externos determinan la amplitud de

oscilaciones, alrededor del punto de trabajo en continua (igual a la tensin de conmutacin del inversor,

VDD/2 si el inversor es simtrico). Para pasar estas oscilaciones a una seal de reloj til para sistemas

digitales es necesario conectar un buffer a la salida del oscilador, encargado de conformar la seal.

Universidad Nacional de Ingeniera. Sulca Carlos.

UNI-FIEE

7

Fig. 7 Oscilador de Pierce

i. Oscilador armnico o lineal

Genera una seal senoidal, se basa en un amplificador realimentado mediante un filtro tal como

se muestra en la figura 8.

Fig. 8 Esquema de un Oscilador armnico

Cuando el sistema se conecta a la alimentacin slo existe ruido, que es muestreado, filtrado y

aplicado a la entrada del amplificador, transcurrido cierto tiempo dispondremos a la salida de una

senoide de frecuencia nica. Debido a que idealmente estos dispositivos poseen una frecuencia de

resonancia, en la cual idealmente funcionan, se los suele conocer como resonadores.

Dentro de esta categora se puede distinguir diferentes tecnologas:

o Osciladores RC.

o Osciladores LC, donde el filtro es un circuito sintonizado (llamado circuito

tanque).

o Osciladores a cristal (tambin llamados cuarzos).

o SAW (Surface Acoustic Wave), permiten alcanzar frecuencias del GHz

Para la implementacin de los mismos existen diferentes topologas:

o Osciladores RC (de desplazamiento de fase, puente de Wien,).

o Osciladores LC (oscilador Hartley, oscilador Colpitts)

Universidad Nacional de Ingeniera. Sulca Carlos.

UNI-FIEE

8

o Osciladores a cristal (oscilador Colpitts)

ii. Oscilador de relajacin

Genera una seal no senoidal (cuadrada, triangular,...). Estn constituidos por un elemento

almacenador de energa (p.e. condensador) y un circuito no lineal (p.e. un Schmitt Trigger) que

peridicamente modifica la energa almacenada, provocando cambios abruptos en la seal de salida

generada.

Fig. 9 Multivibrador con opamp

Dentro de esta categora podemos distinguir diferentes topologas:

o Multivibradores: como el 555 que se explicar en esta prctica.

o Osciladores de anillo: en los que se basan circuitos como los VCO (Voltage

Controlled Oscillator)

iii. Especificaciones tpicas de las seales de reloj

Algunas de las especificaciones a la hora de decidir cul es el mejor generador de reloj para nuestra

aplicacin son las siguientes:

- Frecuencia nominal de funcionamiento.

- Orden de sobretono: nmero de mltiplos impares que se generan de la frecuencia fundamental.

- Potencia: es el consumo de energa del oscilador.

- Factor de calidad (Q): es una medida (aplicada slo a osciladores armnicos) de la eficiencia de la

seal generada. La mxima estabilidad de un cristal depende del valor de "Q". Cuanto ms

pequeo es el ancho de banda del oscilador mayor es su Q.

- Jitter: es la desviacin del tiempo de muestreo real respecto al nominal. En otras palabras se

puede definir como la variabilidad temporal de la frecuencia de una seal peridica.

- Tolerancia de la frecuencia: se refiere a la mxima desviacin permitida y se expresa en partes

por milln (PPM) para una temperatura especificada, usualmente 25C.

- Estabilidad de la frecuencia: se refiere a la mxima desviacin en PPM. La desviacin est

Universidad Nacional de Ingeniera. Sulca Carlos.

UNI-FIEE

9

tomada con referencia a la frecuencia medida a 25C. En las especificaciones suele darse respecto

a la temperatura y al tiempo/envejecimiento, distinguindose entre corto plazo (1 da) y largo

plazo (>1 ao)

iv. Oscilador RC

El ejemplo de la figura 9 es un oscilador RC con topologas de puente de Wien.

Fig. 9 Oscilador RC con topologa de puente wien

Este circuito RC tiene como principal caracterstica la de contar con un filtro paso de banda en el

circuito de alimentacin, formado por un filtro paso de alta y un filtro paso de baja. Este esquema se

puede observar con mayor claridad en la figura 4. Este filtro paso de banda (de segundo orden) permitir

hacer un ajuste fino de la frecuencia de salida, cuyo valor es igual a:

La principal aplicacin de estos circuitos es la de generar ondas de salida para bajas frecuencia. En

concreto, los circuitos RC son empleados para sistemas de audio (hasta KHz) debido a que necesitaran

capacidades muy pequeas para intentar subir la frecuencia de salida.

Fig. 10 Filtro paso de banda

v. Oscilador LC

El ejemplo de la figura 11 es un oscilador LC con topologa Colpitts. La frecuencia de resonancia

de estos circuitos viene dadas por:

Universidad Nacional de Ingeniera. Sulca Carlos.

UNI-FIEE

10

Los osciladores LC s pueden emplearse para frecuencias ms altas, en el rango de los MHz, siendo

una aplicacin tpica la de la banda de FM (88-108 MHz). Estos resonadores pueden encontrarse

como circuitos integrados para frecuencias fijas o variables. Algunos de los fabricantes tpicos de este

tipo de circuitos son Epson o Panasonic.

Fig. 11 Oscilador LC en topologa colpitts

vi. Osciladores de cristal

Existen otros tipos de osciladores que se utilizan para rangos de frecuencias mayores y cuya pureza

espectral es mayor. Estos osciladores estn basados en el empleo de un cristal. El cristal de cuarzo es

utilizado como componente de control de la frecuencia de circuitos osciladores convirtiendo las

vibraciones mecnicas en voltajes elctricos a una frecuencia especfica. Esto ocurre debido al efecto

"piezoelctrico". La piezo-electricidad es electricidad creada por una presin mecnica. En un material

piezoelctrico, al aplicar una presin mecnica sobre un eje, tendr como consecuencia la creacin de

una carga elctrica a lo largo de un eje ubicado en un ngulo recto respecto al de la aplicacin de la

presin mecnica.

Fig. 12 Cristales de reloj

Por las propiedades mecnicas, elctricas, y qumicas, el cuarzo es el material ms apropiado para

fabricar dispositivos con una frecuencia bien controlada, ya que sus caractersticas son prcticamente

constantes respecto al tiempo y la temperatura. De este modo, cuando se aplica una diferencia de

Universidad Nacional de Ingeniera. Sulca Carlos.

UNI-FIEE

11

tensin entre dos caras opuestas de este material se generar una frecuencia que vendr determinada,

junto con su factor de calidad, por las caractersticas del cristal, tales como su dimensin o la

orientacin de las superficies respecto a sus ejes.

Algunos valores tpicos de las especificaciones de los cristales comerciales son:

- Frecuencia de funcionamiento: cuando se incrementa la frecuencia solicitada, el espesor del

cuerpo del cristal disminuye y por supuesto existe un lmite en el proceso de fabricacin.

Alrededor de 30MHz, el espesor de la placa del cristal comienza a ser muy delgada.

- Tolerancia de la frecuencia: los valores tpicos estn entre 15 y 100 PPM.

- Estabilidad respecto a la temperatura y el paso del tiempo: sus valores tpicos oscilan entre 10 y

20PPM.

- Envejecimiento: su valor tpico suele estar entre los 3 y 7 aos. Suele venir determinado por

efectos tales como un exceso de potencia disipada, prdida de elasticidad o efectos trmicos.

- Potencia disipada por el cristal: siendo un valor tpico igual 100 W.

Algunas de las muchas aplicaciones de los cristales de cuarzo son las de uso diario tales como relojes,

microprocesadores o telfonos mviles. Tambin son usados para equipos de test y medidas tales como

generadores de seal u osciloscopios. Los cristales pueden ser construidos para su oscilacin en un

amplio rango de frecuencias, desde unos pocos KHz hasta varios cientos de MHz. Muchas aplicaciones

requieren una misma frecuencia determinada. Algunos ejemplos de bandas de inters donde se usan

osciladores basados en cristal son las de 12 MHz para USB, 23-25 MHz para GPS, 30,72 MHz para 3G,

106,5 MHz para transceivers de radio y 156.5 MHz para 10 Gigabit Ethernet. Algunos fabricantes tpicos

de cristales son Crystek o Murata.

vii. Circuitos generadores de reloj para alta frecuencia

Existen circuitos ms complejos son empleados para la generacin de seales de reloj ms puras y

que suelen estar basados en los anteriores. Algunos de ellos son los PLL (Phase Lock Loop) y los DDS

(Direct Digital Synthesis), todos ellos circuitos capaces de generar frecuencias programables. Uno de

los elementos en los que se basan los PLL, son los VCO nombrados anteriormente. Los parmetros ms

habituales de los VCO son los siguientes:

- Rango de frecuencias a la salida: pudindose alcanzar ms de 1 GHz.

- Rango de tensiones de control: con valores tpicos entre 1 y 16 V.

- Sensitividad de sintonizado: con valores tpicos entre 5 y 30 MHz/V.

Los PLL proporcionan salidas desde la fraccin de Hz hasta varios GHz. Una aplicacin tpica de los

PLL es la de su empleo como oscilador local para realizar la subida en frecuencia en los sistemas de

recepcin o la bajada en frecuencia en los sistemas de recepcin, por ejemplo, para aplicaciones

wireless. Por otra parte, algunas aplicaciones bsicas de los DDS incluyen las de generacin de reloj que

requieren una alta velocidad de sintonizado o un ajuste muy fino de frecuencia. Los fabricantes con

mejores prestaciones para este tipo de circuitos son National o Analog Devices.

S-ar putea să vă placă și

- Máxima Tensión de Contacto Admisible Por El Cuerpo Humano Según Normas IEC e IEEEDocument7 paginiMáxima Tensión de Contacto Admisible Por El Cuerpo Humano Según Normas IEC e IEEELuisa Fernanda RamirezÎncă nu există evaluări

- Resumen Cap 5 "Biografía de La Física" de Gamow - by Carlos J Flores SarachoDocument6 paginiResumen Cap 5 "Biografía de La Física" de Gamow - by Carlos J Flores SarachoCarlos Flores100% (2)

- Estabilización de SuelosDocument12 paginiEstabilización de SuelosYane Mora67% (3)

- Lab - Circuito de Resistores en Serie - ParaleloDocument6 paginiLab - Circuito de Resistores en Serie - ParaleloAndres A. Ortega MilordÎncă nu există evaluări

- Detecion de ObjetosDocument22 paginiDetecion de ObjetoskrlossnÎncă nu există evaluări

- TDT PerúDocument24 paginiTDT PerúkrlossnÎncă nu există evaluări

- Profibus PDFDocument11 paginiProfibus PDFjapmz1973Încă nu există evaluări

- Ley UniversitariaDocument60 paginiLey UniversitariaRider Bendezú100% (2)

- Gestion de Proyectos IntroducciónDocument17 paginiGestion de Proyectos IntroducciónkrlossnÎncă nu există evaluări

- IEC61850Document269 paginiIEC61850krlossnÎncă nu există evaluări

- Normas IP e IKDocument5 paginiNormas IP e IKKléber Chávez CifuentesÎncă nu există evaluări

- Ansi y DinDocument9 paginiAnsi y DinkrlossnÎncă nu există evaluări

- Informe Anual de Evaluación Del Proceso de Implementacion de La TDT en Peru 2013Document20 paginiInforme Anual de Evaluación Del Proceso de Implementacion de La TDT en Peru 2013moebiuszeroÎncă nu există evaluări

- PLCDocument5 paginiPLCkrlossnÎncă nu există evaluări

- RS485Document2 paginiRS485krlossnÎncă nu există evaluări

- 4ta PCDocument3 pagini4ta PCkrlossnÎncă nu există evaluări

- PROYECTODocument16 paginiPROYECTOkrlossnÎncă nu există evaluări

- Espacio de EstadosDocument28 paginiEspacio de EstadoskrlossnÎncă nu există evaluări

- MatlabDocument38 paginiMatlabDaniel PérezÎncă nu există evaluări

- PLCDocument4 paginiPLCkrlossnÎncă nu există evaluări

- GrammarDocument5 paginiGrammarkrlossnÎncă nu există evaluări

- DROGASDocument7 paginiDROGASkrlossnÎncă nu există evaluări

- CH 02 Antenna Parameters UNI 2011-2Document16 paginiCH 02 Antenna Parameters UNI 2011-2krlossnÎncă nu există evaluări

- Cotrol DicretoDocument12 paginiCotrol DicretokrlossnÎncă nu există evaluări

- Amino Acid OsDocument6 paginiAmino Acid OskrlossnÎncă nu există evaluări

- Teoria de TrigonometriaDocument8 paginiTeoria de TrigonometriaIngrid FloresÎncă nu există evaluări

- CH 01 Intro Antennas UNI 2011-2Document16 paginiCH 01 Intro Antennas UNI 2011-2krlossnÎncă nu există evaluări

- Microelectronica 1Document0 paginiMicroelectronica 1krlossnÎncă nu există evaluări

- Control de Motor EncoderDocument29 paginiControl de Motor Encodercymonso100% (15)

- Ampli Cadores MultietapaDocument12 paginiAmpli Cadores Multietapaalvin-jesus-coba-garcia-9437Încă nu există evaluări

- Tarea Domiciliaria Ee616mDocument1 paginăTarea Domiciliaria Ee616mkrlossnÎncă nu există evaluări

- Control OptimoDocument12 paginiControl OptimokrlossnÎncă nu există evaluări

- Paper IEEE TX en FrecuenciaDocument6 paginiPaper IEEE TX en FrecuenciapablodcbaÎncă nu există evaluări

- Lámpara de Prueba PARA TESTEAR CORTOCIRCUITODocument5 paginiLámpara de Prueba PARA TESTEAR CORTOCIRCUITOantonio de jesus reyes luzardoÎncă nu există evaluări

- Medidor de Tierra Tipo PinzaDocument5 paginiMedidor de Tierra Tipo Pinzafranco_3210_Încă nu există evaluări

- Universidad Central Del EcuadorDocument4 paginiUniversidad Central Del EcuadorKevin KmikzeÎncă nu există evaluări

- Retie Articulo 15 y 16Document40 paginiRetie Articulo 15 y 16Eduitar RodriguezÎncă nu există evaluări

- Memorias - Calculo - Casa de Mamatoco - V - 1 PDFDocument44 paginiMemorias - Calculo - Casa de Mamatoco - V - 1 PDFLeonardo Restrepo Herrera40% (5)

- Apuntes de Diseño de Estructuras de AceroDocument19 paginiApuntes de Diseño de Estructuras de AceroAdrian Orozco AtilanoÎncă nu există evaluări

- (Ebook) Pspice - 50 PDFDocument98 pagini(Ebook) Pspice - 50 PDFCaterine Feria RamirezÎncă nu există evaluări

- Detector de HumoDocument7 paginiDetector de HumoVilleda ErazoÎncă nu există evaluări

- Anexo A - Informe Tecnico Sondeo ElecticoDocument30 paginiAnexo A - Informe Tecnico Sondeo ElecticoJose Luis Rodriguez HernandezÎncă nu există evaluări

- Sensores de Equilibrio de FuerzasDocument18 paginiSensores de Equilibrio de FuerzasJulio Cesar CutipaÎncă nu există evaluări

- Imagenes de Dibujo Diagrama 555Document9 paginiImagenes de Dibujo Diagrama 555Arely Vazquez Jmnz'Încă nu există evaluări

- Simbologia Circuito ElectricoDocument1 paginăSimbologia Circuito ElectricoNidia De La RosaÎncă nu există evaluări

- Analisis de Circuitos - Parte1Document7 paginiAnalisis de Circuitos - Parte1JuanDavidRamirezÎncă nu există evaluări

- Equivalente ElectricoDocument14 paginiEquivalente ElectricorudyÎncă nu există evaluări

- Deber 1. Pablo TenecotaDocument4 paginiDeber 1. Pablo Tenecotapablo tenecotaÎncă nu există evaluări

- La Ley de OhmDocument5 paginiLa Ley de OhmDanny Alexander TullumeÎncă nu există evaluări

- Unidad 1 - Introducción A La Corriente EléctricaDocument23 paginiUnidad 1 - Introducción A La Corriente Eléctricaarianna100% (1)

- Informe CircuitosDocument3 paginiInforme CircuitosANA MARIA ROMERO ARIASÎncă nu există evaluări

- FyQ 2 U 2-Electricidad2Document27 paginiFyQ 2 U 2-Electricidad2Vanesa Miriam TorresÎncă nu există evaluări

- Cristian David Parra Torres - Guia de Laboratorio 5Document6 paginiCristian David Parra Torres - Guia de Laboratorio 5Cristian ParraÎncă nu există evaluări

- OPERACIONALESDocument84 paginiOPERACIONALESBerenice FraireÎncă nu există evaluări

- Manual de Operacion Sam4s Er230 EspañolDocument146 paginiManual de Operacion Sam4s Er230 EspañolNicolas VilelaÎncă nu există evaluări

- Guia III - Sistemas de Control IDocument4 paginiGuia III - Sistemas de Control IJohn CastroÎncă nu există evaluări

- 10-Hardware de Red-Transmision de DatosDocument57 pagini10-Hardware de Red-Transmision de DatoseyguyegquÎncă nu există evaluări

- DIS Chispa DesechadaDocument14 paginiDIS Chispa DesechadaGustavo GamezÎncă nu există evaluări

- Laboratorio 2 ElectrotecniaDocument9 paginiLaboratorio 2 ElectrotecniaDiego Llave ChiloÎncă nu există evaluări