Documente Academic

Documente Profesional

Documente Cultură

1453 Pub

Încărcat de

John Walter Ticona QuispeDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

1453 Pub

Încărcat de

John Walter Ticona QuispeDrepturi de autor:

Formate disponibile

Diseo sobre FPGA de una Unidad Aritmtica Decimal

TITULACIN: Ingeniera Tcnica Industrial en Electrnica Industrial

AUTOR: Alejandro Baena Alonso

DIRECTOR: Jean-Pierre Deschamps

FECHA: Febrero / 2010

Diseo sobre FPGA de una Unidad Aritmtica Decimal

1. NDICE GENERAL

Diseo sobre FPGA de una Unidad Aritmtica Decimal ndice general

- 3 -

2. INTRODUCCIN

2.1 Objetivos del proyecto ............................................................................................................... 7

2.2 Aspectos bsicos ......................................................................................................................... 7

2.2.1 Aritmtica decimal.............................................................................................................. 7

2.2.2 Cdigo decimal codificado en binario (BCD) .................................................................... 8

2.2.3 Dispositivos programables.................................................................................................. 8

2.3 Diseo de Sistemas Electrnicos ............................................................................................... 9

2.3.1 Tendencias generales en Diseo Electrnico...................................................................... 9

2.3.2 Lenguajes de descripcin del hardware.............................................................................. 9

2.3.2.1 Qu son los lenguajes de descripcin del hardware?............................................. 9

2.3.2.2 El lenguaje VHDL................................................................................................... 10

2.3.2.2.1 Introduccin al lenguaje VHDL .................................................................... 10

2.3.2.2.2 Caractersticas............................................................................................... 10

2.3.2.2.3 Niveles de descripcin ................................................................................... 11

2.3.2.2.4 Estructura de una descripcin....................................................................... 11

2.3.2.2.5 Metodologa de diseo................................................................................... 12

2.3.3 Dispositivos lgicos programables ................................................................................... 13

2.3.4 Componentes IP (IP cores)............................................................................................... 15

2.3.5 Prototipado rpido ............................................................................................................ 16

2.4 Spartan-3E Starter Kit Board ................................................................................................... 16

3. MEMORIA DESCRIPTIVA

3.1 La Unidad Aritmtica Decimal ............................................................................................... 20

3.2 Bloques de la unidad................................................................................................................ 21

3.2.1 Sumador/Restador............................................................................................................. 21

3.2.1.1 Sumador .................................................................................................................. 21

3.2.1.1.1 Sumador de 1 dgito BCD (bloque one_digit_adder.vhd)......................... 21

3.2.1.1.2 Sumador de n dgitos decimales .................................................................... 24

3.2.1.2 Restador............................................................................................................... 26

3.2.1.2.1 Clculo del complemento a 9 (bloque nine_complement.vhd).................. 27

3.2.1.2.2 Sumador/Restador en complemento a 10

n

..................................................... 28

3.2.1.3 Sumador/Restador, representacin con signo y magnitud (bloque

n_adder_subs.vhd).......................................................................................................... 29

3.2.2 Multiplicador.. .......................................................................................................... 32

3.2.2.1 Multiplicador de 1x1 dgitos BCD (bloque one_digit_multiplier.vhd)................ 32

3.2.2.2 Multiplicador de Nx1 dgitos BCD (bloquen_by_one_multiplier.vhd)............... 34

3.2.2.3 Multiplicador de NxM dgitos BCD (bloquen_by_m_multiplier.vhd) ................ 37

3.2.3 Divisor .............................................................................................................................. 41

3.2.3.1 Algoritmo de divisin binaria ................................................................................. 41

3.2.3.2 Algoritmo de divisin BCD..................................................................................... 42

3.2.3.3 Error generado........................................................................................................ 42

3.2.3.4 Divisor BCD (bloque divider.vhd)...................................................................... 43

3.3 Diseo de la Unidad Aritmtica Decimal ............................................................................... 48

Diseo sobre FPGA de una Unidad Aritmtica Decimal ndice general

- 4 -

4. MEMORIA EXPERIMENTAL

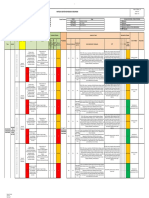

4.1 Descripcin del proceso ........................................................................................................... 54

4.2 Especificaciones ........................................................................................................................ 54

4.3 Elementos necesarios................................................................................................................ 55

4.4 Arquitectura a desarrollar ...................................................................................................... 55

4.5 Mdulos IP de terceros utilizados........................................................................................... 57

4.5.1 Microcontrolador PicoBlaze (mdulo kcpsm.vhd)........................................................ 57

4.5.2 Interfaz LCD (mdulo lcd_interface.vhd)..................................................................... 58

4.6 Memoria de programa (mdulo program_memory.vhd) ................................................... 60

4.7 Generacin del circuito (mdulo main.vhd) ....................................................................... 62

4.8 Asignacin de pines en la FPGA (archivo pins.ucf) .......................................................... 63

4.9 Implementacin en la FPGA................................................................................................... 65

4.9.1 Generacin del archivo..................................................................................................... 66

4.9.2 Implementacin en la FPGA ............................................................................................ 68

5. ANEXOS

5.1 Modelos VHDL......................................................................................................................... 72

5.1.1 Sumador de 1 dgito BCD (one_digit_adder.vhd)............................................................ 72

5.1.2 Complemento a 9 (nine_complement.vhd) ....................................................................... 73

5.1.3 Sumador/Restador de n dgitos decimales (n_adder_subs.vhd) ....................................... 73

5.1.4 Multiplicador de 1x1 dgitos BCD (one_digit_multiplier.vhd) ........................................ 75

5.1.5 Multiplicador de Nx1 dgitos BCD (n_by_one_multiplier.vhd) ....................................... 76

5.1.6 Multiplicador de NxM dgitos BCD (n_by_m_multiplier.vhd)......................................... 78

5.1.7 Divisor BCD (divider.vhd) ............................................................................................... 80

5.1.8 Unidad Aritmtica Decimal (arithmetic_unit.vhd) ........................................................... 83

5.1.9 Memoria de programa (program_memory.vhd) ............................................................... 86

5.1.10 Circuito completo (main.vhd) ......................................................................................... 89

5.2 Programa en lenguaje ensamblador (decimal_unit.asm) ...................................................... 94

5.3 Asignacin de pines en la Spartan-3E (pins.ucf) .................................................................... 97

6. BIBLIOGRAFA........................................................................................................................ 99

Diseo sobre FPGA de una Unidad Aritmtica Decimal

2. INTRODUCCIN

Diseo sobre FPGA de una Unidad Aritmtica Decimal Introduccin

- 6 -

2.1 Objetivos del proyecto ............................................................................................................... 7

2.2 Aspectos bsicos ......................................................................................................................... 7

2.2.1 Aritmtica decimal.............................................................................................................. 7

2.2.2 Cdigo decimal codificado en binario (BCD) .................................................................... 8

2.2.3 Dispositivos programables.................................................................................................. 8

2.3 Diseo de Sistemas Electrnicos ............................................................................................... 9

2.3.1 Tendencias generales en Diseo Electrnico...................................................................... 9

2.3.2 Lenguajes de descripcin del hardware.............................................................................. 9

2.3.2.1 Qu son los lenguajes de descripcin del hardware?............................................. 9

2.3.2.2 El lenguaje VHDL................................................................................................... 10

2.3.2.2.1 Introduccin al lenguaje VHDL .................................................................... 10

2.3.2.2.2 Caractersticas............................................................................................... 10

2.3.2.2.3 Niveles de descripcin ................................................................................... 11

2.3.2.2.4 Estructura de una descripcin....................................................................... 11

2.3.2.2.5 Metodologa de diseo................................................................................... 12

2.3.3 Dispositivos lgicos programables ................................................................................... 13

2.3.4 Componentes IP (IP cores)............................................................................................... 15

2.3.5 Prototipado rpido ............................................................................................................ 16

2.4 Spartan-3E Starter Kit Board ................................................................................................... 16

Diseo sobre FPGA de una Unidad Aritmtica Decimal Introduccin

- 7 -

2.1 Objetivos del proyecto

El objetivo de este proyecto es el diseo del modelo VHDL de una Unidad Aritmtica

Decimal, que pueda funcionar como coprocesador/acelerador dentro de otro sistema ms

complejo. Por tanto, se trata de un componente virtual utilizable en cualquier tipo de

sistemas que requieran operar en decimal.

Dicha unidad permitir realizar las operaciones aritmticas bsicas siempre operando en

decimal como son la suma, resta, multiplicacin y divisin de dos valores decimales.

Posteriormente, y a modo de testeo del modelo resultante, se implementar sobre una

FPGA, la SPARTAN-3E modelo XC3S500E de XILINX.

Para la creacin y simulacin de la unidad aritmtica decimal se ha utilizado el programa

MODELSIM PE en su versin STUDENT EDITION. Para la implementacin en la FPGA,

se ha utilizado el ensamblador PBLAZ IDE para la creacin de la memoria de programa, y

el paquete ISE DESIGN SUITE de XILINX para la sntesis y grabacin del cdigo en la

placa de pruebas.

2.2 Aspectos bsicos

2.2.1 Aritmtica decimal

Los sistemas que operan en decimal son preferibles a los que lo hacen en binario en un

gran nmero de aplicaciones aritmticas informticas. El motivo principal no es la

complejidad de las interfaces de codificacin y decodificacin (que tambin influye), sino

principalmente la falta de precisin y claridad de los resultados.

La aritmtica decimal desempea un papel clave en el procesamiento de datos en diversos

entornos, ya sean comerciales, financieros o de aplicaciones basadas en Internet, entre

otros. Y las prestaciones que estos requieren no quedan satisfechas con las unidades

convencionales que internamente operan en binario. En consecuencia, los procesadores de

propsito general que incluyen la implementacin hardware de aritmtica decimal estn

adquiriendo relevancia

Actualmente, el sistema decimal codificado en binario (BCD) es utilizado en el diseo de

algoritmos de aritmtica decimal; aunque otros sistemas de codificacin podran resultar

interesantes, el sistema BCD parece la mejor opcin por el momento.

Diseo sobre FPGA de una Unidad Aritmtica Decimal Introduccin

- 8 -

2.2.2 Cdigo decimal codificado en binario (BCD)

El cdigo decimal codificado en binario (BCD, Binary Coded Decimal, tambin conocido

como cdigo 8421) codifica los dgitos decimales del 0 al 9 mediante sus representaciones

binarias sin signo de 4 bits, desde 0000 a 1001. Las palabras de cdigo restantes, de 1010 a

1111, no se utilizan. Las conversiones entre las representaciones BCD y decimal son

triviales e implican la sustitucin directa de cuatro bits por cada dgito decimal.

El decimal codificado en binario es un cdigo ponderado, puesto que cada dgito decimal

puede obtenerse a partir de su palabra de cdigo asignando un peso fijo a cada bit de

palabra de cdigo. Los pesos para los bits BCD son 8, 4, 2, 1, y por esta razn el cdigo se

denomina en ocasiones cdigo 8421.

En la siguiente tabla se representa la correspondencia entre los nmeros decimales y las

combinaciones binarias del cdigo BCD:

Decimal BCD

0 0000

1 0001

2 0010

3 0011

4 0100

5 0101

6 0110

7 0111

8 1000

9 1001

Tabla 2.1. Correspondencia entre los dgitos decimales y cdigo BCD

2.2.3 Dispositivos programables

Hoy en da, las FPGA (Field Programmable Gate Arrays, de las que se hablar ms

adelante) son una de las tecnologas disponibles para el desarrollo de sistemas electrnicos.

Representan una atractiva opcin para la produccin de pequeas cantidades ya que sus

costes fijos (coste del prototipo, de la primera unidad) son bastante ms bajos que los

correspondientes en ASIC (Application-Specific Integrated Circuit, circuitos integrados de

aplicacin especfica). Adems, en pos de reducir el tamao y por tanto el coste unitario,

una posibilidad interesante es reconfigurarlas mientras operan de modo que el mismo

dispositivo pueda ejecutar diferentes funciones predefinidas.

Diseo sobre FPGA de una Unidad Aritmtica Decimal Introduccin

- 9 -

2.3 Diseo de Sistemas Electrnicos

2.3.1 Tendencias generales en Diseo Electrnico

Actualmente los sistemas electrnicos estn muy presentes en la mayora de mbitos,

desde la electrnica de consumo a los sistemas de control industrial, pasando por las

aplicaciones para automocin o seguridad, y un largo etctera

El problema principal radica en la complejidad del diseo de muchos de los elementos,

donde se exige, por ejemplo, que sean de fcil utilizacin y adaptables a varias

aplicaciones, que consuman pocos recursos y que puedan estar rpidamente a la venta

La tecnologa actual de circuitos integrados permite realizar e integrar estos complejos

sistemas en muy poco espacio; son los llamados sistemas empotrados (o embebidos) o SoC

(System on Chip). Estos sistemas, como pueden ser los ASIC (Application-Specific

Integrated Circuit) o las FPGA, permiten integrar en el mismo dispositivo uno o ms

microprocesadores o microcontroladores, coprocesadores, diversos bloques de memoria de

diferentes tipos, perifricos de entrada-salida, osciladores, buses para interconectar los

bloques, etc.

Estos sistemas embebidos para aplicaciones especficas incluyen hardware y software

especfico. En el caso de las FPGA, al ser dispositivos reconfigurables, son altamente tiles

para el desarrollo de prototipos o pequeas cantidades, a un precio razonablemente bajo.

2.3.2 Lenguajes de descripcin del hardware

2.3.2.1 Qu son los lenguajes de descripcin del hardware?

Los lenguajes de descripcin hardware (HDL, Hardware Description Language) surgen de

la necesidad de los diseadores de disponer de un conjunto de herramientas que permitan

describir los sistemas digitales de formas diferentes, facilitando el dilogo entre los propios

diseadores, aunque tambin entre las herramientas de diseo asistido por ordenador

(CAD, Computer-Aided Design) y entre diseadores y herramientas.

Los sistemas de desarrollo basados en lenguajes HDL permiten especificar y modelar la

estructura y funcin de un circuito digital; incluyen herramientas para compilar, simular y

sintetizar sistemas digitales. Estas herramientas de programacin se utilizan para

comprobar el funcionamiento del modelo antes de que sea construido.

Actualmente, los lenguajes HDL ms utilizados son VHDL y Verilog, ya que estn

estandarizados por el IEEE (Institute of Electrical and Electronic Engineers). Nosotros nos

centraremos en el primero de ellos.

Diseo sobre FPGA de una Unidad Aritmtica Decimal Introduccin

- 10 -

2.3.2.2 El lenguaje VHDL

2.3.2.2.1 Introduccin al lenguaje VHDL

VHDL proviene de VHSIC (Very High Speed Integrated Circuit) Hardware Description

Language. VHDL es un lenguaje de descripcin del hardware que puede utilizarse para

modelar, documentar, simular, verificar y sintetizar un sistema digital. Por tanto, abarca el

ciclo completo de diseo (salvo el trazado fsico o layout) desde las especificaciones

iniciales hasta la construccin del prototipo hardware. Proporciona el soporte necesario

para especificar su comportamiento o estructura, incluyendo jerarquas. Asimismo, es til

para metodologas de diseo ascendentes (bottom-up) como, sobre todo, descendentes (top-

down).

La semntica y construcciones del lenguaje permiten tambin disear con facilidad bancos

de prueba (test-benches), mediante los que se lleva a cabo la simulacin de los sistemas

modelados.

2.3.2.2.2 Caractersticas

VDHL es un lenguaje de descripcin hardware de mbito general derivado del lenguaje de

alto nivel ADA (que es el lenguaje para programar sistemas en tiempo real por excelencia).

Dispone de tipos abstractos para definir el formato y valores de seales, variables,

constantes, etc., y proporciona amplias facilidades para la realizacin de algoritmos.

Admite casi todos los niveles de descripcin, desde el algortmico (nivel ms alto) hasta el

lgico (nivel ms bajo). Para ello proporciona herramientas semnticas y sintcticas que se

pueden agrupar as:

Aquellas orientadas a las descripciones del comportamiento del circuito.

Aquellas orientas a la descripcin de las relaciones entre los distintos bloques

de un circuito, es decir, su estructura.

Al realizar una descripcin VHDL es importante elegir adecuadamente el nivel de funcin

del objetivo perseguido. Por ejemplo, si se pretende sintetizar la descripcin realizada, es

decir, si el objetivo final es obtener un conjunto de puertas e interconexiones, no se debe

emplear el nivel algortmico, pues en general las herramientas actuales de sntesis no

procesan de forma eficiente estas descripciones. Sin embargo, este nivel s es adecuado

cuando el objetivo es comprobar que un sistema complejo funciona correctamente, pues se

puede describir y simular de una forma rpida y eficaz.

Diseo sobre FPGA de una Unidad Aritmtica Decimal Introduccin

- 11 -

2.3.2.2.3 Niveles de descripcin

El lenguaje VHDL presenta tres mtodos bsicos para describir un circuito digital por

software:

El nivel algortmico es el que presenta un mayor grado de abstraccin (alto nivel).

Aqu el diseador solo describe el comportamiento del sistema, sin preocuparse de

las seales o componentes internos del mismo. Tambin llamado nivel de

comportamiento o behavior.

El nivel RTL (Register-Transfer Level, nivel de transferencia de registros)

proporciona un cierto grado de abstraccin con respecto al hardware, pero el

diseador se ve obligado a describir las distintas seales que interactan en un

circuito y su comportamiento en funcin de las entradas por medio de ecuaciones

lgicas y sentencias de asignacin. Tambin conocido como nivel de flujo de datos.

El nivel lgico describe la estructura interna de un circuito basndose en unos

componentes bsicos definidos previamente (equivaldra a un diagrama lgico).

2.3.2.2.4 Estructura de una descripcin

Toda descripcin en VHDL est constituida al menos por tres tipos de elementos:

bibliotecas (libraries), entidades (entities) y arquitecturas (architectures).

El diseador generalmente realiza la descripcin de las entidades empleando elementos

almacenados en las bibliotecas.

En la declaracin de la entidad se define el diseo como si fuera un producto encapsulado,

indicando el nmero de pines, los puertos de entrada y salida. La entidad puede definir

bien las entradas y salidas de un circuito integrado por disear o puede definir la interfaz

de un mdulo que ser utilizado en un diseo ms grande.

Para que la descripcin de un circuito sea completa se necesita, adems de su declaracin

como entidad, una especificacin de su funcionamiento. La arquitectura es la encargada de

ello. Es posible realizar diversas descripciones del funcionamiento del circuito, por lo que

pueden existir varias arquitecturas para una misma entidad.

Diseo sobre FPGA de una Unidad Aritmtica Decimal Introduccin

- 12 -

2.3.2.2.5 Metodologa de diseo

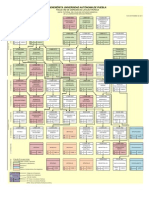

La Figura 2.1 muestra el flujo de diseo de un circuito en VHDL, desde su concepcin

hasta su fabricacin.

Figura 2.1. Flujo de diseo en VHDL

Una vez finalizada la prueba del concepto, se pasa al diseo detallado. Dependiendo de la

herramienta de sntesis que se utilice y de las especificaciones del circuito, la descripcin

VHDL estar desarrollada en un nivel de abstraccin mayor o menor (desde un nivel

algortmico a uno lgico).

Por ltimo se aborda la sntesis del circuito, es decir, el paso de una descripcin en VHDL

a un circuito real. El proceso de diseo puede terminar antes si el objetivo final no es la

fabricacin sino, por ejemplo, la creacin de componentes de biblioteca para uso posterior.

Diseo sobre FPGA de una Unidad Aritmtica Decimal Introduccin

- 13 -

2.3.3 Dispositivos lgicos programables

Existen dos grandes grupos de dispositivos lgicos programables: PLDs (Programmable

Logic Device, dispositivo lgico programable) y FPGAs (Field Programmable Gate Array,

matriz de puertas configurables).

Figura 2.2. Tipos de lgica programable

Los PLDs estn basados en una matriz AND + OR. Dentro de los PLDs encontramos las

PROM (Programmable Read Only Memory), las PAL (Programmable Logic Array) y las

PAL (Programmable Array Logic).

Figura 2.3. Familia de los PLD

Dentro de las PAL se encuentran los CPLDs (Complex PLD), compuestos por la

integracin de PLDs (PAL/GAL o PLA). Estn formados por bloques lgicos y matrices

de interruptores, donde cada bloque lgico corresponde a un PLD.

Figura 2.4. Ejemplo de arquitectura de CPLD (con 4 elementos lgicos o bloques programables)

Diseo sobre FPGA de una Unidad Aritmtica Decimal Introduccin

- 14 -

Las FPGA estn compuestas por una matriz de elementos lgicos cuya interconexin y

funcionalidad se puede programar. En comparacin con los dispositivos CPLD, difieren en

la arquitectura, no utilizan matrices de tipo PAL/PLA y tienen unas densidades mucho

mayores que los anteriores. Una FPGA tpica tiene un nmero de puertas equivalentes

mucho mayor que un dispositivo CPLD tpico. Los elementos que implementan las

funciones lgicas en las FPGA son, generalmente, mucho ms pequeos que en los CPLD,

por lo que hay muchos ms de esos elementos. Asimismo, en las FPGA, las

interconexiones programables estn organizadas segn una disposicin de filas y

columnas.

Figura 2.5. Arquitectura interna de una FPGA

Los tres elementos bsicos en una FPGA son el bloque configurable (CLB, Configurable

Logic Block), las interconexiones y los bloques de entrada/salida (E/S). Los bloques CLB

de una FPGA son menos complejos que sus homnimos en un CPLD, pero suele haber

muchos ms de ellos. La matriz distribuida de interconexiones programables permite

interconectar los bloques CLB entre s y conectarlos a las entradas y a las salidas. Los

bloques de E/S situados alrededor del permetro de las estructura proporcionan un acceso

de entrada/salida o bidireccional, individualmente seleccionable, hacia el mundo exterior.

Estructura de los bloques lgicos configurables

Cada bloque lgico de la FPGA est formado por mltiples mdulos lgicos ms pequeos

(que son los componentes bsicos) y por una serie de interconexiones programables locales

que se emplean para conectar entre s los mdulos lgicos que componen el CLB.

Mdulo lgico

Mdulo lgico

Mdulo lgico

CLB

Interconexin

local

Figura 2.6. Arquitectura de un CLB

Diseo sobre FPGA de una Unidad Aritmtica Decimal Introduccin

- 15 -

Un mdulo lgico puede configurarse para implementar lgica combinacional, lgica

registrada o una combinacin de ambas. Se emplea un flip-flop que forma parte de la lgica

asociada para implementar lgica registrada. A continuacin se muestra un diagrama de

bloques de un mdulo lgico tpico basado en LUT (Look-Up Table, tipo de memoria

programable que se utiliza para generar funciones booleanas):

LUT

Lgica

asociada

A

0

A

1

A

n-1

Salida suma de

productos

Mdulo lgico

E/S

Figura 2.7. Diagrama de bloques bsico de un mdulo lgico

Los dispositivos FPGA son reprogramables, y los de gran tamao pueden tener decenas de

miles de bloques CLB, adems de memoria y otros recursos. Por todo ello y la gran

flexibilidad que presentan, son ideales para realizar prototipos de manera rpida, en

pequeas cantidades.

2.3.4 Componentes IP (IP cores)

Dentro de una FPGA se puede incluir la funcionalidad de varios circuitos integrados. Esta

funcionalidad puede ser desarrollada uno mismo o adquirida a travs de terceros. Debido a

que estas funcionalidades son como componentes electrnicos, pero sin su parte fsica, se

les suele llamar componentes virtuales. En la industria se les conoce como bloques de

propiedad intelectual o IP cores (Intellectual Property).

Existen tres tipos de IP cores:

Hablamos de soft-core cuando se trata de cdigo sintetizable, similar al cdigo

fuente para software o tambin a descripcin a nivel de puerta (netlist).

Entendemos por hard-core el caso de una descripcin fsica, a nivel fsico (de

transistores); estos mdulos presentan problemas a la hora de asociar diferentes

procesos entre ellos o pasar de una lnea de fabricacin a otra.

Por firm-core nos referimos a un diseo que puede ser modificado en trminos de

placement & routing o en tecnologa de bibliotecas.

Los dispositivos FPGA que contienen procesadores integrados y otras funciones

implementadas en forma de mdulos de hardware (hard-core) y de mdulos de software

(soft-core) se conocen con el nombre de dispositivos FPGA de plataforma, porque

pueden emplearse para implementar un sistema completo sin necesidad de dispositivos

externos de soporte.

El objetivo de este proyecto es el de crear un IP core o componente IP que realice

operaciones en decimal. En este caso se tratar de un soft-core.

Diseo sobre FPGA de una Unidad Aritmtica Decimal Introduccin

- 16 -

2.3.5 Prototipado rpido

Un sistema completo (hardware y software) y su entorno no puede ser validado nicamente

mediante la simulacin. El objetivo es comprobar en la prctica el funcionamiento del

prototipo a un coste asequible.

El prototipado rpido es una posibilidad que facilita enormemente el diseo, mediante la

cual un circuito compuesto por una gran cantidad de puertas lgicas puede ser

implementado en un circuito integrado configurable, como lo puede ser una FPGA, a partir

de una descripcin en HDL mediante un simple ordenador personal (PC), sin la necesidad

de adquirir o disponer de un equipamiento caro. Y la tecnologa que permite dicha tcnica

la forman las tarjetas de prototipado rpido, que permiten reproducir desde funciones

sencillas hasta complejos sistemas en un chip (SoC, System on Chip).

Dichas tarjetas incluyen los componentes necesarios para esta misin: dispositivos

programables (CPLD, FPGA), memoria de datos y de programa, componentes de entrada-

salida y conectores (displays, puertos Ethernet, USB, RS-232, conversores analgico-

digital y viceversa, interruptores, LEDs), osciladores internos (reloj del sistema)

Un ejemplo de este tipo de dispositivos es la Spartan-3E Starter Kit Board, que

utilizaremos para comprobar el funcionamiento de nuestra Unidad Aritmtica Decimal.

2.4 Spartan-3E Starter Kit Board

La unidad Spartan-3E Starter Kit Board nos proporciona las herramientas necesarias para

testear nuestro sistema. Incluye la placa de pruebas con una FPGA Spartan-3E modelo

XC3S500E, fuente de alimentacin, cable USB para programar el dispositivo, software

para sintetizar e implementar nuestro modelo y manuales de referencia.

A continuacin enumeramos algunas caractersticas de la placa:

Dispositivos Xilinx integrados:

- FPGA de la familia Spartan-3E modelo XC3S500E-4FG320C (con 232 pines

de E/S para el usuario, 1164 CLBs o bloque lgicos configurables y 10000

celdas o mdulos lgicos)

- Controlador CPLD CoolRunner-II CPLD (XC2C64A-5VQ44C)

- 4 Mbits de memoria PROM Platform Flash

Reloj: oscilador de 50 MHz

Otra memoria incluida:

- 128 Mbits de memoria Parallel Flash

- 16 Mbits de memoria SPI (Serial Peripheral Interface) Flash

- 64 MBytes de memoria DDR SDRAM

Diseo sobre FPGA de una Unidad Aritmtica Decimal Introduccin

- 17 -

Interfaces y conectores:

- 4 interruptores tipo pulsador

- 4 salidas DAC (Digital-to-Analog Converter)

- 2 entradas ADC (Analog-to-Digital Converter)

- Conexin Ethernet 10/100

- Puerto USB

- 2 puertos serie RS-232

- Puerto PS/2 para ratn o teclado

- 4 interruptores tipo slide

-

Display: Pantalla LCD de 2 lneas de 16 caracteres cada una

Figura 2.8. Vista superior de la Spartan-3E

Diseo sobre FPGA de una Unidad Aritmtica Decimal

3. MEMORIA DESCRIPTIVA

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 19 -

3.1 La Unidad Aritmtica Decimal ............................................................................................... 20

3.2 Bloques de la unidad................................................................................................................ 21

3.2.1 Sumador/Restador............................................................................................................. 21

3.2.1.1 Sumador .................................................................................................................. 21

3.2.1.1.1 Sumador de 1 dgito BCD (bloque one_digit_adder.vhd)......................... 21

3.2.1.1.2 Sumador de n dgitos decimales .................................................................... 24

3.2.1.2 Restador............................................................................................................... 26

3.2.1.2.1 Clculo del complemento a 9 (bloque nine_complement.vhd).................. 27

3.2.1.2.2 Sumador/Restador en complemento a 10

n

..................................................... 28

3.2.1.3 Sumador/Restador, representacin con signo y magnitud (bloque

n_adder_subs.vhd).......................................................................................................... 29

3.2.2 Multiplicador.. .......................................................................................................... 32

3.2.2.1 Multiplicador de 1x1 dgitos BCD (bloque one_digit_multiplier.vhd)................ 32

3.2.2.2 Multiplicador de Nx1 dgitos BCD (bloquen_by_one_multiplier.vhd)............... 34

3.2.2.3 Multiplicador de NxM dgitos BCD (bloquen_by_m_multiplier.vhd) ................ 37

3.2.3 Divisor .............................................................................................................................. 41

3.2.3.1 Algoritmo de divisin binaria ................................................................................. 41

3.2.3.2 Algoritmo de divisin BCD..................................................................................... 42

3.2.3.3 Error generado........................................................................................................ 42

3.2.3.4 Divisor BCD (bloque divider.vhd)...................................................................... 43

3.3 Diseo de la Unidad Aritmtica Decimal ............................................................................... 48

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 20 -

3.1 La Unidad Aritmtica Decimal

Nuestro objetivo es la creacin del modelo VHDL de una Unidad Aritmtica Decimal, es

decir, una unidad que, operando en sistema BCD, realice las operaciones de suma, resta,

multiplicacin y divisin.

Figura 3.1. Representacin previa de la Unidad Aritmtica Decimal

Necesitaremos un sistema que dados dos valores de entrada de n dgitos BCD cada uno, x e

y, calcule el resultado z (de 2n dgitos BCD) de la operacin que hayamos escogido

previamente mediante la seal de entrada operation. Adems, contaremos con las seales

de entrada start (para iniciar el clculo interno cuando sea necesario), reset (reiniciar el

sistema), clk (seal de reloj) y las de salida carry (acarreo de salida cuando sea necesario)

y done (indicador de resultado disponible).

Para ello, la primera idea es que deberemos crear el modelo necesario para poder ejecutar

cada operacin.

Unidad aritmtica decimal

Sumador Restador Multiplicador Divisor

Figura 3.2. Estructura interna previa de la Unidad Aritmtica Decimal

Por consiguiente, nos centraremos primero en el diseo de los mdulos primarios que

realizarn las diferentes operaciones y despus los integraremos en la unidad principal.

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 21 -

3.2 Bloques de la unidad

3.2.1 Sumador/Restador

3.2.1.1 Sumador

En este apartado nuestro objetivo es la realizacin de un sumador de n dgitos decimales.

Para ello, lo primero que hacemos es crear una estructura bsica, el sumador de 1 dgito

decimal.

3.2.1.1.1 Sumador de 1 dgito BCD (bloque one_digit_adder.vhd)

La idea principal de este bloque es que, dadas dos entradas, a y b, que representan cada una

1 dgito decimal, tenemos una arquitectura cuya misin es realizar la suma de ambos

dgitos y dar como resultado (c) 1 dgito decimal de salida y un acarreo (carry_out) en caso

de ser necesario.

Figura 3.3. Sumador de 1 dgito decimal

La estructura interna del bloque sera la siguiente:

Figura 3.4. Arquitectura del sumador de 1 dgito decimal

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 22 -

Tenemos dos entradas, a y b, que pueden representar cualquier dgito decimal del 0 al 9,

una salida c que tambin ser un dgito BCD, y un acarreo de salida (carry_out). Tambin

hay un acarreo de entrada, carry_in, que nos permitir interconectar diversos bloques.

Funcionamiento

Al realizar la suma binaria se nos pueden presentar dos casos: si el resultado de dicha suma

es igual o menor a 9 (1001), el resultado es directo (es decir, a + b = c). Si la suma es

superior a 9, debemos realizar una correccin al valor obtenido.

El proceso en este segundo caso es el siguiente: realizamos la suma de a y b en binario,

obteniendo el valor intermedio d formado por 5 bits (Figura 3.4). Son 5 bits porque el

mximo nmero en decimal que podemos obtener es que el que se da cuando a y b tienen

sus valores mximos (9) y el acarreo de entrada carry_in es igual a 1; el resultado de la

suma (a + b + carry_in) es 19, y en binario sera 10011 (los cinco bits mencionados).

Para el caso de que la suma de a y b sea mayor que 9, aplicaremos un factor de correccin

que sera restar 10 al valor obtenido y aumentar 1 el dgito de las decenas. Y restar diez

equivale en binario a sumar 6 (0110). Un ejemplo: si a es 5 y b es 7, la suma es 12 y

debemos realizar la correccin.

Empezamos sumando 5 y 7. Sus correspondientes en binario son 0101 para el 5 y 0111

para el nmero 7. El resultado es 12, que en binario se representa como 1100.

1 1 1 decimal

0 1 0 1 5

+ 0 1 1 1 7

1 1 0 0 12

Vemos que este valor es superior a 9, y por tanto no es un valor BCD vlido. Entonces

hemos de aplicar una correccin para obtener el valor correspondiente en BCD, donde el

nmero 12 se representara con dos dgitos de cuatro bits cada uno; un primer grupo para el

1 0001, y otro grupo para el 2 0010. Para pasar de binario a BCD vamos a sumar 6 (en

binario 0110):

1 1

1 1 0 0 12

+ 0 1 1 0 6

1 0 0 1 0

Obtenemos 10010, donde debemos leer los ltimos cuatro bits para el primer dgito

decimal 0010 y que equivalen al nmero 2, y el bit de ms peso, 1, que formara parte

del siguiente dgito decimal, que sera un 1. Por tanto, tendramos como resultado dos

dgitos decimales, un dgito decimal de las decenas igual a 1, y otro para las unidades que

sera un 2. Hemos pasado del valor 12, 10010 en binario, a su equivalente en

nomenclatura BCD, 0001 0010.

Equivale a un dgito BCD de

valor 2 (0010)

Equivale a un dgito BCD

de valor 1 (0001)

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 23 -

Decimal 12

Binario 1100

BCD 0001 0010

En resumen:

Si a + b + cy_in 9, a + b + cy_in = c, acarreo de salida = 0 (3.1)

Si a + b + cy_in > 9, a + b + cy_in = (c + 6) mod 16, acarreo de salida = 1 (3.2)

A continuacin podemos ver una simulacin del funcionamiento de este bloque:

Figura 3.5. Simulacin del sumador de 1 dgito decimal

Podemos observar como se realiza la correccin cuando a + b > 9, obteniendo como

resultado en c el dgito de las unidades, y el dgito 1 (0001) de las decenas en el acarreo

de salida (cy_out).

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 24 -

3.2.1.1.2 Sumador de n dgitos decimales

Para obtener el sumador de n dgitos BCD vamos a interconectar n sumadores de 1 dgito

decimal (el bloque que hemos creado antes). Gracias a la entrada carry_in de cada bloque,

podemos propagar el acarreo de manera que el resultado obtenido sea el correcto.

Figura 3.6. Diagrama de bloques del sumador de n dgitos decimales

La interconexin de los bloques sencillos crear el sumador de n dgitos BCD,

Figura 3.7. Sumador de n dgitos decimales

donde tendremos dos entradas, x e y, de n dgitos BCD (4n bits), y una salida z que ser el

resultado de la operacin. Adems, en el caso de que haya desbordamiento en z, la salida

out_carry se pondr a 1. La entrada ini_carry en este bloque se corresponde con el

acarreo de entrada del primer sumador de 1 dgito BCD.

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 25 -

A continuacin se muestra la simulacin de unos ejemplos para n = 4:

Figura 3.8. Simulacin del sumador de 4 dgitos decimales

Podemos ver como en la tercera operacin (x = 3050, y = 8070), el acarreo de salida est a

nivel alto, lo que indica que el resultado es z = 11120.

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 26 -

3.2.1.2 Restador

El objetivo es crear un bloque que dados dos valores de entrada de n dgitos, x e y, calcule

la diferencia z, e indique mediante una seal de salida denominada carry_out si el

resultado ha sido positivo (carry_out = 0) o negativo (carry_out = 1),

Figura 3.9. Restador de n dgitos decimales

Para ello, nos basaremos en dos operaciones bsicas; una es la suma descrita en el apartado

anterior, por lo que utilizaremos el Sumador de n dgitos decimales, y la otra es la

utilizacin del complemento a 10

n

del valor y de entrada. El complemento a 10

n

de un

nmero se puede obtener a partir de calcular el complemento a 9 de cada dgito (con un

bloque que haga esta funcin) y sumando 1 al resultado.

Un valor decimal x puede expresarse como:

x

n-1

x

n-2

x

1

x

0

= x

n-1

10

n-1

+ x

n-1

10

n-2

+ + x

1

10 + x

0

, (3.3)

y su complemento a 9 equivale a

9 x

n-1

9 x

n-2

9 x

1

9 x

0

= 10

n

1 (x

n-1

x

n-2

x

1

x

0

), (3.4)

por lo que podemos establecer la siguiente igualdad:

10

n

(x

n-1

x

n-2

x

1

x

0

) = (9 x

n-1

9 x

n-2

9 x

1

9 x

0

) + 1 (3.5)

Es decir, el complemento a 10

n

de un valor x equivale a realizar el complemento a 9 de

cada dgito y sumar 1 (lo que ya habamos avanzado anteriormente).

Se puede calcular la resta mediante la expresin x + (10

n

y), que plantea dos casos

posibles:

Si x y: x + (10

n

y) 10

n

, siendo z = x y, con carry_out = 1 (3.6)

Si x < y: x + (10

n

y) < 10

n

, siendo z = 10

n

+ (x y), con carry_out = 0 (3.7)

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 27 -

3.2.1.2.1 Clculo del complemento a 9 (bloque nine_complement.vhd)

Diseamos un bloque que dado un dgito BCD de entrada (e), calcule su complemento a 9

(s). Este bloque estar controlado por una seal de entrada denominada add_sub,

encargada de habilitar o no la operacin. Si su valor es 1, s mostrar el complemento a 9

de e; en caso contrario s tomar el mismo valor que e.

Figura 3.10. Bloque de complemento a 9 de un dgito BCD

Dado un dgito BCD e de cuatro bits (e

3

e

2

e

1

e

0

), su complemento a 9 (s

3

s

2

s

1

s

0

) se

obtiene mediante la operacin 1001 e

3

e

2

e

1

e

0

(o su equivalente, 1001 + e

3

e

2

e

1

e

0

+ 1, es decir, sumando al minuendo el complemento a 2 del sustraendo). Las expresiones

resultantes son las siguientes:

3 2 1 3

2 1 2

1 1

0 0

e e e s

e e s

e s

e s

=

=

=

=

(3.8)

Si aadimos la seal de control add_sub, dichas expresiones quedan modificadas de esta

forma:

( )

3 2 1 3 3

2 1 2 2

1 1

0 0 0

_ _

) ( _ _

_ _

e e e sub add e sub add s

e e sub add e sub add s

e s

e sub add e sub add s

+ =

+ =

=

+ =

(3.9)

Figura 3.11. Ejemplo del funcionamiento del bloque de complemento a 9

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 28 -

3.2.1.2.2 Sumador/Restador en complemento a 10

n

Para implementar el restador utilizaremos, como hemos explicado antes, el sumador de n

dgitos y el bloque de complemento a 9 (nine_complement.vhd). El diagrama de bloques

resultante sera el mostrado a continuacin:

Figura 3.12. Restador de n dgitos decimales

Si nos fijamos en la Figura 3.12, podemos ver que la seal de control add_sub nos permite

realizar las operaciones de suma y resta:

Si add_sub = 0, la seal y no se modifica y tenemos la operacin suma (z = x + y)

Si add_sub = 1, lo que entra al sumador es el complemento a 9 de y; adems la

seal de entrada del sumador ini_carry (acarreo de entrada) toma el valor de

add_sub, por lo que la operacin que se realiza es la resta (z = x + y + ini_carry).

Debido a que podemos realizar las dos operaciones con un mismo bloque, lo

denominaremos Sumador/Restador de n dgitos.

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 29 -

3.2.1.3 Sumador/Restador, representacin con signo y magnitud (bloque

n_adder_subs.vhd)

Observemos otra vez en el ltimo bloque creado (Figura 3.12). Hemos visto que esta

estructura nos permite realizar las operaciones de suma y resta. Pongamos un par de

ejemplos sobre la resta siendo n = 3:

Si x = 735 e y = 177 (su complemento a 9 es 822), tendremos 735 + 822 + 1 (del

acarreo de entrada, valor de la seal add_sub). El resultado ser positivo e igual a

578, con el acarreo de salida (out_carry) igual a 1.

Si x = 485 e y 823 (su complemento a 9 es 176), tendremos 485 + 176 + 1. El

resultado ser 662 con un acarreo de salida igual a 0 (resultado negativo).

En este ltimo caso, para saber el resultado exacto de la operacin debemos calcular el

complemento a 10

n

del valor z que hemos obtenido; es decir, calcular el complemento a 9

de cada dgito de z y sumar 1 al resultado obtenido. Esto lo hacemos mediante una

modificacin de la arquitectura anterior, por lo que el diagrama de bloques final del

Sumador/Restador de n dgitos BCD ser el siguiente:

Sumador de n

dgitos decimales

ini_carry

carry_out

y(4n-1:0)

4n

x(4n-1:0)

4n

4n

z1

Complemento

a 9

4n

add_sub

Complemento

a 9

4n

1

4n

ini_carry 0

z3

z1

4n

0 1

4n

z(4n-1:0)

add_sub

oc

Sumador de n

dgitos decimales

ini_carry

4n

Figura 3.13. Sumador/Restador de n dgitos decimales

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 30 -

Esta modificacin implica un cambio en el significado del valor del acarreo de salida del

bloque (denominado carry_out), cuando realizamos la operacin resta:

Si carry_out = 0, el resultado de la resta es no negativo (x > y)

Si carry_out = 1, el resultado de la resta es negativo (x < y)

Hemos aadido otro bloque que complementa a 9 el resultado z1 de la primera etapa y

posteriormente suma 1, lo que genera la seal z3. Dependiendo de los valores de add_sub y

oc (acarreo de la primera etapa), el multiplexor seleccionar z1 o z3. Concretamente,

cuando el resultado de la resta sea positivo (carry_out = 0), el multiplexor seleccionar el

canal 0 (z1), y si el resultado es negativo (carry_out = 1) seleccionar el canal 1 (z3).

A modo de resumen, el Sumador/Restador de n dgitos decimales presenta las siguientes

caractersticas:

add_sub Operacin carry_out Resultado

0 Suma 0 Exacto

0 Suma 1 Hay desbordamiento

1 Resta 0 Positivo

1 Resta 1 Negativo

Tabla 3.1. Operaciones del Sumador/Restador

A continuacin mostramos unos ejemplos de la simulacin para n = 4:

En modo resta (add_sub = 1):

Figura 3.14. Simulacin del Sumador/Restador en modo resta

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 31 -

En modo suma (add_sub = 0):

Figura 3.15. Simulacin del Sumador/Restador en modo suma

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 32 -

3.2.2 Multiplicador

En este apartado crearemos un mdulo que multiplique dos valores de entrada, x e y, de n y

m dgitos BCD respectivamente, y muestre el resultado en z, de n + m dgitos BCD.

Figura 3.16. Multiplicador de NxM dgitos BCD

Para ello lo primero que haremos ser definir una estructura bsica que realizar la

multiplicacin de dos dgitos BCD (multiplicador de 1x1 dgitos BCD), despus

realizaremos un bloque que multiplique un nmero de n por 1 dgitos BCD, y finalmente el

multiplicador de NxM dgitos BCD.

3.2.2.1 Multiplicador de 1x1 dgitos BCD (bloque one_digit_multiplier.vhd)

El producto decimal se puede obtener a travs del producto binario y una etapa de

correccin posterior. La etapa bsica sera un multiplicador de 1x1 dgitos BCD, es decir,

dos entradas de 1 dgito BCD cada una. sta se puede implementar a partir de un circuito

combinacional.

Multiplicador de

1 dgito BCD

a(3:0) b(3:0)

4 4

u(3:0)

4

d(3:0)

4

Figura 3.17. Multiplicador de 1x1 dgitos BCD

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 33 -

80 40 20 10 8 4 2 1

p3 p2 p1 p0

p4 p4 p4

+ p5 p5 p5

p6 p6 p6

d3 d2 d1 d0 u3 u2 u1 u0

Tenemos A y B que son dos dgitos BCD (a

3

a

2

a

1

a

0

y b

3

b

2

b

1

b

0

respectivamente). El

producto BCD de ambos dgitos se puede expresar como:

U D B A + = 10 , (3.10)

es decir, la cifra de las decenas multiplicada por 10 ms las unidades.

El producto binario de A y B se puede expresar en un primer paso como un nmero de 7

bits tal que:

0 1 2 3 4 5 6

p p p p p p p P B A = = (3.11)

Son un mximo de 7 bits porque el resultado mximo que podemos tener en esta operacin

es 81 en decimal, que corresponder al caso de que A y B tengan su valor mximo, y este

es 9. La representacin binaria del nmero 81 es 1010001 (7 bits).

Podemos convertir el nmero binario P a cdigo BCD mediante sumas binarias tras

corregir los trminos descritos en la Figura 3.18. La primera fila indica el peso de cada

dgito BCD. Los pesos de p

3

p

2

p

1

p

0

son los mismos que para el valor binario. Pero los

pesos de p

4

p

5

y p

6

se pueden descomponer en los valores BCD de la Figura 3.18.

Concretamente, p

4

(cuyo peso es 16 en binario) se puede descomponer como (10, 4, 2), p

5

(peso binario igual a 32) se puede descomponer en (20, 10, 2) y por ltimo p

6

(peso binario

64) como (40, 20, 4).

Figura 3.18. Reduccin aritmtica de binario a BCD

Sumamos los trminos y obtenemos las expresiones que nos darn el valor de las unidades

(uu) y las decenas (dd):

5 6 4 5 6

5 6 4 4 0 1 2 3

0

0 0 0 0

p p p p p dd

p p p p p p p p uu

+ =

+ + =

(3.12)

Dada esta ltima expresin de uu, podemos ver que su valor estar entre 0 y 27 (segn los

valores de p

0

, p

1

, p

2

, p

3

, p

4

, p

5

y p

6

). Si el valor de uu es superior a 9 (con lo que se

necesitara de ms de 1 dgito BCD para representarse) deberemos realizar una correccin

para obtener un resultado correcto. A continuacin definimos dichos trminos de

correccin:

Si uu 9: no hacemos ninguna correccin, el valor es correcto,

Si 9 < uu 19: sumamos 1 a dd, (aadimos 1 a las decenas y 6 a las unidades; esto

ltimo equivale a restar 10),

Si 19 < uu: sumamos 2 a dd, (aadimos 2 a las decenas y 12 a las unidades; esto

ltimo equivale a restar 20).

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 34 -

Definiremos una variable para cada caso y mediante las siguientes expresiones booleanas

sabremos cual tenemos en cada momento.

Si uu es mayor o igual a 10:

) ( 9

1 2 3 4

uu uu uu uu gt = (3.13)

Si uu es mayor o igual a 20:

) ( 20

2 3 4

uu uu uu gt = (3.14)

Si uu se encuentra entre 10 y 19 (ambos incluidos):

20 9 19 10 gt gt st gt = (3.15)

Por ltimo obtenemos los valores finales para las decenas (d) y las unidades (u) al aadir

las correcciones pertinentes:

u = (uu

3

uu

2

uu

1

uu

0

) + (gt20 gt9 gt10st19 0)

d = (dd

3

dd

2

dd

1

dd

0

) + (0 0 gt20 gt10st19) (3.16)

Simulacin

Figura 3.19. Muestra de la simulacin del multiplicador de 1x1 dgitos BCD

3.2.2.2 Multiplicador de Nx1 dgitos BCD (bloque n_by_one_multiplier.vhd)

Un multiplicador de Nx1 dgitos BCD se puede construir a partir de n multiplicadores de

1x1 dgitos BCD seguido de sumadores BCD. Por tanto, para realizar este bloque

utilizaremos dos que hemos creado anteriormente; uno ser el multiplicador que acabamos

de hacer (multiplicador de 1x1 dgitos BCD, one_digit_multiplier.vhd) y el otro ser el

sumador de 1 dgito BCD (one_digit_adder.vhd).

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 35 -

Pongamos un ejemplo: si n es igual a 3, tendremos la siguiente estructura,

Multipl.

1x1 BCD

4 4

u

0

4

y x

0

d

0

4 Multipl.

1x1 BCD

4 4

u

1

4

y x

1

d

1

4

4 4

u

2

4

y x

2

d

2

4

Multipl.

1x1 BCD

Figura 3.20. Multiplicador de 3x1 dgitos BCD (parte 1)

donde x ser el nmero de 3 dgitos BCD (x

2

x

1

x

0

). Cada multiplicador genera un valor

para las unidades (u

x

) y uno para las decenas (d

x

); este ltimo ser el que deba sumarse a

las unidades del siguiente multiplicador. Esta estructura nos muestra que necesitaremos un

sumador de n + 1 dgitos BCD.

El resultado z (formada por 4 dgitos BCD) ser el siguiente:

z = (0 u

2

u

1

u

0

) + (d

2

d

1

d

0

0) (3.17)

Sumador 1

dgito BCD

z

0

4

4

u

0

4

0

Sumador 1

dgito BCD

z

1

4

4

u

1

4

d

0

Sumador 1

dgito BCD

z

2

4

4

u

2

4

d

1

Sumador 1

dgito BCD

z

3

4

4

0

4

d

2

Figura 3.21. Multiplicador de 3x1 dgitos BCD (parte 2)

Viendo este ejemplo podemos afirmar que, para un multiplicador de Nx1 dgitos BCD,

necesitaremos n multiplicadores 1x1 y n + 1 sumadores de 1 dgito.

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 36 -

Tendremos dos seales de entrada: un valor x de n dgitos (x

n-1

x

n-2

x

2

x

1

x

0

) y un valor y

de 1 dgito, lo que generar una seal de salida z (z

n

z

n-1

z

n-2

z

2

z

1

z

0

).

Figura 3.22. Multiplicador de Nx1 dgitos. Incluye n multiplicadores 1x1 y n + 1 sumadores de 1 dgito

A continuacin se muestra un ejemplo de la simulacin del bloque para n = 5:

Figura 3.23. Simulacin del multiplicador Nx1 dgitos BCD

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 37 -

3.2.2.3 Multiplicador de NxM dgitos BCD (bloque n_by_m_multiplier.vhd)

En este bloque tenemos como datos iniciales dos nmeros decimales, x e y, de n y m

dgitos respectivamente (x

n-1

x

n-2

x

2

x

1

x

0

e y

m-1

y

m-2

y

2

y

1

y

0

). El resultado ser z, un

nmero decimal de n + m dgitos (z

(n+m)-1

z

(n+m)-2

z

2

z

1

z

0

).

Figura 3.24. Multiplicador de NxM dgitos BCD

Tambin tendremos las entradas start (indica inicio de operacin), clk (seal de reloj) y

reset (que inicializa el bloque), y la salida done (que informa de operacin realizada).

Los valores n y m sern los parmetros genricos del circuito.

Para realizar esta operacin vamos a crear un sistema secuencial (a diferencia de los que

habamos hecho hasta ahora, que eran combinacionales) en el que mediante un bucle,

utilizaremos m veces el multiplicador de Nx1 dgitos (n_by_one_multiplier.vhd) y

sumaremos y almacenaremos los resultados parciales (mediante el bloque

n_adder_subs.vhd en modo suma y registros internos).

Que sea un sistema secuencial ayudar a reducir el coste del mismo, ya que utilizaremos un

solo multiplicador en lugar de utilizar m multiplicadores de Nx1.

El algoritmo que utilizaremos ser el siguiente:

z : = 0;

f or i i n 1 . . ml oop

z : = z 10 + x y

m- i

;

end l oop;

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 38 -

El diagrama de bloques del circuito es:

left shift register y

Multiplicador Nx1

dgitos BCD

4 4m

1111 y(4m-1:0)

4n

x(4n-1:0)

load

shift

clk

Sumador n

dgitos BCD

register z

load

shift

clk

4(n+1)

x 10

z(4(n+m)-1:0)

4(n+m)

4

z_by_10

next_z

x_by_yi

int_y(m)

Figura 3.25. Diagrama de bloques del multiplicador NxM

El funcionamiento es el siguiente: se inicializa el registro de desplazamiento (load = 1)

con el valor de y seguido de un dgito no decimal (15 = 1111), que ser el indicador de

que ya hemos multiplicado todos los valores de y. A cada etapa (shift = 1) se desplaza el

valor una posicin (4 bits) a la izquierda. De esta manera entrarn sucesivamente en el

multiplicador Nx1 los dgitos y

m-1

, y

m-2

, y

1

, y

0

; una seal interna detectar el 1111 e

indicar el fin de clculo.

En el multiplicador Nx1 tendremos en una entrada el valor de x, multiplicando cada vez

por el dgito de y correspondiente. Es decir, en un primer paso el multiplicador realizara el

producto de x

n-1

x

n-2

x

1

x

0

e y

m-1

. El valor resultante pasara al sumador, donde no se

modificara ya que el registro z se inicializa con 0, y se almacenara en dicho registro.

En la siguiente etapa, se desplazar el registro de desplazamiento otra posicin; en el

multiplicador ahora tendremos como entradas x

n-1

x

n-2

x

1

x

0

e y

m-2

. En el sumador

tendremos como entradas el ltimo producto generado y el primer valor que se almacen

en el registro z multiplicado por 10.

Este proceso se repite hasta que se detecta el dgito no decimal 1111 en el registro de

desplazamiento que indica que se han ledo todos los valores de y.

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 39 -

En la siguiente figura podemos ver una simulacin del proceso, donde hemos establecido

n = 3 y m = 4:

Figura 3.26. Simulacin del multiplicador NxM dgitos BCD

Para controlar este sistema secuencial necesitaremos una unidad de control. Dicha unidad

recibir como seales de entrada start, clk, reset y end_of_computation, y generar las

seales shift, load y done:

Figura 3.27. Unidad de control

La unidad de control se puede representar con una mquina de 4 estados:

E

0

E

1

E

2

E

3

shift = 0

load = 0

done = 1

start = 1

end_of_ computation = 1

start = 0

start = 1 start = 0

shift = 0

load = 0

done = 1

shift = 0

load = 1

done = 0

shift = 1

load = 0

done = 0

end_of_ computation = 0

Figura 3.28. Mquina de estados de la unidad de control

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 40 -

E

0

es el estado inicial (seal current_state), con un bucle de espera para que la seal start

pase a nivel bajo y avanzar al estado 1 (caso de que start se haya mantenido a 1 como

consecuencia de una operacin anterior).

Aqu se espera a que start sea igual 1 (lo que hemos hecho ha sido detectar la transicin

de 0 a 1 de esta seal). En E

2

se cargan los valores iniciales en los registros (load = 1).

Entonces pasamos a E

3

, donde se ejecutan las etapas de clculo (shift = 1) hasta que la

seal end_of_computation sea igual a 1, lo que significar que el dgito ledo int_y es 15

(1111) y ha finalizado la operacin, volviendo al estado inicial y poniendo la seal done a

1, indicando que el proceso ha terminado.

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 41 -

3.2.3 Divisor

3.2.3.1 Algoritmo de divisin binaria

Dados dos nmeros naturales x e y, siendo x < y, el algoritmo de divisin binaria genera

dos naturales q y r tales que:

, 2 r y q x

p

+ = con r < y (3.18)

As

, 2 2

p p

r y q x

+ = (3.19)

y

, 2 2

p p

y

r

q

y

x

+ = siendo

p p

y

r

< 2 2 (3.20)

El algoritmo se basa en el siguiente conjunto de igualdades:

r

0

= x, de modo que r

0

< y,

2 r

0

= q

p-1

y + r

1

, con r

1

< y,

2 r

1

= q

p-2

y + r

2

, con r

2

< y,

2 r

2

= q

p-3

y + r

3

, con r

3

< y,

2 r

p-1

= q

0

y + r

p

, con r

p

< y, (3.21)

Multiplicando la primera ecuacin por 2

p

, la segunda por 2

p-1

, la tercera por 2

p-2

,, y la

ltima por 2

0

, y sumando las p ecuaciones tenemos que:

x 2p = (q

p-1

2

p-1

+ q

p-2

2

p-2

+ q

p-3

2

p-3

+ + q

0

2

0

) y + r

p

(3.22)

Si comparamos la expresin con (3.18), podemos obtener q y r ya que:

q = 0. q

p-1

q

p-2

q

p-3

q

0

y r = r

p

(3.23)

En cada paso se calculan q

p-i

y r

i

en funcin de r

i-1

e y:

2 r

i-1

= q

p-i

y + r

i

, siendo r

i

< y (3.24)

Se plantean dos opciones:

2 r

i-1

y : entonces

q

p-i

= 1 y r

i

= 2 r

i-1

y (3.25)

2 r

i-1

< y : entonces

q

p-i

= 0 y r

i

= 2 r

i-1

(3.26)

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 42 -

3.2.3.2 Algoritmo de divisin BCD

El algoritmo de divisin binaria se puede utilizar cualquiera que sea el sistema de

numeracin. Si trabajamos en base 10, la nica condicin para poder utilizarlo es que todas

las operaciones se hagan en base 10.

El algoritmo que utilizaremos ser el siguiente:

r : = x; q : = 0; ul p : = 0. 5;

f or i i n 1 . . p l oop

t wo_r : = 2*r ; di f : = t wo_r - y;

i f di f < 0 t hen r : = t wo_r ;

el se r : = di f ; q : = q + ul p;

end i f ;

ul p : = ul p/ 2;

end l oop;

Las operaciones en BCD que utilizaremos sern la multiplicacin por 2, la resta con

generacin de signo y la suma. Adems, la representacin BCD de 1/2, 1/2

2

, ..., 1/2

p

ser

calculada sobre la marcha.

3.2.3.3 Error generado

Si se ejecutan p etapas, el error es menor que 1/2

p

(segn el algoritmo). Supongamos que el

objetivo sea que el resultado se escriba con m dgitos fraccionarios y que el error sea menor

que 1/10

m

(significa que el resultado obtenido es el cociente exacto truncado). Para ello

basta con que se cumpla la siguiente relacin:

m p

<

10

1

2

1

, es decir ) 10 ( log

2

> m p , o sea que m p > 3 . 3 (3.27)

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 43 -

3.2.3.4 Divisor BCD (bloque divider.vhd)

El divisor BCD ser un mdulo que realice la divisin entre dos valores de entrada, x / y,

donde x < y (para que el algoritmo funcione), dando como resultado el cociente q de m

dgitos decimales (q

m-1

q

m-2

q

2

q

1

q

0

).

Tambin tendr como entradas las seales start (inicio de operacin), clk (seal de reloj) y

reset (que inicializa el bloque), y la salida done (que informa de operacin realizada).

Figura 3.29. Divisor BCD

El cociente q es una salida de m dgitos. Internamente, el cociente debe generarse con p

dgitos, donde p es del orden de 3.3m (segn hemos explicado anteriormente). Llmese qq

al cociente interno con p dgitos. El cociente q (el resultado que nosotros veremos) consta

de los m dgitos ms significativos de qq.

Los valores de n (dgitos de los valores de entrada), m (dgitos y por tanto precisin del

resultado, el cociente), p (nmero de iteraciones que se realizarn) y logp (nmero de bits

necesario para representar p) sern los parmetros genricos del modelo.

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 44 -

Basndonos en el algoritmo de ejecucin creamos el siguiente diagrama de bloques:

Sumador/Restador

n dgitos BCD

Multiplicador

Nx1 dgitos BCD

r

4 4n

0010

4n+4

Sumador/Restador

n dgitos BCD

y(4n-1:0)

4n

carry_out add_sub 1

0 1

rr_y(4n-5:0)

rr

load

0 1

ulp

4p

qq

4p

carry_out add_sub 0

4n 4p

ini.: x(4n-1:0)

clk

initially: 0

4n

4p

r

q(4m-1:0)

qq

4p

4p-4(p-m)

4 4p

0101 ulp

load

initially: 0.5

clk

4p

ulp

4p

4p+4

Multiplicador

Nx1 dgitos BCD

Figura 3.30. Diagrama de bloques del divisor BCD

Inicialmente cargamos en el registro r el valor de entrada x.

Para calcular el doble de r utilizamos un multiplicador de Nx1 dgitos BCD

(n_by_one_multiplier.vhd). En una entrada tendremos el valor r y en la otra el dgito 2

(0010 en binario).

La diferencia entre el doble de r (2r, seal rr) y el valor decimal de entrada y, la

calculamos mediante un Sumador/Restador de n dgitos BCD (n_adder_subs.vhd) en

modo resta (seal de entrada add_sub = 1).

Si el resultado de la resta es positivo (rr > y) entonces carry_out = 0 y se almacenarn en

el registro r los n dgitos menos significativos de la diferencia recin calculada (rr - y). Si

por el contrario rr < y, carry_out = 1, se almacenarn en el registro los n dgitos menos

significativos del valor de rr.

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 45 -

El registro qq donde se almacenan los valores intermedios del cociente se inicializa a 0.

La suma de qq y ulp la calculamos mediante un Sumador/Restador de n dgitos BCD

(n_adder_subs.vhd) que opere en modo suma (add_sub = 0). Si el resultado antes

calculado de rr - y es positivo, se almacenar en el registro qq el resultado de qq + ulp; si

es negativo, lo que se almacene ser el valor de qq.

La seal ulp (Unit in the Least significant Position, unidad en la posicin menos

significativa) es un nmero que al final del clculo tendr p dgitos. Su registro

(register_ulp) se inicializa con el valor 0.5 (0000 0101 en cdigo BCD). En cada

iteracin ir tomando los valores 0.5, 0.25, 0.125, 0.0625, y as sucesivamente; es decir,

multiplicando el anterior valor por 5 (mediante el multiplicador de Nx1 dgitos,

n_by_one_multiplier.vhd) y desplazando el resultado 4 bits a la derecha (o lo que es lo

mismo, introduciendo un 0 decimal delante). Al ser la salida del multiplicador por 5 un

nmero de p + 1 dgitos, slo utilizaremos los p dgitos de ms peso (lo que equivale a

dividir por 10).

Al acabar el clculo de la operacin (seal zero = 1), obtendremos el cociente q de

truncar el ltimo valor almacenado en el registro qq, a partir del nmero de dgitos m que

hayamos seleccionado.

Unidad de control

Este sistema que hemos creado tambin es secuencial y necesitar de una unidad de control

que lo gobierne.

Figura 3.31. Unidad de control del divisor

La unidad de control genera las seales load (escritura de los valores iniciales en los

registros), ce (actualizacin de los registros) y done (operacin finalizada).

La seal zero vendr controlada por un contador de p estados (este nmero se representa

con logp bits, como hemos dicho antes). Dicha seal se pondr a 1 cuando se ejecute el

paso p de la iteracin.

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 46 -

La mquina de estados asociada a la unidad de control es la siguiente:

Figura 3.32. Mquina de estados de la unidad de control del divisor

Simulacin

A continuacin mostramos un ejemplo de la simulacin del sistema para los valores

genricos n = 3, m = 8, p = 27 y logp = 5:

Figura 3.33. Simulacin del divisor

La divisin entre x = 335 e y = 927 genera el cociente q = 36138079, que representa

0.36138079 (como x < y, el primer dgito siempre es 0). Al haber definido m = 8, el

cociente est representado por 8 dgitos decimales.

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 47 -

Podemos observar con mayor facilidad en la Figura 3.34 la transicin entre estados, y

vemos como, desde el estado 0 (seal current_state) y dado que la seal start es 0,

pasamos al estado 1 (en caso de que start se hubiera mantenido a 1 como resultado de un

clculo anterior, el sistema esperara a que dicha seal se pusiera a 0).

Figura 3.34. Ampliacin de la Figura 3.33

En el estado 1 y tras detectar un flanco de subida de la seal start, pasamos al estado 2,

donde la unidad de control activa (a 1) la seal load y se escriben los valores iniciales en

los registros. La seal done se pone a 0 indicando que hay una operacin en curso.

Tras un ciclo de reloj pasamos al estado 3 y se inicia el clculo; aqu empieza a funcionar

el contador regresivo (count) de p estados (27 en el ejemplo, de 26 a 0) que determina el

nmero de iteraciones a realizar. Tambin se activa la seal ce que permitir actualizar los

registros. Cuando el contador llegue a 0, dejarn de actualizarse los registros (ce = 0) y se

activar la seal zero informando del fin de clculo (esto se puede ver en la Figura 3.33),

volviendo al estado 0 y ponindose el indicador de operacin realizada done a nivel alto.

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 48 -

3.3 Diseo de la Unidad Aritmtica Decimal (bloque arithmetic_unit.vhd)

El siguiente paso es la definicin de la Unidad Aritmtica Decimal, una estructura que

integre los tres bloques anteriores (Sumador/Restador de n dgitos decimales,

Multiplicador de NxM dgitos BCD y Divisor BCD).

Figura 3.35. Unidad Aritmtica Decimal

Los parmetros genricos del modelo sern:

n: tamao de los operandos (en dgitos decimales) de x e y

p: nmero de etapas de la divisin

logp: nmero de bits necesario para representar p

Este bloque estar controlado por una seal de entrada llamada operation, mediante la cual

se indicar a la unidad la operacin a realizar:

operation Operacin Resultado

00 Suma z = x + y

01 Resta z = x - y

10 Multiplicacin z = x y

11 Divisin z = x / y (con una precisin de 2n dgitos fraccionarios)

Tabla 3.2. Operaciones de la Unidad Aritmtica Decimal

Tanto para la suma como la resta z tendr un tamao de 4n + 1 bits (el bit de mayor peso

corresponde a la seal carry_out del bloque Sumador/Restador), mientras que para la

multiplicacin y divisin el tamao ser de 8n bits.

En la multiplicacin y la divisin el clculo empieza con un flanco de subida de la seal de

entrada start. La bandera done se pone a 0. Una vez disponible el resultado, done tomar

el valor 1.

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 49 -

El diagrama de bloques de la unidad se muestra a continuacin:

8n 8n 4n

z(8n-1:4n) done

done1 done2

1

s1 s2 s3

c_out

Sumador/Restador

n dgitos BCD

Multiplicador de

NxM dgitos BCD

Divisor de n

dgitos BCD

4n

clk

reset

clk

reset

4n 4n 4n 4n 4n

operation

0

operation

1

start

carry_out add_sub

x(4n-1:0)

y(4n-1:0)

start1 start2

00 01 10 11

z(4n-1:0)

operation

4n

MUX-1

00 01 10 11

4n

MUX-2

00 01 10 11

4n

MUX-3

Figura 3.36. Diagrama de bloques de la Unidad Aritmtica Decimal

De cara a la implementacin en la FPGA, el operando y del Multiplicador de NxM dgitos

decimales pasar de estar formado por m dgitos a estarlo por n (podemos decir que ahora

el bloque es un Multiplicador de n dgitos decimales) De esta manera unificamos los

valores de entrada, que siempre estarn formados por n dgitos decimales.

Utilizaremos el bit de menor peso de la seal operation para indicar al Sumador/Restador

la operacin a realizar (entrada add_sub de ste).

Para habilitar el bloque multiplicador utilizaremos la seal start1, que es la salida de una

puerta AND de tres entradas (los dos bits de operation, con el de menor peso negado, y

start). Para el divisor utilizaremos start2, resultado de una puerta AND tambin de tres

entradas, pero esta vez sin negar el bit de menos peso de operation.

Figura 3.37. Circuito generador de las seales start1 y start2

Diseo sobre FPGA de una Unidad Aritmtica Decimal Memoria descriptiva

- 50 -

La salida del primer multiplexor (MUX-1) muestra el resultado de las operaciones suma

(operation = 00) o resta (operation = 01), y la parte baja del resultado de las

operaciones multiplicacin (operation = 10) o divisin (operation = 11), que sera

z(4n-1:0).

El segundo multiplexor recibe a travs de sus dos primeros canales el valor de la seal

carry_out del Sumador/Restador (llamada c_out). Como este valor ocupa 1 solo bit, los

otros bits del dgito de menos peso sern 0 (el dgito de menor peso, 4n+3:4n, estar

formado por 0 0 0 c_out); los dems dgitos (8n-1:4n+4) sern 0. Para la multiplicacin y

la divisin mostrar la parte alta del resultado, los dgitos de mayor peso (8n-1:4n).

MUX-3 muestra el valor actual de la seal done, que estar a nivel alto excepto cuando se

realice el clculo de la multiplicacin o de la divisin (periodo en que la seal se pondr a

nivel bajo, debido a que done1 o done2 tomarn este valor).

A continuacin se muestra una simulacin del sistema con los parmetros n = 8 y p = 56

(en consecuencia logp = 6), para las diferentes operaciones: