Documente Academic

Documente Profesional

Documente Cultură

74HC373

Încărcat de

jnax101Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

74HC373

Încărcat de

jnax101Drepturi de autor:

Formate disponibile

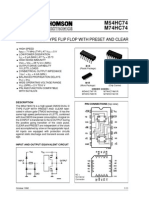

M54/74HC373

M54/74HC533

October 1993

HC373 NON INVERTING - HC533 INVERTING

OCTAL D-TYPE LATCH WITH3 STATE OUTPUT

B1R

(Plastic Package)

ORDER CODES :

M54HCXXXF1R M74HCXXXM1R

M74HCXXXB1R M74HCXXXC1R

F1R

(Ceramic Package)

M1R

(Micro Package)

C1R

(Chip Carrier)

PIN CONNECTION (top view)

.HIGH SPEED

t

PD

= 11 ns (TYP.) AT V

CC

= 5 V

.LOWPOWER DISSIPATION

ICC = 4 A(MAX.) AT TA = 25 C

.HIGH NOISEIMMUNITY

V

NIH

= V

NIL

= 28 % V

CC

(MIN.)

.OUTPUT DRIVE CAPABILITY

15 LSTTL LOADS

.SYMMETRICAL OUTPUT IMPEDANCE

I

OL

= IOH= 6 mA (MIN.)

.BALANCEDPROPAGATION DELAYS

tPLH = tPHL

.WIDE OPERATING VOLTAGE RANGE

V

CC

(OPR) = 2 V TO6 V

.PIN ANDFUNCTION COMPATIBLE

WITH 54/74LS373/533

DESCRIPTION

The M54/74HC373/533 are high speed CMOS

OCTAL LATCH WITH 3-STATE OUTPUTS

fabricated with in silicon gate C

2

MOS technology.

These ICs achive the high speed operation similar

to equivalent LSTTL while maintaning the CMOS

low power dissipation.

These 8 bit D-Type latches are controlled by a latch

enable input (LE) and a output enable input (OE).

While the LE input is held at a high level, the Q

outputs will follow the data input precisely or

inversely. When the LE is taken low, the Q outputs

will be latched precisely or inversely at thelogic level

of D input data. While the OE input is at low level,

the eight outputs will be in a normal logic state (high

or low logic level) and while high level the outpts will

be in a high impedance state.

The application designer has a choise of

combination of inverting and non inverting outputs.

The three state output configuration and the wide

choise of outline make bus organized system

simple.

All inputs are equipped with protection circuits

against discharge and transient excess voltage.

HC373 HC533 HC373 HC533

1/13

INPUT AND OUTPUT EQUIVALENT CIRCUIT

PIN DESCRIPTION (HC373)

PIN No SYMBOL NAME AND FUNCTION

1 OE 3 State output Enable

Input (Active LOW)

2, 5, 6, 9,

12, 15, 16,

19

Q0 to Q7 3 State outputs

3, 4, 7, 8,

13, 14, 17,

18

D0 to D7 Data Inputs

11 LE Latch Enable Input

10 GND Ground (0V)

20 V

CC

Positive Supply Voltage

PIN DESCRIPTION (HC533)

PIN No SYMBOL NAME AND FUNCTION

1 OE 3 State output Enable

Input (Active LOW)

2, 5, 6, 9,

12, 15, 16,

19

Q0 to Q7 3 State outputs

3, 4, 7, 8,

13, 14, 17,

18

D0 to D7 Data Inputs

11 LE Latch Enable Input

10 GND Ground (0V)

20 V

CC

Positive Supply Voltage

IEC LOGIC SYMBOLS

HC373 HC533

M54/M74HC373/533

2/13

TRUTH TABLE

INPUTS OUTPUTS

OE LE D Q (HC373) Q (HC533)

H X X Z Z

L L X NO CHANGE * NO CHANGE *

L H L L H

L H H H L

X: DONT CARE

Z: HIGH IMPEDANCE

*: Q/QOUTPUTS ARELATCHED AT THE TIME WHENTHE LE INPUTIS TAKEN LOWLOGIC LEVEL.

LOGIC DIAGRAMS

HC373

HC533

M54/M74HC373/533

3/13

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

VCC Supply Voltage -0.5 to +7 V

V

I

DC Input Voltage -0.5 to V

CC

+ 0.5 V

VO DC Output Voltage -0.5 to VCC + 0.5 V

IIK DC Input Diode Current 20 mA

I

OK

DC Output Diode Current 20 mA

IO DC Output Source Sink Current Per Output Pin 35 mA

ICC or IGND DC VCC or Ground Current 70 mA

P

D

Power Dissipation 500 (*) mW

Tstg Storage Temperature -65 to +150

o

C

T

L

Lead Temperature (10 sec) 300

o

C

AbsoluteMaximum Ratingsarethosevalues beyond whichdamage tothedevicemayoccur. Functional operation under theseconditions is not implied.

(*) 500 mW: 65

o

C derate to 300 mWby 10mW/

o

C: 65

o

C to85

o

C

RECOMMENDED OPERATING CONDITIONS

Symbol Parameter Value Unit

V

CC

Supply Voltage 2 to 6 V

V

I

Input Voltage 0 to V

CC

V

VO Output Voltage 0 to VCC V

T

op

Operating Temperature: M54HC Series

M74HC Series

-55 to +125

-40 to +85

o

C

o

C

t

r

, t

f

Input Rise and Fall Time V

CC

= 2 V 0 to 1000 ns

VCC = 4.5 V 0 to 500

VCC = 6 V 0 to 400

M54/M74HC373/533

4/13

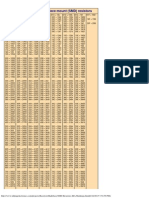

DC SPECIFICATIONS

Symbol Parameter

Test Conditions Value

Unit

VCC

(V)

TA = 25

o

C

54HC and 74HC

-40 to 85

o

C

74HC

-55 to 125

o

C

54HC

Min. Typ. Max. Min. Max. Min. Max.

V

IH

High Level Input

Voltage

2.0 1.5 1.5 1.5

V

4.5 3.15 3.15 3.15

6.0 4.2 4.2 4.2

V

IL

Low Level Input

Voltage

2.0 0.5 0.5 0.5

V

4.5 1.35 1.35 1.35

6.0 1.8 1.8 1.8

VOH High Level

Output Voltage

2.0

VI =

V

IH

or

V

IL

I

O

=-20 A

1.9 2.0 1.9 1.9

V

4.5 4.4 4.5 4.4 4.4

6.0 5.9 6.0 5.9 5.9

4.5 IO=-6.0 mA 4.18 4.31 4.13 4.10

6.0 IO=-7.8 mA 5.68 5.8 5.63 5.60

V

OL

Low Level Output

Voltage

2.0

V

I

=

V

IH

or

VIL

I

O

= 20 A

0.0 0.1 0.1 0.1

V

4.5 0.0 0.1 0.1 0.1

6.0 0.0 0.1 0.1 0.1

4.5 I

O

= 6.0 mA 0.17 0.26 0.33 0.40

6.0 IO= 7.8 mA 0.18 0.26 0.33 0.40

II Input Leakage

Current

6.0

VI = VCC or GND 0.1 1 1 A

I

OZ

3 State Output

Off State Current

6.0 V

I

= V

IH

or V

IL

VO = VCC or GND

0.5 5.0 10 A

I

CC

Quiescent Supply

Current

6.0 V

I

= V

CC

or GND 4 40 80 A

M54/M74HC373/533

5/13

AC ELECTRICAL CHARACTERISTICS (CL = 50 pF, Input tr = tf = 6 ns)

Symbol Parameter

Test Conditions Value

Unit

VCC

(V)

CL

(pF)

TA = 25

o

C

54HC and 74HC

-40 to 85

o

C

74HC

-55 to 125

o

C

54HC

Min. Typ. Max. Min. Max. Min. Max.

t

TLH

t

THL

Output Transition

Time

2.0

50

25 60 75 90

ns

4.5 7 12 15 18

6.0 6 10 13 15

t

PLH

tPHL

Propagation

Delay Time

(LE, D - Q, Q)

2.0

50

42 125 155 190

ns

4.5 14 25 31 38

6.0 12 21 26 32

2.0

150

57 175 220 265

ns

4.5 19 35 44 53

6.0 16 30 37 45

t

PZL

t

PZH

3 State Output

Enable Time

2.0

50 R

L

= 1 K

39 125 155 190

ns

4.5 13 25 31 38

6.0 11 21 26 32

2.0

150 R

L

= 1 K

54 175 220 265

ns

4.5 18 35 44 53

6.0 15 30 37 45

tPLZ

tPHZ

3 State Output

Disable Time

2.0

50 RL = 1 K

30 125 155 190

ns

4.5 14 25 31 38

6.0 13 21 26 32

tW(H) Minimum Pulse

Width (LE)

2.0

50

15 75 95 110

ns

4.5 6 15 19 22

6.0 6 13 16 19

t

s

Minimum Set-up

Time

2.0

50

16 50 65 75

ns

4.5 4 10 13 15

6.0 3 9 11 13

t

h

Minimum Hold

Time

2.0

50

5 5 5

ns

4.5 5 5 5

6.0 5 5 5

CIN Input Capacitance 5 10 10 10 pF

C

OUT

Out put

Capacitance

10

pF

C

PD

(*) Power Dissipation

Capacitance

38

pF

(*) CPD is defined as the value of the ICsinternal equivalent capacitance which is calculated from the operating current consumption without load.

(Refer to Test Circuit). Average operting current can be obtained by the following equation. ICC(opr) = CPD VCC fIN + ICC/8 (per FlipFlop) and the

CPDwhen n pcs of Flip Flop operate, can be gained by following equation: CPD(TOTAL) = 22 + 16 x n [pF]

M54/M74HC373/533

6/13

SWITCHING CHARACTERISTICS TEST WAVEFORM

tPLZ, tPZL

The 1K load resistors should be connected between

outputs and V

CC

line and the 50pF load capacitors

should be connected between outputsand GND line.

All inputs except OE input should be connected to VCC

line or GND line such that outputs will be in low logic

level while OE input is held low.

tPHZ, tPZH

The 1K load resistors and the 50pF load capacitors

should be connected between each output and GND

line.

All inputs except OE input should be connected to VCC

or GND line such that output will be in high logic level

while OE input is held low.

tPLH, tPHL, (D - Q, Q) tPLH, tPHL (LE - Q, Q), ts, th, tW

M54/M74HC373/533

7/13

TEST CIRCUIT I

CC

(Opr.)

INPUTWAVEFORM IS THE SAMEAS THAT IN CASE OF SWITCHINGCHARACTERISTICSTEST.

M54/M74HC373/533

8/13

Plastic DIP20 (0.25) MECHANICAL DATA

DIM.

mm inch

MIN. TYP. MAX. MIN. TYP. MAX.

a1 0.254 0.010

B 1.39 1.65 0.055 0.065

b 0.45 0.018

b1 0.25 0.010

D 25.4 1.000

E 8.5 0.335

e 2.54 0.100

e3 22.86 0.900

F 7.1 0.280

I 3.93 0.155

L 3.3 0.130

Z 1.34 0.053

P001J

M54/M74HC373/533

9/13

Ceramic DIP20 MECHANICAL DATA

DIM.

mm inch

MIN. TYP. MAX. MIN. TYP. MAX.

A 25 0.984

B 7.8 0.307

D 3.3 0.130

E 0.5 1.78 0.020 0.070

e3 22.86 0.900

F 2.29 2.79 0.090 0.110

G 0.4 0.55 0.016 0.022

I 1.27 1.52 0.050 0.060

L 0.22 0.31 0.009 0.012

M 0.51 1.27 0.020 0.050

N1 4 (min.), 15 (max.)

P 7.9 8.13 0.311 0.320

Q 5.71 0.225

P057H

M54/M74HC373/533

10/13

SO20 MECHANICAL DATA

DIM.

mm inch

MIN. TYP. MAX. MIN. TYP. MAX.

A 2.65 0.104

a1 0.10 0.20 0.004 0.007

a2 2.45 0.096

b 0.35 0.49 0.013 0.019

b1 0.23 0.32 0.009 0.012

C 0.50 0.020

c1 45 (typ.)

D 12.60 13.00 0.496 0.512

E 10.00 10.65 0.393 0.419

e 1.27 0.050

e3 11.43 0.450

F 7.40 7.60 0.291 0.299

L 0.50 1.27 0.19 0.050

M 0.75 0.029

S 8 (max.)

P013L

M54/M74HC373/533

11/13

PLCC20 MECHANICAL DATA

DIM.

mm inch

MIN. TYP. MAX. MIN. TYP. MAX.

A 9.78 10.03 0.385 0.395

B 8.89 9.04 0.350 0.356

D 4.2 4.57 0.165 0.180

d1 2.54 0.100

d2 0.56 0.022

E 7.37 8.38 0.290 0.330

e 1.27 0.050

e3 5.08 0.200

F 0.38 0.015

G 0.101 0.004

M 1.27 0.050

M1 1.14 0.045

P027A

M54/M74HC373/533

12/13

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsability for the

consequences of use of such information nor for any infringement of patents or other rights of third parties which may results from its use. No

license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specificationsmentioned

in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied.

SGS-THOMSON Microelectronicsproductsare not authorized for use ascritical componentsin life support devices or systems without express

written approval of SGS-THOMSON Microelectonics.

1994 SGS-THOMSON Microelectronics - All Rights Reserved

SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco - The Netherlands -

Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A

M54/M74HC373/533

13/13

S-ar putea să vă placă și

- 74HC374Document13 pagini74HC374jnax101Încă nu există evaluări

- 74HC373Document13 pagini74HC373hugodjacobÎncă nu există evaluări

- 74HC164Document12 pagini74HC164jnax101Încă nu există evaluări

- 74HC74Document11 pagini74HC74jnax101Încă nu există evaluări

- 74HC393Document12 pagini74HC393jnax101Încă nu există evaluări

- 74HC390Document13 pagini74HC390jnax101Încă nu există evaluări

- 74HC4024Document11 pagini74HC4024jnax101Încă nu există evaluări

- 74HC273Document11 pagini74HC273jnax101Încă nu există evaluări

- 74HC175Document11 pagini74HC175jnax101Încă nu există evaluări

- 74HC151Document11 pagini74HC151jnax101Încă nu există evaluări

- 74HC245Document11 pagini74HC245jnax101Încă nu există evaluări

- 74HC139Document9 pagini74HC139jnax101Încă nu există evaluări

- 74HC241Document12 pagini74HC241jnax101Încă nu există evaluări

- 74HC27Document9 pagini74HC27jnax101Încă nu există evaluări

- 74HC193Document15 pagini74HC193jnax101Încă nu există evaluări

- 74HC00Document9 pagini74HC00jnax101Încă nu există evaluări

- Datasheet 7400Document9 paginiDatasheet 7400gab50Încă nu există evaluări

- 74HC4075Document9 pagini74HC4075jnax101Încă nu există evaluări

- 74HC08Document9 pagini74HC08jnax101Încă nu există evaluări

- 74HC266Document11 pagini74HC266jnax101Încă nu există evaluări

- 74HC04Document9 pagini74HC04jnax101Încă nu există evaluări

- 74HC4016Document11 pagini74HC4016jnax101Încă nu există evaluări

- 74HC14Document9 pagini74HC14jnax101Încă nu există evaluări

- 74HC4543Document12 pagini74HC4543jnax101Încă nu există evaluări

- 74HC138Document10 pagini74HC138jnax101Încă nu există evaluări

- Single Bilateral Switch: Order CodesDocument11 paginiSingle Bilateral Switch: Order CodesGaryTechÎncă nu există evaluări

- hc273 PDFDocument11 paginihc273 PDFGustavo NavaÎncă nu există evaluări

- M54HC164 M74HC164: 8 Bit Sipo Shift RegisterDocument12 paginiM54HC164 M74HC164: 8 Bit Sipo Shift RegisterCANTHO91Încă nu există evaluări

- Octal Bus Buffer With 3 State Outputs (Non Inverted) : M B Order CodesDocument8 paginiOctal Bus Buffer With 3 State Outputs (Non Inverted) : M B Order CodesStevenÎncă nu există evaluări

- 74HC4049Document11 pagini74HC4049jnax101Încă nu există evaluări

- 74HC4852 (Driver Injector)Document16 pagini74HC4852 (Driver Injector)el_george0079491Încă nu există evaluări

- M74HC595B1Document13 paginiM74HC595B1GeorgeÎncă nu există evaluări

- Data SheetDocument9 paginiData SheetAmanda VaughnÎncă nu există evaluări

- 7402Document9 pagini7402eredrag07Încă nu există evaluări

- Synchronous Up:Down Binary) Counter - StmicroelectronicsDocument15 paginiSynchronous Up:Down Binary) Counter - StmicroelectronicsMotivated JuneÎncă nu există evaluări

- 74FST3251 8:1 Multiplexer/ Demultiplexer Bus Switch: SOIC 16 D Suffix CASE 751BDocument7 pagini74FST3251 8:1 Multiplexer/ Demultiplexer Bus Switch: SOIC 16 D Suffix CASE 751BRishabh PariharÎncă nu există evaluări

- HCF4094B: 8 Stage Shift and Store Bus Register With 3-State OutputsDocument13 paginiHCF4094B: 8 Stage Shift and Store Bus Register With 3-State Outputsjamesearl_cubillasÎncă nu există evaluări

- 74HC573 Octal LatchDocument13 pagini74HC573 Octal LatchWonzÎncă nu există evaluări

- Datasheet 7408Document9 paginiDatasheet 7408Antony ZiimerÎncă nu există evaluări

- 74HCT157Document12 pagini74HCT157mikimtb100% (1)

- 7 Segment Driver M74HC4543Document10 pagini7 Segment Driver M74HC4543angelozuccoÎncă nu există evaluări

- 7400Document9 pagini7400LotteDomineÎncă nu există evaluări

- Features: Single Bilateral SwitchDocument15 paginiFeatures: Single Bilateral SwitchGaryTechÎncă nu există evaluări

- 74LVC08A: Low Voltage Cmos Quad 2-Input and Gate High PerformanceDocument11 pagini74LVC08A: Low Voltage Cmos Quad 2-Input and Gate High PerformanceFernando QueirozÎncă nu există evaluări

- 7432Document9 pagini7432diralarkÎncă nu există evaluări

- Octal D-Type Latch With 3 State Outputs (Non Inverted) : Order CodesDocument11 paginiOctal D-Type Latch With 3 State Outputs (Non Inverted) : Order CodesIsaacÎncă nu există evaluări

- 74HC107 PDFDocument12 pagini74HC107 PDFVictor CabosÎncă nu există evaluări

- 74147Document10 pagini74147Jay Dimas JayÎncă nu există evaluări

- 74HC05 PDFDocument9 pagini74HC05 PDFHoàng Nam MelÎncă nu există evaluări

- 74138Document10 pagini74138senthur123Încă nu există evaluări

- Datasheet orDocument9 paginiDatasheet orM Mustafa GözüküçükÎncă nu există evaluări

- Low Voltage Cmos Dual 2 To 4 Decoder/Demultiplexer: Table 1: Order CodesDocument13 paginiLow Voltage Cmos Dual 2 To 4 Decoder/Demultiplexer: Table 1: Order CodesMohammad SoltanmohammadiÎncă nu există evaluări

- 8 Bit Shift Register With Output Latches (3 State) : Order CodesDocument16 pagini8 Bit Shift Register With Output Latches (3 State) : Order CodesQuyet Pham DangÎncă nu există evaluări

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDe la EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsÎncă nu există evaluări

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1De la EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Evaluare: 4.5 din 5 stele4.5/5 (3)

- 110 Waveform Generator Projects for the Home ConstructorDe la Everand110 Waveform Generator Projects for the Home ConstructorEvaluare: 4 din 5 stele4/5 (1)

- Box ExampleDocument6 paginiBox Examplejnax101Încă nu există evaluări

- Artwork SpecificationDocument4 paginiArtwork Specificationjnax101Încă nu există evaluări

- Classd Digital Amplifier TutorialDocument54 paginiClassd Digital Amplifier TutorialemerychÎncă nu există evaluări

- SG 3524Document3 paginiSG 3524florianosÎncă nu există evaluări

- Electronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment RequiredDocument1 paginăElectronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment Requiredjnax101Încă nu există evaluări

- 28701-En LZT14606 en A PDFV1R2Document3 pagini28701-En LZT14606 en A PDFV1R2jnax101Încă nu există evaluări

- Transistor NPN 2n222aDocument8 paginiTransistor NPN 2n222aRoberto Eduardo Tenorio RamosÎncă nu există evaluări

- Applications Using The SG3524: Integrated CircuitsDocument3 paginiApplications Using The SG3524: Integrated Circuitsjnax101Încă nu există evaluări

- SG 3524Document15 paginiSG 3524jnax101Încă nu există evaluări

- SG3524 Application NotesDocument6 paginiSG3524 Application NotesSANDEEP KUMAR RAHEJAÎncă nu există evaluări

- MC 14093Document8 paginiMC 14093rrebollarÎncă nu există evaluări

- Electronics 1 Practical 6: Equipment RequiredDocument1 paginăElectronics 1 Practical 6: Equipment Requiredjnax101Încă nu există evaluări

- Data Sheet IC LM 723Document13 paginiData Sheet IC LM 723Wahyu Sulistyo NugrohoÎncă nu există evaluări

- Elt 1 Practical 1.WpdDocument1 paginăElt 1 Practical 1.Wpdjnax101Încă nu există evaluări

- Electronics 1 Practical 3 Circuit WaveformsDocument2 paginiElectronics 1 Practical 3 Circuit Waveformsjnax101Încă nu există evaluări

- Max 1642Document12 paginiMax 1642jnax101Încă nu există evaluări

- Electronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment RequiredDocument1 paginăElectronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment Requiredjnax101Încă nu există evaluări

- ELT 1 Prac 4Document2 paginiELT 1 Prac 4jnax101Încă nu există evaluări

- MAX608Document12 paginiMAX608jnax101Încă nu există evaluări

- LM2524D/LM3524D Regulating Pulse Width Modulator: General DescriptionDocument22 paginiLM2524D/LM3524D Regulating Pulse Width Modulator: General DescriptionrutayanpÎncă nu există evaluări

- LM337Document12 paginiLM337jnax101Încă nu există evaluări

- LM78XX Series Voltage Regulators: General DescriptionDocument6 paginiLM78XX Series Voltage Regulators: General DescriptiondebabratalogonÎncă nu există evaluări

- LM317Document22 paginiLM317jnax101Încă nu există evaluări

- MAX606Document12 paginiMAX606jnax101Încă nu există evaluări

- LM393Document15 paginiLM393Izabela AlcântaraÎncă nu există evaluări

- Max 1672Document12 paginiMax 1672jnax101Încă nu există evaluări

- MAX619Document7 paginiMAX619jnax101Încă nu există evaluări

- Max 1674Document12 paginiMax 1674jnax101Încă nu există evaluări

- Max 1672Document12 paginiMax 1672jnax101Încă nu există evaluări

- Max 1686Document4 paginiMax 1686jnax101Încă nu există evaluări

- CD4093BM/CD4093BC Quad 2-Input NAND Schmitt Trigger: General DescriptionDocument6 paginiCD4093BM/CD4093BC Quad 2-Input NAND Schmitt Trigger: General DescriptionCristian MorenoÎncă nu există evaluări

- 1 - Memory Unit - Flip-Flops (DLP-2021-22)Document15 pagini1 - Memory Unit - Flip-Flops (DLP-2021-22)SohneaÎncă nu există evaluări

- Stallings Computer Organization and Architecture Chapter 7 Input OutputDocument36 paginiStallings Computer Organization and Architecture Chapter 7 Input OutputZersh EthioÎncă nu există evaluări

- Digital Systems Design: Basics of Asynchronous LogicDocument34 paginiDigital Systems Design: Basics of Asynchronous LogicZartasha MalikÎncă nu există evaluări

- Allen Slides 03 Cmos Models PDFDocument82 paginiAllen Slides 03 Cmos Models PDFAngelino PimentelÎncă nu există evaluări

- HDILayer StackupsDocument17 paginiHDILayer StackupsAnthonyÎncă nu există evaluări

- From RTL To GDS Using Synopsys Flow Within Less Then 10 WeeksDocument15 paginiFrom RTL To GDS Using Synopsys Flow Within Less Then 10 WeeksLohitÎncă nu există evaluări

- CD4000 LibDocument33 paginiCD4000 LibFernando Sobrino-Manzanares MasÎncă nu există evaluări

- Digital and Logic Design Lab-8 Revision LabDocument4 paginiDigital and Logic Design Lab-8 Revision Labprince12Încă nu există evaluări

- Flip-Flop Introduction To SR Flip FlopDocument22 paginiFlip-Flop Introduction To SR Flip FlopljjbÎncă nu există evaluări

- Digital FundamentalsDocument28 paginiDigital Fundamentalsbadhell_18100% (2)

- VLSI Subsystem Design GuideDocument114 paginiVLSI Subsystem Design Guidekotamraju sriindraniÎncă nu există evaluări

- MT7636 DS-EN - Rev1.30Document9 paginiMT7636 DS-EN - Rev1.30Vishal dtuÎncă nu există evaluări

- Mos Transistor: GS DSDocument2 paginiMos Transistor: GS DSHimanshu SahuÎncă nu există evaluări

- Data Path Design (Adder and Multiplier)Document76 paginiData Path Design (Adder and Multiplier)Karthik RamasamyÎncă nu există evaluări

- CD54HC297, CD74HC297, CD74HCT297: Features DescriptionDocument15 paginiCD54HC297, CD74HC297, CD74HCT297: Features DescriptioncgmannerheimÎncă nu există evaluări

- VHDL Code For 4-Bit Shift RegisterDocument17 paginiVHDL Code For 4-Bit Shift RegisterAnónimo AnónimoÎncă nu există evaluări

- Digital Design Lab Manual: Introduction To VerilogDocument48 paginiDigital Design Lab Manual: Introduction To VerilogKeith FernandesÎncă nu există evaluări

- Cpe G4Document13 paginiCpe G4tarvsÎncă nu există evaluări

- SMD Resistor CodesDocument2 paginiSMD Resistor CodesJason Lewis50% (2)

- ALU, Data Path and Control UnitDocument24 paginiALU, Data Path and Control UnitTanisha Jauhari 21BCE3566Încă nu există evaluări

- CC0801A CC0801A Xinhope Electronic Co.,Ltd Xinhope Electronic Co.,LtdDocument39 paginiCC0801A CC0801A Xinhope Electronic Co.,Ltd Xinhope Electronic Co.,LtdSanjay BarewarÎncă nu există evaluări

- Experiment 2 FinalDocument9 paginiExperiment 2 Finalliddleme33Încă nu există evaluări

- Aditya Engineering College (A) : Digital Circuits and Logic Design Synchronous CountersDocument13 paginiAditya Engineering College (A) : Digital Circuits and Logic Design Synchronous CounterskalaÎncă nu există evaluări

- 2023 Ch4-Elmore DelayDocument38 pagini2023 Ch4-Elmore DelayĐạt NguyễnÎncă nu există evaluări

- Interfacing I2C-EEPROM With LPC2148: Arm How-To GuideDocument20 paginiInterfacing I2C-EEPROM With LPC2148: Arm How-To GuideShiva SagarÎncă nu există evaluări

- Engineering Lecture1:: Logic Circuits & Concepts About Basic Electrical Engineering DevicesDocument17 paginiEngineering Lecture1:: Logic Circuits & Concepts About Basic Electrical Engineering DevicessanthoshyeruvakaÎncă nu există evaluări

- DFT DocumentationDocument20 paginiDFT Documentationyamini100% (1)

- ECE VLSI Design Course SyllabusDocument7 paginiECE VLSI Design Course SyllabusDsce CoimbatoreÎncă nu există evaluări

- 1HDocument8 pagini1HSandipChowdhuryÎncă nu există evaluări