Documente Academic

Documente Profesional

Documente Cultură

Microelectronics Group IITB

Încărcat de

kbkkr0 evaluări0% au considerat acest document util (0 voturi)

94 vizualizări36 paginiThe document describes the Microelectronics and VLSI group within the Department of Electrical Engineering at the Indian Institute of Technology Bombay. It provides details about the group's research areas, facilities, projects, publications, collaborations with industry and academia, and educational programs at the institution. The group has over 100 post-graduate students and 12 core faculty members working on areas like VLSI design, device modeling, MEMS, and new materials. It has received over $8 million in sponsored projects and has partnerships with companies like Intel, Motorola, and Siemens.

Descriere originală:

description

Drepturi de autor

© © All Rights Reserved

Formate disponibile

PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentThe document describes the Microelectronics and VLSI group within the Department of Electrical Engineering at the Indian Institute of Technology Bombay. It provides details about the group's research areas, facilities, projects, publications, collaborations with industry and academia, and educational programs at the institution. The group has over 100 post-graduate students and 12 core faculty members working on areas like VLSI design, device modeling, MEMS, and new materials. It has received over $8 million in sponsored projects and has partnerships with companies like Intel, Motorola, and Siemens.

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

94 vizualizări36 paginiMicroelectronics Group IITB

Încărcat de

kbkkrThe document describes the Microelectronics and VLSI group within the Department of Electrical Engineering at the Indian Institute of Technology Bombay. It provides details about the group's research areas, facilities, projects, publications, collaborations with industry and academia, and educational programs at the institution. The group has over 100 post-graduate students and 12 core faculty members working on areas like VLSI design, device modeling, MEMS, and new materials. It has received over $8 million in sponsored projects and has partnerships with companies like Intel, Motorola, and Siemens.

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 36

Department of Electrical Engineering

Indian Institute of Technology, Bombay

2003

IIT Bombay is one of 7 IITs in India, and the

oldest but one

Located on a 250 hectare campus on the

shores of Powai lake

About 400 faculty and 5000 students

More than half of the students are post-

graduate students

26 major Departments, Schools and Centres,

plus 6 inter-disciplinary programmes

The largest Department at IIT Bombay

About 40 faculty and 600 students

Major research and teaching areas

Communications & Signal Processing

Power Electronics & Power Systems

Electronic Systems

Control & Computing

Microelectronics & VLSI

Microelectronics & VLSI is the largest

group in EE Department at IIT Bombay

Started in 1984; Group activity

emphasized

Main thrust in silicon CMOS devices,

technology and design

Group consists of 12 core faculty and

110 post-graduate students

R. Parekhji*

M. B. Patil

R. Pinto

V. Ramgopal Rao

D. K. Sharma

S. D. Sherlekar*

J. Vasi

*Adjunct

P. R. Apte

A. N. Chandorkar

M. P. Desai

S. Duttagupta

B. Gadepally*

R. Lal

S. Mahapatra

H. Narayanan

A. Karandikar Communications

D. Manjunath Communications

V. Gadre Communications

Girish Kumar Communications

Girish Saraph Communications

R.K. Shevgaonkar Communications

P.C. Pandey Electronic Systems

S. S. S. P. Rao Comp. Sci. & Engg.

S. Chakrabarty Comp. Sci. & Engg.

M. Sohoni Comp. Sci. & Engg.

S. Patkar Maths

R. O. Dusane Met. Eng. & Mat. Sci.

R. Srinivasa Met. Eng. & Mat. Sci.

A. Contractor Chemistry

M. Ravikanth Chemistry

S. Mukherji Bio-medical

Ph.D. (graduating ~ 3 - 5 / year)

M.Tech. with specialization in

Microelectronics (~ 35 / year)

Dual Degree (B.Tech. + M.Tech.)

with specialization in Microelectronics

(~ 20 / year)

B.Tech. (~ 50 / year, ~ 15 / year with

projects in Micro-electronics)

Silicon CMOS physics and technology

MEMS, BioMEMS

New materials

Device modeling and simulation

VLSI design (digital, analog, mixed-mode, RF)

VLSI CAD tool development

Interaction between VLSI technology and

design

Class 1000 Clean Room (class 100 work areas) with facilities

for complete IC manufacturing (optical & EB lithography,

RIE, Deposition, Sputter, RTP, Furnace facilities)

MEMS fabrication

Excellent characterization facility

SEM; photoluminescence

VLSI design workstations

VLSI design tools

Cadence, Mentor, Synopsys, Tanner, Xilinx, plus many

public domain tools

Simulation workstations

Simulation software

Medici, TSuprem, ISE-TCAD, SMC (Monte Carlo)

Gaitonde Integrated Systems Laboratory

Intel Microelectronics Lab

TCS VLSI Design Lab

Over 60 projects since 1985 totaling

US$ 8 Million

Projects cover all areas of

Microelectronics & VLSI

Projects from major government

agencies, and leading Indian &

international companies

Silicon sensors for electroporation (Praman

Technology)

BioMEMS sensors for cardiac applications (ADA)

Silicon Locket (TCS)

Channel engineering for 100 nm CMOS devices

(DST)

Characterization of vertical MOS transistors

(Siemens)

Design and characterization of Flash memories

(Hitachi)

Development of a hot-carrier simulator

(Motorola)

Look-up table modeling for circuit simulation

(DST)

Modeling of power semiconductor devices (GE)

Macromodels for circuit simulation (National)

RF MOSFET models (IME, Singapore)

Oxide scaling effects on design issues (Intel)

CMOS device design and optimization for mixed-

signal applications (Intel)

Interconnect capacitance extraction by Monte

Carlo (Intel)

Eigenvalues for large scale systems (NRB)

Math programming & electrical networks (DST)

General purpose systems partitioners (NRB)

Design issues with high-k dielectrics (Intel)

Analog PHY interface chip (ControlNet)

Data Conversion & RF Circuits (Texas Instruments

India)

High-speed comparator design (TII)

Communication VLSI Design (SASKEN)

Packet classifier (Switch-on Networks)

FSM-based packet router (DST)

On-chip coupling capacitance measurement

(MHRD)

VLSI Design training (MIT, TCS)

Design of RF Tuner for Cable Modem Applications: V.Babu, S.

Seth and A.N. Chandorkar won the best paper award at VLSI-

2004

A new Approach to Model Nonquasi-static (NQS) Effects For

MOSFETS A.S. Roy, J.M. Vasi and M.B. Patil, IEEE transactions

on Electron Devices, ED-50, 2401 (2003)

Dual Channel RF receiver design A Krishnakanth, D. K.

Sharma 6

th

International Symposium on Wireless Multimedia

communications WPMC 03, Yokosuka, Kanagawa, Japan, Dec

2003

Linearization of RF Power Amplifiers A. Kotwal, A.N.

Chandorkar (M.Tech. Project)

Power optimal RF data transfer for mobile heart monitoring

N. Nagaraju, S. Gupta, R. Lal, D.K. Sharma (3 M.Tech. Projects

in progress)

S. Vaidya: Neutron radiation effects in MOS systems

J. Meckie: Asynchronous design issues

G. Trivedi: Parallel algorithms for VLSI optimization

N. Mahapatra: High-k dielectrics for 100 nm CMOS

A. Shastry: Microcapillary electrophoresis on silicon

C.A. Betty: Capacitive immunosensor on porous Si

B. Anand: Digital design with dynamic threshold CMOS

D. Nair: Flash memory design and reliability

D.V.Kumar: Look-up table approach for CMOS circuits

K. Narasimhulu: CMOS devices for mixed-signal design

Sponsored, Consultancy & Collaborative Projects

Indian industry: SCL, BEL, ITI, TCS, Sasken, TII, Cypress,

ControlNet, National, etc

International industry: Intel, Motorola, GE, Siemens, Hitachi,

National, IME, Agere

Industry sponsorship of students

M.Tech. & Dual Degree students

Ph.D. students

Endowed Laboratories

Gaitonde Integrated Systems Laboratory

Intel Microelectronics Laboratory

TCS VLSI Design & Characterization Laboratory

Continuing Education Programs for industry

Research Collaborations

Other IITs, IISc, Universities of Bombay, Pune

International universities like

UCLA, UCSB, Yale University (USA)

Hong Kong University of Science & Tech. (HK)

Delft University (The Netherlands)

University of Bundeswehr (Germany)

Griffith University (Australia)

NUS, NTU (Singapore)

Student Exchanges

Intel Laboratory

Intel Sponsored Research

Intel Sponsorship for Students

Intel Sponsored Ph.D. Students

Nihar Mohapatra: Device and Circuit

Performance Trade-offs with the Use of High-K

Dielectrics in Sub-100 nm CMOS Technologies

(Graduated in Jan 2004)

D. Vinay Kumar: Gate Oxide thickness Scaling

in Sub-100 nm MOSFETS and its Effect on

Circuit Performance

K. Narasimhulu + 1 student: Impact of Device

Scaling on Mixed-Signal CMOS Circuits

Intel@IIT Intel@IIT- -B B

Publications by Intel Sponsored Ph.D. Students

International Journals:

Intel@IIT Intel@IIT- -B B

International Conferences:

.

Undertaken projects of national importance (over

US $8 Million in the last 15 years) and

successfully transferred technologies to

industries

Close industry interaction

Publish over 30 research papers every year in

reputed international journals and conferences

IEEE Electron Device Letters

IEEE

Transactions on Electron Devices

, IEEE Electron Device Letters

IEEE Transactions on Electron

Devices

IEEE Transactions on Electron Devices

IEEE Transactions on Electron Devices

IEEE

Trans. Electron Devices 51 (

IEEE

Trans. Electron Devices 51

Groups publications in the area of Electron Devices in the last few

months in IEEE Trans. On Electron Devices/IEEE Electron Device Letters

Over 200 publications in the last 5 years

in major journals and conferences

Cover all areas of interest

Details at www.ee.iitb.ac.in/ ~microel/

Most active Microelectronics & VLSI group in

India (publications, sponsored projects,

students, facilities)

Excellent research facilities

Projects of national importance

Projects from Indian & international industry

Major teaching programs at all levels

High international visibility (Editorial boards,

IEEE AdCom, reviews, conference

committees. etc.)

Microelectronics Group

Department of Electrical Engineering

Indian Institute of Technology, Bombay

Powai

Mumbai 400076 India

Phone: +91-22-2572-3655

Fax: +91-22-2572-3480

email: me@ee.iitb.ac.in

website: www.iitb.ac.in/~microel/

S-ar putea să vă placă și

- EE Department, I.I.T Bombay + IsroDocument45 paginiEE Department, I.I.T Bombay + IsroNishant AgrawalÎncă nu există evaluări

- Advanced CMOSDocument9 paginiAdvanced CMOSamitgh88Încă nu există evaluări

- IEEE MTT-S International Microwave and RF Conference: First Call For PapersDocument1 paginăIEEE MTT-S International Microwave and RF Conference: First Call For PapersPriyanka ChoudharyÎncă nu există evaluări

- Vlsi System DesignDocument29 paginiVlsi System DesignAmar KumarÎncă nu există evaluări

- Anurag Kumar CVDocument22 paginiAnurag Kumar CVSv NikhilÎncă nu există evaluări

- Overview of Nano Electronics 1Document11 paginiOverview of Nano Electronics 1VishNu Teja GÎncă nu există evaluări

- Khalid Ali S Ammar - CVDocument5 paginiKhalid Ali S Ammar - CVSaleem JayousiÎncă nu există evaluări

- ECSEDocument71 paginiECSEwidepermitÎncă nu există evaluări

- Research Profile 2019 PDFDocument7 paginiResearch Profile 2019 PDFMd. Ashikur RahmanÎncă nu există evaluări

- MS in Embedded Systems and IOTsDocument8 paginiMS in Embedded Systems and IOTsSamir KingaÎncă nu există evaluări

- International Journal of Microelectronics Engineering (IJME)Document2 paginiInternational Journal of Microelectronics Engineering (IJME)Anonymous rVWvjCRLGÎncă nu există evaluări

- IEEE FINAL BROCHURE DSG2 LightDocument6 paginiIEEE FINAL BROCHURE DSG2 LightBalaÎncă nu există evaluări

- 01-Intro MEMS History TrendsDocument19 pagini01-Intro MEMS History TrendscmosÎncă nu există evaluări

- Resume and Critique - Catherine KociaDocument6 paginiResume and Critique - Catherine Kociaapi-140137201Încă nu există evaluări

- EE405 LecturesDocument202 paginiEE405 LecturesAbdoooÎncă nu există evaluări

- CV Hemant Jan 09Document3 paginiCV Hemant Jan 09Aniket TakleÎncă nu există evaluări

- Benefits of IEEE Membership-PresentationDocument13 paginiBenefits of IEEE Membership-PresentationCh Srinivasa ReddyÎncă nu există evaluări

- 2023 Cfp-Dat FinalDocument1 pagină2023 Cfp-Dat FinalsyaleafÎncă nu există evaluări

- Call 4 Papers Iscas 2018Document1 paginăCall 4 Papers Iscas 2018Renga PradeepÎncă nu există evaluări

- Present and Future Prospects of Semiconductor IndustryDocument60 paginiPresent and Future Prospects of Semiconductor IndustrySuneetha MathukumalliÎncă nu există evaluări

- Semester 1: 1. Course Structure and Scheme of Evaluation (Semester-Wise, Along With Curriculum Details)Document19 paginiSemester 1: 1. Course Structure and Scheme of Evaluation (Semester-Wise, Along With Curriculum Details)Sneha NargundkarÎncă nu există evaluări

- Ntwrking Acad Sem 1v21Document12 paginiNtwrking Acad Sem 1v21Edinilza LimaÎncă nu există evaluări

- Digital Adder Circuits: A Review of Power, Delay, Area, and Transistor CountDocument15 paginiDigital Adder Circuits: A Review of Power, Delay, Area, and Transistor CountDeepak SharmaÎncă nu există evaluări

- Lectures 1: Review of Technology Trends and Cost/PerformanceDocument53 paginiLectures 1: Review of Technology Trends and Cost/PerformanceNeeraj SharmaÎncă nu există evaluări

- Mvlsi 04Document26 paginiMvlsi 04gudiya90_pvÎncă nu există evaluări

- Aman Goel: Ee11b087@ee - Iitm.ac - in WWW - Ee.iitm - Ac.in/ Ee11b087Document4 paginiAman Goel: Ee11b087@ee - Iitm.ac - in WWW - Ee.iitm - Ac.in/ Ee11b087pussyÎncă nu există evaluări

- CV #2 Abhinav Agarwal For IntelDocument2 paginiCV #2 Abhinav Agarwal For Intelsatbirsingh123Încă nu există evaluări

- Introduction To Analog Integrated Circuits DesignDocument20 paginiIntroduction To Analog Integrated Circuits DesignGowtham HariÎncă nu există evaluări

- Abhinav Resume PDFDocument2 paginiAbhinav Resume PDFAnurag PrabhakarÎncă nu există evaluări

- ESE Pattern and SyllabusDocument3 paginiESE Pattern and SyllabusSanjay SinhaÎncă nu există evaluări

- ESE Pattern and SyllabusDocument3 paginiESE Pattern and SyllabusSanjay SinhaÎncă nu există evaluări

- Signature of The Chairman BOS M.E (AE) : KCT-M.E (AE) - I To IV Semester Curriculum and Syllabus R - 2009Document48 paginiSignature of The Chairman BOS M.E (AE) : KCT-M.E (AE) - I To IV Semester Curriculum and Syllabus R - 2009vickyskarthikÎncă nu există evaluări

- ITW12 - MEMS - IEEEAlexSBDocument48 paginiITW12 - MEMS - IEEEAlexSBIEEEAlexSBÎncă nu există evaluări

- Ese EceDocument6 paginiEse EceGaurab DeyÎncă nu există evaluări

- Lectures 1: Review of Technology Trends and Cost/PerformanceDocument53 paginiLectures 1: Review of Technology Trends and Cost/Performanceprasanna_jayaÎncă nu există evaluări

- TCADDocument33 paginiTCADvpsampathÎncă nu există evaluări

- Mechatronics System Design SyllabusDocument4 paginiMechatronics System Design SyllabusCyborg BpsÎncă nu există evaluări

- Faculty of Engineering: ECE 4240 - Microprocessor InterfacingDocument3 paginiFaculty of Engineering: ECE 4240 - Microprocessor InterfacingDheereshÎncă nu există evaluări

- MEMS in Space ApplicationsDocument31 paginiMEMS in Space ApplicationsJayaprakash ReddyÎncă nu există evaluări

- Icicdt Program 2012Document23 paginiIcicdt Program 2012Hùng NguyễnÎncă nu există evaluări

- Binder Welcome TELPM PDFDocument39 paginiBinder Welcome TELPM PDFKe ChekÎncă nu există evaluări

- Curriculum Vitae Michael D. Adams: Revised October 19, 2012Document9 paginiCurriculum Vitae Michael D. Adams: Revised October 19, 2012otman chakkorÎncă nu există evaluări

- Course File - WSNDocument20 paginiCourse File - WSNajaychhotu100% (1)

- Lecture 1 of Circuit AnalysisDocument13 paginiLecture 1 of Circuit AnalysisGikiTopiÎncă nu există evaluări

- Bme 354 2014 L1Document21 paginiBme 354 2014 L1Javier Solis0% (1)

- NIT 1 4 7040 Lecture 1 VLSI EC601Document26 paginiNIT 1 4 7040 Lecture 1 VLSI EC601SANDIP PODDARÎncă nu există evaluări

- MembinamatlamatkerjayaDocument15 paginiMembinamatlamatkerjayaMuhd Nur SalamÎncă nu există evaluări

- Presented By:: Manar Ahmed Abdel GalilDocument21 paginiPresented By:: Manar Ahmed Abdel GalilManar MansourÎncă nu există evaluări

- VLSI ModulesDocument28 paginiVLSI Modulessai_karthik89Încă nu există evaluări

- Digital Integrated CircuitDocument24 paginiDigital Integrated CircuitUmer JavaidÎncă nu există evaluări

- File: /home/binod/documents/allfmca p/rocket-chip-master/README - MD Page 1 of 7Document7 paginiFile: /home/binod/documents/allfmca p/rocket-chip-master/README - MD Page 1 of 7kbkkrÎncă nu există evaluări

- Micro - Arch OpenpitonDocument51 paginiMicro - Arch OpenpitonkbkkrÎncă nu există evaluări

- Boom Template GithubDocument11 paginiBoom Template GithubkbkkrÎncă nu există evaluări

- Christopher Celio, Krste Asanovic, David PalersonDocument35 paginiChristopher Celio, Krste Asanovic, David PalersonkbkkrÎncă nu există evaluări

- The Berkeley Out - of - Order Machine (Boom!) : An Open - Source Industry - Compeeeve, Synthesizable, Parameterized Risc - V ProcessorDocument45 paginiThe Berkeley Out - of - Order Machine (Boom!) : An Open - Source Industry - Compeeeve, Synthesizable, Parameterized Risc - V ProcessorkbkkrÎncă nu există evaluări

- The Berkeley Out-of-Order Machine (BOOM) : An Industry-Competitive, Synthesizable, Parameterized RISC-V ProcessorDocument5 paginiThe Berkeley Out-of-Order Machine (BOOM) : An Industry-Competitive, Synthesizable, Parameterized RISC-V ProcessorkbkkrÎncă nu există evaluări

- Free and Open Instruction Sets & Other Stuff: Krste Asanović, Representing The ASPIRE LabDocument27 paginiFree and Open Instruction Sets & Other Stuff: Krste Asanović, Representing The ASPIRE LabkbkkrÎncă nu există evaluări

- Present On 2D CompactionDocument26 paginiPresent On 2D CompactionkbkkrÎncă nu există evaluări

- Stealing Hyperparameters in Machine Learning: Binghui Wang and Neil Zhenqiang GongDocument30 paginiStealing Hyperparameters in Machine Learning: Binghui Wang and Neil Zhenqiang GongkbkkrÎncă nu există evaluări

- Assertion Based DebuggingDocument4 paginiAssertion Based DebuggingkbkkrÎncă nu există evaluări

- Post-Silicon Fault Localisation Using MAX-SAT & Backbones: Georg WeissenbacherDocument25 paginiPost-Silicon Fault Localisation Using MAX-SAT & Backbones: Georg WeissenbacherkbkkrÎncă nu există evaluări

- The Rocc Doc V2: An Introduction To The Rocket Custom Coprocessor InterfaceDocument11 paginiThe Rocc Doc V2: An Introduction To The Rocket Custom Coprocessor Interfacekbkkr0% (1)

- Dataflow: Passing The TokenDocument42 paginiDataflow: Passing The TokenkbkkrÎncă nu există evaluări

- Tvlsi00 GuptaDocument11 paginiTvlsi00 GuptakbkkrÎncă nu există evaluări

- Transition Delay Fault Brad Hill ELEC 7250 April 13, 2006Document6 paginiTransition Delay Fault Brad Hill ELEC 7250 April 13, 2006kbkkrÎncă nu există evaluări

- FUJITADocument36 paginiFUJITAkbkkrÎncă nu există evaluări

- 8 Tips For Waking Up Early & Conquering The Alarm ClockDocument9 pagini8 Tips For Waking Up Early & Conquering The Alarm ClockkbkkrÎncă nu există evaluări

- 4 Ways To Wake Up Early - WikihowDocument8 pagini4 Ways To Wake Up Early - WikihowkbkkrÎncă nu există evaluări

- EspressoDocument9 paginiEspressokbkkrÎncă nu există evaluări

- Unified Method To Detect Transistor Stuck-Open Faults & Transition Delay FaultsDocument18 paginiUnified Method To Detect Transistor Stuck-Open Faults & Transition Delay FaultskbkkrÎncă nu există evaluări

- ABC Command$Document20 paginiABC Command$kbkkrÎncă nu există evaluări

- Abc 1Document3 paginiAbc 1kbkkrÎncă nu există evaluări

- A3941 DatasheetDocument21 paginiA3941 Datasheetsoft4gsmÎncă nu există evaluări

- CG2027 0 Introduction 1 The DeviceDocument61 paginiCG2027 0 Introduction 1 The DevicePeng FeiÎncă nu există evaluări

- Irf640a PDFDocument7 paginiIrf640a PDFXavier CastilloÎncă nu există evaluări

- Analysis of Switched-Capacitor Common-Mode Feedback CircuitDocument12 paginiAnalysis of Switched-Capacitor Common-Mode Feedback CircuitDebopam Banerjee100% (1)

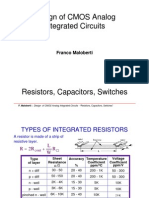

- Design of CMOS Analog Integrated Circuits: Franco MalobertiDocument25 paginiDesign of CMOS Analog Integrated Circuits: Franco MalobertiKesani Venkat Narsimha ReddyÎncă nu există evaluări

- AICDocument21 paginiAICOzephSharifÎncă nu există evaluări

- Daewoo Dtd14h9 Dtd21h9 CH Cp093fDocument58 paginiDaewoo Dtd14h9 Dtd21h9 CH Cp093fminagabiroÎncă nu există evaluări

- Metal Oxide SemiconductorDocument50 paginiMetal Oxide Semiconductorkamal hameed tayyÎncă nu există evaluări

- Cmos, Analog, Design-25Document261 paginiCmos, Analog, Design-25dogudoguÎncă nu există evaluări

- PV - Overview of Real-Time Lifetime Prediction and Extension For SiC Power ConvertersDocument29 paginiPV - Overview of Real-Time Lifetime Prediction and Extension For SiC Power ConvertersCB MildredÎncă nu există evaluări

- Tidr 393Document9 paginiTidr 393bazoka fransiskusÎncă nu există evaluări

- Power ManagementDocument54 paginiPower ManagementkuntaladasÎncă nu există evaluări

- Especificacao Tecnica 8FBMT 1.6 2.0 - 3.5 5.0 PDFDocument10 paginiEspecificacao Tecnica 8FBMT 1.6 2.0 - 3.5 5.0 PDFizidorio soaresÎncă nu există evaluări

- ECE 2nd Year Curriculum Structure Syllabus 2023 24Document43 paginiECE 2nd Year Curriculum Structure Syllabus 2023 24Raghu J MandyaÎncă nu există evaluări

- BSNL Paper On 20Th June, 2008 Visit Site For More InformationDocument11 paginiBSNL Paper On 20Th June, 2008 Visit Site For More InformationReganÎncă nu există evaluări

- High CMR Isolated 2Sw 4A Gate Drive Module For Sic FetsDocument11 paginiHigh CMR Isolated 2Sw 4A Gate Drive Module For Sic FetsMuhammad SameerÎncă nu există evaluări

- Imams Seminar 2Document8 paginiImams Seminar 2Abubakar Hafs MusaÎncă nu există evaluări

- Laptop Chip Level Repairing Course SyllabusDocument4 paginiLaptop Chip Level Repairing Course SyllabusLciit LaptopCareÎncă nu există evaluări

- EC8351 Electronic Circuits I IQDocument20 paginiEC8351 Electronic Circuits I IQRekha SharmilyÎncă nu există evaluări

- Basic Electronics (ES-112)Document29 paginiBasic Electronics (ES-112)Bharat LalÎncă nu există evaluări

- Viper 100 ADocument31 paginiViper 100 AvasilesicoeÎncă nu există evaluări

- FINFETDocument11 paginiFINFETAnusha SagiÎncă nu există evaluări

- ECE Reviewer 001Document10 paginiECE Reviewer 001mrgreen0024Încă nu există evaluări

- EE3950 Class Notes Chapter 12 Hambley 3-12Document56 paginiEE3950 Class Notes Chapter 12 Hambley 3-12anonnnsÎncă nu există evaluări

- EEE SUST Syllabus Session 2011-12Document31 paginiEEE SUST Syllabus Session 2011-12Shahadat Hussain ParvezÎncă nu există evaluări

- 20 NMDocument35 pagini20 NMNikhilAKothariÎncă nu există evaluări

- PRACTICAL1Document7 paginiPRACTICAL1Boy MachoÎncă nu există evaluări

- Mp1423 - MonolithicPowerDocument11 paginiMp1423 - MonolithicPowerJuanKaÎncă nu există evaluări

- EC2257-Lab Manual For Circuits and Simulation Integrated LaboratoryDocument38 paginiEC2257-Lab Manual For Circuits and Simulation Integrated Laboratorygokila_dr9897Încă nu există evaluări

- Irf7832Pbf: V R Max QGDocument10 paginiIrf7832Pbf: V R Max QGdreyes3773Încă nu există evaluări