Documente Academic

Documente Profesional

Documente Cultură

Solution For All Problems in Chapter 9

Încărcat de

hqthang19952602Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Solution For All Problems in Chapter 9

Încărcat de

hqthang19952602Drepturi de autor:

Formate disponibile

SOLUTION FOR PROBLEMS IN CHAPTER 9 : MSI LOGIC CIRCUITS

9-1 : Refer to Figure 9-3 Determine the levels at each decoder output for the following sets of input

conditions :

a. Input : All LOW output : All HIGH

b. Input : LOW except E3= HIGH output : O3=LOW

c. Input : All inputs HIGH except E1=E2=LOW Output : All HIGH

d. Input : All HIGH Output : All LOW

9-3 : For a 74LS138, what input conditions will produce the following outputs :

a. Output : LOW at O6 Input : E3E2E1 = 100, [A]=110 (MSB)

b. Output : LOW at O3 Input : E3E2E1 = 100, [A]=011 (MSB)

c. Output : LOW at O5 Input : E3E2E1 = 100, [A]=101 (MSB)

d. Output : LOW at O0 and O7, simultaneously Input : E3E2E1 = 100, [A]= 111 (MSB)

9-4 : Show how to use 74LS138s to form a 1-of-16 decoder :

Inputs A, B, C are used to select which output on either decoder will be at logic 1 (HIGH) and input Dis used

with the enable input to select which encoder either the first or second will output the 1.

However, there is a limit to the number of inputs that can be used for one particular decoder, because

as n increases, the number of AND gates required to produce an output also becomes larger resulting in the fan-

out of the gates used to drive them becoming large.

This type of active-HIGH decoder can be implemented using just Inverters, ( NOT Gates ) and AND gates. It

is convenient to use an AND gate as the basic decoding element for the output because it produces a HIGH or

logic 1 output only when all of its inputs are logic 1.

But some binary decoders are constructed using NAND gates instead of AND gates for their decoded output,

since NAND gates are cheaper to produce than ANDs as they require fewer transistors to implement within

their design.

The use of NAND gates as the decoding element, results in an active-LOW output while the rest will be

HIGH. As a NAND gate produces the AND operation with an inverted output, the NAND decoder looks like

this with its inverted truth table.

9.5: Figure 9-70 shows how a decoder can be used in the generation of control signals . Assume that s

RESET pulse has occurred at time t0, and determine the CONTROL waveform for 32 clock pulses :

9.8 : Consider the waveform in Figure 9-72 . Apply these signals to the 74LS138 as follow :

AA0, BA1, CA2, DE3

9-13 : Drill question : For each item, indicate whether it is referring to a decoder or an encoder :

(a),(b): Decoder ; (c),(d),(e) : Encoder

9-15: Apply the signals of Figure 9-72 to the inputs of a 74147 as follows : AA7, BA4, CA2,

DA1 :

9-16:

9-24:

9-25:

9-27:

9-29:

9-31:

9-35:

9-36:

9-37:

9-38:

9-39:

9-41:

9-43:

9-44:

9-56:

9-57:

9-58

9-62:

S-ar putea să vă placă și

- Bosch p7100 Injection Pump Service Manual PDFDocument2 paginiBosch p7100 Injection Pump Service Manual PDFAdam Johnson7% (14)

- CS 25000 Spring 2017 Final Practice SolutionsDocument13 paginiCS 25000 Spring 2017 Final Practice SolutionsTiger TangÎncă nu există evaluări

- Design and Implementation of Digital Code Lock Using VHDLDocument24 paginiDesign and Implementation of Digital Code Lock Using VHDLNichanametla Sukumar83% (6)

- Computer NetworksDocument3 paginiComputer NetworksharshaÎncă nu există evaluări

- 8088 Instruction SetDocument6 pagini8088 Instruction SetMuhammad RezkyÎncă nu există evaluări

- Pseudo Random Sequence Generator in VerilogDocument3 paginiPseudo Random Sequence Generator in VerilogAhmed AbduljabbarÎncă nu există evaluări

- Subnetting Questions 1Document12 paginiSubnetting Questions 1smzohaibabbasÎncă nu există evaluări

- 8255Document34 pagini8255Manjula Bn100% (1)

- Abdullah Khurram - Coal Lab 12Document9 paginiAbdullah Khurram - Coal Lab 12muhammad saadÎncă nu există evaluări

- Convolutional CodesDocument83 paginiConvolutional CodesRashmi JamadagniÎncă nu există evaluări

- Interfacing Hex Keypad To 8051.Document5 paginiInterfacing Hex Keypad To 8051.RejinÎncă nu există evaluări

- Instruction Set Architecture-Nguyễn Hoàng Long - BI11-157Document11 paginiInstruction Set Architecture-Nguyễn Hoàng Long - BI11-157Long NguyễnÎncă nu există evaluări

- Solution For All Problems in Chapter 9Document3 paginiSolution For All Problems in Chapter 9Rahmat Hidayat100% (1)

- Avionics - Decoders & EncodersDocument5 paginiAvionics - Decoders & EncoderskrishnamurthyVishÎncă nu există evaluări

- Voltmeter Using 8051.: Circuit DiagramDocument16 paginiVoltmeter Using 8051.: Circuit DiagramVikas Ps100% (1)

- Courses in Electrical Engineering: Digital Electronics Chapter Two: Logic GatesDocument19 paginiCourses in Electrical Engineering: Digital Electronics Chapter Two: Logic GatesNGOUNEÎncă nu există evaluări

- Adc0808 and 8253Document35 paginiAdc0808 and 8253Avanish NiranjanÎncă nu există evaluări

- DCLD LabDocument42 paginiDCLD LabRachit ChauhanÎncă nu există evaluări

- Nand GateDocument5 paginiNand GateNeeraj SharmaÎncă nu există evaluări

- Noise, Nonlinear Distortion and System Parameters: Trinh Xuan Dung, PHDDocument200 paginiNoise, Nonlinear Distortion and System Parameters: Trinh Xuan Dung, PHDKhang Nguyen0% (1)

- Fixed Point and Floating Point Representation #2Document19 paginiFixed Point and Floating Point Representation #2Gasser Alaa EldienÎncă nu există evaluări

- Signals & Systems - Chapter 4: T U e eDocument14 paginiSignals & Systems - Chapter 4: T U e eAlgerian AissaouiÎncă nu există evaluări

- Lab Report 4Document10 paginiLab Report 4abdulbabulÎncă nu există evaluări

- 9A04306 Digital Logic DesignDocument4 pagini9A04306 Digital Logic DesignsivabharathamurthyÎncă nu există evaluări

- Lab Experiment # 9: Implementation and Verification of Truth Table of 8x3 EncoderDocument3 paginiLab Experiment # 9: Implementation and Verification of Truth Table of 8x3 EncoderSaad khanÎncă nu există evaluări

- VHDL Very High Speed Integrated Language: Unit VDocument41 paginiVHDL Very High Speed Integrated Language: Unit VB. MeenakshiÎncă nu există evaluări

- Counter DesignDocument7 paginiCounter Designsujaganesan2009Încă nu există evaluări

- 8086 Inst and Assembler DirectivesDocument49 pagini8086 Inst and Assembler DirectivesGiridhar Kattiri100% (2)

- Chapter 08 BJT Small Signal AnalysisDocument58 paginiChapter 08 BJT Small Signal Analysiscinematic300650% (4)

- Asm 1Document13 paginiAsm 1Daily Batain100% (1)

- Digital System Module 4 PDFDocument52 paginiDigital System Module 4 PDFGeethanjali.pÎncă nu există evaluări

- 2 Universal GateDocument5 pagini2 Universal GateSohil Vohra100% (4)

- Homework Solutions 4Document4 paginiHomework Solutions 4Minh HoangÎncă nu există evaluări

- Mux Ra1911004010178Document10 paginiMux Ra1911004010178Shivanshu TripathiÎncă nu există evaluări

- Electrical Engineering Lab ReportDocument7 paginiElectrical Engineering Lab ReportFrancis Paul SantiagoÎncă nu există evaluări

- LTSpiceDocument21 paginiLTSpicedellxps3941Încă nu există evaluări

- (Do Not Print) Digital-Electronics PDFDocument122 pagini(Do Not Print) Digital-Electronics PDFMasaruNakaegawaÎncă nu există evaluări

- ASM ReferenceDocument22 paginiASM ReferenceAlbert Luzx100% (1)

- Document On Interfacing ADC With 8051 MicrocontrollerDocument5 paginiDocument On Interfacing ADC With 8051 MicrocontrollerSrideviKumaresanÎncă nu există evaluări

- BT19ECE067 Assignment 03Document11 paginiBT19ECE067 Assignment 03BT19ECE067 MiteshÎncă nu există evaluări

- Digital Techniques and MicroprocessorsDocument3 paginiDigital Techniques and MicroprocessorsHarshal DevadeÎncă nu există evaluări

- BCD To Seven SegmentDocument4 paginiBCD To Seven SegmentHari PrasadÎncă nu există evaluări

- 4 Bit BCD AdderDocument7 pagini4 Bit BCD AdderJagnur SinghÎncă nu există evaluări

- Lab2 VerilogDocument5 paginiLab2 VerilogHải TrầnÎncă nu există evaluări

- Triangular Pulse Python CodeDocument2 paginiTriangular Pulse Python Codeanish250% (1)

- Digital Number Systems 3 AnsDocument3 paginiDigital Number Systems 3 AnsbhagÎncă nu există evaluări

- Gray To Binary and Binary To Gray Code Converter: Exp - No: Date: Aim: To Design and Implement A Circuit Which ConvertsDocument3 paginiGray To Binary and Binary To Gray Code Converter: Exp - No: Date: Aim: To Design and Implement A Circuit Which ConvertsNafeesa SalehÎncă nu există evaluări

- Expt 4 Truth Table Verification of Logic GatesDocument5 paginiExpt 4 Truth Table Verification of Logic GatesSwapnil Babele100% (1)

- Escuela Superior Politécnica De Chimborazo: D= P P U sin (θ) dθ d ∅ PDocument7 paginiEscuela Superior Politécnica De Chimborazo: D= P P U sin (θ) dθ d ∅ PJorge SaÎncă nu există evaluări

- K MapDocument30 paginiK MapDollyRajdevÎncă nu există evaluări

- Veilog HDL Module 3Document62 paginiVeilog HDL Module 3Mallik KglÎncă nu există evaluări

- Line CodingDocument59 paginiLine CodingFarhan Aditya100% (1)

- S-Edit Examples GuideDocument41 paginiS-Edit Examples GuideAyan GhoshÎncă nu există evaluări

- Department of Electronics and Communication 8051 Microcontroller and Interfacing Objective Questions and Answers Iii Year Unit - IDocument20 paginiDepartment of Electronics and Communication 8051 Microcontroller and Interfacing Objective Questions and Answers Iii Year Unit - IdeptÎncă nu există evaluări

- To Design An Adaptive Channel Equalizer Using MATLABDocument43 paginiTo Design An Adaptive Channel Equalizer Using MATLABAngel Pushpa100% (1)

- AVR Microcontroller: Prepared By: Eng. Ashraf DarwishDocument28 paginiAVR Microcontroller: Prepared By: Eng. Ashraf DarwishHectorLopez100% (2)

- Digital ElectronicsDocument32 paginiDigital ElectronicsMd. Tanvir Ahmed0% (1)

- Adc InterfacingDocument17 paginiAdc Interfacing21ecuog059Încă nu există evaluări

- Ad-Da Module V1.1Document7 paginiAd-Da Module V1.1Arpita PrasadÎncă nu există evaluări

- Experiment8 Student1Document14 paginiExperiment8 Student1Nicholas ThomasÎncă nu există evaluări

- ADC Module: VoltageDocument5 paginiADC Module: VoltageAmmar AlkindyÎncă nu există evaluări

- Expand IDS Company's Network: I. ProblemsDocument8 paginiExpand IDS Company's Network: I. Problemshqthang19952602Încă nu există evaluări

- Review For Midterm TestDocument1 paginăReview For Midterm Testhqthang19952602Încă nu există evaluări

- Seminar Rubrics - How To Assess Process Tasks?: What Is A Rubric?Document2 paginiSeminar Rubrics - How To Assess Process Tasks?: What Is A Rubric?hqthang19952602Încă nu există evaluări

- Adequate Set of Connectives: Lila KariDocument30 paginiAdequate Set of Connectives: Lila KariSilver BulletÎncă nu există evaluări

- Problems 1 2Document5 paginiProblems 1 2hqthang19952602Încă nu există evaluări

- The Business Pre Intermediate Unit 1 Students BookDocument13 paginiThe Business Pre Intermediate Unit 1 Students Bookpivapivapiva100% (3)

- Cisco 9396tx n9k c9396txDocument13 paginiCisco 9396tx n9k c9396txDejan JovanovicÎncă nu există evaluări

- Protocol Padlet - Online Projects 2020Document2 paginiProtocol Padlet - Online Projects 2020api-284373535Încă nu există evaluări

- Medium Access Control Sublayer (Chapter 4) - CSHub PDFDocument15 paginiMedium Access Control Sublayer (Chapter 4) - CSHub PDFSpeed PianoÎncă nu există evaluări

- D1 - ModBus Device Importer - LABDocument11 paginiD1 - ModBus Device Importer - LABGonzo MelaoÎncă nu există evaluări

- An Efforts Estimate For Agile ProjectsDocument11 paginiAn Efforts Estimate For Agile ProjectsflytosantyÎncă nu există evaluări

- Flair SeriesDocument2 paginiFlair SeriesSse ikolaha SubstationÎncă nu există evaluări

- SMU - Java Programming-Model Question PaperDocument32 paginiSMU - Java Programming-Model Question PaperTanmay MajumderÎncă nu există evaluări

- Yale Smart Home Alarm Manual: Conexis L1Document36 paginiYale Smart Home Alarm Manual: Conexis L1harari itirÎncă nu există evaluări

- Lab 05: Joining Tables: JoinsDocument4 paginiLab 05: Joining Tables: JoinsNida FiazÎncă nu există evaluări

- Project Cover Sheet-CSF 4203 Project (25%) : Higher Colleges of TechnologyDocument8 paginiProject Cover Sheet-CSF 4203 Project (25%) : Higher Colleges of TechnologyengrrhasanÎncă nu există evaluări

- PRODUCTS Final 1Document133 paginiPRODUCTS Final 1Soigne ConsultantsÎncă nu există evaluări

- Chapter 7 E Business SystemsDocument35 paginiChapter 7 E Business Systemsarif213002Încă nu există evaluări

- Chapter 3-Section 3.2-Cylinder BlockDocument46 paginiChapter 3-Section 3.2-Cylinder BlockNikkikumar MaisuriyaÎncă nu există evaluări

- Flygt 2620 EnglishDocument2 paginiFlygt 2620 Englishedwin martinezÎncă nu există evaluări

- Power Supply Unit (PCA-N3060-PSU)Document2 paginiPower Supply Unit (PCA-N3060-PSU)RommelEusuyaÎncă nu există evaluări

- Practical Earthing Bonding Lightning and Surge ProtectionDocument16 paginiPractical Earthing Bonding Lightning and Surge ProtectionAHMED YOUSEFÎncă nu există evaluări

- Report of A 6 Month Internship at Go-Groups LTD, Buea: Faculty of Engineering and TechnologyDocument29 paginiReport of A 6 Month Internship at Go-Groups LTD, Buea: Faculty of Engineering and TechnologyCham RaulÎncă nu există evaluări

- Project TelecommunicationsDocument26 paginiProject Telecommunicationssmart_neo24Încă nu există evaluări

- How To Set Up Inter Company Stock Transfer PDFDocument13 paginiHow To Set Up Inter Company Stock Transfer PDFUfuk DoğanÎncă nu există evaluări

- PDG - 2017 Latest (New Dryer)Document4 paginiPDG - 2017 Latest (New Dryer)mohd fadhilÎncă nu există evaluări

- Cosc - 1436 - Fall 16 - Dalia - Gumeel-CDocument6 paginiCosc - 1436 - Fall 16 - Dalia - Gumeel-CBenÎncă nu există evaluări

- Tnms SNMP Nbi - Operation GuideDocument90 paginiTnms SNMP Nbi - Operation GuideAdrian FlorensaÎncă nu există evaluări

- JETPRO DM-wind (English Small)Document2 paginiJETPRO DM-wind (English Small)Royal Kasepuhan IndonesiaÎncă nu există evaluări

- 2oz Copper PCB Thickness and Its Design GuidelinesDocument14 pagini2oz Copper PCB Thickness and Its Design GuidelinesjackÎncă nu există evaluări

- Q 10Document7 paginiQ 10AndiniPermanaÎncă nu există evaluări

- Variable Environment Hoisting and TDZ in JavaScriptDocument2 paginiVariable Environment Hoisting and TDZ in JavaScriptnoman.ejazÎncă nu există evaluări

- 5 4 VBox User-Manual EngDocument12 pagini5 4 VBox User-Manual Engmax2smith-70% (1)

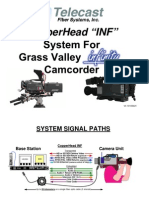

- CopperHead For Infinity Tech Manual V4Document28 paginiCopperHead For Infinity Tech Manual V4TelejuanÎncă nu există evaluări