Documente Academic

Documente Profesional

Documente Cultură

OpAmp - MCP6241

Încărcat de

Ludwig SchmidtDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

OpAmp - MCP6241

Încărcat de

Ludwig SchmidtDrepturi de autor:

Formate disponibile

2005 Microchip Technology Inc.

DS21882C-page 1

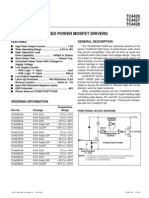

MCP6241/2/4

Features

Gain Bandwidth Product: 550 kHz (typ.)

Supply Current: I

Q

= 50 A (typ.)

Supply Voltage: 1.8V to 5.5V

Rail-to-Rail Input/Output

Extended Temperature Range: -40C to +125C

Available in 5-pin SC-70 and SOT-23 packages

Applications

Automotive

Portable Equipment

Photodiode (Transimpedance) Amplifier

Analog Filters

Notebooks and PDAs

Battery-Powered Systems

Available Tools

SPICE Macro Models (at www.microchip.com)

FilterLab

Software (at www.microchip.com)

Typical Application

Description

The Microchip Technology Inc. MCP6241/2/4

operational amplifiers (op amps) provide wide

bandwidth for the quiescent current. The MCP6241/2/4

has a 550 kHz Gain Bandwidth Product (GBWP) and

68 (typ.) phase margin. This family operates from a

single supply voltage as low as 1.8V, while drawing

50 A (typ.) quiescent current. In addition, the

MCP6241/2/4 family supports rail-to-rail input and

output swing, with a common mode input voltage range

of V

DD

+ 300 mV to V

SS

300 mV. These op amps are

designed in one of Microchips advanced CMOS

processes.

Package Types

MCP6241 V

OUT

V

IN2

+

V

IN1

R

G2

R

G1

R

F

R

Z

V

DD

R

X

R

Y

Summing Amplifier Circuit

4

MCP6241

1

2

3

+

5

V

DD

V

IN

V

OUT

V

SS

V

IN

+

SOT-23-5

4

1

2

3

+

5

V

DD

V

OUT

V

SS

MCP6241R

SOT-23-5

4

1

2

3

+

5

V

SS

V

IN

V

OUT

V

DD

V

IN

+

MCP6241U

SC-70-5, SOT-23-5

4

1

2

3

+

5

V

DD

V

OUT

V

IN

+

V

SS

V

IN

V

IN

+

V

IN

MCP6241

V

SS

V

DD

V

OUT

1

2

3

4

8

7

6

5

+

NC

NC NC

PDIP, SOIC, MSOP

MCP6242

PDIP, SOIC, MSOP

1

2

3

4

8

7

6

5

-

+ -

+

V

INA

_

V

INA

+

V

SS

V

OUTA

V

OUTB

V

DD

V

INB

_

V

INB

+

MCP6244

V

INA

+

V

INA

V

SS

1

2

3

4

14

13

12

11

-

V

OUTA

+ - +

V

DD

V

OUTD

V

IND

V

IND

+

10

9

8

5

6

7 V

OUTB

V

INB

V

INB

+ V

INC

+

V

INC

V

OUTC

+ - - +

PDIP, SOIC, TSSOP

50 A, 550 kHz Rail-to-Rail Op Amp

MCP6241/2/4

DS21882C-page 2 2005 Microchip Technology Inc.

1.0 ELECTRICAL

CHARACTERISTICS

Absolute Maximum Ratings

V

DD

V

SS

........................................................................7.0V

All Inputs and Outputs ................... V

SS

0.3V to V

DD

+ 0.3V

Difference Input Voltage ...................................... |V

DD

V

SS

|

Output Short Circuit Current ..................................continuous

Current at Input Pins ....................................................2 mA

Current at Output and Supply Pins ............................30 mA

Storage Temperature.....................................-65C to +150C

Maximum Junction Temperature (T

J

) .......................... +150C

ESD Protection On All Pins (HBM;MM) ............... 4 kV; 300V

Notice: Stresses above those listed under Absolute

Maximum Ratings may cause permanent damage to the

device. This is a stress rating only and functional operation of

the device at those or any other conditions above those

indicated in the operational listings of this specification is not

implied. Exposure to maximum rating conditions for extended

periods may affect device reliability.

DC ELECTRICAL CHARACTERISTICS

Electrical Characteristics: Unless otherwise indicated, T

A

= +25C, V

DD

= +1.8V to +5.5V, V

SS

= GND,

V

CM

= V

DD

/2, R

L

= 100 k to V

DD

/2 and V

OUT

V

DD

/2.

Parameters Sym Min Typ Max Units Conditions

Input Offset

Input Offset Voltage V

OS

-5.0 +5.0 mV V

CM

= V

SS

Extended Temperature V

OS

-7.0 +7.0 mV T

A

= -40C to +125C,

V

CM

= V

SS

(Note)

Input Offset Drift with

Temperature

V

OS

/T

A

3.0 V/C T

A

= -40C to +125C,

V

CM

= V

SS

Power Supply Rejection PSRR 83 dB V

CM

= V

SS

Input Bias Current and Impedance

Input Bias Current: I

B

1.0 pA

At Temperature I

B

20 pA T

A

= +85C

At Temperature I

B

1100 pA T

A

= +125C

Input Offset Current I

OS

1.0 pA

Common Mode Input Impedance Z

CM

10

13

||6 ||pF

Differential Input Impedance Z

DIFF

10

13

||3 ||pF

Common Mode

Common Mode Input Range V

CMR

V

SS

0.3 V

DD

+ 0.3 V

Common Mode Rejection Ratio CMRR 60 75 dB V

CM

= -0.3V to 5.3V, V

DD

= 5V

Open-Loop Gain

DC Open-Loop Gain

(large signal)

A

OL

90 110 dB V

OUT

= 0.3V to V

DD

0.3V,

V

CM

= V

SS

Output

Maximum Output Voltage Swing V

OL

, V

OH

V

SS

+ 35 V

DD

35 mV R

L

= 10 k, 0.5V Output

Overdrive

Output Short-Circuit Current I

SC

6 mA V

DD

= 1.8V

I

SC

23 mA V

DD

= 5.5V

Power Supply

Supply Voltage V

DD

1.8 5.5 V

Quiescent Current per Amplifier I

Q

30 50 70 A I

O

= 0, V

CM

= V

DD

0.5V

Note: The SC-70 package is only tested at +25C.

2005 Microchip Technology Inc. DS21882C-page 3

MCP6241/2/4

AC ELECTRICAL CHARACTERISTICS

TEMPERATURE CHARACTERISTICS

Electrical Characteristics: Unless otherwise indicated, T

A

= +25C, V

DD

= +1.8 to 5.5V, V

SS

= GND, V

CM

= V

DD

/2,

V

OUT

V

DD

/2, R

L

= 10 k to V

DD

/2 and C

L

= 60 pF.

Parameters Sym Min Typ Max Units Conditions

AC Response

Gain Bandwidth Product GBWP 550 kHz

Phase Margin PM 68 G = +1

Slew Rate SR 0.30 V/s

Noise

Input Noise Voltage E

ni

10 V

P-P

f = 0.1 Hz to 10 Hz

Input Noise Voltage Density e

ni

45 nV/Hz f = 1 kHz

Input Noise Current Density i

ni

0.6 fA/Hz f = 1 kHz

Electrical Characteristics: Unless otherwise indicated, V

DD

= +1.8V to +5.5V and V

SS

= GND.

Parameters Sym Min Typ Max Units Conditions

Temperature Ranges

Extended Temperature Range T

A

-40 +125 C

Operating Temperature Range T

A

-40 +125 C (Note)

Storage Temperature Range T

A

-65 +150 C

Thermal Package Resistances

Thermal Resistance, 5L-SC70

JA

331 C/W

Thermal Resistance, 5L-SOT-23

JA

256 C/W

Thermal Resistance, 8L-MSOP

JA

206 C/W

Thermal Resistance, 8L-PDIP

JA

85 C/W

Thermal Resistance, 8L-SOIC

JA

163 C/W

Thermal Resistance, 14L-PDIP

JA

70 C/W

Thermal Resistance, 14L-SOIC

JA

120 C/W

Thermal Resistance, 14L-TSSOP

JA

100 C/W

Note: The internal Junction Temperature (T

J

) must not exceed the Absolute Maximum specification of +150C.

MCP6241/2/4

DS21882C-page 4 2005 Microchip Technology Inc.

2.0 TYPICAL PERFORMANCE CURVES

Note: Unless otherwise indicated, T

A

= +25C, V

DD

= +1.8V to +5.5V, V

SS

= GND, V

CM

= V

DD

/2, V

OUT

V

DD

/2,

R

L

= 100 k to V

DD

/2 and C

L

= 60 pF.

FIGURE 2-1: Input Offset Voltage.

FIGURE 2-2: PSRR, CMRR vs.

Frequency.

FIGURE 2-3: Input Bias Current at +85C.

FIGURE 2-4: CMRR, PSRR vs. Ambient

Temperature.

FIGURE 2-5: Open-Loop Gain, Phase vs.

Frequency.

FIGURE 2-6: Input Bias Current at +125C.

Note: The graphs and tables provided following this note are a statistical summary based on a limited number of

samples and are provided for informational purposes only. The performance characteristics listed herein

are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified

operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

0%

2%

4%

6%

8%

10%

12%

14%

16%

18%

20%

-

5

-

4

-

3

-

2

-

1012345

Input Offset Voltage (mV)

P

e

r

c

e

n

t

a

g

e

o

f

O

c

c

u

r

r

e

n

c

e

s630 Samples

V

CM

= V

SS

20

30

40

50

60

70

80

90

100

110

1.E+01 1.E+02 1.E+03 1.E+04 1.E+05

Frequency (Hz)

P

S

R

R

,

C

M

R

R

(

d

B

)

10 1k 10k 100k 100

PSRR+

PSRR-

CMRR

0%

5%

10%

15%

20%

25%

06

1

2

1

8

2

4

3

0

3

6

4

2

Input Bias Current (pA)

P

e

r

c

e

n

t

a

g

e

o

f

O

c

c

u

r

r

e

n

c

e

s180 Samples

V

CM

= V

DD

/2

T

A

= +85C

70

75

80

85

90

-50 -25 0 25 50 75 100 125

Ambient Temperature (C)

C

M

R

R

,

P

S

R

R

(

d

B

)

PSRR (V

CM

= V

SS

)

CMRR (V

CM

= -0.3V to +5.3V,

V

DD

= 5.0V)

-20

0

20

40

60

80

100

120

1.E-

01

1.E+

00

1.E+

01

1.E+

02

1.E+

03

1.E+

04

1.E+

05

1.E+

06

1.E+

07

Frequency (Hz)

O

p

e

n

-

L

o

o

p

G

a

i

n

(

d

B

)

-210

-180

-150

-120

-90

-60

-30

0

O

p

e

n

-

L

o

o

p

P

h

a

s

e

(

)

R

L

= 10.0 k

V

CM

= V

DD

/2

0.1 1 10 100 1k 10k 100k 1M 10M

Gain

Phase

0%

5%

10%

15%

20%

25%

30%

0

.

0

0

.

2

0

.

4

0

.

6

0

.

8

1

.

0

1

.

2

1

.

4

1

.

6

1

.

8

2

.

0

Input Bias Current (nA)

P

e

r

c

e

n

t

a

g

e

o

f

O

c

c

u

r

r

e

n

c

e

s

180 Samples

V

CM

= V

DD

/2

T

A

= +125C

2005 Microchip Technology Inc. DS21882C-page 5

MCP6241/2/4

Note: Unless otherwise indicated, T

A

= +25C, V

DD

= +1.8V to +5.5V, V

SS

= GND, V

CM

= V

DD

/2, V

OUT

V

DD

/2,

R

L

= 100 k to V

DD

/2 and C

L

= 60 pF.

FIGURE 2-7: Input Noise Voltage Density

vs. Frequency.

FIGURE 2-8: Input Offset Voltage vs.

Common Mode Input Voltage at V

DD

= 1.8V.

FIGURE 2-9: Input Offset Voltage vs.

Common Mode Input Voltage at V

DD

= 5.5V.

FIGURE 2-10: Input Offset Voltage Drift.

FIGURE 2-11: Input Offset Voltage vs.

Output Voltage.

FIGURE 2-12: Output Short-Circuit Current

vs. Ambient Temperature.

10

100

1,000

10,000

1.E-01 1.E+0

0

1.E+0

1

1.E+0

2

1.E+0

3

1.E+0

4

1.E+0

5

Frequency (Hz)

I

n

p

u

t

N

o

i

s

e

V

o

l

t

a

g

e

D

e

n

s

i

t

y

(

n

V

/

H

z

)

0.1 100 1k 10k 100k 10 1

-300

-200

-100

0

100

200

300

-

0

.

4

-

0

.

2

0

.

0

0

.

2

0

.

4

0

.

6

0

.

8

1

.

0

1

.

2

1

.

4

1

.

6

1

.

8

2

.

0

2

.

2

Common Mode Input Voltage (V)

I

n

p

u

t

O

f

f

s

e

t

V

o

l

t

a

g

e

(

V

)V

DD

= 1.8V

T

A

= -40C

T

A

= +25C

T

A

= +85C

T

A

= +125C

-200

-100

0

100

200

300

400

-

0

.

5

0

.

0

0

.

5

1

.

0

1

.

5

2

.

0

2

.

5

3

.

0

3

.

5

4

.

0

4

.

5

5

.

0

5

.

5

6

.

0

Common Mode Input Voltage (V)

I

n

p

u

t

O

f

f

s

e

t

V

o

l

t

a

g

e

(

V

)V

DD

= 5.5V

T

A

= -40C

T

A

= +25C

T

A

= +85C

T

A

= +125C

0%

2%

4%

6%

8%

10%

12%

14%

16%

18%

20%

-

1

2

-

1

0

-

8

-

6

-

4

-

202468

1

0

1

2

Input Offset Voltage Drift (V/C)

P

e

r

c

e

n

t

a

g

e

o

f

O

c

c

u

r

r

e

n

c

e

s

628 Samples

V

CM

= V

SS

T

A

= -40C to +125C

300

350

400

450

500

550

600

650

700

0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5

Output Voltage (V)

I

n

p

u

t

O

f

f

s

e

t

V

o

l

t

a

g

e

(

V

)

V

DD

= 1.8V

V

CM

= V

SS

V

DD

= 5.5V

-35

-30

-25

-20

-15

-10

-5

0

5

10

15

20

25

30

35

0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5

Power Supply Voltage (V)

S

h

o

r

t

C

i

r

c

u

i

t

C

u

r

r

e

n

t

(

m

A

)

T

A

= +125C

T

A

= +85C

T

A

= +25C

T

A

= -40C

+I

SC

-I

SC

MCP6241/2/4

DS21882C-page 6 2005 Microchip Technology Inc.

Note: Unless otherwise indicated, T

A

= +25C, V

DD

= +1.8V to +5.5V, V

SS

= GND, V

CM

= V

DD

/2, V

OUT

V

DD

/2,

R

L

= 100 k to V

DD

/2 and C

L

= 60 pF.

FIGURE 2-13: Slew Rate vs. Ambient

Temperature.

FIGURE 2-14: Output Voltage Headroom

vs. Output Current Magnitude.

FIGURE 2-15: Maximum Output Voltage

Swing vs. Frequency.

FIGURE 2-16: Small-Signal, Non-Inverting

Pulse Response.

FIGURE 2-17: Large-Signal, Non-Inverting

Pulse Response.

FIGURE 2-18: Quiescent Current vs.

Power Supply Voltage.

0.10

0.15

0.20

0.25

0.30

0.35

0.40

0.45

0.50

-50 -25 0 25 50 75 100 125

Ambient Temperature (C)

S

l

e

w

R

a

t

e

(

V

/

s

)

Falling Edge

Rising Edge

V

DD

= 1.8V

V

DD

= 5.5V

1

10

100

1,000

1.E-02 1.E-01 1.E+00 1.E+01

Output Current Magnitude (A)

O

u

t

p

u

t

V

o

l

t

a

g

e

H

e

a

d

r

o

o

m

(

m

V

)

V

DD

V

OH

10m 1m

V

OL

V

SS

100 10

0.1

1

10

1.E+03 1.E+04 1.E+05 1.E+06

Frequency (Hz)

M

a

x

.

O

u

t

p

u

t

V

o

l

t

a

g

e

S

w

i

n

g

(

V

P

-

P

)

V

DD

= 5.5V

V

DD

= 1.8V

1k 10k 100k 1M

Time (1 s/div)

O

u

t

p

u

t

V

o

l

t

a

g

e

(

1

0

m

V

/

d

i

v

)

G = +1 V/V

R

L

= 10 k

0.0

0.5

1.0

1.5

2.0

2.5

3.0

3.5

4.0

4.5

5.0

Time (10 s/div)

O

u

t

p

u

t

V

o

l

t

a

g

e

(

V

)

V

DD

= 5.0V

G = +1 V/V

0

10

20

30

40

50

60

70

80

0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5

Power Supply Voltage (V)

Q

u

i

e

s

c

e

n

t

C

u

r

r

e

n

t

p

e

r

A

m

p

l

i

f

i

e

r

(

A

)

V

CM

= 0.9V

DD

T

A

= +125C

T

A

= +85C

T

A

= +25C

T

A

= -40C

2005 Microchip Technology Inc. DS21882C-page 7

MCP6241/2/4

3.0 PIN DESCRIPTIONS

Descriptions of the pins are listed in Table 3-1 (single op amps) and Table 3-2 (dual and quad op amps).

TABLE 3-1: PIN FUNCTION TABLE FOR SINGLE OP AMPS

TABLE 3-2: PIN FUNCTION TABLE FOR DUAL AND QUAD OP AMPS

3.1 Analog Outputs

The output pins are low-impedance voltage sources.

3.2 Analog Inputs

The non-inverting and inverting inputs are high-

impedance CMOS inputs with low bias currents.

3.3 Power Supply (V

SS

and V

DD

)

The positive power supply (V

DD

) is 1.8V to 5.5V higher

than the negative power supply (V

SS

). For normal

operation, the other pins are between V

SS

and V

DD

.

Typically, these parts are used in a single-(positive)

supply configuration. In this case, V

SS

is connected to

ground and V

DD

is connected to the supply. V

DD

will

need a local bypass capacitor (typically 0.01 F to

0.1 F) within 2 mm of the V

DD

pin. These parts can

share a bulk capacitor (typically 1 F to 100 F) with

other nearby analog parts; it needs to be within 100 mm

of the V

DD

pin.

MCP6241

(PDIP, SOIC, MSOP)

MCP6241

(SOT-23-5)

MCP6241R

(SOT-23-5)

MCP6241U

(SOT-23-5)

Symbol Description

6 1 1 4 V

OUT

Analog Output

2 4 4 3 V

IN

Inverting Input

3 3 3 1 V

IN

+ Non-inverting Input

7 5 2 5 V

DD

Positive Power Supply

4 2 5 2 V

SS

Negative Power Supply

1, 5, 8 NC No Internal Connection

MCP6242 MCP6244 Symbol Description

1 1 V

OUTA

Analog Output (op amp A)

2 2 V

INA

Inverting Input (op amp A)

3 3 V

INA

+ Non-inverting Input (op amp A)

8 4 V

DD

Positive Power Supply

5 5 V

INB

+ Non-inverting Input (op amp B)

6 6 V

INB

Inverting Input (op amp B)

7 7 V

OUTB

Analog Output (op amp B)

8 V

OUTC

Analog Output (op amp C)

9 V

INC

Inverting Input (op amp C)

10 V

INC

+ Non-inverting Input (op amp C)

4 11 V

SS

Negative Power Supply

12 V

IND

+ Non-inverting Input (op amp D)

13 V

IND

Inverting Input (op amp D)

14 V

OUTD

Analog Output (op amp D)

MCP6241/2/4

DS21882C-page 8 2005 Microchip Technology Inc.

4.0 APPLICATION INFORMATION

The MCP6241/2/4 family of op amps is manufactured

using Microchips state-of-the-art CMOS process and

is specifically designed for low-power and general-

purpose applications. The low supply voltage, low

quiescent current and wide bandwidth makes the

MCP6241/2/4 ideal for battery-powered applications.

4.1 Rail-to-Rail Inputs

The MCP6241/2/4 op amps are designed to prevent

phase reversal when the input pins exceed the supply

voltages. Figure 4-1 shows the input voltage exceeding

the supply voltage without any phase reversal.

FIGURE 4-1: The MCP6241/2/4 Show No

Phase Reversal.

The input stage of the MCP6241/2/4 op amps use two

differential input stages in parallel. One operates at low

common mode input voltage (V

CM

) and the other at

high V

CM

. With this topology, the device operates with

V

CM

up to 300 mV above V

DD

and 300 mV below V

SS

.

The Input Offset Voltage is measured at

V

CM

= V

SS

300 mV and V

DD

+ 300 mV to ensure

proper operation.

Input voltages that exceed the input voltage range

(V

SS

0.3V to V

DD

+ 0.3V at 25C) can cause

excessive current to flow into or out of the input pins.

Current beyond 2 mA can cause reliability problems.

Applications that exceed this rating must be externally

limited with a resistor, as shown in Figure 4-2.

FIGURE 4-2: Input Current-Limiting

Resistor (R

IN

).

4.2 Rail-to-Rail Output

The output voltage range of the MCP6241/2/4 op amps

is V

DD

35 mV (max.) and V

SS

+ 35 mV (min.) when

R

L

= 10 k is connected to V

DD

/2 and V

DD

= 5.5V.

Refer to Figure 2-14 for more information.

4.3 Capacitive Loads

Driving large capacitive loads can cause stability

problems for voltage-feedback op amps. As the load

capacitance increases, the feedback loops phase

margin decreases and the closed-loop bandwidth is

reduced. This produces gain peaking in the frequency

response, with overshoot and ringing in the step

response. A unity-gain buffer (G = +1) is the most

sensitive to capacitive loads, but all gains show the

same general behavior.

When driving large capacitive loads with these op

amps (e.g., > 70 pF when G = +1), a small series

resistor at the output (R

ISO

in Figure 4-3) improves the

feedback loops phase margin (stability) by making the

output load resistive at higher frequencies. The

bandwidth will be generally lower than the bandwidth

with no capacitive load.

FIGURE 4-3: Output resistor, R

ISO

stabilizes large capacitive loads.

Figure 4-4 gives recommended R

ISO

values for

different capacitive loads and gains. The x-axis is the

normalized load capacitance (C

L

/G

N

), where G

N

is the

circuits noise gain. For non-inverting gains, G

N

and the

signal gain are equal. For inverting gains, G

N

is

1 + |Signal Gain| (e.g., 1 V/V gives G

N

= +2 V/V).

-1

0

1

2

3

4

5

6

Time (1 ms/div)

I

n

p

u

t

,

O

u

t

p

u

t

V

o

l

t

a

g

e

(

V

)

V

OUT

V

IN

V

DD

= 5.0V

G = +2 V/V

R

IN

V

SS

Minimum expected V

IN

( )

2 mA

----------------------------------------------------------------------------

R

IN

Maximum expected V

IN

( ) V

DD

2 mA

-------------------------------------------------------------------------------

V

IN

R

IN

V

OUT MCP624X

+

V

IN

R

ISO

V

OUT

MCP624X

C

L

+

2005 Microchip Technology Inc. DS21882C-page 9

MCP6241/2/4

FIGURE 4-4: Recommended R

ISO

Values

for Capacitive Loads.

After selecting R

ISO

for your circuit, double-check the

resulting frequency response peaking and step

response overshoot. Evaluation on the bench and

simulations with the MCP6241/2/4 SPICE macro

model are very helpful. Modify R

ISO

s value until the

response is reasonable.

4.4 Supply Bypass

With this op amp, the power supply pin (V

DD

for

single-supply) should have a local bypass capacitor

(i.e., 0.01 F to 0.1 F) within 2 mm for good high-

frequency performance. It can use a bulk capacitor

(i.e., 1 F or larger) within 100 mm to provide large,

slow currents. This bulk capacitor can be shared with

other nearby analog parts.

4.5 Unused Op Amps

An unused op amp in a quad package (MCP6244)

should be configured as shown in Figure 4-5. Both

circuits prevent the output from toggling and causing

crosstalk. Circuit A can use any reference voltage

between the supplies, provides a buffered DC voltage,

and minimizes the supply current draw of the unused

op amp. Circuit B minimizes the number of

components, but may draw a little more supply current

for the unused op amp.

FIGURE 4-5: Unused Op Amps.

4.6 PCB Surface Leakage

In applications where low input bias current is critical,

PCB (printed circuit board) surface leakage effects

need to be considered. Surface leakage is caused by

humidity, dust or other contamination on the board.

Under low humidity conditions, a typical resistance

between nearby traces is 10

12

. A 5V difference would

cause 5 pA of current to flow, which is greater than the

MCP6241/2/4 familys bias current at 25C (1 pA, typ.).

The easiest way to reduce surface leakage is to use a

guard ring around sensitive pins (or traces). The guard

ring is biased at the same voltage as the sensitive pin.

An example of this type of layout is shown in

Figure 4-6.

FIGURE 4-6: Example Guard Ring Layout

for Inverting Gain.

1. Non-inverting Gain and Unity-Gain Buffer:

a. Connect the non-inverting pin (V

IN

+) to the

input with a wire that does not touch the

PCB surface.

b. Connect the guard ring to the inverting input

pin (V

IN

). This biases the guard ring to the

common mode input voltage.

2. Inverting Gain and Transimpedance Amplifiers

(convert current to voltage, such as photo

detectors):

a. Connect the guard ring to the non-inverting

input pin (V

IN

+). This biases the guard ring

to the same reference voltage as the op

amp (e.g., V

DD

/2 or ground).

b. Connect the inverting pin (V

IN

) to the input

with a wire that does not touch the PCB

surface.

1.E+02

1.E+03

1.E+04

1.E+01 1.E+02 1.E+03 1.E+04

Normalized Load Capacitance; C

L

/G

N

(F)

R

e

c

o

m

m

e

n

d

e

d

R

I

S

O

(

)

10p 100p 1n 10n

10k

1k

100

G

N

= +1 V/V

G

N

+2 V/V

V

DD

V

DD

V

DD

MCP6244 (A) MCP6244 (B)

Guard Ring

V

SS

V

IN

- V

IN

+

MCP6241/2/4

DS21882C-page 10 2005 Microchip Technology Inc.

4.7 Application Circuits

4.7.1 MATCHING THE IMPEDANCE AT

THE INPUTS

To minimize the effect of offset voltage in an amplifier

circuit, the impedances at the inverting and non-

inverting inputs need to be matched. This is done by

choosing the circuit resistor values so that the total

resistance at each input is the same. Figure 4-7 shows

a summing amplifier circuit.

FIGURE 4-7: Summing Amplifier Circuit.

To match the inputs, set all voltage sources to ground

and calculate the total resistance at the input nodes. In

this summing amplifier circuit, the resistance at the

inverting input is calculated by setting V

IN1

, V

IN2

and

V

OUT

to ground. In this case, R

G1

, R

G2

and R

F

are in

parallel. The total resistance at the inverting input is:

At the non-inverting input, V

DD

is the only voltage

source. When V

DD

is set to ground, both R

X

and R

Y

are

in parallel. The total resistance at the non-inverting

input is:

To minimize offset voltage and increase circuit

accuracy, the resistor values need to meet the

condition:

4.7.2 COMPENSATING FOR THE

PARASITIC CAPACITANCE

In analog circuit design, the PCB parasitic capacitance

can compromise the circuit behavior; Figure 4-8 shows

a typical scenario. If the input of an amplifier sees

parasitic capacitance of several picofarad (C

PARA

,

which includes the common mode capacitance of 6 pF,

typical) and large R

F

and R

G

, the frequency response

of the circuit will include a zero. This parasitic zero

introduces gain peaking and can cause circuit

instability.

FIGURE 4-8: Effect of Parasitic

Capacitance at the Input.

One solution is to use smaller resistor values to push

the zero to a higher frequency. Another solution is to

compensate by introducing a pole at the point at which

the zero occurs. This can be done by adding C

F

in

parallel with the feedback resistor (R

F

). C

F

needs to be

selected so that the ratio C

PARA

:C

F

is equal to the ratio

of R

F

:R

G

.

MCP624X V

OUT

V

IN2

+

V

IN1

R

G2

R

G1

R

F

R

Z

V

DD

R

X

R

Y

R

VIN

1

1

R

G1

---------

1

R

G2

---------

1

R

F

------ + +

--------------------------------------------- =

Where:

R

VIN

= total resistance at the inverting input

R

VIN

+

1

1

R

X

------

1

R

Y

------ +

------------------------- R

Z

+ =

Where:

R

VIN

+ = total resistance at the inverting

input

R

VIN

+ R

VIN

=

V

OUT

C

F

V

DC

+

V

AC

R

G

R

F

C

PARA

C

F

C

PARA

R

G

R

F

------- =

MCP624X

2005 Microchip Technology Inc. DS21882C-page 11

MCP6241/2/4

5.0 DESIGN TOOLS

Microchip provides the basic design tools needed for

the MCP6241/2/4 family of op amps.

5.1 SPICE Macro Model

The latest SPICE macro model for the MCP6241/2/4 op

amps is available on our web site at

www.microchip.com. This model is intended to be an

initial design tool that works well in the op amps linear

region of operation at room temperature. See the macro

model file for information on its capabilities.

Bench testing is a very important part of any design and

cannot be replaced with simulations. Also, simulation

results using this macro model need to be validated by

comparing them to the data sheet specifications and

characteristic curves.

5.2 FilterLab

Software

Microchips FilterLab software is an innovative tool that

simplifies analog active-filter (using op amps) design.

Available at no cost from our web site at

www.microchip.com, the FilterLab design tool provides

full schematic diagrams of the filter circuit with

component values. It also outputs the filter circuit in

SPICE format, which can be used with the macro

model to simulate actual filter performance.

MCP6241/2/4

DS21882C-page 12 2005 Microchip Technology Inc.

6.0 PACKAGING INFORMATION

6.1 Package Marking Information

1 2 3

5 4

5-Lead SOT-23

Example:

XXNN

1 2 3

5 4

BQ25

Device Code

MCP6241 BQNN

MCP6241R BRNN

MCP6241U BSNN

Note: Applies to 5-Lead SOT-23.

XXXXXXXX

XXXXXNNN

YYWW

8-Lead PDIP (300 mil) Example:

8-Lead SOIC (150 mil) Example:

XXXXXXXX

XXXXYYWW

NNN

MCP6242

E/P ^^256

0546

MCP6242E

SN^^ 0546

256

8-Lead MSOP

Example:

XXXXXX

YWWNNN

6242E

546256

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week 01)

NNN Alphanumeric traceability code

Pb-free JEDEC designator for Matte Tin (Sn)

* This package is Pb-free. The Pb-free JEDEC designator ( )

can be found on the outer packaging for this package.

Note: In the event the full Microchip part number cannot be marked on one line, it will

be carried over to the next line, thus limiting the number of available

characters for customer-specific information.

3 e

3 e

3 e

3 e

5-Lead SC-70 (MCP6241U Only) Example:

XXN (Front)

YWW (Back)

AT2 (Front)

546 (Back)

XXNN

OR

AT25

OR

2005 Microchip Technology Inc. DS21882C-page 13

MCP6241/2/4

Package Marking Information (Continued)

14-Lead PDIP (300 mil) (MCP6244) Example:

14-Lead TSSOP (MCP6244)

Example:

14-Lead SOIC (150 mil) (MCP6244) Example:

XXXXXXXXXXXXXX

XXXXXXXXXXXXXX

YYWWNNN

XXXXXXXXXX

YYWWNNN

XXXXXXXX

YYWW

NNN

MCP6244

0546256

6244E

0546

256

XXXXXXXXXX

MCP6244

0546256

E/P^^

E/SL^^3 e

3 e

MCP6241/2/4

DS21882C-page 14 2005 Microchip Technology Inc.

5-Lead Plastic Small Outline Transistor Package (LT) (SC-70)

0.30 0.15 .012 .006 B Lead Width

0.18 0.10 .007 .004 c Lead Thickness

0.30 0.10 .012 .004 L Foot Length

2.20 1.80 .087 .071 D Overall Length

1.35 1.15 .053 .045 E1 Molded Package Width

2.40 1.80 .094 .071 E Overall Width

0.10 0.00 .004 .000 A1 Standoff

1.00 0.80 .039 .031 A2 Molded Package Thickness

1.10 0.80 .043 .031 A Overall Height

0.65 (BSC) .026 (BSC)

p

Pitch

5 5 n Number of Pins

MAX NOM MIN MAX NOM MIN Dimension Limits

MILLIMETERS* INCHES Units

exceed .005" (0.127mm) per side.

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not

Notes:

JEITA (EIAJ) Standard: SC-70

Drawing No. C04-061

*Controlling Parameter

L

E1

E

c

D

1

B

p

A2

A1

A

Q1

Top of Molded Pkg to Lead Shoulder Q1 .004 .016 0.10 0.40

n

2005 Microchip Technology Inc. DS21882C-page 15

MCP6241/2/4

5-Lead Plastic Small Outline Transistor (OT) (SOT23)

10 5 0 10 5 0 Mold Draft Angle Bottom

10 5 0 10 5 0 Mold Draft Angle Top

0.50 0.43 0.35 .020 .017 .014 B Lead Width

0.20 0.15 0.09 .008 .006 .004 c Lead Thickness

10 5 0 10 5 0 Foot Angle

0.55 0.45 0.35 .022 .018 .014 L Foot Length

3.10 2.95 2.80 .122 .116 .110 D Overall Length

1.75 1.63 1.50 .069 .064 .059 E1 Molded Package Width

3.00 2.80 2.60 .118 .110 .102 E Overall Width

0.15 0.08 0.00 .006 .003 .000 A1 Standoff

1.30 1.10 0.90 .051 .043 .035 A2 Molded Package Thickness

1.45 1.18 0.90 .057 .046 .035 A Overall Height

1.90 .075 p1 Outside lead pitch (basic)

0.95 .038

p

Pitch

5 5 n Number of Pins

MAX NOM MIN MAX NOM MIN Dimension Limits

MILLIMETERS INCHES* Units

1

p

D

B

n

E

E1

L

c

A2

A

A1

p1

exceed .005" (0.127mm) per side.

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not

Notes:

EIAJ Equivalent: SC-74A

Drawing No. C04-091

*Controlling Parameter

MCP6241/2/4

DS21882C-page 16 2005 Microchip Technology Inc.

8-Lead Plastic Micro Small Outline Package (MS) (MSOP)

D

A

A1

L

c

(F)

A2

E1

E

p

B

n 1

2

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not

.037 REF F Footprint (Reference)

exceed .010" (0.254mm) per side.

Notes:

Drawing No. C04-111

*Controlling Parameter

Mold Draft Angle Top

Mold Draft Angle Bottom

Foot Angle

Lead Width

Lead Thickness

c

B

.003

.009

.006

.012

Dimension Limits

Overall Height

Molded Package Thickness

Molded Package Width

Overall Length

Foot Length

Standoff

Overall Width

Number of Pins

Pitch

A

L

E1

D

A1

E

A2

.016 .024

.118 BSC

.118 BSC

.000

.030

.193 TYP.

.033

MIN

p

n

Units

.026 BSC

NOM

8

INCHES

0.95 REF

-

-

.009

.016

0.08

0.22

0

0.23

0.40

8

MILLIMETERS*

0.65 BSC

0.85

3.00 BSC

3.00 BSC

0.60

4.90 BSC

.043

.031

.037

.006

0.40

0.00

0.75

MIN MAX NOM

1.10

0.80

0.15

0.95

MAX

8

- -

-

15 5 -

15 5 -

JEDEC Equivalent: MO-187

0 - 8

5

5 -

-

15

15

- -

- -

2005 Microchip Technology Inc. DS21882C-page 17

MCP6241/2/4

8-Lead Plastic Dual In-line (P) 300 mil (PDIP)

B1

B

A1

A

L

A2

p

E

eB

c

E1

n

D

1

2

Units INCHES* MILLIMETERS

Dimension Limits MIN NOM MAX MIN NOM MAX

Number of Pins n 8 8

Pitch

p

.100 2.54

Top to Seating Plane A .140 .155 .170 3.56 3.94 4.32

Molded Package Thickness A2 .115 .130 .145 2.92 3.30 3.68

Base to Seating Plane A1 .015 0.38

Shoulder to Shoulder Width E .300 .313 .325 7.62 7.94 8.26

Molded Package Width E1 .240 .250 .260 6.10 6.35 6.60

Overall Length D .360 .373 .385 9.14 9.46 9.78

Tip to Seating Plane L .125 .130 .135 3.18 3.30 3.43

Lead Thickness c .008 .012 .015 0.20 0.29 0.38

Upper Lead Width B1 .045 .058 .070 1.14 1.46 1.78

Lower Lead Width B .014 .018 .022 0.36 0.46 0.56

Overall Row Spacing eB .310 .370 .430 7.87 9.40 10.92

Mold Draft Angle Top 5 10 15 5 10 15

Mold Draft Angle Bottom 5 10 15 5 10 15

* Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

JEDEC Equivalent: MS-001

Drawing No. C04-018

.010 (0.254mm) per side.

Significant Characteristic

MCP6241/2/4

DS21882C-page 18 2005 Microchip Technology Inc.

8-Lead Plastic Small Outline (SN) Narrow, 150 mil (SOIC)

Foot Angle 0 4 8 0 4 8

15 12 0 15 12 0 Mold Draft Angle Bottom

15 12 0 15 12 0 Mold Draft Angle Top

0.51 0.42 0.33 .020 .017 .013 B Lead Width

0.25 0.23 0.20 .010 .009 .008 c Lead Thickness

0.76 0.62 0.48 .030 .025 .019 L Foot Length

0.51 0.38 0.25 .020 .015 .010 h Chamfer Distance

5.00 4.90 4.80 .197 .193 .189 D Overall Length

3.99 3.91 3.71 .157 .154 .146 E1 Molded Package Width

6.20 6.02 5.79 .244 .237 .228 E Overall Width

0.25 0.18 0.10 .010 .007 .004 A1 Standoff

1.55 1.42 1.32 .061 .056 .052 A2 Molded Package Thickness

1.75 1.55 1.35 .069 .061 .053 A Overall Height

1.27 .050

p

Pitch

8 8 n Number of Pins

MAX NOM MIN MAX NOM MIN Dimension Limits

MILLIMETERS INCHES* Units

2

1

D

n

p

B

E

E1

h

L

c

45

A2

A

A1

* Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010 (0.254mm) per side.

JEDEC Equivalent: MS-012

Drawing No. C04-057

Significant Characteristic

2005 Microchip Technology Inc. DS21882C-page 19

MCP6241/2/4

14-Lead Plastic Dual In-line (P) 300 mil (PDIP)

E1

n

D

1

2

eB

E

c

A

A1

B

B1

L

A2

p

Units INCHES* MILLIMETERS

Dimension Limits MIN NOM MAX MIN NOM MAX

Number of Pins n 14 14

Pitch

p

.100 2.54

Top to Seating Plane A .140 .155 .170 3.56 3.94 4.32

Molded Package Thickness A2 .115 .130 .145 2.92 3.30 3.68

Base to Seating Plane A1 .015 0.38

Shoulder to Shoulder Width E .300 .313 .325 7.62 7.94 8.26

Molded Package Width E1 .240 .250 .260 6.10 6.35 6.60

Overall Length D .740 .750 .760 18.80 19.05 19.30

Tip to Seating Plane L .125 .130 .135 3.18 3.30 3.43

Lead Thickness c .008 .012 .015 0.20 0.29 0.38

Upper Lead Width B1 .045 .058 .070 1.14 1.46 1.78

Lower Lead Width B .014 .018 .022 0.36 0.46 0.56

Overall Row Spacing eB .310 .370 .430 7.87 9.40 10.92

Mold Draft Angle Top 5 10 15 5 10 15

5 10 15 5 10 15 Mold Draft Angle Bottom

* Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010 (0.254mm) per side.

JEDEC Equivalent: MS-001

Drawing No. C04-005

Significant Characteristic

MCP6241/2/4

DS21882C-page 20 2005 Microchip Technology Inc.

14-Lead Plastic Small Outline (SL) Narrow, 150 mil (SOIC)

Foot Angle 0 4 8 0 4 8

15 12 0 15 12 0 Mold Draft Angle Bottom

15 12 0 15 12 0 Mold Draft Angle Top

0.51 0.42 0.36 .020 .017 .014 B Lead Width

0.25 0.23 0.20 .010 .009 .008 c Lead Thickness

1.27 0.84 0.41 .050 .033 .016 L Foot Length

0.51 0.38 0.25 .020 .015 .010 h Chamfer Distance

8.81 8.69 8.56 .347 .342 .337 D Overall Length

3.99 3.90 3.81 .157 .154 .150 E1 Molded Package Width

6.20 5.99 5.79 .244 .236 .228 E Overall Width

0.25 0.18 0.10 .010 .007 .004 A1 Standoff

1.55 1.42 1.32 .061 .056 .052 A2 Molded Package Thickness

1.75 1.55 1.35 .069 .061 .053 A Overall Height

1.27 .050

p

Pitch

14 14 n Number of Pins

MAX NOM MIN MAX NOM MIN Dimension Limits

MILLIMETERS INCHES* Units

2

1

D

p

n B

E

E1

h

L

c

45

A2 A

A1

* Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010 (0.254mm) per side.

JEDEC Equivalent: MS-012

Drawing No. C04-065

Significant Characteristic

2005 Microchip Technology Inc. DS21882C-page 21

MCP6241/2/4

14-Lead Plastic Thin Shrink Small Outline (ST) 4.4 mm (TSSOP)

8 4 0 8 4 0 Foot Angle

10 5 0 10 5 0 Mold Draft Angle Bottom

10 5 0 10 5 0 Mold Draft Angle Top

0.30 0.25 0.19 .012 .010 .007 B1 Lead Width

0.20 0.15 0.09 .008 .006 .004 c Lead Thickness

0.70 0.60 0.50 .028 .024 .020 L Foot Length

5.10 5.00 4.90 .201 .197 .193 D Molded Package Length

4.50 4.40 4.30 .177 .173 .169 E1 Molded Package Width

6.50 6.38 6.25 .256 .251 .246 E Overall Width

0.15 0.10 0.05 .006 .004 .002 A1 Standoff

0.95 0.90 0.85 .037 .035 .033 A2 Molded Package Thickness

1.10 .043 A Overall Height

0.65 .026

p

Pitch

14 14 n Number of Pins

MAX NOM MIN MAX NOM MIN Dimension Limits

MILLIMETERS* INCHES Units

L

2

1

D

n

B

p

E1

E

A2 A1

A

* Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.005 (0.127mm) per side.

JEDEC Equivalent: MO-153

Drawing No. C04-087

Significant Characteristic

MCP6241/2/4

DS21882C-page 22 2005 Microchip Technology Inc.

NOTES:

2005 Microchip Technology Inc. DS21882C-page 23

MCP6241/2/4

APPENDIX A: REVISION HISTORY

Revision C (March 2005)

The following is the list of modifications:

1. Added the MCP6244 quad op amp.

2. Re-compensated parts. Specifications that

change are: Gain Bandwidth Product (BWP)

and Phase Margin (PM) in AC Electrical

Characteristics table.

3. Corrected plots in Section 2.0 Typical Perfor-

mance Curves.

4. Added Section 3.0 Pin Descriptions.

5. Added new SC-70 package markings. Added

PDIP-14, SOIC-14, and TSSOP-14 packages

and corrected package marking information

(Section 6.0 Packaging Information).

6. Added Appendix A: Revision History.

Revision B (August 2004)

Revision A (March 2004)

Original Release of this Document.

MCP6241/2/4

DS21882C-page 24 2005 Microchip Technology Inc.

NOTES:

2005 Microchip Technology Inc. DS21882C-page 25

MCP6241/2/4

PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

Device: MCP6241: Single Op Amp (MSOP, PDIP, SOIC)

MCP6241T: Single Op Amp (Tape and Reel)

(MSOP, SOIC, SOT-23)

MCP6241RT: Single Op Amp (Tape and Reel)

(SOT-23)

MCP6241UT: Single Op Amp (Tape and Reel)

(SC-70, SOT-23)

MCP6242: Dual Op Amp

MCP6242T: Dual Op Amp (Tape and Reel)

(MSOP, SOIC)

MCP6244: Quad Op Amp

MCP6244T: Quad Op Amp (Tape and Reel)

(SOIC, TSSOP)

Temperature Range: E = -40C to +125C

Package: LT = Plastic Package (SC-70), 5-lead (MCP6241U only)

MS = Plastic Micro Small Outline (MSOP), 8-lead

P = Plastic DIP (300 mil Body), 8-lead, 14-lead

OT = Plastic Small Outline Transistor (SOT-23), 5-lead

(MCP6241, MCP6241R, MCP6241U)

SN = Plastic SOIC (150 mil Body), 8-lead

SL = Plastic SOIC (150 mil Body), 14-lead

ST = Plastic TSSOP (4.4 mil Body), 14-lead

PART NO. -X /XX

Package Temperature

Range

Device

Examples:

a) MCP6241-E/SN: Extended Temp.,

8LD SOIC package.

b) MCP6241-E/MS: Extended Temp.,

8LD MSOP package.

c) MCP6241-E/P: Extended Temp.,

8LD PDIP package.

d) MCP6241RT-E/OT: Tape and Reel,

Extended Temp.,

5LD SOT-23 package

e) MCP6241UT-E/OT: Tape and Reel,

Extended Temp.,

5LD SOT-23 package.

f) MCP6241UT-E/LT: Tape and Reel,

Extended Temp.,

5LD SC-70 package.

a) MCP6242-E/SN: Extended Temp.,

8LD SOIC package.

b) MCP6242-E/MS: Extended Temp.,

8LD MSOP package.

c) MCP6242-E/P: Extended Temp.,

8LD PDIP package.

d) MCP6242T-E/SN: Tape and Reel,

Extended Temp.,

8LD SOIC package.

a) MCP6244-E/P: Extended Temp.,

14LD PDIP package.

b) MCP6244-E/SL: Extended Temp.,

14LD SOIC package.

c) MCP6244-E/ST: Extended Temp.,

14LD TSSOP

package.

d) MCP6244T-E/SL: Tape and Reel,

Extended Temp.,

14LD SOIC package.

e) MCP6244T-E/ST: Tape and Reel,

Extended Temp.,

14LD TSSOP

package.

X

Tape and Reel

Alternate Pinout

and/or

MCP6241/2/4

DS21882C-page 26 2005 Microchip Technology Inc.

NOTES:

2005 Microchip Technology Inc. DS21882C-page 27

Information contained in this publication regarding device

applications and the like is provided only for your convenience

and may be superseded by updates. It is your responsibility to

ensure that your application meets with your specifications.

MICROCHIP MAKES NO REPRESENTATIONS OR WAR-

RANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED,

WRITTEN OR ORAL, STATUTORY OR OTHERWISE,

RELATED TO THE INFORMATION, INCLUDING BUT NOT

LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE,

MERCHANTABILITY OR FITNESS FOR PURPOSE.

Microchip disclaims all liability arising from this information and

its use. Use of Microchips products as critical components in

life support systems is not authorized except with express

written approval by Microchip. No licenses are conveyed,

implicitly or otherwise, under any Microchip intellectual property

rights.

Trademarks

The Microchip name and logo, the Microchip logo, Accuron,

dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART,

PRO MATE, PowerSmart, rfPIC, and SmartShunt are

registered trademarks of Microchip Technology Incorporated

in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB,

PICMASTER, SEEVAL, SmartSensor and The Embedded

Control Solutions Company are registered trademarks of

Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, dsPICDEM,

dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR,

FanSense, FlexROM, fuzzyLAB, In-Circuit Serial

Programming, ICSP, ICEPIC, MPASM, MPLIB, MPLINK,

MPSIM, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail,

PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB,

rfPICDEM, Select Mode, Smart Serial, SmartTel, Total

Endurance and WiperLock are trademarks of Microchip

Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated

in the U.S.A.

All other trademarks mentioned herein are property of their

respective companies.

2005, Microchip Technology Incorporated, Printed in the

U.S.A., All Rights Reserved.

Printed on recycled paper.

Note the following details of the code protection feature on Microchip devices:

Microchip products meet the specification contained in their particular Microchip Data Sheet.

Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchips Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

Microchip is willing to work with the customer who is concerned about the integrity of their code.

Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as unbreakable.

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our

products. Attempts to break Microchips code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts

allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Microchip received ISO/TS-16949:2002 quality system certification for

its worldwide headquarters, design and wafer fabrication facilities in

Chandler and Tempe, Arizona and Mountain View, California in

October 2003. The Companys quality system processes and

procedures are for its PICmicro

8-bit MCUs, KEELOQ

code hopping

devices, Serial EEPROMs, microperipherals, nonvolatile memory and

analog products. In addition, Microchips quality system for the design

and manufacture of development systems is ISO 9001:2000 certified.

DS21882C-page 28 2005 Microchip Technology Inc.

AMERICAS

Corporate Office

2355 West Chandler Blvd.

Chandler, AZ 85224-6199

Tel: 480-792-7200

Fax: 480-792-7277

Technical Support:

http://support.microchip.com

Web Address:

www.microchip.com

Atlanta

Alpharetta, GA

Tel: 770-640-0034

Fax: 770-640-0307

Boston

Westborough, MA

Tel: 774-760-0087

Fax: 774-760-0088

Chicago

Itasca, IL

Tel: 630-285-0071

Fax: 630-285-0075

Dallas

Addison, TX

Tel: 972-818-7423

Fax: 972-818-2924

Detroit

Farmington Hills, MI

Tel: 248-538-2250

Fax: 248-538-2260

Kokomo

Kokomo, IN

Tel: 765-864-8360

Fax: 765-864-8387

Los Angeles

Mission Viejo, CA

Tel: 949-462-9523

Fax: 949-462-9608

San Jose

Mountain View, CA

Tel: 650-215-1444

Fax: 650-961-0286

Toronto

Mississauga, Ontario,

Canada

Tel: 905-673-0699

Fax: 905-673-6509

ASIA/PACIFIC

Australia - Sydney

Tel: 61-2-9868-6733

Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8528-2100

Fax: 86-10-8528-2104

China - Chengdu

Tel: 86-28-8676-6200

Fax: 86-28-8676-6599

China - Fuzhou

Tel: 86-591-8750-3506

Fax: 86-591-8750-3521

China - Hong Kong SAR

Tel: 852-2401-1200

Fax: 852-2401-3431

China - Shanghai

Tel: 86-21-5407-5533

Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829

Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8203-2660

Fax: 86-755-8203-1760

China - Shunde

Tel: 86-757-2839-5507

Fax: 86-757-2839-5571

China - Qingdao

Tel: 86-532-502-7355

Fax: 86-532-502-7205

ASIA/PACIFIC

India - Bangalore

Tel: 91-80-2229-0061

Fax: 91-80-2229-0062

India - New Delhi

Tel: 91-11-5160-8631

Fax: 91-11-5160-8632

Japan - Kanagawa

Tel: 81-45-471- 6166

Fax: 81-45-471-6122

Korea - Seoul

Tel: 82-2-554-7200

Fax: 82-2-558-5932 or

82-2-558-5934

Singapore

Tel: 65-6334-8870

Fax: 65-6334-8850

Taiwan - Kaohsiung

Tel: 886-7-536-4818

Fax: 886-7-536-4803

Taiwan - Taipei

Tel: 886-2-2500-6610

Fax: 886-2-2508-0102

Taiwan - Hsinchu

Tel: 886-3-572-9526

Fax: 886-3-572-6459

EUROPE

Austria - Weis

Tel: 43-7242-2244-399

Fax: 43-7242-2244-393

Denmark - Ballerup

Tel: 45-4450-2828

Fax: 45-4485-2829

France - Massy

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

Germany - Ismaning

Tel: 49-89-627-144-0

Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611

Fax: 39-0331-466781

Netherlands - Drunen

Tel: 31-416-690399

Fax: 31-416-690340

England - Berkshire

Tel: 44-118-921-5869

Fax: 44-118-921-5820

WORLDWIDE SALES AND SERVICE

03/01/05

S-ar putea să vă placă și

- OpAmp - MCP6244Document38 paginiOpAmp - MCP6244Ludwig SchmidtÎncă nu există evaluări

- 2.5V To 6.0V Micropower CMOS Op Amp: FeaturesDocument42 pagini2.5V To 6.0V Micropower CMOS Op Amp: Featuresinside121Încă nu există evaluări

- Ad 7524Document8 paginiAd 7524Giovanny ContrerasÎncă nu există evaluări

- CD4047Document15 paginiCD4047mohankumarktvrÎncă nu există evaluări

- Description Features: CMOS Low-Power Monostable/Astable MultivibratorDocument15 paginiDescription Features: CMOS Low-Power Monostable/Astable Multivibratorதினேஷ் குமார்Încă nu există evaluări

- D D D D D D D D D D D D: CD4066B Cmos Quad Bilateral SwitchDocument20 paginiD D D D D D D D D D D D: CD4066B Cmos Quad Bilateral SwitchAnna Kaye Sapanhila AninÎncă nu există evaluări

- 450 Μa, 5 Mhz Rail-To-Rail Op Amp: Features DescriptionDocument32 pagini450 Μa, 5 Mhz Rail-To-Rail Op Amp: Features DescriptionYusuf UçkunÎncă nu există evaluări

- Mcp6291/1R/2/3/4/5: 1.0 Ma, 10 MHZ Rail-To-Rail Op AmpDocument36 paginiMcp6291/1R/2/3/4/5: 1.0 Ma, 10 MHZ Rail-To-Rail Op AmpJuan RegaladoÎncă nu există evaluări

- D D D D D D D D D D D D: For Description of "B" Series CMOS DevicesDocument25 paginiD D D D D D D D D D D D: For Description of "B" Series CMOS Devicestotal4321Încă nu există evaluări

- MCP6022Document34 paginiMCP6022Михаил МалсюковÎncă nu există evaluări

- Ic-Cmos-4008 UNTUK DECODER PDFDocument9 paginiIc-Cmos-4008 UNTUK DECODER PDFBenny PadlyÎncă nu există evaluări

- Nte 4013Document4 paginiNte 4013Codinasound CaÎncă nu există evaluări

- 7555 CNDocument9 pagini7555 CNdsdsds4Încă nu există evaluări

- NE5532 - Nte778aDocument3 paginiNE5532 - Nte778adaneloÎncă nu există evaluări

- LC MOS Precision Quad SPST Switches ADG411/ADG412/ADG413: 615 V Analog Signal Range V) MW)Document8 paginiLC MOS Precision Quad SPST Switches ADG411/ADG412/ADG413: 615 V Analog Signal Range V) MW)Fer TgÎncă nu există evaluări

- LM324Document7 paginiLM324quocvttÎncă nu există evaluări

- Adm 232 AarnDocument9 paginiAdm 232 AarnAnna Paula SantosÎncă nu există evaluări

- XTR 105Document22 paginiXTR 105Omar AlmonteÎncă nu există evaluări

- 2sj 598 Power Mos Dell 2407wfpbDocument8 pagini2sj 598 Power Mos Dell 2407wfpbkarkeraÎncă nu există evaluări

- MC 14521Document12 paginiMC 14521rrebollarÎncă nu există evaluări

- cd4007 Intersil DatasheetDocument9 paginicd4007 Intersil DatasheetMarie HayesÎncă nu există evaluări

- Ad 844Document12 paginiAd 844Marciel DervansokiÎncă nu există evaluări

- AD694Document12 paginiAD694Asghar AliÎncă nu există evaluări

- 5MO365R Datasheet 234274 - DSDocument21 pagini5MO365R Datasheet 234274 - DSjoaocarlos1705Încă nu există evaluări

- Ina 122Document14 paginiIna 122Wasang Juwi PracihnoÎncă nu există evaluări

- Low Power Quad Op Amps LM124/224/324/324A/ SA534/LM2902: Description Pin ConfigurationDocument9 paginiLow Power Quad Op Amps LM124/224/324/324A/ SA534/LM2902: Description Pin ConfigurationChaitanya KumarÎncă nu există evaluări

- Tle 2425Document24 paginiTle 2425Giapy Phuc TranÎncă nu există evaluări

- TC4426 TC4427 TC4428 1.5A Dual High-Speed Power Mosfet DriversDocument9 paginiTC4426 TC4427 TC4428 1.5A Dual High-Speed Power Mosfet DriversroozbehxoxÎncă nu există evaluări

- Advanced MOSFET for Power ApplicationsDocument7 paginiAdvanced MOSFET for Power ApplicationsLeonardo NavarroÎncă nu există evaluări

- 5Q1265RFDocument16 pagini5Q1265RFAron Indra Lezcano GalvezÎncă nu există evaluări

- Features Description: Sbas090B - September 2000 - Revised May 2002Document17 paginiFeatures Description: Sbas090B - September 2000 - Revised May 2002alaska112Încă nu există evaluări

- LMC64821 NDocument22 paginiLMC64821 NLucaDirafÎncă nu există evaluări

- 5M0380RDocument20 pagini5M0380RGenaro Santiago MartinezÎncă nu există evaluări

- THS4051, THS4052 70-Mhz High-Speed Amplifiers: DescriptionDocument25 paginiTHS4051, THS4052 70-Mhz High-Speed Amplifiers: DescriptionSaadAhmedBeihaqiÎncă nu există evaluări

- Low Power, +3.3 V, RS-232 Line Drivers/Receivers: F Charge Pump CapacitorsDocument8 paginiLow Power, +3.3 V, RS-232 Line Drivers/Receivers: F Charge Pump Capacitorsmeroka2000Încă nu există evaluări

- MC1458 OnDocument8 paginiMC1458 OnDanteLupuÎncă nu există evaluări

- HS-2420RH - Fast Sample and HolDocument8 paginiHS-2420RH - Fast Sample and HolDeepa DevarajÎncă nu există evaluări

- General Description Features: Bipolar/CMOS/DMOSDocument13 paginiGeneral Description Features: Bipolar/CMOS/DMOSjavierrincon800Încă nu există evaluări

- Tle2426 High Precision Virtual GroundDocument29 paginiTle2426 High Precision Virtual GroundgofuckingdieÎncă nu există evaluări

- AD8561Document11 paginiAD8561ΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣÎncă nu există evaluări

- Nte 4053Document4 paginiNte 4053Codinasound CaÎncă nu există evaluări

- Data SheetDocument10 paginiData SheetAnonymous phg4RBÎncă nu există evaluări

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDe la EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsÎncă nu există evaluări

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Încă nu există evaluări

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Evaluare: 2.5 din 5 stele2.5/5 (3)

- 110 Waveform Generator Projects for the Home ConstructorDe la Everand110 Waveform Generator Projects for the Home ConstructorEvaluare: 4 din 5 stele4/5 (1)

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsDe la EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsEvaluare: 3.5 din 5 stele3.5/5 (6)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1De la EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Evaluare: 4.5 din 5 stele4.5/5 (3)

- Tl-wr1043nd v1 User GuideDocument124 paginiTl-wr1043nd v1 User GuideroblasarÎncă nu există evaluări

- T BJT - TIP41C - TIP42C - Power - BJTs (Sonder Pinout)Document4 paginiT BJT - TIP41C - TIP42C - Power - BJTs (Sonder Pinout)Ludwig SchmidtÎncă nu există evaluări

- T BJT PNP - 2n4403Document7 paginiT BJT PNP - 2n4403Ludwig SchmidtÎncă nu există evaluări

- T BJT - Tip41 - Tip42 (Met Pinout)Document4 paginiT BJT - Tip41 - Tip42 (Met Pinout)Ludwig SchmidtÎncă nu există evaluări

- Router Wlan Gbit Tl-wr1043nd - v1 - DatasheetDocument3 paginiRouter Wlan Gbit Tl-wr1043nd - v1 - DatasheetLudwig SchmidtÎncă nu există evaluări

- SOUND CARD - Sblive24 Sound Blaster Live! 24-Bit ExternalDocument2 paginiSOUND CARD - Sblive24 Sound Blaster Live! 24-Bit ExternalLudwig SchmidtÎncă nu există evaluări

- T Fet N - Bf245a-B-c - 2 - PhilipsDocument12 paginiT Fet N - Bf245a-B-c - 2 - PhilipsLudwig SchmidtÎncă nu există evaluări

- 2n7000 PDFDocument7 pagini2n7000 PDFNuraniIndahSÎncă nu există evaluări

- Sound Card - Emagic A 62 enDocument84 paginiSound Card - Emagic A 62 enLudwig SchmidtÎncă nu există evaluări

- BF245BDocument4 paginiBF245BilanigalÎncă nu există evaluări

- Sound Card - Sound Blaster X-Fi Sb0679 Rev1.0Document5 paginiSound Card - Sound Blaster X-Fi Sb0679 Rev1.0Ludwig SchmidtÎncă nu există evaluări

- R POT - Insulated Shaft Potentiometer RK09K+RK09D Series - 0900766b80f4c571Document7 paginiR POT - Insulated Shaft Potentiometer RK09K+RK09D Series - 0900766b80f4c571Ludwig SchmidtÎncă nu există evaluări

- Transistor NPN 2n222aDocument8 paginiTransistor NPN 2n222aRoberto Eduardo Tenorio RamosÎncă nu există evaluări

- Reg - LM2931Document18 paginiReg - LM2931Ludwig SchmidtÎncă nu există evaluări

- Switch Tact Mic B1736 ++ Me249-020Document1 paginăSwitch Tact Mic B1736 ++ Me249-020Ludwig SchmidtÎncă nu există evaluări

- PICkit 3 User Guide 51795ADocument98 paginiPICkit 3 User Guide 51795AJack Liddle100% (1)

- PLUG DC Mantech Connectors ME249-098Document1 paginăPLUG DC Mantech Connectors ME249-098Ludwig SchmidtÎncă nu există evaluări

- MC78XX/LM78XX/MC78XXA: 3-Terminal 1A Positive Voltage RegulatorDocument28 paginiMC78XX/LM78XX/MC78XXA: 3-Terminal 1A Positive Voltage Regulatorapi-19786583Încă nu există evaluări

- Amplifiers and ComparatorsDocument11 paginiAmplifiers and Comparatorshoang_tuanÎncă nu există evaluări

- OpAmp - LF12741 - NatSemDocument13 paginiOpAmp - LF12741 - NatSemLudwig SchmidtÎncă nu există evaluări

- Optical Distance Sensor - GP2Y0D810Z0F Gp2y0d810z - eDocument9 paginiOptical Distance Sensor - GP2Y0D810Z0F Gp2y0d810z - eLudwig SchmidtÎncă nu există evaluări

- LM318HDocument19 paginiLM318HAlberto MarsicoÎncă nu există evaluări

- LM101ADocument20 paginiLM101AAna MelendezÎncă nu există evaluări

- OpAmp - LF451Document8 paginiOpAmp - LF451Ludwig SchmidtÎncă nu există evaluări

- LM124/LM224/LM324/LM2902 Low Power Quad Operational AmplifiersDocument21 paginiLM124/LM224/LM324/LM2902 Low Power Quad Operational Amplifiersapple.scotch.fool3550Încă nu există evaluări

- OpAmp - LF12741 - NatSemDocument13 paginiOpAmp - LF12741 - NatSemLudwig SchmidtÎncă nu există evaluări

- OpAmp - LM308AN - National Semiconductor - 49173 - DSDocument9 paginiOpAmp - LM308AN - National Semiconductor - 49173 - DSLudwig SchmidtÎncă nu există evaluări

- OpAmp - LM308AN - MotorolaDocument9 paginiOpAmp - LM308AN - MotorolaLudwig SchmidtÎncă nu există evaluări

- Of RT) : SL - No. (Z) (7) - (8) )Document15 paginiOf RT) : SL - No. (Z) (7) - (8) )RoshniÎncă nu există evaluări

- Pspice Vs MatlabDocument5 paginiPspice Vs MatlabAhmad ElsheemyÎncă nu există evaluări

- Tina Manual PDFDocument20 paginiTina Manual PDFNurhanaÎncă nu există evaluări

- MCP6022Document34 paginiMCP6022Михаил МалсюковÎncă nu există evaluări

- ECE429 Laboratory 3 Inverter Layout: Prasanna N A20489739 21/09/2021Document14 paginiECE429 Laboratory 3 Inverter Layout: Prasanna N A20489739 21/09/2021Prasanna NalawarÎncă nu există evaluări

- Ece - 311 LabDocument148 paginiEce - 311 LabSelva RajuÎncă nu există evaluări

- Nutri-Pot Recipe BookDocument150 paginiNutri-Pot Recipe Bookharitha60% (5)

- Introduction To The SkyWater PDKDocument96 paginiIntroduction To The SkyWater PDKPhạm Đức ThuậnÎncă nu există evaluări

- Hari Nayak:: Indian CuisineDocument3 paginiHari Nayak:: Indian CuisinerameshnaiduÎncă nu există evaluări

- Spices InfoDocument6 paginiSpices Inforavishri12345Încă nu există evaluări

- SI PI EMI EMC ANSYS Solution PDFDocument49 paginiSI PI EMI EMC ANSYS Solution PDFMaria Lavinia IordacheÎncă nu există evaluări

- Module3 - SPICE and CMOS VTCDocument23 paginiModule3 - SPICE and CMOS VTCdilshan singhÎncă nu există evaluări

- Herbkraft Seasoning and Spice MixesDocument19 paginiHerbkraft Seasoning and Spice MixesvishalÎncă nu există evaluări

- GB 2760-2014 Food Additive Standard Auto-DeliveredDocument66 paginiGB 2760-2014 Food Additive Standard Auto-Deliveredchristy SimanjuntakÎncă nu există evaluări

- HDMI Cable Modeling and Analysis With TDR DataDocument9 paginiHDMI Cable Modeling and Analysis With TDR DataAmmar AbdullahÎncă nu există evaluări

- Bangladeshi spices listDocument7 paginiBangladeshi spices listalÎncă nu există evaluări

- Spices - The True Flavor of InnovationDocument47 paginiSpices - The True Flavor of InnovationFazuldeen Sirajudeen100% (1)

- Pdfcoffeecom - Jamie Oliver Recipebook PDF Free - 230911 - 232732Document36 paginiPdfcoffeecom - Jamie Oliver Recipebook PDF Free - 230911 - 232732taneaÎncă nu există evaluări

- Coustomer Price List-2023Document20 paginiCoustomer Price List-2023RamÎncă nu există evaluări

- CMOS Design Delay OptimizationDocument22 paginiCMOS Design Delay OptimizationSuraj KumarÎncă nu există evaluări

- Equivalent SPICE Circuits With Guaranteed Passivity From Nonpassive ModelsDocument8 paginiEquivalent SPICE Circuits With Guaranteed Passivity From Nonpassive ModelsAnonymous rsGzBBiqkÎncă nu există evaluări

- Electrical Engineering Freshmen PracticumDocument9 paginiElectrical Engineering Freshmen Practicumdaboa614Încă nu există evaluări

- Shakthi MasalaDocument8 paginiShakthi MasalaSreejith C VarmaÎncă nu există evaluări

- The Plan Vegetarian Pescatarian Fall Women 2020Document25 paginiThe Plan Vegetarian Pescatarian Fall Women 2020Codigos Graficos HuejotzingoÎncă nu există evaluări

- By Kate Scarlata MPH, RDN, FODMAP & IBS Expert: FruitDocument1 paginăBy Kate Scarlata MPH, RDN, FODMAP & IBS Expert: FruitTri SulistiyawatiÎncă nu există evaluări

- CMOS Digital Integrated Circuits: Lec 5 SPICE Modeling of MOSFETDocument16 paginiCMOS Digital Integrated Circuits: Lec 5 SPICE Modeling of MOSFETNIET14Încă nu există evaluări

- 6th STD English 1st Term Notes QuestionsDocument26 pagini6th STD English 1st Term Notes QuestionsBharath KumarÎncă nu există evaluări

- K0518Document36 paginiK0518tyutyuÎncă nu există evaluări

- Voltus-Fi Custom Power Integrity Solution - Electromigration and IR Drop at The Transistor Level - Industry Insights - Cadence Blogs - Cadence Community PDFDocument3 paginiVoltus-Fi Custom Power Integrity Solution - Electromigration and IR Drop at The Transistor Level - Industry Insights - Cadence Blogs - Cadence Community PDFSudatta MohantyÎncă nu există evaluări