Documente Academic

Documente Profesional

Documente Cultură

Dual Slope Integrating Type DVM Ece

Încărcat de

వంశీ క్రిష్ణ0 evaluări0% au considerat acest document util (0 voturi)

402 vizualizări7 paginiInstrumentation

Titlu original

DUAL SLOPE INTEGRATING TYPE DVM ~ ECE

Drepturi de autor

© © All Rights Reserved

Formate disponibile

PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentInstrumentation

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

402 vizualizări7 paginiDual Slope Integrating Type DVM Ece

Încărcat de

వంశీ క్రిష్ణInstrumentation

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 7

ECE

Enter search keyword

Tweet 331

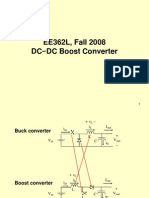

DUAL SLOPE INTEGRATING TYPE DVM

Do you like this story?

Switch connected to +V

M

Once V

M

is connected, the capacitor starts charging linearly then the output at the integrator

decreases linearly. This linearly decreasing ramp is fed to inverting terminal of the zero

crossing detector. Since the input at non inverting terminal is greater than inverting terminal,

it produces a positive going pulse. This positive going pulse makes the gating circuit to start.

Now pulses produced by the clock generator passess through gating circuit and counter count

the number of pulses.

t

V

C

= 1/C I dt

-

t

1

= 1/C V

M

/ R dt

0

= V

M

/ RC ( t

1

0 )

=

V

M

t

1

/RC

= V

M

T

1

/RC (t

1

=T

1

)

V

0

= -V

C

V

0

= - ( V

M

T

1

/RC )

Trending: Bloggermint Blogger Template

Buzz Twitter Facebook RSS Email

Tweet

0

Sponsors

Popular Posts

SUPER MESH ANALYSIS

SUPERMESH: When a current source is

common to two meshes we use the concept

of super mesh. A supermesh is created from

two meshes ...

MOBILITY & CONDUCTIVITY

MOBILITY When an electric field E is applied across a

piece of material, the electrons respond by moving with an

average velocity call...

SUPER NODE analysis

When a voltage source comes in between

two node then these two nodes and the

voltage source form a supernode and we

take this supernod...

DUAL SLOPE INTEGRATING TYPE DVM

Switch connected to +V M Once V M is

connected, the capacitor starts charging

linearly then the output at the integrator

decrea...

DOMINANT POLE

The poles of a system (those closest to the

imaginary axis in the s-plane) give rise to the

longest lasting terms in the transient resp...

SMALL SIGNAL MODEL OF DIODE

Small-signal operation is that a time varying

signal with small amplitude rides on a DC

value that may or may not be large. ...

CAUER FORM 1 LC IMMITTANCE

RC impedance or RL admittance

PROPERTIES OF RC IMPEDANCE OR RL

ADMITTANCE 1)Poles and zeros are

alternating 2) Poles and zeros are simple

and lie on the negat...

HOW TO IDENTIFY THE TYPE OF

FEEDBACK IN OP-AMPS

Let the input terminal to which source is

connected is considered as shunt The

terminal connected to ground at the input is

c...

RC IMPEDANCE FOSTER FORM 1

Home Contact Privacy Policy

Uncategorized Websites Web Design CSS3 Photography Tutorials Wordpress Plugins

Graphs of V

C

and V

0

Let T

1

be the time taken by the capacitor to charge to V

M

ie.,from 0 to t

1

let N

F

be the number of pulses counted during T

1

T

1

= N

F

t

CLK

(t

CLK

= clock period of pulses produced by the clock generator)

When the counter reaches maximum state a reset pulse is produced by the counter which

automatically changes the switch from +V

M

to - V

REF

Switch connected to V

REF

Once V

REF

is connected, the capacitor starts discharging linearly then the output at the

integrator increases linearly. The output of ZCD is still positive, hence gating circuit is on. So

the counter still counts the pulses. When voltage reaches t

2

and crosses zero the input to the

inverting terminal of ZCD is greater than input to the non inverting terminal the output of

ZCD is a negative going pulse, which makes the gating circuit to switch off. At t

2

the capacitor

completely discharges.

Graphs of V

C

and V

0

Let T

2

= t

2

-t

1

be the time taken by the capacitor to discharge completely to zero

Let n be the number of clock pulses during T

2

T

2

= n t

CLK

t

2

V

C

= 1/C I dt + initial voltage

t

1

t

2

= 1/C -V

REF

/ R dt + V

M

T

1

/RC

t

1

Follow Us On Facebook

Grab this Headline Animator

Recent Posts Test

This post was written by: Author Name

Author description goes here. Author description goes here. Follow him on Twitter

0 Responses to DUAL SLOPE INTEGRATING TYPE DVM

Post a Comment

NEWER POST OLDER POST HOME

= - V

REF

/ RC ( t

2

t

1

) + V

M

T

1

/RC

=- V

REF

/ RC ( T

2

) + V

M

T

1

/RC ( t2 t1 = T2 )

V

0

= -V

C

V

0

= V

REF

/ RC ( T

2

) - V

M

T

1

/RC

At t

2

,V

0

=0

V

REF

/ RC ( T

2

) - V

M

T

1

/RC =0

V

REF

/ RC ( T

2

) = V

M

T

1

/RC

Substituting the values of T

1

= N

F

t

CLK

and T

2

= n t

CLK

we get

V

M

= (n V

REF

)/ N

F

Features

1) Conversion time

t

CONV

= T1 + T2

= N

F

t

CLK

+ n t

CLK

Since Conversion time of this DVM is long and variable its speed is less

2) Noise rejection

As we are integrating voltage for time duration we are calculating true average value. So if an

AC signal or noise is super imposed on V

M

,it will be averaged. Hence effect of noise is less.

Therefore noise rejection is high.

3) Accuracy

As V

M

doesnt depends on R and C accuracy is more

Sample Links

Recent Posts

Followers

Join this site

with Google Friend Connect

Members (15)

Already a member? Sign in

Total Pageviews

42,733

About / Followers

dodododod

Labels

CONTENTS OF EDC (1)

CONTENTS OF EMI (1)

CONTENTS OF NETWORK THEORY (1)

CONTROL SYSTEMS (4)

DIGITAL ELECTRONICS (1)

EDC (13)

EMI (4)

EMTL (1)

GK (1)

NETWORK THEORY (24)

QUESTIONS (11)

Sample Text Link

STUDY GUIDE

TTA

Our Price: Rs.625

Blogger news

Fundamentals of

Electric Circ...

List Price: Rs.550

Our Price: Rs.347

Pages

Home

IES BOOKS

Blogger templates

All Rights Reserved ECE | Blogger Template by Bloggermint Sponsored by Florida Phone Book, Florida Accountants, Optician Jobs

Signals and

Systems

List Price: Rs.495

Our Price: Rs.395

Sample

Principles of

Electromagnetics

List Price: Rs.585

Our Price: Rs.399

Search and Subscribe

FEATURED DEALS

The Online Megastore

Buy Now

Nikon D5100 DSLR

Camera

List Price Rs.32950

Our Price Rs.25690

Powered by Blogger.

Pages - Menu

Home

IES BOOKS

Blog Archive

2013 (67)

June (2)

May (6)

April (9)

March (24)

GATE PROBLEM

RC FOSTER FORM - 2

RC IMPEDANCE FOSTER FORM 1

CAUER FORM 2 LC IMMITTANCE

CAUER FORM 1 LC IMMITTANCE

FOSTER FORM 2 FOR LC

IMMITTANCE

FOSTER FORM I FOR LC

IMMITTANCE

RL IMPEDANCE OR RC

ADMITTANCE

RC impedance or RL admittance

DUAL SLOPE INTEGRATING TYPE

DVM

CONTENTS OF EDC

CONTENT OF EMI

RAMP TYPE DVM

DEFINITIONS IN A WAVE FORM

READ OUTS OF DVMs

INTRODUCTION TO DVMs

MILLMANS THEOREM

RECIPROCITY THEOREM

MAXIMUM POWER TRANSFER

THEVENIN TYPE 3

THEVENIN TYPE-2

THEVENIN AND NORTON

EQUIVALENT

QUESTIONS ON TRANSISTOR

TYPES OF CIRCUITS IN

THEVENINS-1

February (26)

About Me

Harish PECHETTI

Follow

29

View my complete profile

Arsip Blog

2013 (67)

June (2)

May (6)

April (9)

March (24)

GATE PROBLEM

RC FOSTER FORM - 2

RC IMPEDANCE FOSTER FORM 1

CAUER FORM 2 LC IMMITTANCE

CAUER FORM 1 LC IMMITTANCE

FOSTER FORM 2 FOR LC

IMMITTANCE

FOSTER FORM I FOR LC

IMMITTANCE

RL IMPEDANCE OR RC

ADMITTANCE

RC impedance or RL admittance

DUAL SLOPE INTEGRATING TYPE

DVM

CONTENTS OF EDC

CONTENT OF EMI

RAMP TYPE DVM

DEFINITIONS IN A WAVE FORM

READ OUTS OF DVMs

INTRODUCTION TO DVMs

MILLMANS THEOREM

RECIPROCITY THEOREM

MAXIMUM POWER TRANSFER

THEVENIN TYPE 3

THEVENIN TYPE-2

THEVENIN AND NORTON

EQUIVALENT

QUESTIONS ON TRANSISTOR

TYPES OF CIRCUITS IN

THEVENINS-1

February (26)

Blogger Templates

EXAMPLE ON SUPER HETERODYNE

RECEIVER

SUPER HETERODYNE RECEIVER

WAVE POLARIZATION

S-ar putea să vă placă și

- Daycounter Inc - Snubber Circuit Design CalculatorsDocument5 paginiDaycounter Inc - Snubber Circuit Design CalculatorsLaercio Marques100% (1)

- Snubber Circuit Design CalculatorsDocument3 paginiSnubber Circuit Design CalculatorsteomondoÎncă nu există evaluări

- RC Circuit Response Introduction & TheoryDocument6 paginiRC Circuit Response Introduction & TheoryMuhammad FarooqÎncă nu există evaluări

- V T) V I T) V R V R: Boost ConverterDocument3 paginiV T) V I T) V R V R: Boost Converterduppal35Încă nu există evaluări

- Lectures 5 To 7 - Diode CircuitsDocument14 paginiLectures 5 To 7 - Diode CircuitsAniketsingh MundlothÎncă nu există evaluări

- Chapter Two: Line or Naturally Commutated ConvertersDocument32 paginiChapter Two: Line or Naturally Commutated ConvertersMichael Adu-boahenÎncă nu există evaluări

- Power Electronics 1-2015bjrDocument80 paginiPower Electronics 1-2015bjrNurAdiFirawanÎncă nu există evaluări

- Snubber PDFDocument5 paginiSnubber PDFJ Milk SilvaÎncă nu există evaluări

- DC-DC BoostDocument21 paginiDC-DC BoostvinaykumaarÎncă nu există evaluări

- Interconnect 03 - Interconnect ModelingDocument31 paginiInterconnect 03 - Interconnect ModelingManar MansourÎncă nu există evaluări

- Variable DC Power Using Full Bridge ConverterDocument6 paginiVariable DC Power Using Full Bridge Convertergoten10daÎncă nu există evaluări

- Boost Converter PrinciplesDocument7 paginiBoost Converter PrinciplesAhmed ArfaÎncă nu există evaluări

- Aplikasi Op Amp: Pertemuan Ke 10 Kuliah Elektronika Dasar Prodi Teknik Elektro Jteti-Ugm Mei 2010Document21 paginiAplikasi Op Amp: Pertemuan Ke 10 Kuliah Elektronika Dasar Prodi Teknik Elektro Jteti-Ugm Mei 2010Adri Muhaimin AfifÎncă nu există evaluări

- Impatt DiodeDocument15 paginiImpatt DiodeGhulam ShabbirÎncă nu există evaluări

- The Cmos Inverter: OutlineDocument20 paginiThe Cmos Inverter: OutlinehappyharrÎncă nu există evaluări

- IMPATT Diode: Name:-Tuhin Dutta Stream: - ECE Roll: 1011Document16 paginiIMPATT Diode: Name:-Tuhin Dutta Stream: - ECE Roll: 1011Nava KrishnanÎncă nu există evaluări

- Introduction To Digital Modulation & Demodulation TechniquesDocument116 paginiIntroduction To Digital Modulation & Demodulation TechniqueswooDefyÎncă nu există evaluări

- Am Modulator (Generation of Am-Dsbfc) : It Is Used To Generate An Amplitude Modulated Wave. ClassificationDocument9 paginiAm Modulator (Generation of Am-Dsbfc) : It Is Used To Generate An Amplitude Modulated Wave. Classificationsujithaa13Încă nu există evaluări

- A Unified Model For The ZVS DC-DC Converters With Active ClampDocument31 paginiA Unified Model For The ZVS DC-DC Converters With Active ClampTirthankar MohantyÎncă nu există evaluări

- Unit 3Document23 paginiUnit 3Prema ElizabethÎncă nu există evaluări

- DC DC BoostDocument21 paginiDC DC BoosttrshaaaÎncă nu există evaluări

- Exp 2Document6 paginiExp 2College ISMÎncă nu există evaluări

- Class19 Crosstalk OverviewDocument32 paginiClass19 Crosstalk OverviewNag ArjunÎncă nu există evaluări

- Design Considerations For An LLC Resonant ConverterDocument29 paginiDesign Considerations For An LLC Resonant Converterbacuoc.nguyen356Încă nu există evaluări

- Generation of High Voltage Using Cockcroft-Walton Voltage Multiplier CircuitDocument18 paginiGeneration of High Voltage Using Cockcroft-Walton Voltage Multiplier Circuitroute2rahulÎncă nu există evaluări

- 1.2 Analog Data SignalDocument38 pagini1.2 Analog Data SignalTran Hoang AnhÎncă nu există evaluări

- IMPATT Diode: Name:-Tarun Kumar AP, ECE DeptDocument16 paginiIMPATT Diode: Name:-Tarun Kumar AP, ECE DeptDr-Tarun ParasharÎncă nu există evaluări

- Module-Iii Syllabus:: Transient Behavior and Initial Conditions: Behavior of Circuit Elements Under SwitchingDocument32 paginiModule-Iii Syllabus:: Transient Behavior and Initial Conditions: Behavior of Circuit Elements Under Switchinglohith sÎncă nu există evaluări

- Chap 2 Erickson Fundamentals of Power Electronics PDFDocument45 paginiChap 2 Erickson Fundamentals of Power Electronics PDFhenrypatriciomunoz1Încă nu există evaluări

- Erickson Slides DC-DC CCMDocument45 paginiErickson Slides DC-DC CCMAlberto Valenzuela OrtizÎncă nu există evaluări

- Principles of Steady-State Converter AnalysisDocument45 paginiPrinciples of Steady-State Converter AnalysisTrung Hiếu ETÎncă nu există evaluări

- Dual ConverterDocument16 paginiDual ConverterUdayakumar VengatesanÎncă nu există evaluări

- Design of A Non-Ideal Buck ConverterDocument13 paginiDesign of A Non-Ideal Buck ConverterJames Xgun100% (1)

- ZCS-PWM Converter For Reducing Switching Losses: Subi SDocument7 paginiZCS-PWM Converter For Reducing Switching Losses: Subi SInternational Organization of Scientific Research (IOSR)Încă nu există evaluări

- CH 2 SlideDocument45 paginiCH 2 Slidemukesh00007Încă nu există evaluări

- Transformer StudiesDocument52 paginiTransformer StudiesSyed JaveedÎncă nu există evaluări

- 10 InvertersDocument136 pagini10 InverterszapzahtÎncă nu există evaluări

- Buck BoostDocument5 paginiBuck BoostSyed Zeeshan Ali ZaidiÎncă nu există evaluări

- Sandy 123Document9 paginiSandy 123Sandy RonaldoÎncă nu există evaluări

- Final Review PDFDocument19 paginiFinal Review PDFurfriend_jjn05Încă nu există evaluări

- PDC Lab Updated 1Document63 paginiPDC Lab Updated 1deepa reddyÎncă nu există evaluări

- Project 6Document21 paginiProject 6karansahniÎncă nu există evaluări

- Dual Transistor Multivariate Circuit.Document3 paginiDual Transistor Multivariate Circuit.sbpatel123Încă nu există evaluări

- Astable Multivibrator Using TransistorsDocument10 paginiAstable Multivibrator Using TransistorsGangireddy SanjeevÎncă nu există evaluări

- Lect 3Document42 paginiLect 3Supriya Rakshit0% (1)

- Cs Lab Manual in PDFDocument56 paginiCs Lab Manual in PDFvasukonetiÎncă nu există evaluări

- Ac Fundamnetals ManualDocument12 paginiAc Fundamnetals ManualRaj Mehra MeharÎncă nu există evaluări

- CukonverterDocument30 paginiCukonverterPowersavvyÎncă nu există evaluări

- The Cmos Inverter: Slides Adapted From: N. Weste, D. Harris, CMOS VLSI Design,, 3/e, 2004Document40 paginiThe Cmos Inverter: Slides Adapted From: N. Weste, D. Harris, CMOS VLSI Design,, 3/e, 2004SrasVelÎncă nu există evaluări

- Where Do You Need This?: 1.maintenance Engineer 2.energy Management System 3.energy ManagerDocument46 paginiWhere Do You Need This?: 1.maintenance Engineer 2.energy Management System 3.energy Managerconference RequirementsÎncă nu există evaluări

- Eee 513 Lecture Module IiDocument30 paginiEee 513 Lecture Module Iistephenhuncho22Încă nu există evaluări

- PDC Lab ManualDocument33 paginiPDC Lab ManualBhanu SriÎncă nu există evaluări

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Încă nu există evaluări

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Evaluare: 2.5 din 5 stele2.5/5 (3)

- Feynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterDe la EverandFeynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterÎncă nu există evaluări

- Giving Research Presentations: Stephanie PfirmanDocument41 paginiGiving Research Presentations: Stephanie PfirmanJohn BaptisteÎncă nu există evaluări

- DC-DC Converters - Jaycar Tech NotesDocument5 paginiDC-DC Converters - Jaycar Tech Noteskimbalsummers801Încă nu există evaluări

- 16.4 000Document18 pagini16.4 000Saichung DewashisÎncă nu există evaluări

- Highly Resonant Power Transfer Kesler Witricity 2013Document32 paginiHighly Resonant Power Transfer Kesler Witricity 2013వంశీ క్రిష్ణÎncă nu există evaluări

- Tech SeminarDocument18 paginiTech SeminarAkshay AringaleÎncă nu există evaluări

- Highly Resonant Power Transfer Kesler Witricity 2013Document32 paginiHighly Resonant Power Transfer Kesler Witricity 2013వంశీ క్రిష్ణÎncă nu există evaluări

- CSS - Verbal Communication SkillsDocument41 paginiCSS - Verbal Communication Skillsవంశీ క్రిష్ణÎncă nu există evaluări

- How To Give A Seminar-2Document9 paginiHow To Give A Seminar-2వంశీ క్రిష్ణÎncă nu există evaluări

- Public Speaking and The Communication ProcessDocument28 paginiPublic Speaking and The Communication Processవంశీ క్రిష్ణ100% (1)

- Group DiscussionDocument20 paginiGroup Discussionsrivan60% (5)

- How To Give A Seminar-1Document12 paginiHow To Give A Seminar-1వంశీ క్రిష్ణÎncă nu există evaluări

- TCP 3Document42 paginiTCP 3nmpmohanÎncă nu există evaluări

- How To Improve Communication SkillDocument28 paginiHow To Improve Communication Skillవంశీ క్రిష్ణÎncă nu există evaluări

- Group CommunicationDocument14 paginiGroup Communicationవంశీ క్రిష్ణÎncă nu există evaluări

- Chapter 2: 8051 Microcontroller Architecture: 2.1 What Is 8051 Standard?Document46 paginiChapter 2: 8051 Microcontroller Architecture: 2.1 What Is 8051 Standard?వంశీ క్రిష్ణÎncă nu există evaluări

- Art of Debating 09Document23 paginiArt of Debating 09వంశీ క్రిష్ణÎncă nu există evaluări

- Basic Debating SkillsDocument20 paginiBasic Debating Skillsవంశీ క్రిష్ణÎncă nu există evaluări

- Writing Linux Device Drivers in Assembly Language (En - US)Document116 paginiWriting Linux Device Drivers in Assembly Language (En - US)api-26866651100% (1)

- A Real-Time Linux: Email Address: The Research Described Here Was Partially Funded Under NSF Grant CCR-9409454Document9 paginiA Real-Time Linux: Email Address: The Research Described Here Was Partially Funded Under NSF Grant CCR-9409454వంశీ క్రిష్ణÎncă nu există evaluări

- BSD IPC ManualDocument246 paginiBSD IPC Manualవంశీ క్రిష్ణÎncă nu există evaluări

- Tenor SNMP Implementation: © 2005 Quintum Technologies, IncDocument26 paginiTenor SNMP Implementation: © 2005 Quintum Technologies, Incవంశీ క్రిష్ణÎncă nu există evaluări

- C Plus Vs CDocument12 paginiC Plus Vs CGilvanLatreilleÎncă nu există evaluări

- Java Interview Questions and AnswersDocument3 paginiJava Interview Questions and AnswersUrvish ShahÎncă nu există evaluări

- Real-Time and Embedded GuideDocument177 paginiReal-Time and Embedded Guideapi-3827556100% (3)

- TCP IP Protocol Definitions SuiteDocument42 paginiTCP IP Protocol Definitions Suitejwu_cool2143Încă nu există evaluări

- PPP 1Document32 paginiPPP 1వంశీ క్రిష్ణÎncă nu există evaluări

- PPPDocument110 paginiPPPవంశీ క్రిష్ణÎncă nu există evaluări

- Extending Point-To-Point Protocol For Integrated Services: Andrei Gurtov Research Seminar On Ip QosDocument18 paginiExtending Point-To-Point Protocol For Integrated Services: Andrei Gurtov Research Seminar On Ip Qosవంశీ క్రిష్ణÎncă nu există evaluări

- ,3, 36Zlwfklqj 6Zlwfklqj3Urwrfrov 3urwrfrovDocument4 pagini,3, 36Zlwfklqj 6Zlwfklqj3Urwrfrov 3urwrfrovవంశీ క్రిష్ణÎncă nu există evaluări

- Test Report - Linearity Tests of RF DevicesDocument9 paginiTest Report - Linearity Tests of RF DevicespippopaperimoÎncă nu există evaluări

- Vienna in Your PocketDocument68 paginiVienna in Your PocketccoccinellaÎncă nu există evaluări

- The Life & Musical Career of Annette Hanshaw (Monica Raney & Amy Land)Document3 paginiThe Life & Musical Career of Annette Hanshaw (Monica Raney & Amy Land)scribdaccountÎncă nu există evaluări

- MP Marites Vol 74 (Small)Document4 paginiMP Marites Vol 74 (Small)carl joseph braza tapayÎncă nu există evaluări

- The Black Culture IndustryDocument217 paginiThe Black Culture IndustryAnietieÎncă nu există evaluări

- TMEG 211 Teaching MUSICDocument8 paginiTMEG 211 Teaching MUSICAngel ChiutenaÎncă nu există evaluări

- $exandru Nicolici-Astrologia Natala 10Document5 pagini$exandru Nicolici-Astrologia Natala 10Andreea RadulescuÎncă nu există evaluări

- Libro InglésDocument143 paginiLibro Ingléspasotogo29100% (3)

- 05 May 1968 Orr Vertical Corta DobladaDocument100 pagini05 May 1968 Orr Vertical Corta DobladaNestor Alberto EscalaÎncă nu există evaluări

- Roar Stylistic AnalysisDocument12 paginiRoar Stylistic AnalysisJoel Igno TadeoÎncă nu există evaluări

- Pokarekare Ana Mori TraditionalDocument3 paginiPokarekare Ana Mori TraditionalcarmenÎncă nu există evaluări

- TV Panasonic TC-20KL05P - Chassis GP31 PDFDocument31 paginiTV Panasonic TC-20KL05P - Chassis GP31 PDFEduardo SierraÎncă nu există evaluări

- January 31, 2020 Strathmore TimesDocument16 paginiJanuary 31, 2020 Strathmore TimesStrathmore TimesÎncă nu există evaluări

- English 5 Sound Devices: The BellsDocument4 paginiEnglish 5 Sound Devices: The BellsEdith LopoÎncă nu există evaluări

- W5 20190214 Group1 MatlabreportDocument18 paginiW5 20190214 Group1 MatlabreportVõ Hoàng ChươngÎncă nu există evaluări

- I Am The WalrusDocument2 paginiI Am The WalrusDaniel BlandonÎncă nu există evaluări

- New York Bus MapDocument1 paginăNew York Bus MapSzabÎncă nu există evaluări

- Happy Brass QuintetDocument11 paginiHappy Brass QuintetadripetÎncă nu există evaluări

- High-Efficiency Matching Network For Rf-Driven Ion SourcesDocument3 paginiHigh-Efficiency Matching Network For Rf-Driven Ion SourcesAmador Garcia IIIÎncă nu există evaluări

- Tryout TOEFL LigamersDocument32 paginiTryout TOEFL LigamersDipa AndiÎncă nu există evaluări

- Unit Plan - Strange HumorsDocument10 paginiUnit Plan - Strange Humorsapi-255265303Încă nu există evaluări

- 147 L020 PDFDocument6 pagini147 L020 PDFPiyush ChauhanÎncă nu există evaluări

- Fiche Technique CobhamDocument5 paginiFiche Technique CobhamFred BacÎncă nu există evaluări

- 7SJ80xx TechDaten V0470 EnUSDocument80 pagini7SJ80xx TechDaten V0470 EnUSPrabhu ChandranÎncă nu există evaluări

- A Grammar of Tamashek (Tuareg of Mali)Document765 paginiA Grammar of Tamashek (Tuareg of Mali)Guldre1okk75% (4)

- Face Your Fears: From Crazy Ex-Girlfriend Season 1Document11 paginiFace Your Fears: From Crazy Ex-Girlfriend Season 1nitsuj888Încă nu există evaluări

- Ginoo Maluoy Ka: para Sa Panahon Sang KwaresmaDocument1 paginăGinoo Maluoy Ka: para Sa Panahon Sang KwaresmaJomel GarciaÎncă nu există evaluări

- Quantum Series HandbookDocument370 paginiQuantum Series HandbookthitsanÎncă nu există evaluări

- Openbox X800 User ManualDocument30 paginiOpenbox X800 User Manualdragon250% (1)

- Acting The Metaphor The Laban-Malmgren System of Movement Psychology and Character AnalysisDocument31 paginiActing The Metaphor The Laban-Malmgren System of Movement Psychology and Character AnalysisJenna Zhu100% (1)