Documente Academic

Documente Profesional

Documente Cultură

ESM740G Tiristor

Încărcat de

josenicolas120000 evaluări0% au considerat acest document util (0 voturi)

67 vizualizări2 paginiPhase detector 1 compares off-air line sync pulses with divided-by-32 output from the 500kHz oscillator. Second phase detector compares timing of divided down output with line output transformer derived pulses. The output from this detector is applied to the line drive pulse generator circuit. This enables the start of the scan and thus the horizontal picture position to. Be set.

Descriere originală:

Titlu original

ESM740G-tiristor

Drepturi de autor

© © All Rights Reserved

Formate disponibile

PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentPhase detector 1 compares off-air line sync pulses with divided-by-32 output from the 500kHz oscillator. Second phase detector compares timing of divided down output with line output transformer derived pulses. The output from this detector is applied to the line drive pulse generator circuit. This enables the start of the scan and thus the horizontal picture position to. Be set.

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

67 vizualizări2 paginiESM740G Tiristor

Încărcat de

josenicolas12000Phase detector 1 compares off-air line sync pulses with divided-by-32 output from the 500kHz oscillator. Second phase detector compares timing of divided down output with line output transformer derived pulses. The output from this detector is applied to the line drive pulse generator circuit. This enables the start of the scan and thus the horizontal picture position to. Be set.

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 2

The off-air line sync pulses and the divided-by-32

output from the 500kHz oscillator are compared in phase

detector 1, which controls the 500kHz oscillator. Thus all

the outputs from the dividers are synchronised to the

incoming line sync pulses. This phase detector has time-

constant switching, operated by a voltage supplied to pin

23 by the central processor chip IR01

-

programme

selectors 8, 9 and 10 are reserved for AV use. The chip

also switches to the AV time-constant when there is no or

a very noisy video signal.

The second phase detector compares the timing of the

divided down output from the 500kHz oscillator with line

output transformer derived pulses which are fed in at pin

12, arriving at the phase detector via the sandcastle pulse

generator circuit. The output from this detector is applied

to the line drive pulse generator circuit. This enables the

start of the scan and thus the horizontal picture position to.

be set. There is also a d.c. input from the line shift

control, giving manual adjustment of the picture within

the raster. During normal operation the line drive pulse

generator stage produces from the output of the sawtooth

line oscillator a constant 26psec wide pulse which is

passed via the output stage to pin 10. At start up however

the pulse width is narrower, giving a soft-start action to

prevent overloading the line output transistor.

The output from the saMooth line oscillator is also

applied to the chopper drive modulator and the field drive

modulator. For chopper pulse width modulation the

modulator stage is under the control of an operational

amplifier whose inverting input is taken to the slider of the

set h.t. control. As previously mentioned, the mark-space

ratio of the chopper drivc pulses is reduced at switch on to

give a soft-start action.

The field drive system is a bit more elaborate. A field-

frequency sawtooth oscillator controlled by the vertical

timing circuit provides, at pin 3, an output for the EW

correction circuit in the TDA4950 chip IG01. This output

is also shaped and fed back to pin 2, one of the inputs of

another operational amplifier, together with a feedback

waveform from the field output stage. The sawtooth

output from this operational amplifier is fed, along with

the output from the sawtooth line oscillator, to the field

drive modulator circuit. The result of mixing these two

signals is a pulse-width modulated output, i.e. the output

from the field drive modulator consists of line-frequency

pulses modulated at field rate. At the beginning of the

field scan the pulses are narrow. They gradually increase

in width during the field scan. Those familiar with the old

Philips G1l chassis will recognise this as class D drive. We

shall see how it's used shortly.

Interchannel sound muting is based on detecting the

presence of off-air sync pulses. Pin 24 goes low when a

video signal is present, rising to 6.7V in the absence of a

video signal to activate the sound muting system.

The TDA2029C incorporates a safety circuit which

shuts down the line, field and chopper drive outputs in the

event of excessive output voltages in the line output or

chopper circuits. Voltage sensing is at pin 28, which is

normally at 0V and rises to about 6V in the trip condition.

Line Deflection

The line driver and output stages follow conventional

practice. A BU508A or S2fil0A3 acts as the line output

transistor (TL31). Taps and windings on the line output

transformer provide zffiV, 23V and 13V lines and the

c.r.t.'s heater supply. The diode-split winding provides the

680

e.h.t. and the input to the combined focus/first anode

control unit on the c.r.t. base panel. A further winding

provides current for the thyristor field output stage.

Field Deflection

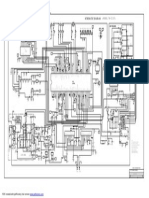

Field scanning is controlled by an ESM740G thyristor,

DL21, whose gate is coupled via RL21 to IL14's field

output pin 4, which as we have seen produces a pulse-

width modulated output. The arrangement is shown in

Fi g. 7.

The reason for using a winding on the line output

transformer as a load for DL2l is the need to be able to

switch it off. As you will doubtless know, a thyristor can

be switched on by applying a positive-going pulse to its

gate but will switch off only when the voltage across it is

reduced to zero. The line flyback pulses picked up by

winding 4-11 of the line output transformer switch DL22

on, with the result that DL21 is switched off once per line.

The pulse-width modulation applied to DL21's gate

switches it on once per line at a progressively earlier point

as the field scan progresses. Since the impedance of the

field scan coils at line frequency is large they have an

integrating effect on the field scan current. In this way the

steadily increasing current pulses are smoothed to produce

a ramp. Current flows from chassis via DL2l, LL32,

winding 4-11 on the line output transformer, RL50, the

field scan coils and RF17 to the 23V supply.

During the field flyback period DL21 remains cut off

and DL22 acts as a clamp. The voltage developed across

CL54 rises to some 200V and the direction of current

through the scan coils is reversed.

RF17 is included to provide a feedback signal which is

tapped from the height control and fed back to pin 2 of

TLI4.

EW Correction

A conventional diode modulator arrangement is used

for EW correction, with the driver and waveform shaping

circuitry incorporated in a TDA4950 chip (IG01). Fig. 8

shows the circuitry here. The field-frequency sawtooth

waveform fed into pin 1 is converted to a parabolic

waveform by the first stage, a Miller integrator. PG02

adjusts the tilt of the parabolic waveform to provide

keystone correction. Overall feedback is applied to pin 7

to control the gain of the internal circuitry, PG08 adjust-

ing the degree of pincushion correction provided. An anti-

breathing input from the earthy end of the e.h.t. circuit is

also applied to pin 7. The other input to the operational

amplifier, at pin 8, is fed with a sawtooth waveform

derived from a 50V peak+o-peak pulse obtained from the

line output transformer. This signal is in anti-phase to the

line scan, and as PG12 sets its amplitude this preset

operates as a width control.

NS Correction

With Super-Planar tubes additional S correction plus

pincushion and "gullwing" (or moustache) correction are

required. These are provided by the NS correction cir-

cuitry on board NS5000M.

Text and Graphics

Most receivers that incorporate the ICC5 chassis also

have Fastext and on-screen graphics. A set of three chips

TELEVISION JULY 1989

T

coni r ol

Gat i nq

DUr SeS

Composi te

vids inDst

Fig.7: The field deflection circuit.

provides the Fastext facilities, with a 4-page memory. The

SAA5231 text acquisition chip IV03 feeds an SAA5243

device (IV02) which is dcscribed as a computer-controlled

teletext chip

-

it's controlled by IR01 via the I2C bus.

Captured pages of data are transferred to IV01, a static

RAM (p.PD43&C[5L).IV02 contains a character gener-

ator which provides RGB text signals plus blanking

suitable for text-only, mixed or subtitle operation. The

teletext panel also contains two custom-built chips, IV05

and IV06, which provide synchronised RGB graphics for

user-control information, station identification and the

point-of-sale message.

ln Conclusion

Much has been fitted into this compact chassis by clever

TELEVISION JULY 1989

Sandc asl t e

pul ses

Fig. 8: Circuitry around the TDA4950 chip which controls

the EW diode modulator.

use of conventional and MELF (metal-ended leadless-

frame, i.e. surface mounted) components. Some might

query the return of plug-in modules, but the plug and

socketry is of a high standard and will permit a degree of

panel jockeying

in the event of a bout of technofear. The

performance provided by the chassis should win many

admirers. It's an interesting change from established UK

and Japanese designs.

681

Hori zontal

t hi t t

Fig. 6: Simplified block diagram of the TEA2029C power processor chip.

Wi ndrng

on LOPI

I

I

tt

t

t

I

t

I

PWM fi el d dri ve

l r om l L16

S-ar putea să vă placă și

- MAS Assessment Exam Answer Key SolutionDocument7 paginiMAS Assessment Exam Answer Key SolutionJonalyn JavierÎncă nu există evaluări

- Trend Graphs - Sample AnswerDocument4 paginiTrend Graphs - Sample AnswerannieannsÎncă nu există evaluări

- Chapter SixDocument5 paginiChapter Sixyunus memonÎncă nu există evaluări

- Vital StatisticsDocument35 paginiVital StatisticsRadha100% (1)

- Manual de Servicio Samsung MAX-X55!56!66Document44 paginiManual de Servicio Samsung MAX-X55!56!66Mauro Mangialavori0% (1)

- Measuring Mosfet Curve Tracer PDFDocument11 paginiMeasuring Mosfet Curve Tracer PDFEugene Chew100% (2)

- M113 Service ManualDocument87 paginiM113 Service ManualMISHALSAGARÎncă nu există evaluări

- RPH Sains DLP Y3 2018Document29 paginiRPH Sains DLP Y3 2018Sukhveer Kaur0% (1)

- Active Disturbance Rejection Control for Nonlinear Systems: An IntroductionDe la EverandActive Disturbance Rejection Control for Nonlinear Systems: An IntroductionÎncă nu există evaluări

- Passive HouseDocument16 paginiPassive HouseZarkima RanteÎncă nu există evaluări

- Power Rectifier ASIC ControllerDocument5 paginiPower Rectifier ASIC ControllerQuang TaÎncă nu există evaluări

- Lab 5: Design Single Stage and Telescopic Differential AmplifiersDocument13 paginiLab 5: Design Single Stage and Telescopic Differential AmplifiersTamilinbaaÎncă nu există evaluări

- Toyocom Cristal OscillatorsDocument58 paginiToyocom Cristal Oscillatorsb33g33100% (1)

- C8Samsung: KA2263 Linear Integrated CircuitDocument4 paginiC8Samsung: KA2263 Linear Integrated CircuitHanse69Încă nu există evaluări

- The Phase Control Circuit The TC787Document10 paginiThe Phase Control Circuit The TC787nansusanÎncă nu există evaluări

- Panasonic TX-25lk1p TX-28lk1p Chassis z8Document22 paginiPanasonic TX-25lk1p TX-28lk1p Chassis z8drrebyÎncă nu există evaluări

- TV Sanyo Cm29af8x (La76818)Document34 paginiTV Sanyo Cm29af8x (La76818)deimos1Încă nu există evaluări

- Voltage Controlled Ring OscillatorDocument4 paginiVoltage Controlled Ring OscillatorNurulMaisaraAwangÎncă nu există evaluări

- Analizer EU1KY Var1.2Document13 paginiAnalizer EU1KY Var1.2Augustin SerbanÎncă nu există evaluări

- Bluesky, TV Beko 12.7 Chassis, SMDocument5 paginiBluesky, TV Beko 12.7 Chassis, SMkilol0Încă nu există evaluări

- Autodesk serial numbers and activation keysDocument1 paginăAutodesk serial numbers and activation keysAnamaria IacobÎncă nu există evaluări

- Flair 22d ManualDocument2 paginiFlair 22d ManualArip SaepudinÎncă nu există evaluări

- Asus H61 Common SequenceDocument4 paginiAsus H61 Common SequencesachinÎncă nu există evaluări

- Fitbit Alta TeardownDocument8 paginiFitbit Alta Teardowndorian451Încă nu există evaluări

- Zelio-Logic Relays: File 8501Document16 paginiZelio-Logic Relays: File 8501Claudio Valdes GutierrezÎncă nu există evaluări

- PLL Control Algorithm For Precise Speed Control of The Slotless PDFDocument7 paginiPLL Control Algorithm For Precise Speed Control of The Slotless PDFAshish KushwahaÎncă nu există evaluări

- Design Issues in CMOS OscillatorsDocument4 paginiDesign Issues in CMOS OscillatorsdhrubÎncă nu există evaluări

- OZW672.01 Autres Fiches en PDFDocument24 paginiOZW672.01 Autres Fiches en PDFe-genieclimatique.comÎncă nu există evaluări

- Datasheet - HK cn1016 1227640Document2 paginiDatasheet - HK cn1016 1227640Reinaldo KoslowskiÎncă nu există evaluări

- Schneider Preventa TelemecaniqueDocument84 paginiSchneider Preventa TelemecaniqueTheKing MarcasÎncă nu există evaluări

- 1992 - Performance Characterization of A High-Power Dual Active Bridge DC-To-DC Converter - KheraluwalaDocument8 pagini1992 - Performance Characterization of A High-Power Dual Active Bridge DC-To-DC Converter - Kheraluwalahafizabu123Încă nu există evaluări

- Wisol Wssfm10r at Command Sfm10r Rev.00 1Document6 paginiWisol Wssfm10r at Command Sfm10r Rev.00 1AdimaroÎncă nu există evaluări

- Datasheet IT8987E PDFDocument1 paginăDatasheet IT8987E PDFAnalia Madeled Tovar JimenezÎncă nu există evaluări

- Introduction to Digiac 1750 Transducers & InstrumentationDocument18 paginiIntroduction to Digiac 1750 Transducers & Instrumentationmalimanaz100% (1)

- Service Manual RAINBOW 180E EnglishDocument54 paginiService Manual RAINBOW 180E EnglishJaroslaw BrzozowskiÎncă nu există evaluări

- Solve Ex 2.0Document6 paginiSolve Ex 2.0Omar Abd El-RaoufÎncă nu există evaluări

- RM2048XE: 2.0kW 48V DC Modular RectifiersDocument2 paginiRM2048XE: 2.0kW 48V DC Modular Rectifiersalways_975382984100% (2)

- Circuit Breaker Selection and Protection of Distribution SystemsDocument28 paginiCircuit Breaker Selection and Protection of Distribution SystemsAlexandre MorenoÎncă nu există evaluări

- 8.4 A Case Study: Using LCD Module On DE2 BoardDocument19 pagini8.4 A Case Study: Using LCD Module On DE2 BoardMas Shari0% (1)

- CC Taix01Document11 paginiCC Taix01Anonymous JoUoNP41Încă nu există evaluări

- Aparat Sudura Tecnica - 144-164Document21 paginiAparat Sudura Tecnica - 144-164florin071Încă nu există evaluări

- Magnetron TechDocument10 paginiMagnetron TechramjoceÎncă nu există evaluări

- Color Monitor: Service ManualDocument23 paginiColor Monitor: Service ManualtaviÎncă nu există evaluări

- LED 16x2 InterfacingDocument8 paginiLED 16x2 InterfacingopooyoÎncă nu există evaluări

- Wireless Speed Control of DC Motor Using PWM and UARTDocument3 paginiWireless Speed Control of DC Motor Using PWM and UARTElins Journal100% (1)

- Zhao. Space Vector PWM Control of Dual Three-Phase Induction Machine Using Vector Space DecompositionDocument10 paginiZhao. Space Vector PWM Control of Dual Three-Phase Induction Machine Using Vector Space DecompositionAnonymous 1D3dCWNcÎncă nu există evaluări

- Formula SAE Electric Division: Safety Failure Modes Effects AnalysisDocument19 paginiFormula SAE Electric Division: Safety Failure Modes Effects AnalysisNelsonÎncă nu există evaluări

- Application FFT-LVDTDocument6 paginiApplication FFT-LVDTnapoleon_velasc3617Încă nu există evaluări

- 253 Apl Modbus-Protocol en 140929Document12 pagini253 Apl Modbus-Protocol en 140929MOHAMED ABDELMALEKÎncă nu există evaluări

- Datasheet IC 7473Document6 paginiDatasheet IC 7473arif vereroÎncă nu există evaluări

- Catalogue Brushless DC Drives GB 02 2007Document56 paginiCatalogue Brushless DC Drives GB 02 2007Bianca CerveiraÎncă nu există evaluări

- ELT50 ELR50 ManualDocument96 paginiELT50 ELR50 ManualRogerÎncă nu există evaluări

- Trench Earth-Fault Compensation Controllers Technical SpecificationsDocument6 paginiTrench Earth-Fault Compensation Controllers Technical SpecificationsHillary McgowanÎncă nu există evaluări

- Daewoo - NC-8913DE - NC-8915DE - Manual Servicio Audio PDFDocument30 paginiDaewoo - NC-8913DE - NC-8915DE - Manual Servicio Audio PDFjose4445Încă nu există evaluări

- UCC381ADDocument33 paginiUCC381ADbenaya2012Încă nu există evaluări

- Space Vector Pulse Width Modulation PDFDocument5 paginiSpace Vector Pulse Width Modulation PDFnarendra kumarÎncă nu există evaluări

- Izone 400 435 Installation User Manual Nov 2017Document100 paginiIzone 400 435 Installation User Manual Nov 2017Yozi AkgÎncă nu există evaluări

- Laboratory 8 - AGCDocument2 paginiLaboratory 8 - AGCAriana Ribeiro LameirinhasÎncă nu există evaluări

- Cushman 303 O&M ManualDocument20 paginiCushman 303 O&M Manual240GL guyÎncă nu există evaluări

- K 203Document5 paginiK 203Alexandre S. CorrêaÎncă nu există evaluări

- Obsolete Product(s) - Obsolete Product(s) Obsolete Product(s) - Obsolete Product(s)Document15 paginiObsolete Product(s) - Obsolete Product(s) Obsolete Product(s) - Obsolete Product(s)teomondoÎncă nu există evaluări

- Mini Project DocumentationDocument34 paginiMini Project DocumentationSri Krishna RakeshÎncă nu există evaluări

- Research Article: A Four Quadrature Signals' Generator With Precise Phase AdjustmentDocument7 paginiResearch Article: A Four Quadrature Signals' Generator With Precise Phase Adjustmentaamir.nedian4139Încă nu există evaluări

- Colour TV Set: ModelsDocument19 paginiColour TV Set: ModelsLefter TironÎncă nu există evaluări

- 2 Ask, PSK, FSKDocument15 pagini2 Ask, PSK, FSKI AM A PROGRAMMERÎncă nu există evaluări

- Raytheon R1206XXDocument70 paginiRaytheon R1206XXtyutyuÎncă nu există evaluări

- whirpool-MT 255-Red - Microondas PDFDocument8 paginiwhirpool-MT 255-Red - Microondas PDFjosenicolas12000Încă nu există evaluări

- BasicLine Chasis 782-TS-2030 Con LA76931, SRA - MAGALYDocument37 paginiBasicLine Chasis 782-TS-2030 Con LA76931, SRA - MAGALYRafael Ernesto Torres MasabeÎncă nu există evaluări

- Samsung - HT-Q9 - Circuito PDFDocument6 paginiSamsung - HT-Q9 - Circuito PDFjosenicolas12000Încă nu există evaluări

- BasicLine Chasis 782-TS-2030 Con LA76931, SRA - MAGALYDocument37 paginiBasicLine Chasis 782-TS-2030 Con LA76931, SRA - MAGALYRafael Ernesto Torres MasabeÎncă nu există evaluări

- 9619 BGH BL3202S Televisor LCD Manual de ServicioDocument46 pagini9619 BGH BL3202S Televisor LCD Manual de Serviciocanario92Încă nu există evaluări

- RM V3Document15 paginiRM V3Andres SilvaÎncă nu există evaluări

- 17" LCD Color Monitor Specs and Service ManualDocument70 pagini17" LCD Color Monitor Specs and Service ManualsenthilrbÎncă nu există evaluări

- Chasis 8873-A2+tmpa8873cscng6v11 PDFDocument4 paginiChasis 8873-A2+tmpa8873cscng6v11 PDFjosenicolas12000Încă nu există evaluări

- whirpool-MT 244-1-Black - Microondas PDFDocument8 paginiwhirpool-MT 244-1-Black - Microondas PDFjosenicolas12000Încă nu există evaluări

- Philips-HTS6600-manual Service PDFDocument77 paginiPhilips-HTS6600-manual Service PDFjosenicolas12000Încă nu există evaluări

- Samsung DVD-P 300mm Training ManualDocument74 paginiSamsung DVD-P 300mm Training Manualjosenicolas12000Încă nu există evaluări

- whirpool-MD 364-W - Microondas PDFDocument7 paginiwhirpool-MD 364-W - Microondas PDFjosenicolas12000Încă nu există evaluări

- Whirpool Time Masters0001 - Microondas PDFDocument8 paginiWhirpool Time Masters0001 - Microondas PDFjosenicolas12000Încă nu există evaluări

- Aiwa cx81 xs81 PDFDocument32 paginiAiwa cx81 xs81 PDFAndreskoiraÎncă nu există evaluări

- whirpool-MT 255-Red - Microondas PDFDocument8 paginiwhirpool-MT 255-Red - Microondas PDFjosenicolas12000Încă nu există evaluări

- 17" LCD Color Monitor Specs and Service ManualDocument70 pagini17" LCD Color Monitor Specs and Service ManualsenthilrbÎncă nu există evaluări

- Whirpool - MWO 165NB AVM 424 - Microondas PDFDocument9 paginiWhirpool - MWO 165NB AVM 424 - Microondas PDFjosenicolas12000Încă nu există evaluări

- 3y03 Mono20020712Document1 pagină3y03 Mono20020712parascoliÎncă nu există evaluări

- 14 21 25 29 Diagrama Orientativo MIRACLEDocument1 pagină14 21 25 29 Diagrama Orientativo MIRACLEdani37aigÎncă nu există evaluări

- STR W6754 PDFDocument8 paginiSTR W6754 PDFBoniface Asuva100% (2)

- Mustang CT-1405 R (BUT11AF) - Compatà Vel Com TV FirstLine TMT2059FL PDFDocument6 paginiMustang CT-1405 R (BUT11AF) - Compatà Vel Com TV FirstLine TMT2059FL PDFjosenicolas12000Încă nu există evaluări

- Chasis ETA-1D Firstline BPF2904Document33 paginiChasis ETA-1D Firstline BPF2904josenicolas12000Încă nu există evaluări

- BA00BC0WFP Datasheet PDFDocument6 paginiBA00BC0WFP Datasheet PDFjosenicolas12000Încă nu există evaluări

- Cobia ctv29pf08Document1 paginăCobia ctv29pf08Efrain Magaña PonceÎncă nu există evaluări

- TCL Service Manual for M28 One-Chip ChassisDocument78 paginiTCL Service Manual for M28 One-Chip Chassisjosenicolas12000Încă nu există evaluări

- FalseDocument6 paginiFalsePablo CamachoÎncă nu există evaluări

- SB560 - SB5100Document3 paginiSB560 - SB5100josenicolas12000Încă nu există evaluări

- Pioneer dv-383-s (ET)Document12 paginiPioneer dv-383-s (ET)azulazulÎncă nu există evaluări

- Counter Circuit Types, Components and ApplicationsDocument22 paginiCounter Circuit Types, Components and Applicationsnavin_barnwalÎncă nu există evaluări

- Kamera Basler Aca2500-20gmDocument20 paginiKamera Basler Aca2500-20gmJan KubalaÎncă nu există evaluări

- Me2404 Set1Document16 paginiMe2404 Set1sakthivelsvsÎncă nu există evaluări

- The English Center Articulation AgreementDocument9 paginiThe English Center Articulation AgreementJose CabreraÎncă nu există evaluări

- Teaching and Learning in the Multigrade ClassroomDocument18 paginiTeaching and Learning in the Multigrade ClassroomMasitah Binti TaibÎncă nu există evaluări

- PP 12 Maths 2024 2Document21 paginiPP 12 Maths 2024 2Risika SinghÎncă nu există evaluări

- Remembering Manoj ShuklaDocument2 paginiRemembering Manoj ShuklamadhukarshuklaÎncă nu există evaluări

- Baella-Silva v. Hulsey, 454 F.3d 5, 1st Cir. (2006)Document9 paginiBaella-Silva v. Hulsey, 454 F.3d 5, 1st Cir. (2006)Scribd Government DocsÎncă nu există evaluări

- Adjective: the girl is beautifulDocument15 paginiAdjective: the girl is beautifulIn'am TraboulsiÎncă nu există evaluări

- Drug Delivery Technologies and Future DirectionsDocument14 paginiDrug Delivery Technologies and Future Directionsraju1559405Încă nu există evaluări

- New Pacific Timber v. Señeris, 101 SCRA 686Document5 paginiNew Pacific Timber v. Señeris, 101 SCRA 686Ishmael AbrahamÎncă nu există evaluări

- Uvas CaractDocument10 paginiUvas CaractgondeluÎncă nu există evaluări

- Explosive Loading of Engineering Structures PDFDocument2 paginiExplosive Loading of Engineering Structures PDFBillÎncă nu există evaluări

- aCTION PLAN IN HEALTHDocument13 paginiaCTION PLAN IN HEALTHCATHERINE FAJARDOÎncă nu există evaluări

- Weakness and Hypotonia: Prepared by DR Hodan Jama MDDocument38 paginiWeakness and Hypotonia: Prepared by DR Hodan Jama MDabdisalaan hassanÎncă nu există evaluări

- GTA Max Profit Bunker Locations Update v1.4Document1 paginăGTA Max Profit Bunker Locations Update v1.4Sam FarrelÎncă nu există evaluări

- Writing Lesson Plan LMDocument6 paginiWriting Lesson Plan LMapi-457032696Încă nu există evaluări

- Investigation Report on Engine Room Fire on Ferry BerlinDocument63 paginiInvestigation Report on Engine Room Fire on Ferry Berlin卓文翔Încă nu există evaluări

- Axis Bank Placement Paper Interview Questions 48072Document3 paginiAxis Bank Placement Paper Interview Questions 48072Ravi RanjanÎncă nu există evaluări

- Eladio Dieste's Free-Standing Barrel VaultsDocument18 paginiEladio Dieste's Free-Standing Barrel Vaultssoniamoise100% (1)

- AP Biology Isopod LabDocument5 paginiAP Biology Isopod LabAhyyaÎncă nu există evaluări

- Or Medallist Results WorldSkills Scale and 100 ScaleDocument39 paginiOr Medallist Results WorldSkills Scale and 100 ScaleJoseÎncă nu există evaluări

- MCS Adopts Milyli Software Redaction Tool BlackoutDocument3 paginiMCS Adopts Milyli Software Redaction Tool BlackoutPR.comÎncă nu există evaluări

- Generic Strategies: Lessons From Crown Cork & Seal and Matching DellDocument16 paginiGeneric Strategies: Lessons From Crown Cork & Seal and Matching DellavaÎncă nu există evaluări

- Entrepreneurial Intentions of Cavite Business StudentsDocument12 paginiEntrepreneurial Intentions of Cavite Business StudentsKevin Pereña GuinsisanaÎncă nu există evaluări