Documente Academic

Documente Profesional

Documente Cultură

TD Architecture Des Ordinateurs PDF

Încărcat de

AhmedBoukadTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

TD Architecture Des Ordinateurs PDF

Încărcat de

AhmedBoukadDrepturi de autor:

Formate disponibile

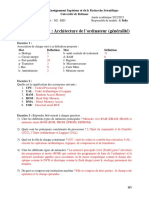

TD Architecture des ordinateurs

Jean-Luc Dekeyser

Fiche 1 Nombres de linformatique

Exercice 1

Une entreprise dsire raliser la sauvegarde de ses donnes sur un site distant. Le volume de

donnes sauvegarder est limit 10Go/jour. La sauvegarde doit s'effectuer la nuit de 22h00

6h00. Les deux sites sont relis par une ligne 2Mbit/s.

On vous demande de vrifier si cette solution est ralisable et le cas chant de proposer une

solution qui permette cette sauvegarde.

Tableau de bit en octets

bit octet (byte) Ko (KB) Mo (MB) Go (GB) To (TB)

1 bit 1

1 octet (byte) 8 1

1 Ko (KB) 8 192 1024 1

1 Mo (MB) 8 388 608 1 048 576 1024 1

1 Go (GB) 8 589 934 592 1 073 741 824 1 048 576 1024 1

1 To (TB) 8 796 093 022 208 1 099 511 627 776 1 073 741 824 1 048 576 1024 1

Exemple de lecture du tableau : 1 Mo =1 048 576 octets

Exercice 2

Question 1 : Combien de nombres peut-on coder sur 4, 8, 16 et 32 bits ? Quelles sont les

bornes ?

Convertir en binaire, puis en octal, et enfin en hexadcimal les nombres suivants :

100, 127, 128, 256, 1000, 1023, 1024, 10000

Exercice 3

1. Quel est le plus grand nombre que l'on peut stocker dans un octet ?

2. Quel est le plus grand nombre que l'on peut stocker dans deux octets ?

3. Quel est le plus grand nombre que l'on peut stocker dans quatre octets ?

4. Quel est le plus grand nombre que l'on peut stocker dans 64 bits ?

5. Combien d'octets faut-il pour stocker la chane <<Que j'aime faire apprendre... >>, sachant qu'en

outre de chaque caractre de la chane elle-mme, nous devons stocker sa longueur sous la forme

d'un nombre entier cod sur quatre octets ?

6. Un disque dur a une capacit de 40 giga-octets, quel est le nombre de bits que l'on peut stocker

sur ce disque ?

7. Un disque dur hautes performances vous est vendu comme pouvant contenir 72 giga-octets, or

vous vous rendez compte qu'il ne peut contenir que 72 Milliards d'octets. Expliquez cette

supercherie.

8. Le disque dur de la question prcdente vous a t factur 10000 Francs, de quelle somme vous

avez t ls ?

Fiche 2 Les portes logiques

Exercice 1

Considrer la fonction dfinie par la table de vrit ci-dessous :

1 - Gnrer une expression logique correspondante (somme de produits et produit de sommes)

2 - Simplifier les deux expressions en utilisant les rgles de lalgbre de Boole.

3 - Construire le diagramme de Karnaugh et dterminer une expression logique associe.

4 - Considrer les fonctions logiques suivantes. Pour chacune delles,

construire le diagramme de Karnaugh ;

utiliser le diagramme pour simplifier les expressions.

Exercice 2

1. Calculer la table de vrit du circuit logique suivant :

2. Donner une expression logique simple pour cette fonction logique.

3. Dessiner son circuit logique.

Fiche TD3 Circuits combinatoires

Exercice 1

- Trouver les tables de vrit de s0, s1, . . . s6.

- Trouver les expressions logiques pour chacune des sorties et dessiner le circuit complet.

Exercice 2

Montrer, en dessinant les circuits logiques, que toutes les fonctions logiques deux variables peuvent

tre exprimes avec uniquement des AND, OR et NOT.

Exercice 3

- On rappelle quun systme de fonctions logiques est dit complet sil permet de calculer toutes les

fonctions logiques.

1. Montrer que {AND, OR, NOT} est complet.

2. Montrer que {AND, NOT} et {OR, NOT} sont complets.

3. Montrer que {NAND} et {NOR} sont complets.

- Construire les fonctions de la question 1 avec des NAND. En sachant quun NAND prend deux

transistors, calculer le cot correspondant si lon nutilise que des NAND.

Mme question mais avec des NOR...

Fiche 4 Logique squentielle

Exercice 1

Aprs avoir rappel les tables de vrit des bascules D et JK, synchronises sur front montant,

donnez le chronogramme des sorties Q de chacune des bascules cbles ci- dessous en fonction

dune entre dhorloge H.

Exercice 2

1. Donnez la table de vrit du montage ci-dessous :

2. Quelle fonction reconnaissez-vous ?

Exercice 3

On dispose de bascules JK synchronises sur front montant. Chaque bascule possde des entres

asynchrones prioritaires actives ltat bas : set et reset.

1. Ralisez un compteur asynchrone modulo 16.

2. Modifiez le montage pour en faire un compteur modulo 12.

3. En partant de zro, tracez son chronogramme sur un cycle complet.

4. Que suffit-il de faire pour remplacer les bascules JK par des bascules D ?

Fiche 5 Assembleur

Exercice 1

1) Donnez l'arbre dvaluation, la notation post-fixe et la notation prfixe de cette expression:

I =( A +B * C ) / ( D - E * F )

2) On dispose de 4 processeurs avec leur propre jeu d'instruction

0 adresse 1 adresse 2 adresses 3 adresses

PUSH M LOAD M MOV(X:=Y) MOV(X:=Y)

POP M STORE M ADD(X:=X+Y) ADD(X:=Y+Z)

ADD ADD M SUB(X:=X-Y) SUB(X:=Y-Z)

SUB SUB M MUL(X:=X*Y) MUL(X:=Y*Z)

MUL MUL M DIV(X:=X/Y) DIV(X:=Y/Z)

DIV DIV M

M est une adresse mmoire (A, B, C, D, E, F, I). X, Y, Z sont soit une adresse mmoire, soit une adresse

registre. La machine 0 adresse utilise une pile. La machine 1 adresse utilise un accumulateur. Les

autres machines disposent de 16 registres R0.. R15. Chaque code oprateur est cod sur 8 bits. Une

adresse mmoire est code sur 16 Bits. Un numro de registre est cod sur 4 bits.

- Donnez les 4 programmes ralisant l'expression de 1)

- Donnez la taille en bits de chaque programme

Exercice 2

Comme cela a t dit en cours, chaque processeur est associ un langage machine. Voici un langage

assembleur du langage machine du Motorola 68000 qui diffre de celui utilis en TP (le X86)

La mmoire est une mmoire de mot de 8 Bits.

L'instruction MOVE S, D transfert la source S sur la destination D

Le $ signifie valeur en Hexa

Le #signifie adressage immdiat

Les registres Di, Ai sont des adressages direct registre, les registres sont de 32 bits

Les adresses mmoire sont des entiers.

Le ( ) signifie adressage indirect

le -( ) est un adressage pr-dcrment (La valeur d'incrment est de 1 ou 2 suivant le nombre

d'octets transfrs)

Le ( ) +est un adressage post-incrment

Et le n( , ) est un adresse indirect index avec dplacement

Les instructions manipulent des mots de 2 octets par dfaut, de 1 octet si le .B est spcifi

derrire l'instruction MOVE. Les bits de poids faible sont ceux qui sont modifis.

Excutez ce programme et pour chaque instruction montrez les changements intervenus sur les

contenus des registres et de la mmoire. Les registres sont initialiss $00000000.

MOVE #$0010,D0

MOVE #$10FB,$2000

MOVE #$2002,A0

MOVE -'(A0),D1

MOVE.B (A0)+,D2

MOVE.B (A0)+,D2

MOVE #$8FFF,16(A0,D0)

Fiche 6 Programmation Assembleur

Exercice 1

Supposez que vous voulez multiplier deux variables a et b, stockes dans les positions de mmoire

M[20] et M[21], respectivement, pour affecter cette valeur la variable toto, stocke la position de

mmoire M[40] C'est--dire, vous voulez effectuer l'opration:

toto =a*b ou: M[40] =M[20]*M[21]

Le processeur possde 8 registres (R0...R7). Le registre R0 contient initialement la valeur 0. Les

instructions du langage machine du processeur sont:

LOAD Rd, M[adr] Rd <=M[adr]

STORE M[adr], Rs M[adr] <=Rs

ADD Rd, Rs1, Rs2 Rd <=Rs1 +Rs2

SUB Rd, Rs1, Rs2 Rd <=Rs1 Rs2

DEC R R <=R - 1

JMP adr sauter adr

JZ Rs, adr si Rs =zero alors sauter adr

Avant d'crire le programme, nous devons trouver un algorithme ralisant la tche voulue. Un

algorithme possible serait:

1. Donnez le code correspondant cet algorithme qui commence ladresse b0000

2. Donnez le code correspondant cet algorithme qui commence ladresse b0010

3. Comment tendre le jeu dinstruction pour crire un programme indpendant de ladresse

de dpart. Rcrire le programme. Quelle diffrence avec lutilisation dun assembleur et

dun label.

Exercice 2

Sachant que le bus dadresse du processeur est de 16 bits avec un alignement loctet, quelle

est la taille de lespace mmoire maximum que celui-ci peut adresser ?

1. Quelles solutions existent pour adresser une plus grande zone mmoire ?

2. O sont effectus les calculs ?

3. A quoi servent les registres suivants du processeur :

i. PC/IP (ou CO/PI)

ii. IR (ou RI)

iii. SP (ou PP)

iv. Accumulateur

4. Quelle tche ralise le squenceur dans un processeur ? l'ordonnanceur ?

Fiche 7 Micro programmation

Exercice 1

Ce processeur ne possde quun seul bus, il servira transfrer les donnes et les instructions. LALU

peut excuter 16 fonctions diffrents,,lune dentre elles se nomme ADD, elle ajoute X avec la valeur

sur le BUS et evntuellement la retenue si celle-ci est positionne. Ces fonctions se font en moins dun

cycle. Une entre de lALU positionne la retenue 1. Un mcanisme de remise zro du registre X

est associ un signal RAZX. Les registres RAM et RDM sont les buffers adresse et donne

vers/depuis la mmoire externe. Laccs la mmoire est ralis par deux signaux lecture et criture,

un seul cycle suffit pour obtenir le effcetuer laccs. Les regsitres R0.. R3 sont les registres gnraux.

1. Donnez la liste des micro-instructions de ce CPU et proposez une codification pas champs

2. Donnez les micro programme des phases dexcution des instructions :

AA R1, R2 source , source/desta

ADD ( R1 ) , R2 adressage indirect

ADD (R1) +, R2 adressage indirect postincrment

3. Donnez le micro programme de la phase de chargement

4. Reprendre les micro programme (2) avec un accs mmoire qui demande entre>2 et <3

cycles.

Fiche TD 8 La mmoire

Exercice 1

En gnral lorsqu'on ne dispose que de circuits ayant une certaine capacit mmoire et que

l'on dsire raliser un espace mmoire de plus grande capacit nous devons faire face deux

problmes diffrents :

tendre la largeur du bus de donnes ;

tendre la largeur du bus d'adresse.

On dispose de deux ROM de taille 1024 mots de 8 Bits

1) Dessinez le circuit ROM

2) Proposez un cablage pour une mmoire de 1024 mots de 16 bit

3) Proposez un cablage pour une mmoire de 2048 mots de 8 bits

Exercice 2 Le dcodage d'adresses

A une adresse prsente par le microprocesseur, un seul priphrique ( RAM, ROM., etc. ) doit

rpondre. Le processeur a 16 bits dadresse.

1) Le circuit mmoire RAM est implant dans la zone adressable de $2000 $2FFF. Proposez un

dcodage dadresse cbl avec gnration du Chip Select.

2) Placez la ROM en $3000-$30FF et linterface en $FFFE-$FFFF

3) On voudrait raliser un adressage programmable. Une commande matrielle permet de

modifier l'espace adressable du circuit mmoire. On utilise pour cela 3 interrupteurs qui

produisent suivant leur position un 1 ou un 0. Proposez un circuit qui ralise huit implantations

possibles de la RAM en $0000, $2000$E000.

Exercice 3 : adressage de mmoire

La capacit des circuits mmoire est en augmentation constante. Le nombre de broches

ncessaire l'adressage des mots mmoire suit cette augmentation, et il est souvent gnant

d'avoir un nombre de broches trop important sur un botier. Imaginez un moyen d'adresser

2

n

mots mmoire en utilisant n' broches, avec n' <n. Faites un schma et dterminez n'.

Exercice 4

Que semble faire le montage ci-dessous ? Trouvez les erreurs et proposez un montage qui

fonctionne.

Fiche TD 9 Mmoire virtuelle

Exercice 1 Espace dadressage pagin

Soit un systme ayant 4 pages mmoire, la taille dune page est gale 100, ladressage commence

0. Un Programme P fait successivement rfrence aux adresses suivantes : 100, 210, 355, 120,420,

110, 200, 550, 139, 201, 395, 404, 505.

1) Donner la chane de rfrences aux pages qui correspondent aux adresses.

2) Calculer le nombre de dfauts de pages en appliquant la stratgie U.

3) Proposer une mthode qui donne un nombre minimum (optimal) de dfauts de pages. Calculer le

nombre de dfauts de pages optimal.

Exercice 2

I) Soit un programme dont le code occupe 1024 octets en mmoire et qui utilise un

vecteur avec 1000 lments de type caractre (un caractre =un octet en mmoire). Ce

programme est excut dans un systme qui utilise la pagination de la mmoire dont la taille

de la mmoire relle est de 1 Mo, la taille d'une page est de 512 octets et les instructions

rfrence mmoire ont un champ dadresse de 24 bits.

a) Donnez :

1) la taille de l'espace logique dadressage

2) le nombre de bits du dplacement

3) le nombre de bits du numro de page virtuelle

4) le nombre de bits d'une adresse relle

5) le nombre de bits du numro de page relle (case)

6) le nombre d'entres de la table des pages

b) Le chargement de ce programme en mmoire engendre-t-il une fragmentation interne de

lespace mmoire?

Justifiez votre rponse.

II) On appelle "anomalie de Belady" le fait que le nombre de dfauts de pages augmente

quand on augmente le nombre de pages disponibles en mmoire physique. On appelle

"algorithme pile" un algorithme prsentant la proprit d'inclusion :

M(m,r) inclus dans M(m+1, r),

o m est le nombre de pages physiques en mmoire et r un index dans le vecteur de rfrences

aux pages ().

M(m,r) reprsente l'ensemble des pages prsentes en mmoire aprs r rfrences mmoire,

lorsque l'on dispose de m pages. Une condition suffisante pour qu'un algorithme ne prsente

pas l'anomalie de Belady est qu'il soit pile.

a) Montrez lanomalie de Belady pour lalgorithme FIFO avec m=3, puis m=4, pour

le vecteur de rfrences aux pages suivant : ={ 1, 2, 3, 4, 1, 2, 5, 1, 2, 3, 4, 5 }.

b) Montrez sur cet exemple que lalgorithme FIFO nest pas un algorithme pile,

en indiquant les tats pour lesquels la proprit d'inclusion n'est pas vrifie.

Exercice 3

Considrez un systme de gestion de mmoire qui a les caractristiques suivantes :

Un adressage virtuel sur 32 bits

Une taille de Page de 4Ko

Une mmoire physique de 1 Mo

a) Supposez que le systme utilise la segmentation pagine et que ladresse virtuelle est de la

forme

:

Quelles sont les donnes manquantes ce problme pour traduire ladresse virtuelle de 32

bits suivante : (hexadcimal) AE854C9C en adresse physique ?

Dessinez un schmas qui utilise ces informations, et visualise les tapes suivre pour

effectuer cette translation. Combien y-a-t-il de pages par segment ?

b) Supposez que le systme utilise une pagination deux niveaux, o les entres des tables de

pages sont sur 4 octets. La premire page contient des pointeurs vers les pages de deuxime

niveau. La structure de ladresse virtuelle est illustre par la figure suivante :

b.1) Si un processus utilise tout lespace adressable qui lui est fourni, combien de pages

seront elles ncessaires pour contenir toutes les tables de pages de ce processus.

b.2) Un second processus ncessite 22Mo pour sexcuter entirement (son code, ses

donnes, pile). La partie contenant son code est dispose dans sa mmoire virtuelle aux

adresses suivantes [2Mo 6Mo-1], les donnes sont quant elles dans lintervalle [12Mo-

21Mo-1].Si nous devons charger les tables de pages associes ces deux parties, combien de

pages de niveaux 2 seront charges en mmoire centrale.

Fiche 10 Bus

Exercice 1 performance de bus

Le bus PC/AT, fonctionnant une frquence de 10 MHz, ncessite 4 cycles pour lire un mot mmoire.

1) Est-ce un bus synchrone ou asynchrone ? Justifiez votre rponse.

2) La taille d'un mot mmoire tant de 16 bits, calculez la bande passante de ce bus en bits/s et en

octets/s.

Exercice 2 dbit de bus

1) Calculez la bande passante de bus ncessaire un cran VGA couleur (640x480) pour afficher

une vido 50 et 60 images/seconde. Chaque pixel se voit attribuer une couleur parmi une

palette fixe de 16 couleurs choisies parmi 262 144 possibles.

2) Soit un moniteur connectable par le bus USB sur un ordinateur. Le bus USB a un dbit de 1,5

Mo/s. Avec un taux de rafrachissement de 25 images/seconde et des images en noir et blanc,

quelle rsolution pourrait-on obtenir sur ce moniteur ?

Exercice 3

Quels sont les diffrents bus systme et quel est le rle de chacun d'entre eux?

Complter le schma ci-dessous :

Exercice 4

En utilisant des multiplexeurs, implmenter un bus permettant dchanger des donnes entre 4

registres R0, R1, R2, R3 de 8 bits chacun. Le bus doit permettre de raliser une opration de type

RiRj, avec i<>j, cest--dire lchange des contenus de Ri et Rj en un seul cycle dhorloge

Fiche 11 I/ O

Exercice 1 Interruption Scrutation

Un dispositif dentres/sorties effectue dix requtes par seconde, chacune dentre elles ncessitant

cinq mille instructions processeur pour tre traite.

1) Les entres/sorties se font par interruption. Il faut mille instructions processeur pour

sauvegarder le contexte et dmarrer le gestionnaire de traitement de la requte, et de nouveau

mille instructions processeur pour charger le contexte et revenir au processus principal. Combien

dinstructions par seconde faut-il pour grer les entres/sorties ?

2) Les entres/sorties se font maintenant par interrogation. Le processeur profite dune

interruption priodique prexistante tous les centimes de seconde pour scruter le priphrique

et voir sil y a une requte traiter. Il ny a donc pas de cot supplmentaire de commutation de

contexte. Chaque interrogation ncessite cinq cents instructions processeur, en plus du

traitement de la requte si elle est prsente. Combien dinstructions par seconde faut-il pour

grer les entres/sorties ?

3) Quel peut tre lintrt de grer les entres/sorties par interrogation plutt que par

interruption?

Exercice 2 DMA

Un disque dur peut transfrer des donnes sur le bus la vitesse de 8 Mo/s.

1) Les entres/sorties se font par interrogation. Chaque scrutation du priphrique prend 0,1 s,

temps pendant lequel sont transfrs 4 octets. Combien dinterrogations faut-il chaque seconde

pour soutenir le dbit du disque ? Quel pourcentage de temps processeur est utilis pour cela ?

2) Les entres/sorties se font maintenant par DMA. 1 s est ncessaire pour initialiser le contrleur

DMA et encore 1 s pour traiter linterruption de fin. Le disque peut transfrer 4 Ko chaque

session DMA. Combien de temps prend chaque session de transfert ? Quel pourcentage de

temps processeur est utilis pour grer le transfert de donnes ?

Exercice 3

Le dialogue entre le CPU et le contrleur (UART 8250) du port srie (priphrique), seffectue

travers des registres, et ce par des oprations dcritures et de lectures successives dans ces

derniers. On distingue essentiellement les registres suivants :

Registre dmission : Avant dtre mis, un caractre doit tre charg dans ce registre.

Registre de rception : Ce registre joue le rle dintermdiaire entre lUART et la CPU. La

lecture des donnes reues passe obligatoirement par la lecture de ce registre.

Registre tat de la ligne : Ce registre permet dinformer le CPU sur ltat de transfert de

donnes. Si le bit 0 est 1 ceci indique la fin de la rception dun caractre et que ce dernier

est disponible dans le registre buffer de rception, ce bit peut tre remis zro par une

opration de lecture du buffer de rception par le CPU ou par une opration dcriture

directe dans le registre tat de la ligne. Le bit 5 est mis 1 pour indiquer que le registre

dmission est vide et que lUART est capable de recevoir un autre caractre dans ce buffer.

On suppose que ces trois registres portent successivement les adresses : 3F8, 3F9 et 3FD

en hexadcimal. On dispose de deux instructions, une dentre et une de sortie. IN et OUT

1. Ecrire un programme en pseudo-assembleur qui permet denvoyer 3 caractres successifs

vers le port srie

2. Ecrire un programme en pseudo-assembleur qui permet de recevoir 2 caractres successifs

depuis le port srie.

S-ar putea să vă placă și

- Corrigé Devoir N°1Document3 paginiCorrigé Devoir N°1Colmain Nassiri100% (1)

- TP3: Conception Schématique Des Microprocesseurs: ObjectifDocument6 paginiTP3: Conception Schématique Des Microprocesseurs: ObjectifDor SafÎncă nu există evaluări

- Exercices Architecture Des OrdinateursDocument8 paginiExercices Architecture Des Ordinateursdouam100% (1)

- 2015 08 21 Examen Jan2007collectifDocument3 pagini2015 08 21 Examen Jan2007collectifMēđ GouigaÎncă nu există evaluări

- Correction Du td1 ArmDocument2 paginiCorrection Du td1 Armazza memmi100% (1)

- TD 2 - Archi - SolDocument4 paginiTD 2 - Archi - SolYoucef BenjillaliÎncă nu există evaluări

- TD2-Architecture Des Ordinateurs GIT 2020-2021Document2 paginiTD2-Architecture Des Ordinateurs GIT 2020-2021Cheick Sidi Mohamed SakhoÎncă nu există evaluări

- Devoir Dmoicile CorrectionDocument8 paginiDevoir Dmoicile CorrectionSimo Light100% (1)

- Solutionnaire Archi TD1Document5 paginiSolutionnaire Archi TD1Colmain Nassiri100% (1)

- TDs ArchitectureDocument5 paginiTDs Architectureben houria yassine100% (1)

- Exam 2017Document2 paginiExam 2017Mohamed Hmamouch100% (2)

- Corrigé Série de TD N° 3Document5 paginiCorrigé Série de TD N° 3Alaa MessaoudÎncă nu există evaluări

- Série D'exercicesDocument4 paginiSérie D'exercicesnesrine nina100% (1)

- ExamDocument3 paginiExamhouda nakkabÎncă nu există evaluări

- Examen 2018 ReseauxDocument3 paginiExamen 2018 Reseauxsow100% (1)

- TD Gest Memoire PDFDocument1 paginăTD Gest Memoire PDFAdil Abouelhassan100% (1)

- TD4Document1 paginăTD4Mounira Tarhouni100% (1)

- Série AssembleurDocument3 paginiSérie AssembleurSoufiane Aggour100% (1)

- TD Allocation de Memoire CorrectionDocument2 paginiTD Allocation de Memoire CorrectionGhediraFakhreddine100% (2)

- TD 1 Les Mémoires: 1. Partie ThéoriqueDocument2 paginiTD 1 Les Mémoires: 1. Partie ThéoriqueAla DorbozÎncă nu există evaluări

- 15 Exercices Corrigés en Systèmes D'exploitation Et Architecture Des OrdinateursDocument11 pagini15 Exercices Corrigés en Systèmes D'exploitation Et Architecture Des OrdinateursJean Baptiste SAWADOGOÎncă nu există evaluări

- Examen ATODocument2 paginiExamen ATOAdos Agbidinoukoun100% (1)

- TD 4 SolutionDocument3 paginiTD 4 SolutionEttaoufik AbdelazizÎncă nu există evaluări

- Chapitre 2 Les InterruptionsDocument10 paginiChapitre 2 Les Interruptionsمصعب مصعبÎncă nu există evaluări

- Gestion de La Memoire CorrectionDocument3 paginiGestion de La Memoire CorrectionOthmane Serraj100% (2)

- TD4 MémoireDocument2 paginiTD4 MémoireŽặ Íŋặß0% (2)

- Systèmes D'exploitation TD5 (Gestion de La Mémoire) : Exercice N°1Document1 paginăSystèmes D'exploitation TD5 (Gestion de La Mémoire) : Exercice N°1kandil fouratÎncă nu există evaluări

- TD2 Correction PDFDocument7 paginiTD2 Correction PDFelmamoun1Încă nu există evaluări

- Exercices Assembleur M1 ELT ER Serie 2 Avec CorrigéDocument5 paginiExercices Assembleur M1 ELT ER Serie 2 Avec CorrigéAmir Na DzÎncă nu există evaluări

- TD CH 3 Architecture Des Ordinateurs 2Document1 paginăTD CH 3 Architecture Des Ordinateurs 2Pape Moussa DiopÎncă nu există evaluări

- TD1 CorrectionDocument6 paginiTD1 CorrectionHoussem1993100% (1)

- (Réseaux) TD 1-Introduction (Correction)Document3 pagini(Réseaux) TD 1-Introduction (Correction)abdo-dz0% (1)

- TD6 Gestion de La MemoireDocument3 paginiTD6 Gestion de La MemoireMahamat Souradje salehÎncă nu există evaluări

- TD2 CorrigeDocument3 paginiTD2 CorrigeMouna Ben Mohamed100% (1)

- TD1 Mémoires 2021Document3 paginiTD1 Mémoires 2021Younesse El100% (1)

- Correction TD1Document14 paginiCorrection TD1Hicham Loukili100% (1)

- Exercices Avec Solutions Systèmes Temps RéelDocument12 paginiExercices Avec Solutions Systèmes Temps RéelAs Ma100% (3)

- Solution Fiche de TD4 P2 AO USTO 2022-2023 BEKDocument3 paginiSolution Fiche de TD4 P2 AO USTO 2022-2023 BEKKandjeré djida silace SilaceÎncă nu există evaluări

- Gestion de La MémoireDocument11 paginiGestion de La MémoireChaimae Salsabil000% (1)

- TD2Document3 paginiTD2Nouaman MohamedÎncă nu există evaluări

- TD#3Document2 paginiTD#3Marouane TaibiniÎncă nu există evaluări

- Les Mémoires CachesDocument46 paginiLes Mémoires Cacheshi123Încă nu există evaluări

- (R Seaux) TD 2-Reseaux Locaux (Correction)Document2 pagini(R Seaux) TD 2-Reseaux Locaux (Correction)elmamoun1100% (1)

- Questions de CoursDocument2 paginiQuestions de CoursbilalÎncă nu există evaluări

- Ch5-Gestion Des Entrées SortiesDocument11 paginiCh5-Gestion Des Entrées Sortiesb hamidÎncă nu există evaluări

- TD2 CorrigeDocument3 paginiTD2 CorrigeAbderrahmane SmaaliÎncă nu există evaluări

- TD - Ipv4Document2 paginiTD - Ipv4MARIAM MAATOUGÎncă nu există evaluări

- Série 3Document8 paginiSérie 3Blidi AymenÎncă nu există evaluări

- Corrigé TD 154Document3 paginiCorrigé TD 154MBADJOUN Daniel100% (1)

- Architecture Ordinateurs 8086 ElmokhtariDocument63 paginiArchitecture Ordinateurs 8086 ElmokhtariZakaria HaitoutÎncă nu există evaluări

- 0B4CjIMFACisHckpYZHNmY2xDTms PDFDocument4 pagini0B4CjIMFACisHckpYZHNmY2xDTms PDFAbdoul Nasser Aboubacar100% (1)

- TD RL 4Document7 paginiTD RL 4Joël KoffiÎncă nu există evaluări

- TD5-correction Mémoire Paginaion Iset NabDocument4 paginiTD5-correction Mémoire Paginaion Iset NabZi EdÎncă nu există evaluări

- Corrigé Du TD1Document3 paginiCorrigé Du TD1youssef BohaÎncă nu există evaluări

- Ser TD4 20222023Document4 paginiSer TD4 20222023ramzi ayadi100% (1)

- TD Assembleur Lp2 Mirtax86Document8 paginiTD Assembleur Lp2 Mirtax86Oumar Farouk Achirou ElhadjiÎncă nu există evaluări

- sérieTD2 2021Document3 paginisérieTD2 2021Møu AtezÎncă nu există evaluări

- 10.mecanique Des FluidesDocument41 pagini10.mecanique Des FluidesSaid HallaiÎncă nu există evaluări

- m16 Appli Règles Béton Armé El - Bael - Ac CCTP-BTP-CCTPDocument71 paginim16 Appli Règles Béton Armé El - Bael - Ac CCTP-BTP-CCTPAhmedBoukad0% (1)

- Sujet TD01 PDFDocument1 paginăSujet TD01 PDFAhmedBoukadÎncă nu există evaluări

- Circuit LogiqueDocument91 paginiCircuit Logiqueleibniz100% (9)

- TD VHDLPPDocument23 paginiTD VHDLPPMël DjäÎncă nu există evaluări

- Système À MicroprocesseurDocument43 paginiSystème À MicroprocesseurW DÎncă nu există evaluări

- Pic 2Document49 paginiPic 2jugurthaÎncă nu există evaluări

- RapportDocument9 paginiRapportKhaoula AmahouchÎncă nu există evaluări

- Chapitre 1 CoursDocument17 paginiChapitre 1 CoursNouzha BoukoubaÎncă nu există evaluări

- Chapitre 2 - Familles Des Circuits Intégrés Numériques (Logiques)Document26 paginiChapitre 2 - Familles Des Circuits Intégrés Numériques (Logiques)Ttech hackÎncă nu există evaluări

- TDSystemes SequentielsDocument7 paginiTDSystemes SequentielsBouazzaoui KaramÎncă nu există evaluări

- TD Architecture Des OrdinateursDocument2 paginiTD Architecture Des OrdinateursPacome ChedeÎncă nu există evaluări

- Add SOUSDocument9 paginiAdd SOUSNabil KhÎncă nu există evaluări

- Cours No 08 Les MicroprocesseursDocument7 paginiCours No 08 Les MicroprocesseursBernard HounnouveÎncă nu există evaluări

- Bsim3v31 250nmDocument5 paginiBsim3v31 250nmdomingouclarayÎncă nu există evaluări

- CoursDocument110 paginiCoursMaria MEKLIÎncă nu există evaluări

- TriggerDocument3 paginiTriggersamilouahÎncă nu există evaluări

- Chapitre 3 Logiques CombinatoiresDocument20 paginiChapitre 3 Logiques Combinatoireslilian camilleÎncă nu există evaluări

- LEEA - L2 - TP LogiqueDocument10 paginiLEEA - L2 - TP LogiqueMH BkrÎncă nu există evaluări

- Devoir Synthese 1-Bac - deDocument5 paginiDevoir Synthese 1-Bac - deFethi BenmassoudeÎncă nu există evaluări

- Partie2 ENDocument48 paginiPartie2 ENOthmane EL BAROUDIÎncă nu există evaluări

- Travaux Pratiques 3-ElectroniqueDocument5 paginiTravaux Pratiques 3-ElectroniqueAyoub OumousÎncă nu există evaluări

- CEA-N-1033: Analyse Des Circuits Sequentiels Application Aux Bascules Bistables SN 54-Et SNDocument54 paginiCEA-N-1033: Analyse Des Circuits Sequentiels Application Aux Bascules Bistables SN 54-Et SNAudrey DreysÎncă nu există evaluări

- Cours VHDLDocument15 paginiCours VHDLFaycel HamdiÎncă nu există evaluări

- CIRA1 - 3) Logique Sequentielle PDFDocument7 paginiCIRA1 - 3) Logique Sequentielle PDFLANGO RICHARD BAMBAÎncă nu există evaluări

- Thème 3: Logique Sequentielle: Compteurs/décompteurs Intégrés 74192 - 74193Document4 paginiThème 3: Logique Sequentielle: Compteurs/décompteurs Intégrés 74192 - 74193amerjlali456Încă nu există evaluări

- Compteur 7490Document6 paginiCompteur 7490Atef Stili100% (2)

- TD2-Les Bascules+Correction FinalDocument5 paginiTD2-Les Bascules+Correction FinalOmayma BoukatayaÎncă nu există evaluări

- GE MP16bDocument98 paginiGE MP16bSafaa BelagounÎncă nu există evaluări

- VHDL Exercices Du CoursDocument16 paginiVHDL Exercices Du Coursdhaouadi hazemÎncă nu există evaluări

- Travaux Pratiques Electronique NumériqueDocument10 paginiTravaux Pratiques Electronique NumériqueOumaima RhayaÎncă nu există evaluări

- Using ADC of PIC MicrocontrollerDocument7 paginiUsing ADC of PIC MicrocontrollernawzatÎncă nu există evaluări

- ENSL1 Comb 10 11Document71 paginiENSL1 Comb 10 11Oussama SimourÎncă nu există evaluări

- CPCG TD1 SolutionDocument2 paginiCPCG TD1 SolutionBella SalimaÎncă nu există evaluări