Documente Academic

Documente Profesional

Documente Cultură

Sistemas - Embebidos 2012 - 1erc Conversores - ADC DAC Lutenberg PDF

Încărcat de

Gloria AlgarañazTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Sistemas - Embebidos 2012 - 1erc Conversores - ADC DAC Lutenberg PDF

Încărcat de

Gloria AlgarañazDrepturi de autor:

Formate disponibile

1

Conversores

Analgico/digital

Dr. Ing. Ariel Lutenberg

Laboratorio de Sistemas Embebidos - UBA

011100110

011100110

2

Conversores

Analgico/digital

Organizacin de la clase:

1. Repaso de conversin A-D

2. Conversores A-D

3. Conversores D-A

3

1. Repaso de

conversin A-D

4

1. Introduccin a conversin A-D

Seal analgica y seal digital

Una seal analgica puede tomar cualquier valor real.

Una seal digital slo toma valores discretos de un conjunto predeterminado.

5

1. Introduccin a conversin A-D

Ventajas de la seal digital

1. Puede replicarse sin perdida de calidad (CD, repetidores, etc).

2. Pueden detectarse y corregirse errores (ej. CD/DVD, CRC, etc.)

3. Procesamiento digital y compresin (MP3, JPG, etc.)

Desventajas de la seal digital

1. Requiere conversores A/D y D/A

2. Introduce ruido de cuantizacin que limita la resolucin.

6

1. Introduccin a conversin A-D

Error de cuantizacin

Al discretizar una seal se introduce una distorsin: Error de cuantizacin

N = bits de discretizacin

# valores de salida = 2

N

Resolucin = FullScale/2

N

= q

Error de cuantizacin < 1/2 q

5,96 x 10e(-8) 16777216 24

1,52 x 10e(-5) 65536 16

0.00390 256 8

0.0625 16 4

0.25 4 2

Resolucin # valores de salida N (bits de discretizacin)

7

1. Introduccin a conversin A-D

Ruido de cuantizacin

El error de cuantizacin se puede visualizar mediante un grfico cartesiano:

q

001

8

1. Introduccin a conversin A-D

Ruido de cuantizacin

La sucesin en el tiempo de los errores de cuantizacin dan lugar a una seal

de error, e(t), que llamamos ruido de cuantizacin.

ruido de

cuantizacin

tiempo

-0.5

+0.3

-0.5

+0.4

-0.3

+0.2

0 0

0

e(t)

9

1. Introduccin a conversin A-D

Ruido de cuantizacin

La sucesin en el tiempo de los errores de cuantizacin dan lugar a una seal

de error, e(t), que llamamos ruido de cuantizacin.

ruido de

cuantizacin

tiempo

-0.5

+0.3

-0.5

+0.4

-0.3

+0.2

0 0

0

e(t)

El ruido de cuantizacin

es una seal aleatoria en el

rango 1/2 q

10

1. Introduccin a conversin A-D

Ruido de cuantizacin

Queremos estimar la energa del ruido de cuantizacin, e(t), as podemos

calcular la relacin seal a ruido (SNR) del conversor para una seal de entrada

tpica, v(t), pero cmo hacemos?

11

1. Introduccin a conversin A-D

Ruido de cuantizacin

Queremos estimar la energa del ruido de cuantizacin, e(t), as podemos

calcular la relacin seal a ruido (SNR) del conversor para una seal de entrada

tpica, v(t), pero cmo hacemos?

Para estimar la energa de e(t) debemos considerar sus principales propiedades:

1. Rango de valores entre -q/2 y +q/2.

2. Valor medio igual a cero (e(t)= 0).

3. Probabilidad uniforme entre -q/2 y +q/2.

12

1. Introduccin a conversin A-D

Ruido de cuantizacin

Queremos estimar la energa del ruido de cuantizacin, e(t), as podemos

calcular la relacin seal a ruido (SNR) del conversor para una seal de entrada

tpica, v(t), pero cmo hacemos?

Para estimar la energa de e(t) debemos considerar sus principales propiedades:

1. Rango de valores entre -q/2 y +q/2.

2. Valor medio igual a cero (e(t)= 0).

3. Probabilidad uniforme entre -q/2 y +q/2.

Proponemos entonces una seal e(t) auxiliar que satisface estas propiedades:

13

Atencin!

Esta no es la verdadera seal e(t),

sino una seal auxiliar con

propiedades similares, que vamos

a usar para hacer algunas cuentas.

1. Introduccin a conversin A-D

Ruido de cuantizacin

Queremos estimar la energa del ruido de cuantizacin, e(t), as podemos

calcular la relacin seal a ruido (SNR) del conversor para una seal de entrada

tpica, v(t), pero cmo hacemos?

Para estimar la energa de e(t) debemos considerar sus principales propiedades:

1. Rango de valores entre -q/2 y +q/2.

2. Valor medio igual a cero (e(t)= 0).

3. Probabilidad uniforme entre -q/2 y +q/2.

Proponemos entonces una seal e(t) auxiliar que satisface estas propiedades:

14

1. Introduccin a conversin A-D

Ruido de cuantizacin

Calculamos entonces la energa de e(t):

( ) ( )

2 2

2 2

2

12

q

s

q

s

s q

t s t dt

q

+

+

= =

12

RMS

q

=

15

1. Introduccin a conversin A-D

Ruido de cuantizacin

Calculamos entonces la energa de e(t):

( ) ( )

2 2

2 2

2

12

q

s

q

s

s q

t s t dt

q

+

+

= =

12

RMS

q

=

Y cul es la seal de entrada v(t) que vamos a considerar para calcular SNR?

16

1. Introduccin a conversin A-D

Ruido de cuantizacin

Calculamos entonces la energa de e(t):

( ) ( )

2 2

2 2

2

12

q

s

q

s

s q

t s t dt

q

+

+

= =

12

RMS

q

=

Y cul es la seal de entrada v(t) que vamos a considerar para calcular SNR?

- Consideremos una seal senoidal de amplitud mxima:

( ) ( )

2

sin 2

2

N

in

q

v t f t =

2

2 2

N

RMS

q

v =

17

1. Introduccin a conversin A-D

Ruido de cuantizacin

Calculamos entonces la energa de e(t):

( ) ( )

2 2

2 2

2

12

q

s

q

s

s q

t s t dt

q

+

+

= =

12

RMS

q

=

Y cul es la seal de entrada v(t) que vamos a considerar para calcular SNR?

- Consideremos una seal senoidal de amplitud mxima:

As resulta la relacin SNR para un conversor ideal:

( ) ( )

2

sin 2

2

N

in

q

v t f t =

2

2 2

N

RMS

q

v =

( )

10 10 10 10

( )

( )

3

10log 20log 20log 2 20log

2

N

RMS

RMS

POT v

POT

v

SNR

= = = +

6.02 1.76 SNR N dB = +

18

1. Introduccin a conversin A-D

Ruido de cuantizacin

Ejemplo:

- Para un conversor ideal con N=8 bits y full scale = 2.56V hallar e

RMS

y SNR

19

1. Introduccin a conversin A-D

Ruido de cuantizacin

Ejemplo:

- Para un conversor ideal con N=8 bits y full scale = 2.56V hallar e

RMS

y SNR

Primero q = 2.56V/2

8

= 10mV e

RMS

= 2.9mV

20

1. Introduccin a conversin A-D

Ruido de cuantizacin

Ejemplo:

- Para un conversor ideal con N=8 bits y full scale = 2.56V hallar e

RMS

y SNR

Primero q = 2.56V/2

8

= 10mV e

RMS

= 2.9mV

Verificamos: si v

in

es una seal sinusoidal de amplitud mxima

y luego q

RMS

= v

RMS

/256 256 256 256 = 3.54mV

2.56

907

2 2

RMS

V

v mV = =

21

1. Introduccin a conversin A-D

Ruido de cuantizacin

Ejemplo:

- Para un conversor ideal con N=8 bits y full scale = 2.56V hallar e

RMS

y SNR

Primero q = 2.56V/2

8

= 10mV e

RMS

= 2.9mV

Verificamos: si v

in

es una seal sinusoidal de amplitud mxima

y luego q

RMS

= v

RMS

/256 256 256 256 = 3.54mV

Tiene sentido? S, porque el ruido de cuantizacin es menor a un LSB (q).

2.56

907

2 2

RMS

V

v mV = =

22

1. Introduccin a conversin A-D

Ruido de cuantizacin

Ejemplo:

- Para un conversor ideal con N=8 bits y full scale = 2.56V hallar e

RMS

y SNR

Primero q = 2.56V/2

8

= 10mV e

RMS

= 2.9mV

Verificamos: si v

in

es una seal sinusoidal de amplitud mxima

y luego q

RMS

= v

RMS

/256 256 256 256 = 3.54mV

Tiene sentido? S, porque el ruido de cuantizacin es menor a un LSB (q).

Finalmente SNR = 6.02*8+1.76dB SNR = 50dB

2.56

907

2 2

RMS

V

v mV = =

23

1. Introduccin a conversin A-D

Medicin experimental de la SNR de un conversor

- En un conversor real, se desconoce el verdadero valor de

RMS

entonces

se mide experimentalmente SNR y se calcula el Effective Number of bits:

1.76

6.02

SNR dB

ENOB

dB

=

Atencin!

Generalmente ENOB < #bits conversor

Generador

senoidal de muy

baja distorsin

Conversor AD

a caracterizar

Analizador de

espectros de

muy alta calidad

010001..

010100..

011010..

Potencia

espectral

Frecuencia

Potencia

espectral

Frecuencia

Medicin de

la SNR

IN

OUT

24

Promediar reduce el ruido de cuantizacin

1. Introduccin a conversin A-D

La seal est mezclada con el ruido:

- La cuantizacin idealmente introduce ruido

distribuido en todas las frecuencias (ruido blanco).

Potencia

espectral

Frecuencia

25

Promediar reduce el ruido de cuantizacin

1. Introduccin a conversin A-D

Tomando una conversin por muestra:

6.02 1.76 SNR N dB = +

La seal est mezclada con el ruido:

- La cuantizacin idealmente introduce ruido

distribuido en todas las frecuencias (ruido blanco).

Potencia

espectral

Frecuencia

26

Promediar reduce el ruido de cuantizacin

1. Introduccin a conversin A-D

Tomando una conversin por muestra:

6.02 1.76 SNR N dB = +

La seal est mezclada con el ruido:

- La cuantizacin idealmente introduce ruido

distribuido en todas las frecuencias (ruido blanco).

Muestreando K veces y promediando mejora la SNR:

- La varianza del ruido (e

RMS

) se reduce K veces (si el ruido no est auto-correlacionado)

- La varianza de la seal (v

RMS

) se mantiene constante (si se asume que vara lentamente)

Potencia

espectral

Frecuencia

27

Promediar reduce el ruido de cuantizacin

1. Introduccin a conversin A-D

Tomando una conversin por muestra:

6.02 1.76 SNR N dB = +

La seal est mezclada con el ruido:

- La cuantizacin idealmente introduce ruido

distribuido en todas las frecuencias (ruido blanco).

10

6.02 1.76 10log SNR N dB K = + +

Se consigue mejorar la SNR en un factor de K veces

Muestreando K veces y promediando mejora la SNR:

- La varianza del ruido (e

RMS

) se reduce K veces (si el ruido no est auto-correlacionado)

- La varianza de la seal (v

RMS

) se mantiene constante (si se asume que vara lentamente)

Potencia

espectral

Frecuencia

28

Promediar reduce el ruido de cuantizacin

1. Introduccin a conversin A-D

jemplo:

- Un conversor ideal de 8 bits tiene una relacin seal a ruido de 50dB

- Si se promedian 10 muestras (K=10) entonces la SNR aumenta a:

- Para haber obtenido esta misma SNR sin promediar habran sido necesarios:

( )

10

6.02 1.76 10log 60 SNR N dB K dB = + + =

60 1.76

9.67 bits

6.02

dB dB

N

= =

29

Promediar reduce el ruido de cuantizacin

1. Introduccin a conversin A-D

jemplo:

- Un conversor ideal de 8 bits tiene una relacin seal a ruido de 50dB

- Si se promedian 10 muestras (K=10) entonces la SNR aumenta a:

- Para haber obtenido esta misma SNR sin promediar habran sido necesarios:

- O sea, el SNR de un conversor ideal de 8 bits que promedia 10 muestras es

similar al SNR de un conversor ideal de 10 bits que no promedia muestras.

( )

10

6.02 1.76 10log 60 SNR N dB K dB = + + =

60 1.76

9.67 bits

6.02

dB dB

N

= =

30

1. Introduccin a conversin A-D

Tensin de referencia

- Un conversor AD indica la proporcin entre

la seal de entrada y la tensin de referencia:

31

1. Introduccin a conversin A-D

Tensin de referencia

- Un conversor AD indica la proporcin entre

la seal de entrada y la tensin de referencia:

La calidad de la conversin depende de la calidad de la tensin de referencia!

" #isten $uentes de re$erencia con alta e#actitud% esta&ilidad t'rmica y &ajo ruido:

jemplo: M()*+,-% .

/0T

1 ,!-.23!345 6,-78% 9 ppm:78% 9!-;.

pp

% 0<S *!*=

32

1. Introduccin a conversin A-D

Errores de conversin

- Errores lineales: son corregibles mediante ajustes sencillos:

- Errores no lineales: son difciles de corregir:

Error de

offset

Error de

ganancia

Error de

alinealidad

Error de

alinealidad

33

1. Introduccin a conversin A-D

Circuito sample&hold (muestreo y retencin)

- Durante el tiempo de conversin (t

c

) la seal debe variar menos que q/2.

34

1. Introduccin a conversin A-D

Circuito sample&hold (muestreo y retencin)

- Durante el tiempo de conversin (t

c

) la seal debe variar menos que q/2.

Ejemplo

Para un ADC de N=8 bits, con t

c

= 100s (10KHz) y

Resulta:

Entonces:

2

sin(2 )

2

N

i

q

v ft

=

2

2 cos(2 )

2

N

i

dv q

f ft

dt

=

MUY BAJO!

2

2

2

N

i

MAX

dv q

f

dt

=

1

2 1

6.2

2

i

N

c c MAX

dv q

f Hz

dt t t

+

=

35

1. Introduccin a conversin A-D

Circuito sample&hold (muestreo y retencin)

- Durante el tiempo de conversin (t

c

) la seal debe variar menos que q/2.

Ejemplo

Para un ADC de N=8 bits, con t

c

= 100s (10KHz) y

Resulta:

Entonces:

- Solucin: circuitos sample&hold

muestrean la seal y retienen

su valor durante la conversin.

2

sin(2 )

2

N

i

q

v ft

=

2

2 cos(2 )

2

N

i

dv q

f ft

dt

=

MUY BAJO!

2

2

2

N

i

MAX

dv q

f

dt

=

1

2 1

6.2

2

i

N

c c MAX

dv q

f Hz

dt t t

+

=

36

1. Introduccin a conversin A-D

Acondicionamiento de la seal de entrada

- La seal debe aprovechar todo el rango de entrada del ADC:

Se aprovecha mejor la resolucin del conversor

Se minimiza el efecto de los errores de conversin

37

1. Introduccin a conversin A-D

Acondicionamiento de la seal de entrada

- La seal debe aprovechar todo el rango de entrada del ADC:

Se aprovecha mejor la resolucin del conversor

Se minimiza el efecto de los errores de conversin

Ejemplo

Se tiene una seal con rango 10 a 10 Volts y un conversor con rango 05Volts.

38

1. Introduccin a conversin A-D

Acondicionamiento de la seal de entrada

- La seal debe aprovechar todo el rango de entrada del ADC:

Se aprovecha mejor la resolucin del conversor

Se minimiza el efecto de los errores de conversin

Ejemplo

Se tiene una seal con rango 10 a 10 Volts y un conversor con rango 05Volts.

- Hoy en da generalmente el scaling viene integrado en los ADCs.

39

1. Introduccin a conversin A-D

Evolucin de los ADCs

Por ejemplo, en el Instituto de Microelectrnica de Sevilla (IMSE) - C.N.M.:

17-bit 40-kS/s 4th-order SC M (CMOS 1.2um) [I !SSC"1##$%

1&.4-bit #.&-kS/s 1.71m' SC M (CMOS 0.7um) [I!C()"1##7%

1*-bit 2.2-MS/s $$m' SC M (CMOS 0.7um) [I !SSC"1###%

10.$-bit 1.&*-M+, SI -./d-0.ss M (CMOS 0.1um) [I !SSC"2000%

1*-bit 4-MS/s 77m' SC M (CMOS 0.*$um) [23u4er"2002%

2.$-5 SC M 6or )7S8/)7S89 (CMOS 0.2$um) [I (C)S"2004%

110-d- 40-kS/s :ro;. ;.i/ SC M (CMOS 0.*$um) [I !SSC"200$%

12-bit 10MS/s :i0e3i/e )7C 6or :8C (CMOS 1*0/m) [I )77)0$%

12-bit 10MS/s Curre/t Steeri/; 7)C 6or :8C (CMOS 1*0/m) [I )77)0$%

<e=o/6. SC M 6or >SM/?M(S/-( (CMOS 1*0/m) [I )-SSCC07%

12-bit 40-MS/s *-2 C.s=.de C( M (CMOS 1*0/m) [I 58SI01%

)d.0ti@e SC M 6or -eAo/d-*> 'ire3ess (e3e=om (CMOS #0/m) [SSCI<C10%

0.*$um (Se/sor I/ter6.=e"

-est BOM" !SSC 200$)

0.2$um ()7S8" i/ 0rodu=tio/"

(C)S-I" 2004)

0.1*um (MStd Com."

)-SSCC07)

#0/m (--*>)

SSCI<CC2010

40

1. Introduccin a conversin A-D

Evolucin de los ADCs

El avance de los ADCs es muy rpido, pero ms lento que los circuitos digitales:

- Consecuencia:

Los conversores que tengan ms subcircuitos internos digitales evolucionarn

ms rpidamente que los que tengan ms subcircuitos internos analgicos.

41

1. Introduccin a conversin A-D

Evolucin de los ADCs

El avance de los ADCs es muy rpido, pero ms lento que los circuitos digitales:

- Consecuencia:

Usar ms subcircuitos digitales reduce el costo de los conversores.

42

1. Introduccin a conversin A-D

Caractersticas de los ADCs

Entradas analgicas:

Tensin o corriente

Unipolar o bipolar

Nmero de canales

Rango de seal

Salidas digitales:

Resolucin [Bits]

Throughput Rate (1/t

c

)

Salida paralelo o serie

Tensin 5V, 3.3V, etc.

Detalles adicionales:

Tensin de alimentacin

Consumo de potencia

Tensin de referencia interna o externa

Clock del conversor interno o externo

PRECIO

Error de offset

Error de ganancia

Monotonicidad

Relacin seal/ruido

Encapsulado

43

2. Conversores A-D

44

2. Conversores A-D

Comparacin de tecnologas de ADC

La tecnologa a utilizar depende de los requisitos de la aplicacin.

Veamos las caractersticas de las principales tecnologas:

Existe relaciones de compromiso al elegir la tecnologa del ADC

Bajo

Bajo

Bajo

Alto

Medio

Alto

PRECIO

TECNOLOGA

VELOCIDAD RESOLUCIN

INMUNIDAD

AL RIUDO CONSUMO

Time Interleaving Muy rpido 4-10 bits No Muy alto

Flash Rpido 4-10 bits No Alto

Pipelined Subraging Rpido 10-16 bits No Medio

Succesive Approximation Medio 10-16 bits Escasa Bajo

Integrating (obsoleto) Lento 12-18 bits Buena Medio

Sigma-Delta Lento 12-24 bits Muy buena Muy bajo

45

2. Conversores A-D

Comparacin de tecnologas de ADC

Veamos en detalle cada una de las tecnologas

46

2. Conversores A-D

a. ADC Flash converters

Realiza la conversin de manera

inmediata en una nica operacin.

La salida es inherentemente digital.

La larga cadena de resistores

imposibilita ms de ~8 bits

de resolucin (255 resistores)

y/o impone un alto costo $$$.

47

2. Conversores A-D

a. ADC Flash converters (ejemplo)

48

2. Conversores A-D

a. ADC Flash converters (ejemplo)

ENOB

= 7.43

49

2. Conversores A-D

a. ADC Flash converters (importancia del layout en alta velocidad)

50

2. Conversores A-D

b. ADC Time Interleaved

La idea de estos conversores es usar un sistema de M canales en paralelo

que convierten alternativamente la seal y la alimentan a un MUX.

El resultado es un conversor M veces ms rpido que cada conversor individual.

51

2. Conversores A-D

b. ADC Time Interleaved

Por ejemplo, si se multiplexan tres conversores AD resulta el siguiente esquema:

El requisito de que todos los conversores sean idnticos impone

una limitacin tecnolgica e implica un alto costo ($$$).

tiempo

conversion

time

tiempo

tiempo

conversion

time

conversion

time

conversion

time

conversion

time

conversion

time

tiempo

ADC

0

ADC

1

ADC

2

MUX

Digital

output

Analog

input

ADC

0

ADC

1

ADC

2

A

D

C

0

A

D

C

1

A

D

C

2

A

D

C

0

A

D

C

1

Digital

Output

Latencia

incial

Tres

conversores

idnticos

Mayor

velocidad de

conversin!!!

52

2. Conversores A-D

b. ADC Time Interleaved

Es fundamental ecualizar los M canales y para eso hay varias alternativas:

Los resultados

son muy

Impresionantes.

Ejemplo del

Advanced

Filter Bank

del AD12400:

53

2. Conversores A-D

b. ADC Time Interleaved

54

2. Conversores A-D

c. ADC Succesive Aproximation

- Es apto para aplicaciones de baja

resolucin y velocidad.

- Su bajo costo posibilita integrarlo

en microcontroladores baratos.

55

2. Conversores A-D

c. ADC Succesive Aproximation

- Es apto para aplicaciones de baja

resolucin y velocidad.

- Su bajo costo posibilita integrarlo

en microcontroladores baratos.

Su algoritmo de funcionamiento es una bsqueda binaria:

56

2. Conversores A-D

c. ADC Succesive Aproximation

Se implementa mediante un sencillo sistema analgico digital:

Pero al ser iterativo su velocidad de conversin no es muy alta.

Y adems su resolucin depende del DAC utilizado en el sistema.

57

2. Conversores A-D

c. ADC Succesive Aproximation (ejemplo)

58

2. Conversores A-D

d. ADC Pipelined subraging

Utilizan una estructura en cascada tipo tubera (pipeline), donde la conversin se

realiza sucesivamente sobre fracciones cada vez menores de V

in

(subraging).

59

2. Conversores A-D

d. ADC Pipelined subraging

- Por ejemplo, en un ADC subraging de 4 etapas de rango 01 Volts y una

seal de entrada de 0.7 Volts el funcionamiento sera el siguiente:

La ventaja es que cada una de las etapas realiza una operacin elemental e

idntica a las dems etapas entonces resulta sencillo agregar ms etapas.

La limitacin es el error que introduce cada etapa y su variabilidad.

1011

Su funcionamiento es:

aux=input;

for i=1:n_bits,

if (aux > Vref/2)

output[i]=1

aux=(aux-0.5)*2;

else

output[i]=0;

aux=aux*2;

endif

endfor

60

2. Conversores A-D

d. ADC Pipelined subraging (ejemplo)

Para un ADC subraging de 4 etapas de 1 bits y de rango 01 Volts, y una seal

de entrada de 0.4 Volts indique las tensiones y conversiones en cada etapa.

Resolucin

0.4V

-0.1

0.8V

0.3

0.6V

0.1

0.2V

-0.3

0 1 1 0 Output = 0110

1011

Su funcionamiento es:

aux=input;

for i=1:n_bits,

if (aux > Vref/2)

output[i]=1

aux=(aux-0.5)*2;

else

output[i]=0;

aux=aux*2;

endif

endfor

61

2. Conversores A-D

d.ADC Pipelined subraging

- Implementacin para ms bits:

Los ADC pipeline subraging

dominan las aplicaciones de alta

velocidad (>5 MSPS) y consumo

moderado: - Video

- Comunicaciones

- etc.

62

2. Conversores A-D

d.ADC Pipelined subraging (ejemplo)

63

2. Conversores A-D

e. ADC de integracin (OBSOLETO)

Hoy en da es obsoleto y fue ampliamente superado por el Sigma-Delta:

Pero veamos igualmente cmo funciona

64

2. Conversores A-D

e. ADC de integracin (OBSOLETO)

La seal de entrada se integra por un tiempo T que se controla con R y C

Luego el integrador se descarga a una tensin V

REF

conocida y se mide t

x

.

Entonces:

La resolucin depende de la cantidad de pulsos ck contabilizados durante t

x

.

Hay una relacin inversa entre resolucin y velocidad de conversin.

in x REF

Tv t V =

x

in REF

t

v V

T

=

65

2. Conversores A-D

e. ADC integracin (OBSOLETO)

Ventaja: - El ruido de frecuencia N/T es filtrado por el proceso de integracin.

Desventajas: - Requiere muchos componentes discretos.

- El valor de T depende de R y C (vara con la temperatura y tiene

alta dispersin, sobre todo el capacitor).

Por ejemplo:

- Si T = 20ms o 40ms o 60ms

entonces el ADC es

inmune al ruido de la

red elctrica de

220V/50Hz (20ms)

- Para 110V/60Hz (16.6ms)

debe elegirse T = N*16.6ms

66

2. Conversores A-D

e. ADC integracin (ejemplo clsico) (OBSOLETO)

67

2. Conversores A-D

f. ADC - Sigma Delta

Ventajas: - La mayor parte del sistema es digital:

Integracin en C, DSP, etc.

No existen derivas trmicas

Bajo costo.

- No requiere Sample & hold ni filtros RC

- Muy bajo ruido de discretizacin Alta resolucin

- Bajo consumo

Desventaja: - La conversin es lenta, porque requiere muchas iteraciones.

68

2. Conversores A-D

f. ADC - Sigma Delta

Ver Simulacin Interactiva

ADCTutorial.jar

l lazo cerrado $uerza a >ue el valor l lazo cerrado $uerza a >ue el valor

medio de ? sea i@ual a . medio de ? sea i@ual a .

AN AN

: :

B?C 1 .

AN

La tensi La tensi n B?C es controlada por la n B?C es controlada por la

densidad de unos y ceros del densidad de unos y ceros del D D?AT E(T( ?AT E(T(

STR(M STR(MF F en 8 : en 8 :

.

AN

8 : 9 G 3

.

AN

8 : 3 G 9

( partir de B8C se o&tienen en E los ( partir de B8C se o&tienen en E los

N &its de salida mediante el $iltro di@ital y N &its de salida mediante el $iltro di@ital y

el el decimador decimador: :

B8C E

/0T

69

2. Conversores A-D

f. ADC - Sigma Delta: Noise Shaping!

Modelo del ruido de cuantizacin:

70

2. Conversores A-D

f. ADC - Sigma Delta: Noise Shaping!

La ecuacin del lazo resulta:

( )

1

- Y X Y Q

f

= +

Modelo del ruido de cuantizacin:

71

2. Conversores A-D

f. ADC - Sigma Delta: Noise Shaping!

La ecuacin del lazo resulta:

Eespejando la seal de salida:

f H I ) JK I3L

f H I K J) I3L

1 1

X Q f

Y

f f

= +

+ +

( )

1

- Y X Y Q

f

= +

Modelo del ruido de cuantizacin:

72

2. Conversores A-D

f. ADC - Sigma Delta: Noise Shaping!

La ecuacin del lazo resulta:

Eespejando la seal de salida:

f H I ) JK I3L

f H I K J) I3L

Seal

Ruido de

cuantizacin

Motencia

Nrecuencia

1 1

X Q f

Y

f f

= +

+ +

( )

1

- Y X Y Q

f

= +

K$s

,

K$s

Modelo del ruido de cuantizacin:

73

2. Conversores A-D

f. ADC - Sigma Delta: Noise Shaping!

La ecuacin del lazo resulta:

Eespejando la seal de salida:

f H I ) JK I3L

f H I K J) I3L

Seal

Ruido de

cuantizacin

Motencia

Nrecuencia

1 1

X Q f

Y

f f

= +

+ +

( )

1

- Y X Y Q

f

= +

K$s

,

K$s

Modelo del ruido de cuantizacin:

74

2. Conversores A-D

f. ADC - Sigma Delta: Noise Shaping!

La ecuacin del lazo resulta:

Eespejando la seal de salida:

f H I ) JK I3L

f H I K J) I3L

Seal

Ruido de

cuantizacin

Motencia

Nrecuencia

1 1

X Q f

Y

f f

= +

+ +

( )

1

- Y X Y Q

f

= +

K$s

,

K$s

Modelo del ruido de cuantizacin:

75

2. Conversores A-D

f. ADC - Sigma Delta: Noise Shaping!

La ecuacin del lazo resulta:

Eespejando la seal de salida:

f H I ) JK I3L

f H I K J) I3L

Seal

Ruido de

cuantizacin

Motencia

Nrecuencia

1 1

X Q f

Y

f f

= +

+ +

( )

1

- Y X Y Q

f

= +

$s

,

$s

Modelo del ruido de cuantizacin:

76

2. Conversores A-D

f. ADC - Sigma Delta: Noise Shaping!

La ecuacin del lazo resulta:

Eespejando la seal de salida:

f H I ) JK I3L

f H I K J) I3L

Seal

Ruido de

cuantizacin

Motencia

Nrecuencia

1 1

X Q f

Y

f f

= +

+ +

( )

1

- Y X Y Q

f

= +

$s

,

$s

Modelo del ruido de cuantizacin:

Se reduce notablemente

el ruido de cuantizacin!!

77

2. Conversores A-D

f. ADC - Sigma Delta: Noise Shaping!

(umentando el orden del modulador se o&tienen mejores SNR:

8onversor O O" "P P de se@undo orden

78

2. Conversores A-D

f. ADC - Sigma Delta: Noise Shaping!

(umentando el orden del modulador se o&tienen mejores SNR:

8onversor O O" "P P de se@undo orden

79

2. Conversores A-D

f. ADC - Sigma Delta: Noise Shaping!

(umentando el orden del modulador se o&tienen mejores SNR:

8onversor O O" "P P de se@undo orden

ENOB = 13

ENOB = 16.3

ENOB = 9.7

ENOB = 6.3

ENOB = 19.6

ENOB = 3.0

80

2. Conversores A-D

f. ADC - Sigma Delta: Noise Shaping!

(umentando el orden del modulador se o&tienen mejores SNR:

8onversor O O" "P P de se@undo orden

ENOB = 13

ENOB = 16.3

ENOB = 9.7

ENOB = 6.3

ENOB = 19.6

ENOB = 3.0

81

2. Conversores A-D

f. ADC - Sigma Delta (ejemplo de diseo)

Digitalizar una seal de audio de

20Hz - 20kHz con una SNR de 80dB

82

2. Conversores A-D

f. ADC - Sigma Delta (ejemplo de diseo)

Digitalizar una seal de audio de

20Hz - 20kHz con una SNR de 80dB

Solucin:

Existen dos alternativas:

Utilizar un - de tercer orden.

Esto implica un K de 26:

fs = 20kHz x 2 x 26 = 1.04MHz

Utilizar un - de segundo orden.

Esto implica un K de 85:

fs = 20kHz x 2 x 84 = 3.36MHz

26 85

ENOB = 13

ENOB = 16.3

ENOB = 9.7

ENOB = 6.3

ENOB = 19.6

ENOB = 3.0

83

2. Conversores A-D

f. ADC - Sigma Delta (ejemplo de diseo)

Digitalizar una seal de audio de

20Hz - 20kHz con una SNR de 80dB

Solucin:

Existen dos alternativas:

Utilizar un - de tercer orden.

Esto implica un K de 26:

fs = 20kHz x 2 x 26 = 1.04MHz

Utilizar un - de segundo orden.

Esto implica un K de 85:

fs = 20kHz x 2 x 84 = 3.36MHz

El ENOB ser de: (80dB 1.76dB)/6.02 = 13bits

26 85

ENOB = 13

ENOB = 16.3

ENOB = 9.7

ENOB = 6.3

ENOB = 19.6

ENOB = 3.0

84

2. Conversores A-D

f. ADC - Sigma Delta (ejemplo de diseo)

Digitalizar una seal de audio de

20Hz - 20kHz con una SNR de 80dB

Solucin:

Existen dos alternativas:

Utilizar un - de tercer orden.

Esto implica un K de 26:

fs = 20kHz x 2 x 26 = 1.04MHz

Utilizar un - de segundo orden.

Esto implica un K de 85:

fs = 20kHz x 2 x 84 = 3.36MHz

El ENOB ser de: (80dB 1.76dB)/6.02 = 13bits

Puedo poner una salida de 16 bits, pero slo 13 bits contendrn informacin til.

26 85

ENOB = 13

ENOB = 16.3

ENOB = 9.7

ENOB = 6.3

ENOB = 19.6

ENOB = 3.0

85

2. Conversores A-D

f. ADC - Sigma Delta

Ventajas:

La mayor parte del sistema es digital:

- Posibilidad de alta integracin en C, DSP, etc.

- No existen derivas trmicas ni temporales.

- Bajo costo.

La alta tasa de sobre-muestreo y la baja precisin de la conversin analgica implica:

- No se requiere circuitos externos de sample & hold

- No se requieren filtros antialiasing (Ej. RC pasa-bajos)

El filtro digital permite obtener:

- Excelente figura de ruido

- Minimizacin del ruido en puntos crticos (Ej. 50/60 Hz)

- Nivel de ruido independiente de la amplitud de la seal

Es un diseo inherentemente monotnico y lineal

- Ideal para lazos cerrados de control

Desventajas:

Limitacin en la velocidad de conversin debido a la necesidad de sobremuestreo.

Problemas en sistemas multiplexados debido a la latencia del filtro digital:

- Sin embargo, en estos casos la solucin ms econmica y conveniente es

colocar un circuito integrado con varios Sigma-Delta incorporados.

86

2. Conversores A-D

f. ADC - Sigma Delta (ejemplo)

Figure 6. Schematic of the AD7793

87

2. Conversores A-D

f. ADC - Sigma Delta (ejemplo)

Figure 6. Schematic of the AD7793

88

2. Conversores A-D

f. ADC - Sigma Delta (ejemplo)

Figure 6. Schematic of the AD7793

131dB

89

2. Conversores A-D

f. ADC - Sigma Delta (simulacin en LTspice)

Figure 6. Schematic of the AD7793

90

2. Conversores A-D

f. ADC - Sigma Delta (simulacin en LTspice)

Figure 6. Schematic of the AD7793

91

2. Conversores A-D

f. ADC - Sigma Delta (Inmunidad a variaciones de la ganancia)

Figure 6. Schematic of the AD7793

Una variacin del 20% en la ganancia

slo produce una variacin de 2dB en

en el ruido de fondo de 80dB.

92

3. Conversores D-A

93

3. Conversores D-A

Introduccin

Un DAC convierte una entrada digital a una seal analgica de salida:

El resultado es una aproximacin con escalones:

94

3. Conversores D-A

La conversin DA introduce distorsin armnica

La discretizacin puede verse como el producto con un tren de deltas de Dirac

y la posterior convolucin con una ventana cuadrada:

En el dominio de la frecuencia esto equivale a convolucionar la seal con un

tren de deltas de frecuencia f

c

y multiplicar por una ventana sinc.

Genera armnicos superiores que pueden filtrarse con un pasabajos.

95

3. Conversores D-A

La conversin DA introduce distorsin armnica

La discretizacin puede verse como el producto con un tren de deltas de Dirac

y la posterior convolucin con una ventana cuadrada:

En el dominio de la frecuencia esto equivale a convolucionar la seal con un

tren de deltas de frecuencia f

c

y multiplicar por una ventana sinc.

Genera armnicos superiores que pueden filtrarse con un pasabajos.

Esta falta de

planicidad se

puede ecualizar

96

3. Conversores D-A

Tiempo de establecimiento Settling time

En algunas aplicaciones puede ser importante el tiempo de establecimiento.

Ejemplo: en un display de video puede haber una transicin entre negro y blanco

entre pixeles adyacentes y esto debe resolverse en <5% del ancho de un pixel.

En un display de 1024768 y refresh rate de 60Hz se recorre cada pixel en 16 ns.

Esto implica que la seal de salida se debe estabilizar en menos de 1 ns.

97

3. Conversores D-A

Tiempo de establecimiento Settling time

Tambin es importante analizar la transicin entre 01111 y 10000.,

que es cuando se producen el mayor nmero de conmutaciones internas:

Este glitch introduce una fuerte distorsin armnica.

98

3. Conversores D-A

Distorsin armnica

Los armnicos out of band son filtrables, pero los in band no son filtrables:

99

3. Conversores D-A

Distorsin armnica

Muchos DACs se usan en comunicaciones o anlisis espectrales, por lo que en

general se especifican parmetros como:

100

3. Conversores D-A

Distorsin armnica

Muchos DACs se usan en comunicaciones o anlisis espectrales, por lo que en

general se especifican parmetros como:

- Distorsin armnica total (THD)

Suma de los armnicos 2 a 6

101

3. Conversores D-A

Distorsin armnica

Muchos DACs se usan en comunicaciones o anlisis espectrales, por lo que en

general se especifican parmetros como:

- Distorsin armnica total (THD)

Suma de los armnicos 2 a 6

- Relacin seal a ruido (SNR)

102

3. Conversores D-A

Distorsin armnica

Muchos DACs se usan en comunicaciones o anlisis espectrales, por lo que en

general se especifican parmetros como:

- Distorsin armnica total (THD)

Suma de los armnicos 2 a 6

- Relacin seal a ruido (SNR)

- SINAD

103

3. Conversores D-A

Distorsin armnica

El tipo de ruido resultante depende tambin de la relacin entre la frecuencia de

conversin (f

c

) y la frecuencia de la seal digital de entrada (f

o

):

104

3. Conversores D-A

Caracterizacin de DACs

Se ingresa con una seal sinusoidal y se analiza el resultado:

105

3. Conversores D-A

Caractersticas de los DACs

Entradas digitales:

Resolucin [Bits]

Update rate

Nmero de canales

Tipo de interfaz

Salidas analgicas:

Tensin o corriente

Unipolar o bipolar

Rango de seal

Settling time

Detalles adicionales:

Tensin de alimentacin

Consumo de potencia

Tensin de referencia interna o externa

Clock del conversor interno o externo

PRECIO

Error de offset

Error de ganancia

Monotonicidad

Relacin seal/ruido

Encapsulado

106

3. Conversores D-A

a. DAC - Red de resistencias ponderadas

El siguiente circuito permite convertir una seal digital en una analgica:

El problema es que para lograr mucha resolucin se requiere resistencias de

mucha exactitud que cubran un rango muy amplio de valores.

Adems genera mucho ruido de glitch.

107

3. Conversores D-A

b. DAC - Red de resistencias R2R

El siguiente circuito slo utiliza resistores de valor R y 2R:

De esta manera ya no se requieren resistencias de mucha exactitud que cubran

un rango muy grande de valores, como el DAC de resistencias ponderadas.

Pero igualmente genera mucho ruido de glitch.

108

3. Conversores D-A

c. DAC Kelvin divider o Fully decoder DACs o string DACs o thermother

El conversor ms elemental que no genera glitch es termomtrico:

- Es una arquitectura simple

- Es inherentemente monotnico.

- Tiene muy bajo glitch (conmuta un solo switch).

- DIFICULTAD: No se pueden crear redes de ms de ~255 resistores (8 bits).

109

3. Conversores D-A

c. DAC Kelvin divider o Fully decoder DACs o string DACs o thermother

110

3. Conversores D-A

d. DAC Low distortion DACs

La cantidad de conmutaciones puede minimizarse subdiviendo el rango :

- Es una arquitectura relativamente simple.

- Es inherentemente monotnico.

- Tiene muy bajo glitch (conmuta un solo switch).

- DIFICULTAD: No se pueden crear redes de ms de ~255 resistores (8 bits).

111

3. Conversores D-A

e. DAC Low distortion DACs

Para minimizar los glitches pueden utilizarse un latch intermedio:

Pero nuevamente la dificultad se presenta para resoluciones altas.

Pero est tcnica se usa en los MSBs de los DACs y mejora mucho los glitches

112

3. Conversores D-A

e. DAC Low distortion DACs

Ejemplo de aplicacin prctica: AD9772 TxDAC14-BIT CMOS DAC CORE

113

3. Conversores D-A

d. Interpolating DACs

Se puede disminuir el ruido introducido en la seal mediante un interpolador

que genere valores digitales intermedios entre muestras consecutivas.

114

3. Conversores D-A

d. Interpolating DACs

Ejemplo de aplicacin prctica: AD9772 TxDAC14-BIT CMOS DAC CORE

115

3. Conversores D-A

e. SigmaDeltas DACs

Dada una seal digital se puede usar un modulador SigmaDelta digital para

que genere un bit stream y despus filtrar analgicamente:

Esta misma idea se puede aplicar para obtener moduladores sigma-delta de

orden superior.

Se pueden disear sistemas ms complejos y con mejores prestaciones.

Digital to Digital converter

0100011001101..

0/1

00000/11111

R

C

116

3. Conversores D-A

e. SigmaDeltas DACs (ejemplo)

117

3. Conversores D-A

e. Sigma-Deltas DACs

Dada una seal interpolada digitalmente se puede usar un Sigma-Delta:

118

FIN.

S-ar putea să vă placă și

- Construccion Con Panel TRIDITECDocument24 paginiConstruccion Con Panel TRIDITECOmegacool100% (5)

- Caracterización FloraDocument30 paginiCaracterización FloraRosana OtalvarezÎncă nu există evaluări

- Apunte - Maritza Montero. Introducción A La Psicología Comunitaria. Cap 8 - La Participación en El Trabajo Comunitario.Document8 paginiApunte - Maritza Montero. Introducción A La Psicología Comunitaria. Cap 8 - La Participación en El Trabajo Comunitario.Belén Canteros0% (1)

- Ciencia y Práctica de La IridologíaDocument389 paginiCiencia y Práctica de La Iridologíatoseguiolatinmail97% (33)

- Avanze 2Document21 paginiAvanze 2Elvin Nuñez TorresÎncă nu există evaluări

- Protocolo Del Test TeaDocument28 paginiProtocolo Del Test TeaMaria Ventura ParedesÎncă nu există evaluări

- MatrizDocument5 paginiMatrizjulio hurtadoÎncă nu există evaluări

- ARQUETIPOS SISTÉMICOS AlanDocument19 paginiARQUETIPOS SISTÉMICOS AlanHarry DelgadoÎncă nu există evaluări

- Practica n2 Pureza CianuroDocument9 paginiPractica n2 Pureza CianuroEdson HurtadoÎncă nu există evaluări

- Sistemas Integrados de Gestión PDFDocument390 paginiSistemas Integrados de Gestión PDFAna María FV0% (1)

- Bases científicas de los aceites esencialesDocument5 paginiBases científicas de los aceites esencialesYOVANI RODRIGUEZ PEREZÎncă nu există evaluări

- Solubilidad de compuestos en agua, acetona y etanolDocument7 paginiSolubilidad de compuestos en agua, acetona y etanolArv RiañoÎncă nu există evaluări

- Formato de Evaluación de Desempeño de 180° (Aux Contable)Document4 paginiFormato de Evaluación de Desempeño de 180° (Aux Contable)Laura Lorena Cerquera Barrera100% (1)

- DIA Proyecto Ampliacion Servicio Energia Electirca CP ChenchenDocument133 paginiDIA Proyecto Ampliacion Servicio Energia Electirca CP Chenchenyois casamayorÎncă nu există evaluări

- Fua Sis Adolescente RC 017Document2 paginiFua Sis Adolescente RC 017LORENA ROSALINDA QUINTO RODRIGUEZÎncă nu există evaluări

- Telefonica MovistarDocument5 paginiTelefonica MovistarKatia DunsephÎncă nu există evaluări

- Estructura microscópica de los palos de yerba mateDocument5 paginiEstructura microscópica de los palos de yerba mateBruno LopezÎncă nu există evaluări

- Cartel Inspeccion AmpostaDocument2 paginiCartel Inspeccion Ampostavideos gym VictorPascualÎncă nu există evaluări

- Bomba de Plastico X-Class Stubbe Heavy-Duty PumpDocument11 paginiBomba de Plastico X-Class Stubbe Heavy-Duty PumpBase SistemasÎncă nu există evaluări

- Plan estratégico hospital Carlos Monge Medrano-Juliaca PunoDocument28 paginiPlan estratégico hospital Carlos Monge Medrano-Juliaca PunoBraulio Joel JM100% (1)

- 0606 Sistemas Operativos 2003-2Document5 pagini0606 Sistemas Operativos 2003-2iespaaÎncă nu există evaluări

- Cuestionario Sobre El Origen de Las EspeciesDocument3 paginiCuestionario Sobre El Origen de Las EspeciesFernándo nieto100% (1)

- Arjun Appadurai en Su Libro “La Modernidad Desbordada- Dimensiones Culturales de La Globalización” Plantea Una Teoría de La Ruptura, En La Cual Sostiene Que La Modernidad Es Una Etapa Reciente en Donde Grandes Flujos rDocument2 paginiArjun Appadurai en Su Libro “La Modernidad Desbordada- Dimensiones Culturales de La Globalización” Plantea Una Teoría de La Ruptura, En La Cual Sostiene Que La Modernidad Es Una Etapa Reciente en Donde Grandes Flujos rEmanuel AlejandroÎncă nu există evaluări

- 02.formato Clase 02Document22 pagini02.formato Clase 02diego guzmanÎncă nu există evaluări

- Actividad Integradora - SuturaDocument3 paginiActividad Integradora - Suturagerman p0% (1)

- Actividad 2. Evidencia 2Document4 paginiActividad 2. Evidencia 2yongeiber posadaÎncă nu există evaluări

- Exposición Siderurgia BasicaDocument35 paginiExposición Siderurgia BasicaPrincipeg WalterÎncă nu există evaluări

- CUROBA - Cronograma de Obra - Los Parques de Comas - 12-12xlsxDocument42 paginiCUROBA - Cronograma de Obra - Los Parques de Comas - 12-12xlsxjustthhua-1Încă nu există evaluări

- Tema 6 Teoría Unid. EstratigraficasDocument22 paginiTema 6 Teoría Unid. EstratigraficasCarlos Gonzalez VergaraÎncă nu există evaluări

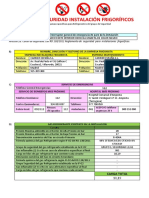

- Gases medicinales e instalacionesDocument18 paginiGases medicinales e instalacionesIvonn OchoaÎncă nu există evaluări