Documente Academic

Documente Profesional

Documente Cultură

GP22 Interlock PSL Limitations

Încărcat de

veeraboss0 evaluări0% au considerat acest document util (0 voturi)

34 vizualizări3 paginiThis document defines limitations for programmable scheme logic (PSL) automations in AREVA T&D MiCOM C264 devices. It specifies that there is a maximum of 768 blocks per device, with each block limited to 3 levels and 256 inputs. Interlocking equations are also limited to 512 maximum. The goals are to keep PSL automations simple, instantaneous, and easy to analyze for debugging purposes.

Descriere originală:

interlock

Drepturi de autor

© © All Rights Reserved

Formate disponibile

PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentThis document defines limitations for programmable scheme logic (PSL) automations in AREVA T&D MiCOM C264 devices. It specifies that there is a maximum of 768 blocks per device, with each block limited to 3 levels and 256 inputs. Interlocking equations are also limited to 512 maximum. The goals are to keep PSL automations simple, instantaneous, and easy to analyze for debugging purposes.

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

34 vizualizări3 paginiGP22 Interlock PSL Limitations

Încărcat de

veerabossThis document defines limitations for programmable scheme logic (PSL) automations in AREVA T&D MiCOM C264 devices. It specifies that there is a maximum of 768 blocks per device, with each block limited to 3 levels and 256 inputs. Interlocking equations are also limited to 512 maximum. The goals are to keep PSL automations simple, instantaneous, and easy to analyze for debugging purposes.

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 3

AREVA T&D Protection & Contrle Avenue de Figuires Font de la Banquire BP75 34975 Lattes Cedex (France)

Tl. : +33 (0) 4 67 20 54 54 - Fax : +33 (0) 4 67 20 54 99

Socit Anonyme au capital de 16 000 000 -343 074 142 RCS Montpellier - Siret 343 074 142 00070 - Code APE 312B

Sood Pructices V 4,0

SPZZ PSL / InterIock Iimitutions

Document version 1.0

Creation 14/05/2007

Last update 14/05/2007

Author Pierre-Yves LEGRIS

Josselin DOHOLLO

Category SCE / FBD Editor

Language English

File name GP22_Interlock_PSL_Limitations.doc

CONTENTS

1. SCOPE............................................................................................................................................ 2

2. INTRODUCTION......................................................................................................................... 2

3. RULES............................................................................................................................................ 2

3.1. MAXIMA.................................................................................................................................. 2

3.2. DESCRIPTION AND EXAMPLES.................................................................................................. 3

4. CONCLUSION.............................................................................................................................. 3

AREVA T&D Protection & Contrle Avenue de Figuires Font de la Banquire BP75 34975 Lattes Cedex (France)

Tl. : +33 (0) 4 67 20 54 54 - Fax : +33 (0) 4 67 20 54 99

Socit Anonyme au capital de 16 000 000 -343 074 142 RCS Montpellier - Siret 343 074 142 00070 - Code APE 312B

1. Scope

The purpose of this good practice is to define the limitations of PSL automations.

2. Introduction

The MiCOM C264 can be configured to create logical schemes through Isagraf, PSL and

interlock equations.

Definitions:

FBD: one automation scheme based on logic operators, timers, RS gates, having one or

several input/outputs. each FBD is edited with the SCE / FBD Editor

PSL: Set of all the automation schemes (named FBD) based on logics, integrated in a

MiCOM C264 and edited with SCE/ FBD editor

Interlock equation: specific logic scheme with one output, directly associated to a BAY

control and integrating some logical operators (OR, AND, NOT, XOR)

The purpose of the PSL and interlock equations is to execute simple logical schemes upon

change of one of its logical input, i.e. on an event basis. PSL also accommodate timer

operator in order to process slightly more complex schemes. The use of Isagraf is for more

complex schemes, typically sequential, executed on a periodical basis (from 50 ms and

above depending on the computer load).

3. Rules

In term of PSL the programming shall be organised in simple blocks. A block is made of

one or several OR, AND, NOT, XOR, NAND and NOR operators, and has one output. The

blocks are then chained by timers (minimum 50 ms) or RS gates inside one PSL or FBD.

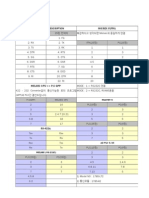

3.1. Maxima

There is a maximum of 768 blocks per MiCOM C264. One FBD has a minimum of one block

(more if the FBD contains timers or RS gates).

A timer counts as a block.

An interlocking equation counts as a block as well and there is a maximum of 512

interlocking equations.

RS Gates do not count in the total number of blocks; each of RS input is associated to a

blocks output.

There are also 256 logical operations available (i.e. [A & B] OR [C & D] by developing [A

OR C] & [B OR C] & [A OR D] & [B OR D] and gives 7 logical operations).

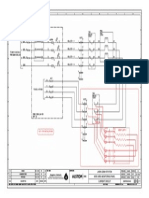

A block shall have a maximum of 3 levels, as explained in the figure 1, able to be:

- executed instantaneously (few ms, depending on the computer load),

- analysed easily for tuning purpose,

- constrained in term of number of inputs and gates.

The engineering tool enables to have more than 3 levels however the debug and sizing of

the PSL becomes unpractical and is thus not described hereafter.

AREVA T&D Protection & Contrle Avenue de Figuires Font de la Banquire BP75 34975 Lattes Cedex (France)

Tl. : +33 (0) 4 67 20 54 54 - Fax : +33 (0) 4 67 20 54 99

Socit Anonyme au capital de 16 000 000 -343 074 142 RCS Montpellier - Siret 343 074 142 00070 - Code APE 312B

AND

AND

/OR

AND

/OR

Output

Inputs

Level 1

M inputs per gate

AND

AND

etc.

AND

/OR

etc.

AND

/OR

AND

AND

AND

Level 2

N inputs per gate

Level 3

P inputs per gate

M inputs per gate

N inputs per gate

P inputs

Figure 1: A block shall have a maximum of 3 levels

3.2. Description and examples

The first level of a block shall be made of AND, NOT or NOR gates only, in order to

increase the PSL capabilities. OR, NAND and XOR shall be handled by a specific block.

One block can get up to 256 inputs and up to 4 outputs.

3.2.1. 1 gate per level

For a given block, there is a maximum of 256 inputs. This corresponds to the extreme case

where each level has a single gate, i.e. 3 gates in total, M = 256, N = P = 1 (M, N and P are

defined in the diagram).

3.2.2. More than 1 gate at 1st level

When a level of a block has more than one gate the worst case corresponds to a level 3

made of OR/NOR/XOR gates only and a level 3 made of one AND/NAND gate. In this case

the configuration shall not exceed:

- Either M = 10 inputs at level 1, N = 2 inputs at level 2 and P = 3 inputs at level 3.

This corresponds to 60 external inputs and 10 gates.

- Or M = N = P = 3. This corresponds to 27 inputs and 13 gates.

These limits might be exceeded depending on the occupation of a given level (i.e. existence

or not of the maximum number of inputs per gate) and type of gates.

4. Conclusion

- PSL Max_nb =768 ---------- Interlock equations: max_nb = 512

---------- FBD: max_nb= (768 interlock_equations_nb)

- Each input might be present in a maximum of 256 blocks.

- The MiCOM C264 can manage up to 5600 binary values, that are part of PSL or

not.

S-ar putea să vă placă și

- Divine CouncilDocument23 paginiDivine CouncilDaniel Tanasa100% (3)

- Application Configuration RET670 2Document24 paginiApplication Configuration RET670 2veerabossÎncă nu există evaluări

- Varga ChartsDocument39 paginiVarga Chartsalnewman100% (2)

- Relay Setting For 7ut51 Differential Protection RelayDocument12 paginiRelay Setting For 7ut51 Differential Protection Relayyesrojas100% (1)

- Read Me Slave 2.1Document7 paginiRead Me Slave 2.1Prasad VylaleÎncă nu există evaluări

- Questions On Logic SynthesisDocument11 paginiQuestions On Logic SynthesisrAM89% (9)

- Rituals Taken From Filipino Sorcerer - For Success To Your Plans and Personal Undertakings and For Those Who Has Hatre - WattpadDocument3 paginiRituals Taken From Filipino Sorcerer - For Success To Your Plans and Personal Undertakings and For Those Who Has Hatre - WattpadGene Ganutan50% (2)

- Serial Port rs232Document35 paginiSerial Port rs232dokeosÎncă nu există evaluări

- Tutorial-Using SCI For Real-Time Monitoring in TI F28335 TargetDocument12 paginiTutorial-Using SCI For Real-Time Monitoring in TI F28335 TargetHector Jalil DesirenaÎncă nu există evaluări

- CISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkDe la EverandCISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkÎncă nu există evaluări

- VLSI RamDocument18 paginiVLSI RamrAM100% (4)

- Digital Design Interview Questions & AnswersDocument5 paginiDigital Design Interview Questions & AnswersSahil KhanÎncă nu există evaluări

- FPGA Interview QuestionsDocument11 paginiFPGA Interview Questionssneha587Încă nu există evaluări

- IP Routing Protocols All-in-one: OSPF EIGRP IS-IS BGP Hands-on LabsDe la EverandIP Routing Protocols All-in-one: OSPF EIGRP IS-IS BGP Hands-on LabsÎncă nu există evaluări

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationDe la EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationÎncă nu există evaluări

- 8 - Class INTSO Work Sheet - 1 - Basics On GeometryDocument2 pagini8 - Class INTSO Work Sheet - 1 - Basics On Geometryyoutuber tanishÎncă nu există evaluări

- USB Protocol Specification: Data Encoding/DecodingDocument12 paginiUSB Protocol Specification: Data Encoding/DecodingUtpal100% (5)

- Concept of ERS in SAP MMDocument9 paginiConcept of ERS in SAP MMARABINDA CHAKRAVARTYÎncă nu există evaluări

- Application Configuration RET670 3Document23 paginiApplication Configuration RET670 3veerabossÎncă nu există evaluări

- DRS202M Modbus Register MapDocument15 paginiDRS202M Modbus Register MapSocaciu VioricaÎncă nu există evaluări

- Z3 2 4Document104 paginiZ3 2 4Vu Duc Hoan100% (1)

- 02 - SDH IntroductionDocument96 pagini02 - SDH IntroductionKunwar Sandeep S Chauhan100% (1)

- SDH BasicsDocument46 paginiSDH BasicsmettlemasterÎncă nu există evaluări

- Deld End Sem 5,6Document6 paginiDeld End Sem 5,6The GK TalksÎncă nu există evaluări

- Modbus Rtu Protocol PDFDocument18 paginiModbus Rtu Protocol PDFsavaobayÎncă nu există evaluări

- 10 DevicesDocument34 pagini10 DevicesRajesh NelavalaÎncă nu există evaluări

- TrondecDocument12 paginiTrondecHenry DengÎncă nu există evaluări

- Network Variables For EXOline and Modbus EnglishDocument46 paginiNetwork Variables For EXOline and Modbus EnglishVlad Stefan CristianÎncă nu există evaluări

- XNC Modbus MasterDocument12 paginiXNC Modbus Masterjgr77Încă nu există evaluări

- 10 DevicesDocument34 pagini10 DevicesFeroz ShaikÎncă nu există evaluări

- Alarm Modbus Protocol Uk PDFDocument29 paginiAlarm Modbus Protocol Uk PDFMiguel Angel Bedolla PonceÎncă nu există evaluări

- Show Interface in DepthDocument12 paginiShow Interface in DepthIvan MachuzaÎncă nu există evaluări

- Protocol Max v4: Third Party InterfaceDocument16 paginiProtocol Max v4: Third Party InterfaceHugo LoureiroÎncă nu există evaluări

- PLC Communication Options For Electro 19288097645029848Document5 paginiPLC Communication Options For Electro 19288097645029848Rajesh RavichandranÎncă nu există evaluări

- University Automoma of Queretaro Engineering Faculty: Digital System 2Document15 paginiUniversity Automoma of Queretaro Engineering Faculty: Digital System 2Carlos Eduardo Martínez Hernández100% (1)

- Nexus 9000 Cloud Scale ASIC (Tahoe) NX-OS ELAMDocument7 paginiNexus 9000 Cloud Scale ASIC (Tahoe) NX-OS ELAMIsmail MirzayevÎncă nu există evaluări

- Amm Cheet PrintDocument7 paginiAmm Cheet PrintjokerÎncă nu există evaluări

- LTE - PRACH DetectionDocument12 paginiLTE - PRACH DetectionAshish ShuklaÎncă nu există evaluări

- Modbus App v00Document43 paginiModbus App v00siashahabÎncă nu există evaluări

- SIMCON, Ver. 3.0.: FPGA Based, DSP Integrated, 8-ChannelDocument34 paginiSIMCON, Ver. 3.0.: FPGA Based, DSP Integrated, 8-ChanneljuanÎncă nu există evaluări

- Test2 Aplicatii CID Seriaf V4.ro - enDocument3 paginiTest2 Aplicatii CID Seriaf V4.ro - enAmmarArshadÎncă nu există evaluări

- 2CSG445012D0201 - Modbus Communication Protocol - M2M BasicDocument13 pagini2CSG445012D0201 - Modbus Communication Protocol - M2M BasicJoako FilipovichÎncă nu există evaluări

- A Turbo Co/Decoder Implementation For Next Generation DVB-S2Document10 paginiA Turbo Co/Decoder Implementation For Next Generation DVB-S2rohitvanÎncă nu există evaluări

- Constant Log BCJR Turbo Decoder With Pipelined ArchitectureDocument5 paginiConstant Log BCJR Turbo Decoder With Pipelined ArchitectureInternational Journal of Scientific Research and Engineering StudiesÎncă nu există evaluări

- I2CDocument6 paginiI2CGovinda RaoÎncă nu există evaluări

- EI2353 DSDQbankDocument24 paginiEI2353 DSDQbankRaja RockÎncă nu există evaluări

- EL - 302 Instrumentation & Measurements: Experiment # 13Document5 paginiEL - 302 Instrumentation & Measurements: Experiment # 13Lala's gamingÎncă nu există evaluări

- Forlong Modbus Protocol V3.0 - 1-4Document36 paginiForlong Modbus Protocol V3.0 - 1-4Vidian Prakasa AriantoÎncă nu există evaluări

- SB Digi CommDocument12 paginiSB Digi CommpiyushpandeyÎncă nu există evaluări

- EPROM Micro With Real Time Clock: Features Package OutlineDocument40 paginiEPROM Micro With Real Time Clock: Features Package OutlineAakash SheelvantÎncă nu există evaluări

- Spot ProtocolDocument12 paginiSpot Protocolj_pozo_c209Încă nu există evaluări

- CPE 185 TestDocument16 paginiCPE 185 TestPaul DyeÎncă nu există evaluări

- Lab2 PabillaranDocument9 paginiLab2 PabillaranLouise Lope PabillaranÎncă nu există evaluări

- EL - 302 Instrumentation & Measurements: Experiment # 13Document5 paginiEL - 302 Instrumentation & Measurements: Experiment # 13Lala's gamingÎncă nu există evaluări

- DMX and Arduino TutorialDocument5 paginiDMX and Arduino TutorialHonorino García FernándezÎncă nu există evaluări

- GP16 Naming Rules enDocument3 paginiGP16 Naming Rules enveerabossÎncă nu există evaluări

- T BOX ManualDocument26 paginiT BOX ManualVlady TeoÎncă nu există evaluări

- Router 1X3 - RTL Design and VerificationDocument10 paginiRouter 1X3 - RTL Design and VerificationIJERDÎncă nu există evaluări

- SPM33 Modbus Address ListDocument26 paginiSPM33 Modbus Address ListjesankingÎncă nu există evaluări

- HomeDocument65 paginiHomecrsarinÎncă nu există evaluări

- Computer Instruction Set: - An Instruction Has Two ComponentsDocument25 paginiComputer Instruction Set: - An Instruction Has Two ComponentsKaniniAnbazhaganÎncă nu există evaluări

- IPR-A Communication Protocol GB V1.7Document14 paginiIPR-A Communication Protocol GB V1.7Seba Vásquez Von MulsowÎncă nu există evaluări

- PLC CableDocument17 paginiPLC CableDarlan MedeirosÎncă nu există evaluări

- Usb Implementation Using Utmi MacrocellDocument71 paginiUsb Implementation Using Utmi Macrocellrockfloyd100% (6)

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.De la EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Încă nu există evaluări

- LEARN MPLS FROM SCRATCH PART-B: A Beginners guide to next level of networkingDe la EverandLEARN MPLS FROM SCRATCH PART-B: A Beginners guide to next level of networkingÎncă nu există evaluări

- 03 UserMeeting Jordan 2014 PPT SamehEldmrdash 01Document12 pagini03 UserMeeting Jordan 2014 PPT SamehEldmrdash 01Felipe MonteroÎncă nu există evaluări

- t=τ - ln - I Ibase p I Ibase T T T: trip amb baseDocument6 paginit=τ - ln - I Ibase p I Ibase T T T: trip amb baseveerabossÎncă nu există evaluări

- Core Balance Current TransformersDocument2 paginiCore Balance Current TransformersveerabossÎncă nu există evaluări

- Mx7xI EN M D44Document138 paginiMx7xI EN M D44veerabossÎncă nu există evaluări

- BSP Lsp-1: Xct1 17818 Installed New 13 Xct2 X1C 1 3Document1 paginăBSP Lsp-1: Xct1 17818 Installed New 13 Xct2 X1C 1 3veerabossÎncă nu există evaluări

- Wide Area Page 10-ModelDocument1 paginăWide Area Page 10-ModelveerabossÎncă nu există evaluări

- CW - Fcm2043 - CHDocument3 paginiCW - Fcm2043 - CHFarrukhakaÎncă nu există evaluări

- Verilog Bhaskar .JDocument230 paginiVerilog Bhaskar .JSuraj GhaleÎncă nu există evaluări

- 12principles of Speech WritingDocument20 pagini12principles of Speech WritingIan Roy Monsanto BataanÎncă nu există evaluări

- Part 2 - Philo Oral Compre ReviewerDocument28 paginiPart 2 - Philo Oral Compre ReviewerJonathan RacelisÎncă nu există evaluări

- Unit 6 Lesson BDocument21 paginiUnit 6 Lesson BDianaÎncă nu există evaluări

- Arthalankaras in The BhattikavyaDocument14 paginiArthalankaras in The BhattikavyaPriyanka Mokkapati100% (1)

- Week 17 - Instructions - Task Assignment - Final Assignment - Applying To Disney - Part IDocument5 paginiWeek 17 - Instructions - Task Assignment - Final Assignment - Applying To Disney - Part IvanessaÎncă nu există evaluări

- Republique Du Senegal: MR Faye 776468049Document9 paginiRepublique Du Senegal: MR Faye 776468049Bass GueyeÎncă nu există evaluări

- Function Is To Entertain The ReadersDocument2 paginiFunction Is To Entertain The Readersedelweis salwa putriÎncă nu există evaluări

- Syntax: The Sentence Patterns of LanguageDocument7 paginiSyntax: The Sentence Patterns of LanguageEcha ChanÎncă nu există evaluări

- Lecture 1 and 2 Basic Concepts: Computer Organiaztion and Assembly LanguageDocument41 paginiLecture 1 and 2 Basic Concepts: Computer Organiaztion and Assembly LanguageABRAR RASUL QADRIÎncă nu există evaluări

- Chapter 3: Fixed Asset ReclassificationsDocument6 paginiChapter 3: Fixed Asset ReclassificationsAlice WairimuÎncă nu există evaluări

- Verbo To Be 1.Document25 paginiVerbo To Be 1.leny maritza alvarado huallccaÎncă nu există evaluări

- Cleopatra Finds Her VoiceDocument5 paginiCleopatra Finds Her Voiceapi-264591964Încă nu există evaluări

- Way of The Wolf SummaryDocument4 paginiWay of The Wolf SummaryJohn Arlo SanchezÎncă nu există evaluări

- How Picturebooks WorkDocument308 paginiHow Picturebooks Workdoraszujo1994Încă nu există evaluări

- 07DiA01 PDFDocument437 pagini07DiA01 PDFzeldasaÎncă nu există evaluări

- Sample Written Work RubricDocument1 paginăSample Written Work RubricFlower may DoctoleroÎncă nu există evaluări

- Cloud Server Administration Labs 2Document46 paginiCloud Server Administration Labs 2yanezhjsÎncă nu există evaluări

- Collocations - EnglishClub PDFDocument3 paginiCollocations - EnglishClub PDFInés Amaya DíazÎncă nu există evaluări

- PGP PI Module PDFDocument17 paginiPGP PI Module PDFRAMESHÎncă nu există evaluări

- Dwnload Full Business Statistics 2nd Edition Sharpe Test Bank PDFDocument35 paginiDwnload Full Business Statistics 2nd Edition Sharpe Test Bank PDFmislayersalad2qkh6u100% (9)

- Bổ sung Thì trong tiếng AnhDocument4 paginiBổ sung Thì trong tiếng AnhĐô Nguyễn TiếnÎncă nu există evaluări

- 66 Essential Phrasal Verbs EnglishDocument6 pagini66 Essential Phrasal Verbs EnglishNarcisVega100% (15)

- Chapter 4 - Hallidayan ApproachesDocument68 paginiChapter 4 - Hallidayan ApproachesMeti Mallikarjun100% (2)