Documente Academic

Documente Profesional

Documente Cultură

Logica de Emisor Acoplado

Încărcat de

ingenieross080 evaluări0% au considerat acest document util (0 voturi)

424 vizualizări14 paginiLOGICA DE EMISOR ACOPLADO

Titlu original

LOGICA DE EMISOR ACOPLADO

Drepturi de autor

© © All Rights Reserved

Formate disponibile

DOCX, PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentLOGICA DE EMISOR ACOPLADO

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca DOCX, PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

424 vizualizări14 paginiLogica de Emisor Acoplado

Încărcat de

ingenieross08LOGICA DE EMISOR ACOPLADO

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca DOCX, PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 14

Repblica Bolivariana de Venezuela

Ministerio del Poder Popular para la Educacin superior

Ministerio del Poder Popular la Defensa

UNEFA : Universidad Nacional Experimental de la Fuerza Armada

Ncleo-Trujillo

Ampliacin-Plata III

LOGICA DE EMISOR ACOPLADO

(ECL)

Integrantes:

Bermdez Magalys

Briceo German

Evangelista Pablo

Valera, Octubre 2014

INDICE

Introduccin..3

Historia de (ECL).....4

Que es lgica de emisor acoplado (ECL)?...........................................5

Estructura del ECL...6

Implementacin del ECL.6

Operaciones del ECL..7

Caractersticas del ECL8

Fundamentos del ECL .9

Configuracin de una ECL..10

Ventajas .13

Desventajas14

Conclusiones..14

Bibliografa..16

Introduccin

La Lgica Acoplada en Emisor o sus siglas en ingles (emmiter-

coupled logic) son unos circuitos integrados digitales los cuales usan

transistores bipolares, sin embargo a diferencia de los TTL en los ECL se

evita la saturacin de los transistores, lo cual ocasiona un incremento en la

velocidad total de conmutacin. La familia ECL opera bajo el principio de la

conmutacin de corriente, por el cual una corriente de polarizacin fija menor

que la corriente del colector de saturacin es conmutada del colector de un

transistor al otro.

En la lgica de emisor acoplado las tensiones de entrada y salida

tienen una pequea oscilacin, la impedancia de entrada es alta y la

resistencia de salida es baja, y como resultado, los transistores estados

cambian rpidamente, Adems, el consumo de corriente constante de los

amplificadores diferenciales minimiza los retrasos y problemas.

Su estructura se basa en un par diferencial en el que una rama se

conecta a una tensin de referencia, que determina el umbral alto o bajo y la

otra rama con n transistores en paralelo a las n entradas y obtener

simultneamente dos salidas. Estas salidas se llevan a sendos seguidores

de emisor para proporcionar ganancia en corriente .

Historia

Fue inventado en agosto de 1956 en IBM por Hannon S. Yourke.

Originalmente llamado la lgica actual de direccin, hace su aparecin en el

ao 62 con las primeras familias de circuitos integrados. Ya en aquella poca

se trataba de la familia ms rpida. Tambin se llama un circuito de modo

actual.

El interruptor de corriente de Yourke, tambin conocido como ECL, era

un amplificador diferencial, y los niveles lgicos de entrada eran diferentes de

los niveles lgicos de salida. En el modo de operacin actual, sin embargo, la

seal de salida se compone de los niveles de voltaje que varan sobre un

nivel de referencia diferente del nivel de referencia de entrada." En el diseo

de Yourke, los dos niveles de referencia lgicos difieren de 3 voltios. Por

consiguiente, se utilizaron dos versiones complementarias: una versin NPN

y una versin PNP. La salida NPN podra conducir entradas PNP, y vice-

versa. "Las desventajas son que se necesitan ms diferentes tensiones de

alimentacin, y ambos transistores npn y pnp se requieren.

En lugar de alterna etapas NPN y PNP, otro mtodo de acoplamiento

emplea diodos Zener y los resistores de cambiar los niveles de la lgica de

salida a ser el mismo que los niveles lgicos de entrada.

Circuitos ECL a mediados de la dcada de 1960 hasta la dcada de

1990 consisti en una etapa de entrada del amplificador diferencial para

llevar a cabo la lgica, seguido por un seguidor de emisor para impulsar las

salidas y cambiar las tensiones de salida para que sean compatibles con las

entradas.

Que es el circuito lgico de emisor acoplado (ECL)?

El circuito ECL se basa en el uso de un interruptor de direccin de

corriente, que se puede construir con un par diferencial, que se polariza con

un voltaje Vr y de corriente I ambos. la naturaleza diferencial del circuito lo

hace menos susceptible a captar ruido.

En electrnica, la lgica de emisor acoplado a una familia lgica

transistor bipolar de alta velocidad de circuitos integrados. ECL utiliza un

amplificador diferencial BJT saturado con la entrada de una sola terminal y la

corriente para evitar la zona saturada de la operacin y su comportamiento

de apagado lento emisor limitado. Como la corriente es dirigida entre dos

piernas de un par de emisores acoplados, tambin se llama a veces la lgica

actual de direccin, lgica en modo de corriente o la lgica emisor-seguidor

de corriente del interruptor.

En ECL, los transistores no son nunca en la saturacin, las tensiones

de entrada y salida tienen una pequea oscilacin, la impedancia de entrada

es alta y la resistencia de salida es baja, y como resultado, los transistores

estados cambian rpidamente, retardos de puerta son bajos, y la

convergencia de salida capacidad es alta. Adems, el consumo de corriente

esencialmente constante de los amplificadores diferenciales minimiza los

retrasos y problemas tcnicos debido a la inductancia de la lnea de

suministro y la capacitancia, y las salidas complementarias disminuir el

tiempo de propagacin de todo el circuito por el ahorro de convertidores

adicionales.

Estructura del ECL

La estructura ECL se basa en un par diferencial (Q1-Q2 y Q3) en el

que una rama se conecta a una tensin de referencia, que determina el

umbral ALTO / BAJO y la otra rama con n transistores en paralelo a las n

entradas. Del diferencial se pueden obtener simultneamente dos salidas

con la salida y la salida negada y muy bajo jitter entre ellas. Estas salidas se

llevan, finalmente, a sendos seguidores de emisor para proporcionar

ganancia en corriente y el fan-out adecuado, que en muchos casos pueden

alimentar lneas de 50 directamente. Es comn la presencia de pines de

alimentacin separados para estos ltimos transistores ya que, a diferencia

del par diferencial, su corriente varia con la seal si no estn los dos

transistores conectados a impedancias iguales. Alimentndolos

separadamente se evita que estas variaciones alcancen el par diferencial.

Implementacin del ECL

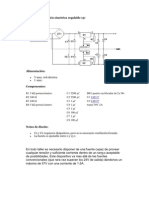

ECL se basa en un par de emisores acoplados, sombreado rojo en la

figura de la derecha. La mitad izquierda del par se compone de dos mdulos

de entrada conectado en paralelo transistores T1 y T2 se aplica el NI lgica.

La tensin de base del transistor T3 derecho se mantiene fijo por una fuente

de tensin de referencia, a la sombra luz verde: el divisor de tensin con un

diodo de compensacin trmica y, a veces un seguidor de emisor

almacenamiento en bfer, por lo que las tensiones de emisor se mantiene

relativamente constante. Como resultado, la resistencia de emisor RE comn

acta casi como una fuente de corriente. Las tensiones de salida en el

colector de carga resistencias RC1 y RC3 se desplazan y tamponarse a las

salidas inversora y no inversora de los seguidores de emisor T4 y T5. Las

resistencias de emisor de salida RE4 y RE5 no existen en todas las

versiones de ECL. En algunos casos, la lnea 50 O resistencias de

terminacin conectadas entre las bases de los transistores de entrada y -2 V

actan como resistencias de emisor.

Aplicaciones del ECL

Adems de las familias lgicas ECL I, ECL II, ECL III, ECL10K y ECL100K, la

tecnologa ECL se ha utilizando en circuitos LSI:

Matrices lgicas

Memorias (Motorola, Fairchild)

Microprocesadores (Motorola, F100 de Ferranti)

Para mejorar las prestaciones de la tecnologa CMOS, la ECL se incorpora

en ciertas funciones crticas en circuitos CMOS, aumentando la velocidad,

pero manteniendo bajo el consumo total.

Operacin del ECL

El funcionamiento del circuito ECL se considera a continuacin con

supuesto de que la tensin de entrada se aplica a la base de T1, T2,

mientras que la entrada no se utiliza o se aplica un "0" lgico.

Durante la transicin, el ncleo del circuito - el par emisor acoplado -

acta como un amplificador diferencial con la entrada de una sola terminal.

La "cola larga" fuente de corriente establece la corriente total que fluye a

travs de las dos piernas de la pareja. El voltaje de entrada controla la

corriente que fluye a travs de los transistores compartindolo entre las dos

piernas, dirigiendo todo a un lado cuando no est cerca del punto de

conexin. La ganancia es mayor que en los estados finales y los

interruptores de circuito de forma rpida.

A la tensin de entrada baja o en alta tensin de entrada est

sobrecargado el amplificador diferencial. El transistor es uno de corte y el

otro es en la regin lineal activa que acta como una etapa de emisor comn

con degeneracin de emisor que se lleva a toda la corriente, hambre

transistor de la otra de corte. El transistor activa se carga con el RE

resistencia relativamente alta emisor que introduce una retroalimentacin

negativa significativa. Para evitar la saturacin del transistor activa, de

manera que el tiempo de difusin que ralentiza la recuperacin de la

saturacin no estar involucrado en el retardo de la lgica, se eligen las

resistencias de emisor y colector de tal manera que a la tensin mxima de

entrada de alguna tensin se deja a travs del transistor. La ganancia

residual es bajo. El circuito es insensible a las variaciones de la tensin de

entrada y el transistor se mantiene firmemente en su regin lineal activa. La

resistencia de entrada es alto debido a la retroalimentacin negativa serie. El

transistor de corte se rompe la conexin entre su entrada y salida. Como

resultado, su voltaje de entrada no afecta a la tensin de salida. La

resistencia de entrada es alto de nuevo ya que la unin base-emisor es de

corte.

Caractersticas del ECL

Otras caractersticas notables de la familia ECL incluyen el hecho de

que la gran requisito actual es aproximadamente constante, y no depende

significativamente sobre el estado del circuito. Esto significa que los circuitos

ECL generan relativamente poca potencia de ruido, a diferencia de muchos

otros tipos de lgica que generalmente atraen mucho ms actual al cambiar

de reposo, por lo que la potencia de ruido puede llegar a ser problemtico.

En aplicaciones criptogrficas, circuitos ECL tambin son menos susceptibles

a los ataques de canal lateral, tales como anlisis de la potencia diferencial.

El tiempo de propagacin de esta disposicin puede ser menos de un

nanosegundo, por lo que es durante muchos aos la familia lgica ms

rpido.

Fuentes de alimentacin y niveles lgicos

Los circuitos ECL generalmente operan con fuentes de alimentacin

negativas en contraste con otras familias lgicas en el que extremo negativo

de la alimentacin est conectado a tierra. Esto se hace principalmente para

reducir al mnimo la influencia de las variaciones de la fuente de potencia en

los niveles lgicos ECL como es ms sensible al ruido en el VCC y

relativamente inmune al ruido en la EEV. Debido a tierra debe ser la tensin

ms estable en un sistema, ECL se especifica con un terreno positivo. En

esta conexin, cuando la tensin de alimentacin vara, la tensin cae a

travs de las resistencias de colector cambian ligeramente. Como las

resistencias de colector estn firmemente "atados" a la tierra, la salida de

voltajes de "mover" un poco. Si el extremo negativo de la fuente de

alimentacin se ha conectado a tierra, las resistencias de colector se fija al

carril positivo. Como las gotas de voltaje constante a travs de las

resistencias de colector cambian ligeramente, las tensiones de salida siguen

las variaciones de tensin de alimentacin y las dos partes del circuito actan

como constantes desplazadores de nivel actuales. En este caso, el divisor de

tensin R1-R2 compensa las variaciones de tensin en cierta medida. La

fuente de alimentacin positiva tiene otra desventaja - los voltajes de salida

pueden variar ligeramente en un contexto de alta tensin constante. Otra

razn para utilizar una fuente de alimentacin negativa es la proteccin de

los transistores de salida de un cortocircuito accidental entre la produccin y

el desarrollo de suelo.

El valor de la tensin de alimentacin se elige de modo que una

corriente suficiente para fluir a travs de los compensadores diodos D1 y D2

y la cada de voltaje a travs de la resistencia de emisor RE comn para ser

adecuada.

Circuitos ECL disponibles en el mercado abierto generalmente se

operan con niveles lgicos incompatibles con otras familias. Esto significaba

que la interoperacin entre familias lgicas ECL y otras, tales como la familia

TTL populares, circuitos de interfaz adicionales requeridos. El hecho de que

los niveles altos y bajos de lgica son relativamente cerca significaba que

ECL sufre de pequeos mrgenes de ruido, que puede ser problemtico.

Fundamento del ECL

El funcionamiento de los circuitos ECL se basa en el mismo del

amplificador diferencial. Los transistores no se saturan, la operacin normal

es en zona activa, lo que constituye una de las razones que hace que estos

circuitos sean los mas veloces de los circuitos integrados digitales.

La configuracin de una ECL

Est basada en el amplificador diferencial, denominado as porque su

salida es proporcional a la diferencia entre dos tensiones de entrada V1 y V2.

Este circuito se utiliza principalmente en sistemas analgicos, pero tambin

tiene propiedades digitales, llegando a ser la base de construccin de la

lgica de emisor acoplado o ECL (en algunos casos nos la podemos

encontrar como lgica de modo corriente o CML), como lo muestra el circuito.

Al aumentar el nmero de entradas, es necesario poner dos

seguidores de emisor para igualar niveles de tensin de entrada y salida.

Si V1 es igual que V2 se tendr que, por simetra del circuito, las

corrientes de los transistores son iguales. Sin embargo, si V1 sobrepasa a V2

en aproximadamente 0,1 voltio, el transistor T1 estar en conduccin y T2 en

corte; e inversamente, si V1 es menor que V2 en 0,1 voltio, entonces T2

conducir y T1 estar en corte.

La corriente de emisor se mantiene prcticamente constante, y se

transfiere o conmuta del transistor T1 al T2 cuando la tensin V1 vara desde

0,1 V, por encima de la tensin de referencia V2, hasta 0,1 voltios por debajo

de esta tensin. Excepto dentro de un margen muy estrecho de variacin de

la tensin de entrada V1, a la salida S slo puede tener uno de dos posibles

valores y, por tanto, acta como circuito digital.

Los dos niveles lgicos pueden deducirse fcilmente. Si T2 est en

corte, la tensin de salida ser igual a la de alimentacin y se estar a nivel

lgico 1. Cuando T2 est en conduccin, los valores de las resistencias

calculados previamente harn que el transistor se encuentre en su zona

activa, es decir, T2 estar en su regin activa cuando la unin colector-base

est polarizada inversamente. Entonces, la tensin de salida ser la de

alimentacin menos la cada de tensin en la resistencia de colector,

obteniendo de esta manera el estado lgico 0.

Puesto que en el amplificador diferencial ningn transistor est

dispuesto a llegar a saturacin, se elimina el tiempo de almacenamiento y,

por tanto, la lgica ECL se convierte en la ms rpida de las familias lgicas.

Podemos conseguir retardos de propagacin inferiores a 0,5 nanosegundos

por puerta.

Ventajas

Son los circuitos ms veloces y pueden alcanzar tiempos de demora

de hasta 1ns.

El menor retardo de propagacin

Buena flexibilidad lgica

No existen picos de corrientes en los transistores como sucede en la

familia lgica TTL.

Se dispone de salidas complementadas, lo que le brinda mayor

versatilidad.

El nivel de 1 lgica es prcticamente independiente del factor de carga.

Salidas complementarias

Baja impedancia de salida

Buena inmunidad al ruido

Desventajas

Pequeos valores de los mrgenes de ruidos.

Altos valores de potencia del orden de 40 mW.

No son compatibles con los circuitos TTL.

Ocupan gran rea en los circuitos integrados

Alta disipacin (40 mW)

Necesita circuito de adaptacin con otras familias

Conclusiones

La lgica de emisor acoplado esta basada en un amplificador

diferencial denominado as porque su salida es proporcional a la diferencia

entre dos tensiones de entrada V1 y V2. Utiliza un amplificador diferencial

BJT saturado con la entrada de una sola terminal y la corriente para evitar la

zona saturada de la operacin y su comportamiento de apagado lento emisor

limitado .Este circuito se utiliza principalmente en sistemas analgicos, pero

tambin tiene propiedades digitales sin embargo se debe aumentar el

nmero de entradas ya que es necesario poner dos seguidores de emisor

para igualar niveles de tensin de entrada y salida.

La lgica de emisor acoplado (ECL) pertenece a la familia de circuitos

MSI implementada con tecnologa bipolar esta es la ms rpida disponible

dentro de los circuitos de tipo.

Este circuito tiene muchas ventajas una de ellas es buena flexibilidad

logica posee buena inmunidad al ruido baja impedancia de salida .Al igual

que otros circuitos tiene desventajas ya que necesita un circuito de

adaptacion otro problema que se presenta es que cada puerta dibuja

continua actual, lo que significa que requiere mucha ms energa que los de

otras familias lgicas.

Los diseos de ECL han sido tan importantes y funcionales que se

han implementado hasta con tubos de vaco, y por supuesto con transistores

discretos. En la actualidad puede parecer que 8 ns es mucho cuando hay

circuitos CMOS que con un consumo muy bajo sobre todo esttico superan

con creces esta prestacin, pero en realidad la tecnologa ECL tambin ha

evolucionado tanto en diseo como en fabricacin, y en la actualidad se

consiguen retardos netamente inferiores al nanosegundo, con un consumo

alto pero no desorbitado.

S-ar putea să vă placă și

- Transistor UjtDocument12 paginiTransistor UjtMaria CalleÎncă nu există evaluări

- Montaje y mantenimiento de transformadores. ELEE0109De la EverandMontaje y mantenimiento de transformadores. ELEE0109Încă nu există evaluări

- Fuente Alimentación Simétrica Regulable 15vDocument18 paginiFuente Alimentación Simétrica Regulable 15vHernandez Adan0% (1)

- Probadores de transistores MOSFET y bipolares enDocument10 paginiProbadores de transistores MOSFET y bipolares enTONY ESPIRITU100% (1)

- Inversor de Corriente PDFDocument11 paginiInversor de Corriente PDFXavier PalaciosÎncă nu există evaluări

- Inverter 1Document63 paginiInverter 1Manuel GomezÎncă nu există evaluări

- Circuitos Schmitt TriggerDocument10 paginiCircuitos Schmitt TriggerAfir MinayaÎncă nu există evaluări

- Laboratorio #1 Oscilador ColpittsDocument6 paginiLaboratorio #1 Oscilador ColpittsBrandon Cruz0% (1)

- Arq Del Cpu 23-01Document5 paginiArq Del Cpu 23-01Iván Jesús Jiménez DíazÎncă nu există evaluări

- L8 - Puente HDocument11 paginiL8 - Puente HSergioarturo MorenochucoÎncă nu există evaluări

- Familias lógicas TTL y CMOS: características y diferenciasDocument18 paginiFamilias lógicas TTL y CMOS: características y diferenciasWALTER CHOQUE COPARIÎncă nu există evaluări

- Informe 3Document14 paginiInforme 3Wilber HuillcaÎncă nu există evaluări

- Implementacion CicloconvertidoresDocument29 paginiImplementacion Cicloconvertidorespablo gÎncă nu există evaluări

- Encendido TransistorizadoDocument6 paginiEncendido TransistorizadoRoberth Murillo GomezÎncă nu există evaluări

- Familia LógicasDocument5 paginiFamilia LógicasCarlos OrtegaÎncă nu există evaluări

- Elementos de Potencia - Ochoa - Munguia - José - ÁngelDocument8 paginiElementos de Potencia - Ochoa - Munguia - José - ÁngelJOSE ANGEL OCHOA MUNGUIAÎncă nu există evaluări

- Compuertas Y Familias LógicasDocument5 paginiCompuertas Y Familias LógicasLuis OliverosÎncă nu există evaluări

- Unidad 1Document32 paginiUnidad 1lolo lolaÎncă nu există evaluări

- Electricidad 02Document16 paginiElectricidad 02YERALDINE ARACELY MARQUEZ CARRASCOÎncă nu există evaluări

- Practicas 1-12 Diseño Con Transistores - 23Document30 paginiPracticas 1-12 Diseño Con Transistores - 23MarcoÎncă nu există evaluări

- Implementación osciladores y multivibradores con componentes discretosDocument11 paginiImplementación osciladores y multivibradores con componentes discretosttavvo50% (2)

- Informe 7Document28 paginiInforme 7Jean Carlos DiazÎncă nu există evaluări

- Trabajo 2Document8 paginiTrabajo 2Romny PeraltaÎncă nu există evaluări

- Tarea 1 U2 E.A.Document13 paginiTarea 1 U2 E.A.Andrea MuñizÎncă nu există evaluări

- Resolucion Electronica y TelecomunicacionesDocument15 paginiResolucion Electronica y Telecomunicacionesenrique cubaÎncă nu există evaluări

- Rodriguez Moreno Trabajo TransistoresDocument10 paginiRodriguez Moreno Trabajo Transistoressipper22Încă nu există evaluări

- 10-Practica Familia Logicas Ttl-CmosDocument10 pagini10-Practica Familia Logicas Ttl-CmosGerber VargasÎncă nu există evaluări

- Ma 29000 Ea-Ie-300 27Document7 paginiMa 29000 Ea-Ie-300 27carlos orregoÎncă nu există evaluări

- Informe MosfetDocument12 paginiInforme Mosfetmayra alejandta villamil barbosaÎncă nu există evaluări

- Fuentes ConmutadasDocument6 paginiFuentes Conmutadasjaver9006Încă nu există evaluări

- Introduccion A Las Fuentes ConmutadasDocument9 paginiIntroduccion A Las Fuentes ConmutadasJuan Jimenez Gomez100% (1)

- Sistema DigitalesDocument14 paginiSistema Digitalesmc ivan bÎncă nu există evaluări

- Aplicacion de Transitores 2222222Document12 paginiAplicacion de Transitores 2222222Dark Angel26Încă nu există evaluări

- Transistores y SCRDocument19 paginiTransistores y SCRKarina Chacón ArciniegaÎncă nu există evaluări

- Aislamiento óptico y magnético en control de potenciaDocument6 paginiAislamiento óptico y magnético en control de potenciaCristian Alejandro Agüero MoránÎncă nu există evaluări

- Transistor Bipolar y Transistor de Efecto de CampoDocument33 paginiTransistor Bipolar y Transistor de Efecto de CampoFERNANDO JOSUE UREÑA NAVARROÎncă nu există evaluări

- Caracteristicas de Un TransistorDocument10 paginiCaracteristicas de Un TransistorTazann24Încă nu există evaluări

- Amplificadores diferenciales BJT pequeña señalDocument4 paginiAmplificadores diferenciales BJT pequeña señalRoberto OwenÎncă nu există evaluări

- Trabajo Fuentes ConmutadasDocument20 paginiTrabajo Fuentes ConmutadasJesus Palacios100% (1)

- Circuito NPN 2 transistores caídas tensiónDocument2 paginiCircuito NPN 2 transistores caídas tensiónmiguel cruzate alzamoraÎncă nu există evaluări

- Transistor BJTDocument35 paginiTransistor BJTFrancisco HernandezÎncă nu există evaluări

- Temporizador 1Document4 paginiTemporizador 1Oliver RomeroÎncă nu există evaluări

- Transistor Como Un InterruptorDocument7 paginiTransistor Como Un InterruptorJose MartinezÎncă nu există evaluări

- ANITADocument8 paginiANITAMARIA CRISTINA RODRIGUEZ DIAZÎncă nu există evaluări

- Transistor BipolarDocument5 paginiTransistor BipolarFroylanBelaunzaranÎncă nu există evaluări

- Lab 4 Fisica ElectricaDocument8 paginiLab 4 Fisica ElectricaCapital Chill TVÎncă nu există evaluări

- Proyectos ElectronicosDocument13 paginiProyectos ElectronicosSonia CarrazcoÎncă nu există evaluări

- Transistores 123Document5 paginiTransistores 123andresinho1993Încă nu există evaluări

- Conexión DarlingtonDocument12 paginiConexión Darlingtonpedrolyg905Încă nu există evaluări

- L7 - Transistor BJTDocument12 paginiL7 - Transistor BJTJorge Luis Espinoza AcunaÎncă nu există evaluări

- Practicas TransistoresDocument14 paginiPracticas TransistoresCameron RiosÎncă nu există evaluări

- UJT Transistor Uniunión: Símbolo Del UJTDocument4 paginiUJT Transistor Uniunión: Símbolo Del UJTMarcial Hernández SimónÎncă nu există evaluări

- Informe Del Oscilador ColpittsDocument4 paginiInforme Del Oscilador ColpittsJefferson RoseroÎncă nu există evaluări

- Transistores bipolares y de efecto campoDocument33 paginiTransistores bipolares y de efecto campoFERNANDO JOSUE UREÑA NAVARROÎncă nu există evaluări

- Amplificador de Audio Con 3 EtapasDocument22 paginiAmplificador de Audio Con 3 EtapasFranklin Callalli AcostaÎncă nu există evaluări

- Ecl (Emmiter-Coupled Logic)Document15 paginiEcl (Emmiter-Coupled Logic)programas peyÎncă nu există evaluări

- Resumen - Funcionamiento de Los Circuitos Electrónicos - Rivera MTZ Diana JocelynDocument18 paginiResumen - Funcionamiento de Los Circuitos Electrónicos - Rivera MTZ Diana JocelynDiana J. Rivera MartínezÎncă nu există evaluări

- 5.1-Cto. de Disparo Con AislamientoDocument37 pagini5.1-Cto. de Disparo Con AislamientoAislinn Valeria MartínezÎncă nu există evaluări

- Laboratorio 1 - Telecomunicaciones IDocument11 paginiLaboratorio 1 - Telecomunicaciones IAbraham Mendoza0% (1)

- Ejercicios CE BRHDocument43 paginiEjercicios CE BRHMARTÍNEZ BAUTISTA VICTOR EDUARDOÎncă nu există evaluări

- Trabajo-03-Compuertas XorDocument4 paginiTrabajo-03-Compuertas XorAaronBautistaCastañedaÎncă nu există evaluări

- Actividad 1Document4 paginiActividad 1Jhon edinson BautistaÎncă nu există evaluări

- Teoremas de Thevenin y NortonDocument14 paginiTeoremas de Thevenin y NortonAngel MejiaÎncă nu există evaluări

- Lógica Secuencial con PLDDocument17 paginiLógica Secuencial con PLDAlex RMÎncă nu există evaluări

- Clase Iv Compuertas LogicasDocument19 paginiClase Iv Compuertas LogicasAaron LopezÎncă nu există evaluări

- Teoremas de Thevenin y Norton en circuitos electrónicosDocument11 paginiTeoremas de Thevenin y Norton en circuitos electrónicosbigorosiano100% (1)

- El Amplificador Diferencial LaboratorioDocument9 paginiEl Amplificador Diferencial LaboratorioMarcelo SandovalÎncă nu există evaluări

- Tecnología CMOSDocument6 paginiTecnología CMOSapi-3762100100% (2)

- Compuertas Lógicas Con Transistores - Sincronización y MultiplexajeDocument9 paginiCompuertas Lógicas Con Transistores - Sincronización y MultiplexajeCarlos AularÎncă nu există evaluări

- Experimento 12Document3 paginiExperimento 12William MarínÎncă nu există evaluări

- Sistemas Computacionales Sesion02 v1Document30 paginiSistemas Computacionales Sesion02 v1Oscar Canchari OrunaÎncă nu există evaluări

- Filtro Pasa Banda (Banda Ancha)Document15 paginiFiltro Pasa Banda (Banda Ancha)oscar ulises lopez camarillo100% (1)

- Evaluación de Salida S5 - Circuitos Electrónicos Integrados - C5 3ero A-A - C5 3ero B-A-ADocument4 paginiEvaluación de Salida S5 - Circuitos Electrónicos Integrados - C5 3ero A-A - C5 3ero B-A-ARene Paul Oliva TurpoÎncă nu există evaluări

- Laboratorio Electrónica Digital UNSADocument9 paginiLaboratorio Electrónica Digital UNSAMarco Calizaya MartinezÎncă nu există evaluări

- PREVIO #1 Digitales SamirDocument9 paginiPREVIO #1 Digitales SamirBenny Samir Bautista EscobarÎncă nu există evaluări

- Amplificadore de Potencia-P.PDocument30 paginiAmplificadore de Potencia-P.PJorge ParraÎncă nu există evaluări

- Práctico 8 - Electrónica FundamentalDocument5 paginiPráctico 8 - Electrónica FundamentalGastón MassaferroÎncă nu există evaluări

- Circuitos DigitalesDocument17 paginiCircuitos DigitalesJuanÎncă nu există evaluări

- Bloques Funcionales IntegradosDocument4 paginiBloques Funcionales Integradosjuanprans16Încă nu există evaluări

- Guia Practica #2Document12 paginiGuia Practica #2JOAN BRANCO QUISPE BREÑAÎncă nu există evaluări

- Laboratorio 2 Electronicos IIDocument14 paginiLaboratorio 2 Electronicos IIJuan Arnao AlarconÎncă nu există evaluări

- Ejercicio de Diagramas de BloquesDocument5 paginiEjercicio de Diagramas de BloquesdeivisÎncă nu există evaluări

- Amplificadores Clase B Clase C Clase AB PDFDocument4 paginiAmplificadores Clase B Clase C Clase AB PDFDiegoÎncă nu există evaluări

- Cmos Por TTL y TTL Por CmosDocument16 paginiCmos Por TTL y TTL Por CmosNabia Stefania Sepulveda Bravo0% (1)

- 4796 Angos Naranjo Guano Morales Informe Clase B AbDocument8 pagini4796 Angos Naranjo Guano Morales Informe Clase B AbANDRES WLADIMIR NARANJO PEREZÎncă nu există evaluări

- td2 TareaDocument11 paginitd2 Tareapatrick santibañezÎncă nu există evaluări

- Problemas para El Examen Final Ee513 Tele I 08-12-15Document3 paginiProblemas para El Examen Final Ee513 Tele I 08-12-15eric lop vegÎncă nu există evaluări