Documente Academic

Documente Profesional

Documente Cultură

Arreglo de Microfonos

Încărcat de

juankmalagonDescriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Arreglo de Microfonos

Încărcat de

juankmalagonDrepturi de autor:

Formate disponibile

69

CAPTULO 4

DISEO DEL SISTEMA

Para el diseo del sistema existen varios parmetros que se tienen que tomar en

cuenta, como el nmero de canales disponibles, frecuencia de la seal de prueba y

frecuencia de muestreo del sistema. Algunos parmetros tendrn mayor peso que otros por

lo que influirn en mayor medida en el funcionamiento del sistema.

Se realiz el diseo del sistema considerando la naturaleza de la seal, las

caractersticas del hardware disponible as como la teora. ste se puede dividir en dos

partes, hardware y software, que a su vez tendrn subdivisiones. El hardware comprende el

circuito acondicionador de seal para conectar los micrfonos con la tarjeta DSP, el arreglo

de micrfonos y el DSP. El software es el programa con todas las instrucciones que

ejecutar el DSP, que se puede dividir en configuracin del DSP y sus perifricos, captura

de datos, y el proceso del formador de haz.

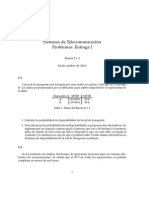

El diseo general del sistema se ilustra en la Figura 4.1, que se divide en tres partes,

arreglo de micrfonos, el circuito acondicionador de seal y la tarjeta de desarrollo DSK

TMS320F2812. A continuacin se explicar cada parte del sistema en forma separada.

Figura 4.1 Diagrama del sistema en forma general.

A

r

r

e

g

l

o

d

e

m

i

c

r

f

o

n

o

s

A

D

C

Circuito

acondicionador

de seal

Tarjeta de

desarrollo

DSK

TMS320F2812

SISTEMA

70

4.1 ARREGLO DE MICRFONOS

Consiste en un conjunto de micrfonos ubicados en forma lineal y separados una

distancia d. A continuacin se mencionan los criterios tomados en cuenta en el diseo del

arreglo, el tipo de micrfono a utilizar, la distancia de separacin entre micrfonos, etc.

4.1.1 Micrfono Electret em-926

Se eligi este micrfono por varias razones las cuales son:

- Bajo costo. Existen en el mercado otros tipos de micrfonos con caractersticas

superiores pero sus altos costos son una limitante a diferencia del micrfono electret

- Directividad omnidireccional. Como se plante en el Captulo 3, los sensores del

arreglo deben ser omnidireccionales, el micrfono electret tiene esta propiedad.

- Baja potencia. Ya que el arreglo requiere de diecisis micrfonos, estos micrfonos

consumirn una cierta potencia, es por ello que dado el nmero de micrfonos la

potencia requerida sea mnima, el micrfono electret requiere voltajes pequeos de

polarizacin y una baja corriente para su funcionamiento.

- El intervalo de frecuencia til es de 20 Hz a 16 kHz.

- Las dimensiones del micrfono son lo suficientemente reducidas en comparacin de

otros micrfonos, con un dimetro de 9.7 mm y 5.2 mm de espesor

4.1.2 Diseo del arreglo lineal de micrfonos

El diseo del arreglo lineal de micrfonos consiste en decidir el nmero de

elementos que conforman el arreglo, as como la distancia entre los mismos. Como se

observ en el Captulo 4, entre mayor sea el nmero de micrfonos mayor ser la

directividad del arreglo, dado que conviene que el mximo nmero de elementos que se

pueden emplear es el nmero de canales del convertidor ADC del DSP los cuales son

diecisis.

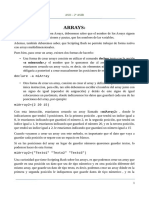

Ahora bien, en la teora los elementos se consideran como elementos puntuales pero

en la realidad estos elementos tienen dimensiones. En la Figura 4.2 se muestran las

dimensiones del micrfono electret em-926.

Figura 4.2 Dimensiones micrfono electret em-926.

La distancia entre elementos se medir a partir del centro de la cara circular de los

micrfonos.

9

.

7

m

m

2

.

5

m

m

5.2 mm 7 mm

2 mm

71

Por limitaciones que se vern ms adelante, el sistema se ha especificado para que

funcione como un arreglo de banda angosta, es decir, que el sistema funcione para un ancho

de banda reducido, alrededor de la frecuencia de 17 kHz; la frecuencia de 17 kHz se

seleccion para de modo que al hacer las pruebas se presente una menor molestia, que

puedan afectar a las personas que se encuentran expuestas a la seal de prueba.

Otro aspecto que se tom en cuenta es la consideracin de campo lejano y campo

cercano que se mencion en el Captulo 3, como la distancia a la cual debe estar la fuente

de sonido del arreglo a la cual se considera lo suficientemente, alejado para que el frente de

onda sea una onda plana dada por la desigualdad

2

total s

d F

r

c

< . Como ejemplo, si la

frecuencia de muestreo es 44.1 kHz, dado que la velocidad del sonido es aproximadamente

de 340 m/s y para un arreglo de 16 micrfonos con distancia entre elementos de 2 cm, y la

longitud total del arreglo es de 30 cm. Sustituyendo valores, la distancia a la cual se

considera campo cercano son distancias menores a 11.67 m; en cambio, si la distancia entre

elementos es de 1 cm, la distancia total del arreglo es 15 cm, entonces la distancia r es

2.91 m, que fue la distancia mnima a la cual se considera campo lejano; distancias menores

implican que se considera campo cercano.

De este ejemplo se observa que entre mayor sea la distancia entre elementos del

arreglo, mayor es la distancia a la cual debe estar alejada la fuente de sonido. Para el

arreglo de 15 cm. se requiere una distancia mnima de 2.91 m, en cambio, el arreglo de 30

cm requiere de 11.67 m. Esto trae el problema que entre mayor sea la distancia entre

elementos se requerir de mayor potencia del sonido, as como las dimensiones de la

habitacin en donde se realizan las pruebas sea mayor de los 11.67 m. Ya que lo anterior no

es posible, se eligi el primer arreglo ya que la distancia requerida fue aceptable para las

dimensiones de la habitacin donde se realizaron las pruebas.

4.2 CIRCUITO ACONDICIONADOR DE SEAL

Como el voltaje de la seal de salida de los micrfonos es del orden de milivolts,

este no es lo suficiente para ser detectado por el convertidor analgico digital, adems el

convertidor analgico digital realiza la conversin de seales en el intervalo de 0 a 3 V. Por

ello es necesario acondicionar la seal de salida de los micrfonos, lo cual implica

amplificar la seal, sumar un voltaje de offset a la seal as como asegurar que el voltaje de

salida se encuentre en dicho intervalo, adems que la seal de entrada est limitada en

banda.

Como parmetros de diseo se fijaron el ancho de banda del circuito, la ganancia,

voltajes de operacin y voltajes a los cuales se limita la seal de salida. El ancho de banda

del circuito sobre el que se hizo el diseo fue un intervalo de frecuencia de 20 Hz a 20

kHz, la ganancia de voltaje del circuito debe ser lo bastante alta para que la seal de prueba

sea captada y la seal de salida es necesario que est limitada al intervalo de voltajes de 0 a

3 V. Se eligi el amplificador operacional TL074 debido a su ancho de banda de ganancia

unitaria BW de 4 MHz mayor al del LM741, parmetro que limita la ganancia y ancho de

banda del circuito, adems de ser diseado como una versin de bajo ruido del TL084.

72

De la Figura 4.3 (a) se observa que el amplificador opera como un sumador inversor

con dos seales una que proviene del micrfono y la otra es un voltaje que se aade para

obtener el voltaje de offset, que se obtiene del amplificador operacional conectado como

fuente de voltaje; se observa que el voltaje de offset es ajustado mediante la resistencia

variable R

V

.

La ganancia del amplificador depende de las resistencias R

1

y R

2

y si el circuito se

aproxima a un amplificador inversor la ganancia de voltaje A

V

es igual a la ecuacin (4.1).

Tal y como se observa en la Figura 4.3 (b). Los valores de R1 y R2 fueron elegidos

a) Circuito acondicionador de seal

b) Circuito amplificador inversor formado por R

1

y R

2

Figura 4.3 Circuito acondicionador de seal.

2

1

V

R

A

R

~

(4.1)

V

V

V

-V

V

V

V

V

R

r

R

V

C

1

R

1

R

2

d

R

R

TL074

TL074

micrfono

TL074

R

2

R

1

R

C

2

73

Los valores de R

1

y R

2

se muestran a continuacin con lo que obtenemos la

ganancia del circuito

Para limitar en banda la seal, se necesita un filtro paso banda el cual se forma con

un filtro pasa altas y un filtro pasa bajas. Estos filtros se componen de la malla C

1

y R

1

,

conectados en serie forman un filtro pasa altas, y el filtro pasa bajas lo forman C

2

y R

2

conectados en paralelo y que se encuentran en la malla de retroalimentacin del

amplificador sumador inversor; entonces las frecuencias de corte del filtro pasa bajas son

aproximadamente [9]:

Calculando el valor de los capacitores

La respuesta en frecuencia real del filtro se muestra en la Figura 4.4, se observa que

el circuito tiene una ganancia de voltaje real de 100, equivalente a 40 dB en la banda de

paso. Las frecuencias de corte son de 12 Hz para la frecuencia de corte para bajas

frecuencias y 23 kHz para altas frecuencias, aproximadamente.

Los valores de R

1

y R

2

fueron elegidos debido a que con ellos fue posible obtener

una ganancia real lo bastante alta y que cumpliera con la respuesta en frecuencia del

circuito, adems la ganancia real se ve afectada por tres factores dos que ya han sido

mencionados, las resistencias externas, ancho de banda de ganancia unitaria, pero adems

los capacitores con los que se forman los filtros pasa bajas y pasa altas. Es por ello que el

desarrollo mostrado es una aproximacin al circuito real [9].

1

3.9 R k = O y

2

680 R k = O

680

174.4

3.9

V

k

A

k

O

= =

O

(4.2)

1 1

1

2

L

f

RC t

~

(4.3)

2 2

1

2

H

f

R C t

~

(4.4)

1

1

1

2

L

C

R f t

~

( ) ( )

1

1

2 3.9 20

C

k Hz t

=

O

1

2.04 C F = con valor comercial

1

2.2 C F =

( )( )

2

1

2 680 20

C

k kHz t

=

O

2

10.7 C pF = con valor comercial

2

10 C pF =

74

Figura 4.4 Respuesta en frecuencia de circuito pasa banda.

Finalmente a la salida del amplificador operacional se encuentra un diodo

rectificador, que se encarga de rectificar la seal, los voltajes negativos son truncados y se

saturan a 0 V. El circuito acondicionador de seal se conecta a la interfaz analgica de la

tarjeta de desarrollo.

4.3 TARJETA DE DESARROLLO DSK DSP TMS320F2812

El DSP F2812 ejecuta 150 millones de instrucciones por segundo (Mips), lo cual

permite al usuario realizar aplicaciones en tiempo real. Tiene internamente los siguientes

perifricos [28]:

- Dos administradores de eventos (A y B) EVA EVB

- Generador de seal PWM

- 3 temporizadores de 32 bits

- Convertidor analgico digital ADC, 12 bits, 16 canales, con frecuencia mxima de

conversin de 20 MHz

- Interfaz controlador de red CAN

- Interfaz de comunicacin serial A y B (asncrona) SCIA, SCIB

- Puerto serial SPI

- Terminal de propsito general bidireccional digital I/O GPIO

- Temporizador watchdog (temporizador que reinicia el DSP)

- Joint Test Action Group (JTAG)

- Modulo lazo de fase encadenada (del ingls Phase-Locked Loop, PLL)

4.4 PROCESO DE DETECCIN DIRECCIN DE ARRIBO (DOA)

El proceso se realiza con los datos obtenidos del arreglo de micrfonos, el cual

realizar el DSP TMS320F2812 y que se representa en la Figura 4.5. Para entender como

realiza el DSP el proceso, se explicar cada parte del proceso en el orden secuencial que

sugiere la figura. El proceso comienza con la obtencin de datos del arreglo lo cual se hace

Frecuencia [Hz]

G

a

n

a

n

c

i

a

[

d

B

]

3 dB

16 kHz

38.69 dB

18 kHz

38.38 dB

75

mediante el perifrico ADC, el cual almacena los datos en un buffer de 16 elementos; ms

adelante se explica este proceso. El proceso representado en la Figura 4.5 est dividido en

los siguientes bloques, buffer de datos de entrada obtenidos del arreglo, muestras o retrasos

del arreglo, formador de haz fijo con ventana, un filtro pasa banda a la salida del formador

de haz fijo, algoritmo GSC que a su vez est compuesto por una matriz de bloqueo B y un

algoritmo adaptable LMS, y por ltimo el proceso de deteccin de direccin de arribo

DOA.

4.4.1 Tiempo de muestreo

El tiempo de muestreo del sistema se controla mediante el contador temporizador

CPU-Timer0 y el perifrico PIE el cual controla la interrupcin asociada al temporizador.

El contador CPU-TIMER0 consiste de dos registros de 32 bits, el registro contador formado

por los dos registros de 16 bits TIMH y TIM, y por el registro que controla el periodo del

contador que tambin est formado por dos registros de 16 bits PRDH y PRD.

El contador temporizador se configura de manera que opere a la misma frecuencia

que opera el DSP, se carga un valor en el registro que controla el periodo PRDH:PRD y se

iguala al registro contador TIMH:TIM, despus se activa el funcionamiento del contador, el

registro TIMH:TIM decrementa su valor con cada ciclo de reloj hasta llegar a cero, cuando

llega a cero el valor de PRDH:PRD nuevamente es cargado en TIMH:TIM, con lo que se

reinicia el proceso de decrementar TIMH:TIM y adems se emite la peticin de

interrupcin de TIMER0, esto se realiza de forma continua con lo cual se genera un ciclo

de reloj cuyo perodo es el perodo de muestreo del convertidor analgico digital ADC.

Adicionalmente, se habilita una interrupcin TINT0 que cuando el contador

TIMH:TIM llega a cero se enva una seal al perifrico PIE para ejecutar la interrupcin

aociada a TINT0. La siguiente instruccin asocia la interrupcin TINT0 con la rutina

Timer0_interrup.

PieVectTable.TINT0=&Timer0_interrup;

El sistema se dise considerando que la frecuencia de muestreo es de 44.1 kHz,

con el DSP funcionando a una frecuencia de 150 MHz, con lo cual se calcula el valor del

registro PRDH:PRD. Entonces se calcula el valor del registro para tener la frecuencia de

muestreo deseada de la siguiente forma:

Sustituyendo valores se tiene

:

Frecuencia de operacin del sistema

PRDH PRD

Frecuencia deseada

= (4.5)

150

:

44.1

MHz

PRDH PRD

kHz

=

76

Figura 4.5 Diagrama general del proceso de deteccin de direccin de arribo.

R

e

t

r

a

s

o

s

d

e

l

a

s

s

e

a

l

e

s

d

e

e

n

t

r

a

d

a

F

o

r

m

a

d

o

r

d

e

h

a

z

f

i

j

o

M

u

e

s

t

r

a

s

s

e

l

e

c

c

i

o

n

a

d

a

s

p

o

r

e

l

v

e

c

t

o

r

d

e

d

i

r

e

c

c

i

o

n

a

m

i

e

n

t

o

F

i

l

t

r

o

p

a

s

a

b

a

n

d

a

M

a

t

r

i

z

d

e

b

l

o

q

u

e

o

B

S

e

a

l

e

s

d

e

e

n

t

r

a

d

a

p

r

o

v

e

n

i

e

n

t

e

s

d

e

l

a

r

r

e

g

l

o

V

e

c

t

o

r

d

e

d

i

r

e

c

c

i

o

n

a

m

i

e

n

t

o

A

l

g

o

r

i

t

m

o

a

d

a

p

t

a

b

l

e

L

M

S

C

l

c

u

l

o

d

e

p

o

t

e

n

c

i

a

P

o

t

e

n

c

i

a

e

n

u

n

a

d

i

r

e

c

c

i

n

D

i

r

e

c

c

i

n

u

77

Que se redondean a 3401, PRDH:PRD = 3401.

4.4.2 Conversin analgica digital

Cuando el DSP recibe la seal de interrupcin del perifrico PIE relacionada al

perifrico contador temporizador cero (Timer0), ste atiende la interrupcin, la cual

consiste de las instrucciones de acuerdo al diagrama de flujo de la Figura 4.6.

Figura 4.6 Diagrama de flujo, interrupcin TIMER0.

Cdigo en lenguaje C de la rutina de la interrupcin de Timer0.

interrupt void Timer0_interrup(void){

AdcRegs.ADCTRL2.bit.SOC_SEQ1=0x1;

PieCtrlRegs.PIEACK.bit.ACK1=0x1;

return;

}

La instruccin AdcRegs.ADCTRL2.bit.SOC_SEQ1=0x1; enva al convertidor

ADC la seal de inicio de conversin (del ingls Start Of Convertion, SOC), con lo que

inicia la conversin de los 16 canales. Y la segunda instruccin

PieCtrlRegs.PIEACK.bit.ACK1=0x1; borra la bandera que indica que est pendiente la

interrupcin por temporizador, para que una vez terminada la interrupcin no vuelva a

ejecutarse hasta que la bandera sea habilitada por otro proceso, de lo contrario la

interrupcin se reconocera como que an est pendiente. Y por ltimo, con la instruccin

return se terminan las instrucciones de la interrupcin temporizador y se retorna al

programa principal (ciclo while infinito).

: 3401.36 PRDH PRD =

Interrupcin

Timer0

Envo de la seal SOC al

perifrico ADC

Se deshabilita la bandera

interrupcin Timer0 del

registro PIEACK

return

78

El proceso de conversin no es parte de la interrupcin, ya que se realiza de forma

paralela a las instrucciones que realiza el DSP. Con la seal inicio de conversin (SOC) el

convertidor inicia la conversin de los 16 canales de forma secuencial, el tiempo que existe

entre la conversin de un canal y otro es de aproximadamente 26 ns , los datos se guardan

en el buffer ADCRESULT que est formado por 16 localidades ubicadas en la memoria

dato como se muestra en la Figura 4.7, de la localidad 0x7108 a la 0x7117 [26].

Figura 4.7 Captura y almacenamiento de datos con el perifrico ADC.

La conversin comienza con el canal A1 y termina con el canal B8; el convertidor

ADC est configurado para que al terminar la conversin de los diecisis canales se enva

la seal fin de conversin (del ingls End Of Convertion, EOC), la cual a su vez habilita

una segunda interrupcin. La interrupcin ADC en la cul se realiza el resto del proceso se

muestra en la Figura 4.8.

Figura 4.8 Interrupcin ADC.

Seal SOC

Canal A1

Canal A8

Canal B1

Canal B8

Seal EOC

0x7108

0x7117

Buffer ADC RESULT 0-15

Interrupcin

ADC

Proceso

return

79

En la Figura 4.9 se muestra la secuencia de conversin de los 16 canales, con los

ciclos de reloj generados por el temporizador CPU-TIMER0 con un periodo de 22.6 s.

Cada que llega el temporizador a cero activa la interrupcin TIMER0, sta a su vez activa la

conversin ADC mediante la seal SOC y finaliza la interrupcin. Est interrupcin se

lleva a cabo en 50 ns, de forma paralela el convertidor ADC convierte los 16 canales. Cabe

mencionar que este proceso no es parte de la interrupcin TIMER0 y se lleva a cabo de

forma paralela en el perifrico ADC, la conversin se realiza en 40 ns aproximadamente. Al

finalizar la conversin de los 16 canales se activa una segunda interrupcin a partir de la

seal EOC, la interrupcin ADC en la cual se realiza el resto del proceso para lo cual se

dispone cerca de 22.60 s, lo que es equivalente a 3380 instrucciones del DSP. Como se

puede el proceso se efecta en 19 s, quedando 3.6 s disponibles entre el fin del proceso y

la siguiente interrupcin TIMER0.

Figura 4.9 Diagrama de tiempos.

4.4.3 Cancelador general de lbulos laterales GSC

El cancelador general de lbulos laterales, GSC, se implement con el objetivo de

obtener un haz con una mayor selectividad del que se puede obtener con un formador de

haz fijo, y de acuerdo con la teora est compuesto por el formador de haz fijo con el vector

de direccionamiento, una matriz de bloqueo B y un algoritmo adaptable, en este caso se

utiliz el algoritmo LMS como se muestra en la Figura 4.5.

4.4.4 Matriz de vectores de direccionamiento

La direccin del lbulo principal del patrn de radiacin del arreglo se cambia

mediante retrasos de las seales de los micrfonos. A modo de ejemplo se muestra un

arreglo que realiza un escaneo de -60 a 60 con respecto a la perpendicular del arreglo,

escaneo que tambin puede ser de -90 a 90 lo cual se ver en el Captulo 5; el escaneo de -

60 a 60 se realiza con incrementos de 5 por lo que son 25 vectores de direccin. Cada

80

vector de direccionamiento est activo por aproximadamente 45.35 ms, cumplido este

tiempo cambia al siguiente vector de direccionamiento, por lo que el sistema tarda en

realizar el escaneo de -60 a 60 1.1337 s. El clculo de cada vector de direccionamiento se

realiz con la ecuacin (4.6)

De la ecuacin (4.6), el resultado es un valor real, adicionalmente se aplica un

redondeo o truncamiento ya que es necesario que

i

o sea un valor entero. Donde d es la

distancia entre elementos, T es el periodo de muestreo,

0

u es la direccin deseada del haz,

x

u es la mitad del ancho del lbulo principal, v la velocidad del sonido, i representa el

nmero del sensor que va de 0 a 15, es decir, el primer micrfono se considera el micrfono

cero y el micrfono diecisis se considera el micrfono quince, y

i

o es el retraso

correspondiente al micrfono i. As formamos la matriz

0

i u

o

cuyos subndices indican la

direccin

0

u por el numer de sensor i, que se muestra en la figura 4.10.

Esta matriz representa los retrasos necesarios en cada uno de los micrfonos. En

este caso cada rengln de la matriz es el vector direccionamiento para una direccin en

especfico en un intervalo angular de -60 a 60, el primer rengln corresponde a -60, el

segundo rengln corresponde a -55 y as sucesivamente hasta llegar a los 60. Y cada

columna de la matriz corresponde a un micrfono del arreglo.

Figura 4.10 Matriz de vectores de direccionamiento.

La matriz de la Figura 4.10 es para el caso del intervalo angular de -60 a 60, para

un intervalo de -90 a 90 se deben agregar los vectores de direccionamiento de los

intervalos -90 a -60 y de 60 a 90.

Como se puede ver en el diagrama de la Figura 4.11, el vector de direccionamiento

selecciona los datos que son utilizados por el formador de haz y son representados como un

nuevo buffer de datos de entrada.

( ) ( )

0

cos sin

x

i

di

Tv

u u

o = (4.6)

81

Figura 4.11 Seleccin de las muestras que realiza el vector de direccionamiento.

En la Figura 4.11 se puede observar cmo estn seleccionados los elementos de las

muestras tomadas de cada uno de los sensores, y en este caso, para la direccin de 35.

a) Seleccin de muestras para la direccin de 35.

b) Seleccin de muestras para la direccin de 15.

Figura 4.12 Seleccin de muestras.

82

En la Figura 4.12 se observa como a partir de las muestras seleccionadas se forma

un segundo buffer de datos

( )

i

i n

x

o

que sirve de entrada al formador de haz.

4.4.5 Formador de haz fijo con estructura GSC

El formador de haz implementado se divide en dos partes, en un formador de haz

fijo y uno adaptable. El formador de haz fijo realiza el producto de los datos del buffer de

entrada, seleccionado por el vector de direccionamiento, por una ventana para despus

realizar la suma de los datos; el resultado es una seal nica, como se puede ver, y como ya

se ha mencionado anteriormente, la estructura del formador de haz es parecida a la de un

filtro FIR.

Figura 4.13 Formador de haz fijo con ventana de diecisis elementos.

4.4.6 Filtro pasa banda

A la salida del formador de haz se obtiene una seal la cual es necesario filtrar, para

minimizar posibles interferencias de bajas y altas frecuencias, se utiliza un filtro pasa

banda, del tipo FIR de diecisis muestras, con una frecuencia de corte inferior de 15 kHz y

con una frecuencia de corte superior de 18 kHz, de esta manera la frecuencia central se

encuentra aproximadamente en los 17 kHz; a est frecuencia es donde el patrn de

radiacin del arreglo es ms selectivo, por lo que es ms sencillo ubicar el lbulo principal

del patrn de radiacin. La frecuencia de corte inferior es necesaria ya que conforme es

menor la frecuencia de la seal que incide sobre el arreglo, el lbulo principal es ms ancho

y por tanto ms difcil de conocer su direccin. Cabe mencionar, que se eligi el tipo FIR

debido a su fase lineal la cual es necesaria al momento de utilizar la estructura GSC.

El filtro utilizado es un filtro FIR de diecisis elementos con una ventana

Chebyshev-Dolph.

83

Figura 4.14 Filtro FIR pasa banda despus del formador de haz fijo.

4.4.7 Matriz de bloqueo

Para formar la matriz de bloqueo se utiliz la estructura Griffits-Jim, que utiliza el

mismo buffer de entrada del formador de haz fijo; de la matriz de bloqueo se obtienen

quince valores de muestra, tal como se muestra en la Figura 4.15.

Figura 4.15 Matriz de bloqueo, diecisis entradas con quince salidas.

Como se observa en la figura 4.15 las salidas de la matriz de bloqueo son el vector

B

j

y es el resultado de la multiplicacin matricial entre el vector de entrada de datos por la

matriz de bloqueo B como se muestra en las ecuaciones (4.7), (4.6) y (4.9), como ya se

mencion para obtener la matriz B se utiliza la estructura Griffits-Jim y a continuacin se

muestra como se obtienen las salidas B

j

a partir del vector buffer de entrada de datos. Las

seales de salida de la matriz de bloqueo B son las seales de referencia de ruido

independiente.

T

j

XB B = (4.7)

Filtro pasa

banda

Matriz

de

Bloqueo

B

y(n) y(n)

84

En la Figura 4.16 se muestra el vector resultado B

j

.

1 2

1 3

1 4

1 5

1 6

1 7

1 8

1 9

1 10

1 11

1 12

1( ) 2( )

1( ) 3( )

1( ) 4( )

1( ) 5( )

1( ) 6( )

1( ) 7( )

1( ) 8( )

1( ) 9( )

1( ) 10( )

1( ) 11( )

1( ) 12( )

1(

n n

n n

n n

n n

n n

n n

n n

n n

n n

n n

n n

n

j

x x

x x

x x

x x

x x

x x

x x

x x

x x

x x

x x

x

B

o o

o o

o o

o o

o o

o o

o o

o o

o o

o o

o o

=

1 13

1 14

1 15

1 16

) 13( )

1( ) 14( )

1( ) 15( )

1( ) 16( )

n

n n

n n

n n

x

x x

x x

x x

o o

o o

o o

o o

(

(

(

(

(

(

(

(

(

(

(

(

(

(

(

(

(

(

(

(

(

(

(

(

(

Figura 4.16 Vector salida de la matriz de bloqueo, seales de ruido.

1( 1) 2( 2) 16( 16)

[ ... ]

n n n

X x x x

o o o

= (4.8)

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

1 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0 1 0 0 0 0 0 0 0 0 0 0 0 0 0

0 0 1 0 0 0 0 0 0 0 0 0 0 0 0

0 0 0 1 0 0 0 0 0 0 0 0 0 0 0

0 0 0 0 1 0 0 0 0 0 0 0 0 0 0

0 0 0 0 0 1 0 0 0 0 0 0 0 0 0

0 0 0 0 0 0 1 0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 1 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0 1 0 0 0 0 0 0

0 0 0 0 0 0 0 0 0 1 0 0 0 0 0

0 0 0 0 0 0 0 0 0 0 1 0 0 0 0

0 0 0 0 0 0 0

B

0 0 0 0 1 0 0 0

0 0 0 0 0 0 0 0 0 0 0 0 1 0 0

0 0 0 0 0 0 0 0 0 0 0 0 0 1 0

0 0 0 0 0 0 0 0 0 0 0 0 0 0 1

(

(

(

(

(

(

(

(

(

(

(

(

(

(4.9)

85

4.4.8 Algoritmo adaptable LMS

Para desarrollar el algoritmo LMS se utilizan las seales obtenidas de la matriz de

bloqueo, es decir las seales de referencia de ruido independiente, la seal obtenida del

formador de haz fijo y del filtro pasa banda que sirve como seal de referencia. El

algoritmo adaptable LMS busca reducir en amplitud los lbulos laterales del patrn de

radiacin de arreglo. Se utiliz la estructura transversal de filtro adaptable como se muestra

en la Figura 4.17.

Figura 4.17 Algoritmo adaptable LMS.

En la Figura 4.17 se observa que los resultados de la matriz de bloqueo B

j

son

multiplicados por los coeficientes w

cj

y despus se realiza la sumatoria de los productos con

lo que se obtiene la seal ( ) n q , de acuerdo con la ecuacin (4.10), lo que se busca con

dicha seal es enfatizar la seal deseada, es decir la seal de prueba, y atenuar las posibles

interferencias presentes.

La seal '( ) y n es la seal obtenida del formador de haz fijo despus de pasar por

un filtro pasa banda, la cual contiene la seal de prueba mezclada con interferencias; la

seal ( ) n q , la cual no contiene la seal de prueba y solo interferencias (que es lo que se

desea obtener con la matriz de bloqueo), al restar ( ) n q a '( ) y n se refuerza la seal deseada

con lo que se obtiene ( ), s n la cual sirve como seal de referencia para el algoritmo

adaptable LMS.

El algoritmo se realiza de acuerdo a la ecuacin (4.11)

15

1

( )

j Cj

j

n B w q

=

=

_

<

(4.10)

( 1) ( ) 2 ( )

Cj Cj j

w n w n s n B + = + < < < para j = 1, 2, 15

(4.11)

Matriz

de

Bloqueo

B

Algoritmo

adaptable

LMS

y(n)

q(n)

s(n)

W

c

B

j

86

Cabe mencionar que cada 45.35 ms que se realiza el cambio del vector de

direccionamiento, los coeficientes del algoritmo adaptable se igualan a cero para no ser

afectados por las condiciones anteriores debidas al vector de direccionamiento.

4.4.9 Clculo de la potencia

El clculo de la potencia se realiza mediante la ecuacin (4.12)

Al iniciar el proceso un registro acumulador se iguala a cero, s(n) se eleva al

cuadrado y se suma al registro acumulador:

Esto se realiza en cada 22.67 s , es decir, en cada periodo de muestreo, y sucede

2000 veces con lo que el acumulador es igual a

Una vez transcurridos 45.35 ms, dos mil veces el periodo de muestreo, el

acumulador es multiplicado por el inverso de dos mil y se guarda en un registro del buffer

de datos.

Continuando el ejemplo anterior de un escaneo de -60 a 60, el buffer de datos se

compone de veinticinco registros, cada registro corresponde a una direccin en especfico,

es decir cada registro contiene la potencia en una direccin de -60 hasta 60 cada 5 tal

como se muestra en la Figura 4.18.

Figura 4.18 Buffer registro de potencias.

Como se observa en la Figura 4.18, al inicio cuando el vector de direccionamiento

es de -60, transcurridos los 45.35 ms se guarda la potencia calculada en el buffer de datos,

2000

2

1

1

( ( ))

2000

k

k

P s n

=

=

_

(4.12)

2

( ( )) acumulador acumulador s n = + (4.13)

2000

2

1

( ( ))

k

k

acumulador s n

=

=

_

(4.14)

1

2000

P acumulador

u

= < (4.15)

P

u

Buffer registro de

potencia por direccin

u

87

el acumulador se iguala a cero para el clculo del siguiente valor de potencia. Ahora,

cuando el vector de direccionamiento apunta a -55, nuevamente trascurridos otros 45.35

ms se guarda la nueva potencia calculada en el registro reservado para -55; esto sucede

sucesivamente hasta cubrir todas las direcciones del buffer, lo cual se lleva a acabo en

1.1337 s. Una vez que se llega a la localidad asignada a los 60, se reinicia el proceso

regresando el vector direccionamiento a -60 y se calcula nuevamente la potencia.

Aunque aqu se mostr el caso del clculo de la potencia para la seal s(n),

adicionalmente se realiza el calculo de la potencia de la seal y(n), los resultados de la

potencia se ubican en otro buffer de datos, esto con el fin de ms adelante hacer una

comparacin entre el formador de haz con la estructura GSC y el formador de haz fijo.

Adicionalmente, las direcciones del haz controlados por el vector de

direccionamiento son dados para el intervalo de -60 a 60, aunque como se ver en el

Captulo 5 se utilizaron otros vectores direccionamiento para los intervalos de -90 a -60 y

de 60 a 90 con tal de saber como es el comportamiento del haz en esas direcciones; por lo

que el procedimiento del clculo de las potencias se realiza tambin para tales vectores de

direccionamiento.

4.4.10 Deteccin de direccin de arribo

Para determinar la direccin de arribo de la seal que incide en el arreglo se utiliza

el mtodo ms sencillo, es decir el mtodo de retraso y suma, el cual consiste en comparar

las potencias del haz apuntando a una direccin en especfico, la direccin que tenga una

mayor potencia es la direccin donde se encuentra la fuente.

Del proceso anterior, cuando se inicia en la direccin de -60, mientras se guarda la

potencia calculada en esa direccin se guarda esa misma potencia en un segundo registro

as como la direccin, ya en la siguiente direccin, en -55 mientras se guarda la nueva

potencia, sta se compara con la anterior; en caso de existir una mayor potencia, se guarda

esta potencia en el registro donde se encuentra la potencia calculada anteriormente as

como la direccin, en caso de no ser mayor simplemente no se hace ningn cambio. Esto se

efecta sucesivamente hasta llegar a los 60. Con este procedimiento, al finalizar se obtiene

la direccin donde se ubica la fuente la cual se va guardando en la variable dir la cual

cambia cada 1.13 s.

4.5 Sntesis

Paso a paso se ha descrito cmo est conformado el sistema, comenzando con el

arreglo de micrfonos formado por los diecisis micrfonos electret, y despus el circuito

acondicionador y la captura de datos que realiza el DSP con su perifrico ADC.

Con los datos obtenidos se procede a realizar el proceso de deteccin de direccin

de arribo; se muestra cmo se implement el algoritmo GSC, conformado por el formador

de haz fijo que junto con el vector de direccionamiento, la matriz de bloqueo y el algoritmo

adaptable, se obtienen las potencias respectivas a un haz en una direccin en especfico. Y

88

por ltimo, se explica el algoritmo de control para determinar la direccin de arribo de la

seal deseada.

S-ar putea să vă placă și

- Banco de filtros: Información sobre las técnicas del banco de filtros de Computer VisionDe la EverandBanco de filtros: Información sobre las técnicas del banco de filtros de Computer VisionÎncă nu există evaluări

- Transmisor de RF A 433.33 MHZDocument18 paginiTransmisor de RF A 433.33 MHZIng. Sergio RodríguezÎncă nu există evaluări

- Filtro adaptativo: Mejora de la visión por computadora mediante filtrado adaptativoDe la EverandFiltro adaptativo: Mejora de la visión por computadora mediante filtrado adaptativoÎncă nu există evaluări

- .2015 Radio Enlaces Digitales Con Linea de Vista Capitulo 3 Freddman y MasDocument67 pagini.2015 Radio Enlaces Digitales Con Linea de Vista Capitulo 3 Freddman y MasJorge Enrique Herrera RubioÎncă nu există evaluări

- Recepción y distribución de señales de radiodifusión. ELES0108De la EverandRecepción y distribución de señales de radiodifusión. ELES0108Încă nu există evaluări

- Transmisor FMDocument7 paginiTransmisor FMFercho RamoneÎncă nu există evaluări

- Antenas verticales para bajas frecuencias: (MF y HF)De la EverandAntenas verticales para bajas frecuencias: (MF y HF)Încă nu există evaluări

- AntenaLogaritimica - Aspectos de Diseño y Diagramas de RadiaciónDocument6 paginiAntenaLogaritimica - Aspectos de Diseño y Diagramas de RadiaciónMauro MAÎncă nu există evaluări

- Informe AnalizadorDocument10 paginiInforme AnalizadorNicolas BenavidesÎncă nu există evaluări

- Antena SHFDocument18 paginiAntena SHFMorgan WelchÎncă nu există evaluări

- Practica 6 ReceptoresDocument16 paginiPractica 6 ReceptoresHxCziiTaÎncă nu există evaluări

- Trabajo 1Document10 paginiTrabajo 1Romny PeraltaÎncă nu există evaluări

- Sintetizadores de FrecuenciaDocument5 paginiSintetizadores de FrecuenciaManuel AlejandroÎncă nu există evaluări

- Radio para ImprimirDocument28 paginiRadio para ImprimirsarasasasasaÎncă nu există evaluări

- Transmisión y Recepción AskDocument17 paginiTransmisión y Recepción AskLuis GsÎncă nu există evaluări

- Sistema FMDocument16 paginiSistema FMJaime Reyes RamosÎncă nu există evaluări

- Transmisor de Amplitud Modulada IDocument6 paginiTransmisor de Amplitud Modulada IjuniorÎncă nu există evaluări

- Amplificador de Audio de 20WDocument13 paginiAmplificador de Audio de 20WErikaMaldonadoPinedaÎncă nu există evaluări

- Transmisor de Frecuencia Modulada InformeDocument8 paginiTransmisor de Frecuencia Modulada InformeCarlos Chaname Segovia0% (1)

- QuizLab5 GrupoNo4Document4 paginiQuizLab5 GrupoNo4DiegoÎncă nu există evaluări

- Diseño Del Modulador de AmDocument5 paginiDiseño Del Modulador de AmKenyi DanielÎncă nu există evaluări

- Emisora de FM 1WDocument8 paginiEmisora de FM 1WRo JPÎncă nu există evaluări

- Modulacion y Demodulacion FMDocument8 paginiModulacion y Demodulacion FMWilliam TamayoÎncă nu există evaluări

- Circuitos de Filtrado Con Componentes PasivosDocument7 paginiCircuitos de Filtrado Con Componentes PasivosFhertronics AutotronicaÎncă nu există evaluări

- Diseño de Un Amplificador de Mínimo Ruido en ADSDocument10 paginiDiseño de Un Amplificador de Mínimo Ruido en ADSCRISTIAN BRAYAN ALDUDE JOSECÎncă nu există evaluări

- Laboratorio de Telecomunicaciones IDocument7 paginiLaboratorio de Telecomunicaciones IJhan Marcos Llusco MamaniÎncă nu există evaluări

- Problem As 1Document13 paginiProblem As 1Rubén GalleÎncă nu există evaluări

- Filtro PasabandaDocument28 paginiFiltro PasabandaHector Yucra MattosÎncă nu există evaluări

- Curso de Sistemas de Television Por Cable-MantoDocument29 paginiCurso de Sistemas de Television Por Cable-Mantoyiyojose100% (1)

- Lab12 Metx 2Document34 paginiLab12 Metx 2Maria Alejandra Cortes PinzonÎncă nu există evaluări

- Modulacion FMDocument8 paginiModulacion FMAlvio Valencia GonzaliaÎncă nu există evaluări

- (Comunicaciones I) Informe de Practica Nro. 3Document9 pagini(Comunicaciones I) Informe de Practica Nro. 3Criistopher CoroniilÎncă nu există evaluări

- (Comunicaciones I) Informe de Practica Nro. 2Document9 pagini(Comunicaciones I) Informe de Practica Nro. 2Criistopher CoroniilÎncă nu există evaluări

- Informe Transmisor FMDocument10 paginiInforme Transmisor FMDavid CamargoÎncă nu există evaluări

- Laboratorio Comunicaciones 3Document7 paginiLaboratorio Comunicaciones 3Jessica SuarezÎncă nu există evaluări

- 2da Actividad Sumativa, Samuel Ali, C.I 28.312.919, O713Document16 pagini2da Actividad Sumativa, Samuel Ali, C.I 28.312.919, O713samuel.boscan.18Încă nu există evaluări

- Diseño, Implementación y Evaluación de Un Modulador AMDocument18 paginiDiseño, Implementación y Evaluación de Un Modulador AMMajo TeranÎncă nu există evaluări

- Sistema de Radio Control DiscretoDocument9 paginiSistema de Radio Control DiscretoSebastián Sandoval100% (1)

- Filtros ActivosDocument42 paginiFiltros ActivosFredo AlejosÎncă nu există evaluări

- Transmisor FM Escorpión e Info InfrarrojoDocument5 paginiTransmisor FM Escorpión e Info InfrarrojoRoger Azcorra NoveloÎncă nu există evaluări

- Modulador y Demodulador AMDocument12 paginiModulador y Demodulador AMXime OrtizÎncă nu există evaluări

- Sistema de ComunicacionDocument28 paginiSistema de ComunicacionAlvaro FabianÎncă nu există evaluări

- Diseño e Implementación de Un Transmisor FM A 106.5Document11 paginiDiseño e Implementación de Un Transmisor FM A 106.5Ronald Pineda100% (1)

- Micro OndasDocument18 paginiMicro OndasAngel Figueroa SierraÎncă nu există evaluări

- Bobinas 1111Document8 paginiBobinas 1111Hernán Cote IsaacsÎncă nu există evaluări

- Modulos de RFDocument10 paginiModulos de RFHarry CalahamÎncă nu există evaluări

- Luces AudioritmicasDocument14 paginiLuces AudioritmicasA.JÎncă nu există evaluări

- Inf6 LTelcom1Document4 paginiInf6 LTelcom1Mónica Condori100% (1)

- P 04Document39 paginiP 04GastarotÎncă nu există evaluări

- Modulación ASKDocument14 paginiModulación ASKMIGUEL GUEVARA RAMIREZÎncă nu există evaluări

- Radio-Enlace de MicroondasDocument32 paginiRadio-Enlace de Microondasplavin2012100% (1)

- Transmisor FMDocument15 paginiTransmisor FMJuan Carlos Quispe SanoÎncă nu există evaluări

- Modulador y Demodulador FMDocument14 paginiModulador y Demodulador FMThony HAÎncă nu există evaluări

- Proyecto FinalDocument6 paginiProyecto FinalDavid FigueroaÎncă nu există evaluări

- Laboratorio 2 Comunicación AnalógicaDocument10 paginiLaboratorio 2 Comunicación AnalógicaHENRY GABRIEL G�MEZ GER�NIMOÎncă nu există evaluări

- Recepcion de Amplitud Modulada InformeDocument11 paginiRecepcion de Amplitud Modulada InformeAyrton Estrada SotoÎncă nu există evaluări

- Cálculo de Enlace Fibra ÓpticaDocument13 paginiCálculo de Enlace Fibra ÓpticaNovio De Yulii DiiazÎncă nu există evaluări

- FMDocument3 paginiFMDeivid CarreraÎncă nu există evaluări

- Curso de Datos en Redes HFCDocument60 paginiCurso de Datos en Redes HFCFrancisco Serrano Flores100% (2)

- Informe Laboratorio (Filtro Pasa Bajos) - Sebastián Puerta, Juan Camilo Sabogal y Jorge GuzmánDocument11 paginiInforme Laboratorio (Filtro Pasa Bajos) - Sebastián Puerta, Juan Camilo Sabogal y Jorge GuzmánSebastian PuertaÎncă nu există evaluări

- Practica 12 CPIDocument13 paginiPractica 12 CPIvaniaDRCÎncă nu există evaluări

- CU00825B Arrays Asociativos PHP Concepto Ejemplos Ejercicios Resueltos PDFDocument3 paginiCU00825B Arrays Asociativos PHP Concepto Ejemplos Ejercicios Resueltos PDFRoger8aÎncă nu există evaluări

- Informe Computacion Matrices PDFDocument5 paginiInforme Computacion Matrices PDFDianys LCÎncă nu există evaluări

- Comandos Básicos en ArduinoDocument15 paginiComandos Básicos en ArduinoCheChyHr50% (6)

- Compuertas LogicasDocument13 paginiCompuertas Logicaspumb000Încă nu există evaluări

- Introducción A Data Science: Programación Estadística Con RDocument80 paginiIntroducción A Data Science: Programación Estadística Con RJaviercyto López100% (1)

- Drupal 7 Conocimientos Previos para Entender Este TutorialDocument5 paginiDrupal 7 Conocimientos Previos para Entender Este TutorialHomero Ruiz Hernandez100% (1)

- Introduccion A RDocument9 paginiIntroduccion A ROmar GzlzÎncă nu există evaluări

- Swift EspanolDocument27 paginiSwift EspanolFrancisco Reyes Santana100% (2)

- Arreglo MultidimensionalDocument16 paginiArreglo Multidimensionaladrilinda67% (6)

- Pilasveersion 1Document28 paginiPilasveersion 1Axel SarmientoÎncă nu există evaluări

- EjerciciosDocument40 paginiEjerciciosQarrizalw's xdÎncă nu există evaluări

- LISTAS ENLAZADAS Trabajo MonograficoDocument14 paginiLISTAS ENLAZADAS Trabajo MonograficoJaime Jayden Charri HuertaÎncă nu există evaluări

- ArrayDocument7 paginiArrayAnita Jas V MÎncă nu există evaluări

- Ut1.6 ArraysDocument4 paginiUt1.6 ArraysKaterine Aracely Lampeduza PomaÎncă nu există evaluări

- Nómina Usando Ciclos y Acumuladores en JavaDocument7 paginiNómina Usando Ciclos y Acumuladores en JavaMarco SánchezÎncă nu există evaluări

- Arreglos UnidimensionalesDocument2 paginiArreglos UnidimensionalesMaricielo AnampaÎncă nu există evaluări

- FortranDocument84 paginiFortranCesar Hernandez100% (1)

- Guia Arreglos Bidimensionales en C++Document8 paginiGuia Arreglos Bidimensionales en C++Guadalupe Lopez LeyvaÎncă nu există evaluări

- Parte Textual Actividad de Aprendizaje #2Document11 paginiParte Textual Actividad de Aprendizaje #2Gabriel CastroÎncă nu există evaluări

- CursorDocument99 paginiCursorLuis Fernando MaronÎncă nu există evaluări

- Arreglos Bidimensionales ProgramacionDocument3 paginiArreglos Bidimensionales ProgramacionSebastián LassoÎncă nu există evaluări

- Unidad 1 - ColeccionesDocument19 paginiUnidad 1 - ColeccionesMariano MoyanoÎncă nu există evaluări

- Guia de Trabajo POODocument42 paginiGuia de Trabajo POOsaul valdezÎncă nu există evaluări

- Unidad 3 Manipulación de Errores y Conjuntos de Objetos NET IIDocument64 paginiUnidad 3 Manipulación de Errores y Conjuntos de Objetos NET IILeonel MoralesÎncă nu există evaluări

- Taller Dividir y Conquistar Marzo 25 - 2020Document2 paginiTaller Dividir y Conquistar Marzo 25 - 2020eduardo ariasÎncă nu există evaluări

- Arreglos UnidimensionalesDocument12 paginiArreglos UnidimensionalesDiego Steven Pulido AriasÎncă nu există evaluări

- Tema 2: de C A C++. Introducción y Conceptos.: Declaraciones Frente A DefinicionesDocument19 paginiTema 2: de C A C++. Introducción y Conceptos.: Declaraciones Frente A DefinicionesJose MaldonadoÎncă nu există evaluări

- Manual Desarrollador WSCT v11Document88 paginiManual Desarrollador WSCT v11MatiasÎncă nu există evaluări

- Flashlite 2.x 3.x AslrDocument738 paginiFlashlite 2.x 3.x AslrRaúl ParísÎncă nu există evaluări