Documente Academic

Documente Profesional

Documente Cultură

Pid VHDL 6

Încărcat de

Pleple ArjsanamTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Pid VHDL 6

Încărcat de

Pleple ArjsanamDrepturi de autor:

Formate disponibile

The 8th Symposium on Advances in Science and Technology (8thSASTech), Mashhad, Iran. 8thSASTech.khi.ac.

ir

FPGA Design and Implementation of Digital PID Controller

based on floating point arithmetic

Pourya Alinezhad 1, Arash Ahmadi 2

1- M.Sc. student of Electrical and communication engineering

Shahid Bahonar University, Iran

palinezhad@eng.uk.ac.ir

2- B.Sc. of Electrical and Electronics Engineering

Karaj Islamic Azad University, Iran

ahmadi.eng87@gmail.com

Abstract

This paper proposes a method for the design of digital PID controller on Field Programmable

Gate Array with floating point arithmetic. Here we use Matlab HDL coder toolbox for

implementing PID controller. Also an 8bit microprocessor called Picoblaze is programmed on

FPGA chip to control peripherals like A/D and D/A converters, input output bottoms,

character LCD etc. Required logical and mathematical operators like comparison and

summation are overloaded to accept floating point numbers as input so calculations would

have higher precision than software based PID controllers. Simulink model is used to plot the

time response of PID controller. VHDL code generation and programming is performed in

ISE9 software from Xilinx Company. We used Coregen for implementing floating point

blocks. The proposed method was implemented practically on Xilinx Spartan-3E FPGA

Board.

Key words: FPGA, Picoblaze, PID controller, HDL, Simulink

1. Introduction

A control system consists of two subsystems, a plant and a controller. The plant is an

entity controlled by the controller [1]. The controller can be either analog or digital.

Generally, an implementation of digital PID controller includes the use of microprocessors

or microcontrollers. The memory holds the application program while the processor

fetches, decodes, and executes the program instructions. One of disadvantages of this

method is the speed of operations because the operations depend on software which has a

sequence of instructions and commands which needs many machine cycles to execute.

Therefore, FPGA-based digital PID controller is proposed because the operations on

FPGA are hardware compatible operations. Better speed performance could be achieved

because all operations are down in parallel. Proposed FPGA-based digital PID controller

uses floating point math operands for computations. Here we overloaded these

computations for floating point arithmetic to achieve better accuracy.

Modern FPGAs and their distinguishable capabilities have been advertised

extensively by FPGA vendors. Moreover, some refereed articles addressed the advantages

of utilizing these powerful chips [2]. Recently, Spartan II and III FPGA families from

Xilinx have been successfully utilized in a variety of applications which include inverters,

communications, imbedded processors, and image processing.

The 8th Symposium on Advances in Science and Technology (8thSASTech), Mashhad, Iran. 8thSASTech.khi.ac.ir

Here we use Spartan-3E toolkit from Xilinx Company to implement our designed PID

controller.

So many works have been down to implement conventional PID controllers but a

few studies were made for implementing PID controllers on FPGAs. Gupta and Khare [1]

proposed a method to design the PID controller in Simulink but no practical works were

made. XU and SHUANG [3] designed a Fixed-point Digital PID Controller and showed

that high reliability and fast response speed with wide dynamic range could be achieved.

Sonoli and Nagabhushan [4] used FPGA based PID Controller for controlling DC Motor

system. Behnam and Mansouryar [5] designed a digital PID Controller and Encoder Using

Xilinx System Generator library in Simulink. Xilinx System Generator is a Simulink

library block set provided by Xilinx Company to generate FPGA compatible models.

In [6] a PID controller designed to achieve a balance between the speed and the

exhausted FPGA resources. [7] Presents a novel technique for implementation of an

efficient FPGA based digital PID controller for the motion control of a permanent magnet

DC motor. In [8] Patel & singh designed FPGA-based all Digital PID Controller on

Spartan3e XC3S100E FPGA.

In this paper, we develop a new PID controller model based on floating point

arithmetic. In section 2 discrete PID model is reviewed and a Simulink model is designed

and simulations are performed to verify model. Also some practical issues like

Untiwindup implementation are considered. Section 3 illustrates floating point numbers

and HDL code generation. Section 4 shows practical results of designed PID controller

and also describes some practically used tools. Finally, section 5 concludes the paper.

2.Discrete PID model

At first we need a complete model of the digital controller. We start our work by

continues model and then the discrete model could be achieved with some manipulations.

Consider a PID and the Planet model as shown in Fig 1.

Fig 1. A typical Planet model

As we know PID controller consists of proportional, derivative and integral

coefficients. The controller could be shown in time domain by Eq.1.

1

()

() +

]

0

is the proportional coefficient and e(t) shows controller input signal.

are integral and derivative coefficients respectively. In Laplace domain

we can write Eq.1 as follows:

() = [() +

() = [1 +

1

+ ]

(1)

(2)

The 8th Symposium on Advances in Science and Technology (8thSASTech), Mashhad, Iran. 8thSASTech.khi.ac.ir

Now in order to have discrete form we must transfer Eq.2 to z domain. We can

determine a digital implementation of this controller by using a discrete

approximation for the derivative and integration [9].Impulse invariance or bilinear

methods [10] could be used to achieve discrete form. Here we use bilinear

transform. Bilinear transform is made by Taylor series expansion of function and

using time shift property of signal with is equal to a delay in z domain (Eq.3).

{[ ]}] = [z] , where

{[]} = []

(3)

is transform operator and illustrates time shifting. Bilinear transformation

equation is performed as follows:

() = ( 1) +

[](1 1 ) =

() + ( 1)

[](1 + 1 )

2

[] + 1

=

[] 2 1

(4)

(5)

(6)

Eq.4 shows Taylor expansion and Eq.5 shows transformed series to Z domain.

Finally, Eq.6 is rearranged form of Eq.5 and shows the bilinear formula. is

sampling Time.

Applying bilinear transform on PID controller by Eq.2 and Eq.6 results:

( 1)

[]

( + 1)

= +

+

[]

2 ( 1)

2

2

2

[] ( ) + 2 ( + ) + Ts (z 2z + 1)

=

[]

2

2

2

[] ( + 2 + ) + ( + 2 ) +

=

[]

2

After multiplying numerator and denominator of Eq.8 by 2 we have:

2 1 2

[] ( + 2 + ) + ( + 2 ) +

=

[]

1 1

(7)

(8)

(9)

(10)

And after some straight forward simplifications we reach the following formula:

[] = 1 [] + [] + 1 [] + 2 []

(11)

[] = [ 1] + [] + [ 1] + [ 2]

(12)

Eq.12 shows the time domain discrete PID controller.

The 8th Symposium on Advances in Science and Technology (8thSASTech), Mashhad, Iran. 8thSASTech.khi.ac.ir

Now we progress our work by simulating the discrete PID controller base on Eq.11.

Fig.2 shows the designed PID controller in Matlabs Simulink environment. The

coefficients are tuned practically.

This model still has some problems. We have to use an Untiwindup to prevent

integral term from saturation. There are many ways to protect against windup where the

integrator part of PID controller saturates due to accumulation nature of integration.

Tracking is a simple method which is illustrated in block diagram in Fig.3.a.

Fig.2.Disceret PID controller model

Fig.3.b shows the Simulink model of Untiwindup. In Fig.3.a the system has an extra

feedback path around the integrator. The signal is the difference between the nominal

controller output and the saturated control output . The signal is fed to the input of

integrator through gain1/ . The signal is zero when there is no saturation. Under these

circumstances it will not have any effect on the integrator. When the actuator saturates, the

signal is different from zero and it will try to drive the integrator output to a value such

that the signal is close to the saturation limit.

Fig.3.a. Untiwindup presentation

Fig.3.b. Untiwindup simulation model

2

The designed PID controller is simulated in a planet with () = 2 +4+100 as

systems transfer function in a closed loop and a periodic pulse with = 1/20 is

applied to input. Moreover predefined Simulink PID model is included for comparing

results. Fig.4 shows the input signal, designed discrete PID controller without Untiwindup,

designed discrete PID controller with Untiwindup and predefined Simulink Model

The 8th Symposium on Advances in Science and Technology (8thSASTech), Mashhad, Iran. 8thSASTech.khi.ac.ir

respectively from top to bottom. Its obvious that the PID without Untiwindup couldnt

answer to input step pulse applied in 10sec.

So far we have defined the essential concepts for discrete PID controller. In next

section a brief review on floating point representation is explained.

Fig.4. top to bottom : input signal , designed discrete PID controller without Untiwindup ,

designed discrete PID controller with Untiwindup , predefined Simulink PID block output

3. Floating point blocks

Floating-point numbers are the favorites of software people, and the least favorite of

hardware people. The reason for this is because floating point takes up almost 3X the

hardware of fixed-point math. The advantage of floating point is that precision is always

maintained with a wide dynamic range, where fixed point numbers loose precision.

Floating-point numbers are well defined by IEEE-754 (32 and 64 bit) and IEEE-854

(variable width) specifications. Floating point has been used in processors and IP for years

and is a well-understood format. This is a sign magnitude system, where the sign is

processed differently from the magnitude.

There are many concepts in floating point that make it different from our common

signed and unsigned number notations. These come from the definition of a floating-point

number. Below is a 32-bit floating-point number format:

S EEEEEEEE FFFFFFFFFFFFFFFFFFFFFFF

31 30

+/-

25 24

exp

Fraction

(13)

Basically, a floating-point number comprises a sign bit (+ or ), a normalized exponent,

and a fraction. To convert this number back into an integer, the following equation can be

used:

(14)

2 ^ ( _) (1.0 + /_)

Where the exponent_base is 2^(( /2) 1), and Fraction_base is

the maximum possible fraction (unsigned) plus one. Thus, for a 32-bit floating-point an

example would be:

0 10000001 101000000000000000000000

(15)

= +1 2^ (129 127) * (1.0 + 10485760/16777216) = +1 * 4.0 * 1.625 = 6.5

The 8th Symposium on Advances in Science and Technology (8thSASTech), Mashhad, Iran. 8thSASTech.khi.ac.ir

There are also denormal numbers, which are numbers smaller than can be represented

with this structure. The tag for a denormal number is that the exponent is 0. This forces

you to invoke another formula where you drop the 1.0 +:

1 00000000 100000000000000000000000

= -1 * 2** -126 * (8388608/16777216) = -1 * 2**-126 * 0.5 = -2**-127

(16)

Next, the constants that exist in the floating-point context are:

0 00000000 000000000000000000000000 = 0

1 00000000 000000000000000000000000 = -0 (which = 0)

0 11111111 000000000000000000000000 = positive infinity

1 11111111 000000000000000000000000 = negative infinity

(17)

In this project we define and use a smaller floating point with just 11 fraction bits and

7 exponent bits. So counting the sign bit, our floating point number has 20 bits. Floating

point blocks are implemented using ISE9 Corgen which easily produces embedded

codes based on user defined adjustments.

4. Results

HDL code of the designed PID Model in section 2 is generated using Matlab HDL Coder

Toolbox. On the other hand floating point arithmetic operands are programmed using

Corgen. Merging these two codes results an overloaded PID controller with floating point

operations. The whole code is simulated in ISE9 environment and the results are shown in

Fi.4.a. , Fig.4.b and Fig.5.

Fig.4.b. Part of the technological schematic

(Zoomed)

Fig.4.a. Full PID

technological schematic

The 8th Symposium on Advances in Science and Technology (8thSASTech), Mashhad, Iran. 8thSASTech.khi.ac.ir

Fig.5. PID controller RTL schematic

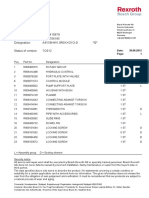

Device utilization summary could be seen in Fig.6. The target device is xc3s500e

FPGA from Xilinx Family.

Fig.6. Utilized sources of FPGA

Now as could be seen in Fig.4 we implemented a full digital PID controller which has

9 pins. pid_z and pid_u are input and output ports respectively. pid_kp, pid_ki and

pid_kd are proportional, derivative and integral coefficients respectively. These

coefficients are adjusted by available on board devices like pushbuttons and their values

could be seen on an LCD. Linear Tech LTC2624 Quad DAC and LTC1407A-1 Dual

A/D are used to convert input analog signal to digital and vice versa. For additional

information about the peripherals on Spartan-3E board see [11]. All UCF location

constraints for FPGA pin assignment are adopted from embedded Kit.

At last an 8 bit microprocessor called Picoblaze [12] is programmed on FPGA and

hundreds line of embedded assembly code for this microprocessor was written and

assembled using KCPSM3 Assembler in order to control peripheral devices like A/D

and D/A converter, pushbuttons, LCD.etc. The Picoblaze and Assembler source codes are

available at Xilinx official website for free. Simulated signals of these peripherals are

shown in Fig.7.

Fig.7. control signals generated by Picoblaze for controlling peripheral devices

5. Conclusions

The 8th Symposium on Advances in Science and Technology (8thSASTech), Mashhad, Iran. 8thSASTech.khi.ac.ir

In this paper we designed and implemented a digital PID controller with floating point

arithmetic. The advantage of the proposed method is its capability to do high precision

arithmetic. The designed controller also benefits from other intrinsic performances of

FPGAs like its high speed and low power. Obviously these floating point operands could

be used to implement other digital filters. Matlab HDL coder toolbox and Picoblaze

played a main role in PID implementation on xc3s500e FPGA. Future researches could be

down to use the designed PID to control a system like servomotor. Another topic would be

implementing floating point with higher precision (32 or 64 bit).

Acknowledgements

The authors gratefully acknowledge the support and encouragements of Sir AmirReza

Siminfar without whom this project couldnt be completed.

References

[1] Gupta & Khare .(2009) Efficient FPGA Design and Implementation of Digital PID

Controllers in Simulink. International Journal of Recent Trends in Engineering

[2] Abdelati.(2008).FPGA-Based PID Controller Implementation.The Islamic University

of Gaza

[3] XU & SHUANG. (2009) FPGA Implementation of a Best-precision Fixed-point

Digital PID Controlle. 2009 International Conference on Measuring Technology and

Mechatronics Automation

[4] Sonoli & Raju .(2010). Implementation of FPGA based PID Controller for DC Motor

Speed Control System. Proceedings of the World Congress on Engineering and Computer

Science 2010 Vol II

[5] Behnam & Mansouryar .(2011). Modeling and Simulation of a DC Motor Control

System with Digital PID Controller and Encoder in FPGA Using Xilinx System

Generator. 2nd International Conference on Instrumentation, Control and Automation 1517 November 2011, Bandung, Indonesia

[6] Feng & Yan. (2011). Implement of digital PID Controller Based on FPGA and the

System Co-simulation. International Conference on Instrumentation, Measurement,

Computer, Communication and Control

[7] Ghosh & Barai (2013) An FPGA Based Implementation of a Flexible Digital PID

Controller For a Motion Control System. 2013 International Conference on Computer

Communication and Informatics (ICCCI -2013), Jan. 04 06, 2013, Coimbatore, INDIA

[8] Patel & singh. (2012). Design of FPGA-based All Digital PID Controller for Dynamic

Systems. International Journal of Advanced Research in Electrical, Electronics and

Instrumentation Engineering Vol. 1, Issue 2, August 2012

[9] Dorf & Bishop. (2010) Modern Control Systems. Prentice Hall

[10] Oppenheim & Schafer (1999) Discrete Time signal processing. Prentice Hall

[11] Digilent, Inc.(2011) Spartan-3E FPGA Starter Kit Board User Guide. UG230 (v1.2)

[12] Digilent, Inc.(2011) PicoBlaze 8-bit Embedded Microcontroller User Guide. UG129

June 22, 2011

S-ar putea să vă placă și

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (400)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (74)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- 0404 eDocument80 pagini0404 eFrancisco MisleÎncă nu există evaluări

- Inventory Counting in Inventory ManagementDocument15 paginiInventory Counting in Inventory ManagementDinesh GuptaÎncă nu există evaluări

- S1 Mock 2Document13 paginiS1 Mock 2Abdulrahman HatemÎncă nu există evaluări

- Tankless Vs TankDocument2 paginiTankless Vs TankClick's PlumbingÎncă nu există evaluări

- Service Manual: DDX24BT, DDX340BTDocument94 paginiService Manual: DDX24BT, DDX340BTDumur SaileshÎncă nu există evaluări

- Czujniki Temperatury MOTOMETERDocument7 paginiCzujniki Temperatury MOTOMETERhelp3rÎncă nu există evaluări

- Indian Standard: Methods of Test For Aggregates For ConcreteDocument22 paginiIndian Standard: Methods of Test For Aggregates For ConcreteAnuradhaPatraÎncă nu există evaluări

- Control System Engineering: Topic Block Diagram RepresentationDocument24 paginiControl System Engineering: Topic Block Diagram RepresentationWaqas AfzalÎncă nu există evaluări

- Universiti Teknologi Mara (Uitm) Shah Alam, MalaysiaDocument4 paginiUniversiti Teknologi Mara (Uitm) Shah Alam, MalaysiaSuraya AdriyanÎncă nu există evaluări

- Music, Arts, Pe & HealthDocument2 paginiMusic, Arts, Pe & HealthEvan Maagad LutchaÎncă nu există evaluări

- AI Coming For LawyersDocument4 paginiAI Coming For LawyersbashiÎncă nu există evaluări

- 09-Hispec DespecDocument51 pagini09-Hispec DespecHyungon KimÎncă nu există evaluări

- Refrigeration and Air ConditioningDocument41 paginiRefrigeration and Air Conditioningrejeesh_rajendranÎncă nu există evaluări

- What Is Situational Coaching and When To Use ItDocument3 paginiWhat Is Situational Coaching and When To Use ItBrian KamoedÎncă nu există evaluări

- Vocabulary Placement TestDocument3 paginiVocabulary Placement TestMonica Vergara MejiaÎncă nu există evaluări

- Rizal and The Theory of NationalismDocument37 paginiRizal and The Theory of NationalismLiza Betua Sotelo78% (58)

- X20PS9600-en V1.20Document10 paginiX20PS9600-en V1.20PREVENCIONISTA HUAQUIANÎncă nu există evaluări

- Prudence and FrugalityDocument17 paginiPrudence and FrugalitySolaiman III SaripÎncă nu există evaluări

- Sec ListDocument288 paginiSec ListTeeranun NakyaiÎncă nu există evaluări

- Art & Science: Meeting The Needs of Patients' Families in Intensive Care UnitsDocument8 paginiArt & Science: Meeting The Needs of Patients' Families in Intensive Care UnitsRiaÎncă nu există evaluări

- Sepction - 3Document3 paginiSepction - 3k koradiaÎncă nu există evaluări

- A4v56hw1 0r0xxo1o-S R909410979 233 19 04 03Document25 paginiA4v56hw1 0r0xxo1o-S R909410979 233 19 04 03Alonso TabordaÎncă nu există evaluări

- Form-1: Application Form For Gate Registration Fee Refund Under Teqip-IiiDocument1 paginăForm-1: Application Form For Gate Registration Fee Refund Under Teqip-IiiWasim LaskarÎncă nu există evaluări

- Oo All MethodDocument35 paginiOo All Methodmeeraselvam19761970Încă nu există evaluări

- Mazada Consortium LimitedDocument3 paginiMazada Consortium Limitedjowila5377Încă nu există evaluări

- Remembering Thanu Padmanabhan - The HinduDocument3 paginiRemembering Thanu Padmanabhan - The HinduIucaa libraryÎncă nu există evaluări

- C PM 71.v2016-12-11 PDFDocument31 paginiC PM 71.v2016-12-11 PDFbobi2201Încă nu există evaluări

- Accenture United Nations Global Compact IndexDocument4 paginiAccenture United Nations Global Compact IndexBlasÎncă nu există evaluări

- List of ItemsDocument5 paginiList of ItemsMoiÎncă nu există evaluări

- Ball Valves PDFDocument34 paginiBall Valves PDFThomasFrenchÎncă nu există evaluări