Documente Academic

Documente Profesional

Documente Cultură

VHDL Sequential

Încărcat de

SAKETSHOURAVDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

VHDL Sequential

Încărcat de

SAKETSHOURAVDrepturi de autor:

Formate disponibile

VHDL codes for common Sequential

Circuits:

Positive edge triggered JK Flip Flop with reset input

Here is the code for JK Flip flop which is positive edge triggered.The flip flop also has a reset input which

when set to '1' makes the output Q as '0' and Qbar as '1'.

--libraries to be used are specified here

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

--entity declaration with port definitions

entity JK_Flipflop is

port ( clk:

in std_logic;

J, K:

in std_logic;

Q, Qbar:

out std_logic;

reset:

in std_logic

);

end JK_Flipflop;

--architecture of entity

architecture Behavioral of JK_Flipflop is

--signal declaration.

signal qtemp,qbartemp : std_logic :='0';

begin

Q <= qtemp;

Qbar <= qbartemp;

process(clk,reset)

begin

if(reset = '1') then

qtemp <= '0';

qbartemp <= '1';

elsif( rising_edge(clk) ) then

if(J='0' and K='0') then

NULL;

elsif(J='0' and K='1') then

qtemp <= '0';

qbartemp <= '1';

elsif(J='1' and K='0') then

qtemp <= '1';

qbartemp <= '0';

else

qtemp <= not qtemp;

qbartemp <= not qbartemp;

end if;

end if;

end process;

end Behavioral;

--Reset the output.

--No change in the output

--Set the output.

--Reset the output.

--Toggle the output.

4 bit Synchronous UP counter(with reset) using JK flip-flops

Here is the code for 4 bit Synchronous UP counter.The module uses positive edge triggered JK flip flops for

the counter.The counter has also a reset input.The JK flipflop code used is from my previous blog.For simulating

this counter code,copy and paste the JK flipflop code available at the above link in a file and store the file in the

same directory with other .vhd files.

The top module code is given below:

--libraries to be used are specified here

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

--entity declaration with port definitions

entity syn_count4 is

port ( clk:

in std_logic;

reset:

in std_logic;

counter : out std_logic_vector(3 downto 0)

);

end syn_count4;

--architecture of entity

architecture Behavioral of syn_count4 is

--signal declaration.

signal J3,J4,Q1,Q2,Q3,Q4,Qbar1,Qbar2,Qbar3,Qbar4 : std_logic :='0';

begin

J3 <= Q1 and Q2;

J4<= J3 and Q3;

--entity instantiations

FF1 : entity work.JK_Flipflop

FF2 : entity work.JK_Flipflop

FF3 : entity work.JK_Flipflop

FF4 : entity work.JK_Flipflop

counter <= Q4 & Q3 & Q2 & Q1;

end Behavioral;

port

port

port

port

map

map

map

map

(clk,'1','1',Q1,Qbar1,reset);

(clk,Q1,Q1,Q2,Qbar2,reset);

(clk,J3,J3,Q3,Qbar3,reset);

(clk,J4,J4,Q4,Qbar4,reset);

Example : 4 bit Ring Counter with testbench

A ring counter is a digital circuit which consists of a series of flip flops connected together in a feedback

manner.The circuit is special type of shift register where the output of the last flipflop is fed back to the input of

first flipflop.When the circuit is reset, except one of the flipflop output,all others are made zero. For n-flipflop ring

counter we have a MOD-n counter. That means the counter has n different states.

The circuit diagram for a 4 bit ring counter is shown below:

I have written a VHDL code for a 4-bit ring counter which has the following states:

0001 - 0010 - 0100 - 1000 ....

The code is posted below:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity ring_counter is

port (

DAT_O : out unsigned(3 downto 0);

RST_I : in std_logic;

CLK_I : in std_logic

);

end ring_counter;

architecture Behavioral of ring_counter is

signal temp : unsigned(3 downto 0):=(others => '0');

begin

DAT_O <= temp;

process(CLK_I)

begin

if( rising_edge(CLK_I) ) then

if (RST_I = '1') then

temp <= (0=> '1', others => '0');

else

temp(1) <= temp(0);

temp(2) <= temp(1);

temp(3) <= temp(2);

temp(0) <= temp(3);

end if;

end if;

end process;

end Behavioral;

Example : D Flip-Flop with Asynchronous Clear,Set and Clock

Enable

As per the request from readers I have decided to post some basic VHDL codes for beginners in VHDL. This

is the second one in the series, a basic D Flip-Flop with Asynchronous Clear,Set and Clock Enable(negedge

clock).The code is self explanatory and I have added few comments for easy understanding.

--library declaration for the module.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

--This is a D Flip-Flop with Asynchronous Clear,Set and Clock

Enable(negedge clock).

--Note that the clear input has the highest priority,preset being the

next highest

--priority and clock enable having the lowest priority

entity example_FDCPE is

port(

Q : out std_logic;

-- Data output

CLK :in std_logic;

-- Clock input

CE :in std_logic;

-- Clock enable input

CLR :in std_logic; -- Asynchronous clear input

D :in std_logic;

-- Data input

PRE : in std_logic

-- Asynchronous set input

);

end example_FDCPE;

architecture Behavioral of example_FDCPE is

circuit.

begin

--architecture of the

--"begin" statement for architecture.

process(CLR,PRE,CLK) --process with sensitivity list.

begin --"begin" statment for the process.

if (CLR = '1') then --Asynchronous clear input

Q <= '0';

else

if(PRE = '1') then --Asynchronous set input

Q <= '1';

else

if ( CE = '1' and falling_edge(CLK) ) then

Q <= D;

end if;

end if;

end if;

end process;

--end of process statement.

end Behavioral;

Example : D Flip-Flop with Synchronous Reset,Set and Clock

Enable

As per the request from readers I have decided to post some basic VHDL codes for beginners in VHDL. This is

the first one, a basic D Flip-Flop with Synchronous Reset,Set and Clock Enable(posedge clock).The code is

self explanatory and I have added few comments for easy understanding.

--library declaration for the module.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

--This is a D Flip-Flop with Synchronous Reset,Set and Clock

Enable(posedge clk).

--Note that the reset input has the highest priority,Set being the next

highest

--priority and clock enable having the lowest priority.

entity example_FDRSE is

port(

Q : out std_logic;

-- Data output

CLK :in std_logic;

-- Clock input

CE :in std_logic;

-- Clock enable input

RESET :in std_logic; -- Synchronous reset input

D :in std_logic;

-- Data input

SET : in std_logic

-- Synchronous set input

);

end example_FDRSE;

architecture Behavioral of example_FDRSE is --architecture of the

circuit.

begin --"begin" statement for architecture.

process(CLK) --process with sensitivity list.

begin --"begin" statment for the process.

if ( rising_edge(CLK) ) then --This makes the process

synchronous(with clock)

if (RESET = '1') then

Q <= '0';

else

if(SET = '1') then

Q <= '1';

else

if ( CE = '1') then

Q <= D;

end if;

end if;

end if;

end if;

end process; --end of process statement.

end Behavioral;

S-ar putea să vă placă și

- Projects With Microcontrollers And PICCDe la EverandProjects With Microcontrollers And PICCEvaluare: 5 din 5 stele5/5 (1)

- VHDL Code For D FF Using Behavior ModelDocument20 paginiVHDL Code For D FF Using Behavior ModelAdithya ChakilamÎncă nu există evaluări

- Experiment No. 2: Aim: A) D Flip-Flop: Synchronous VHDL CodeDocument6 paginiExperiment No. 2: Aim: A) D Flip-Flop: Synchronous VHDL CodeRahul MishraÎncă nu există evaluări

- New Text DocumentDocument3 paginiNew Text DocumentNaveen NegiÎncă nu există evaluări

- Decade CounterDocument3 paginiDecade CounterManohar thota100% (1)

- E Cad Lab ManualDocument51 paginiE Cad Lab ManualRajesh DoradlaÎncă nu există evaluări

- Sequential ExampleDocument11 paginiSequential ExampleAmit JadhavÎncă nu există evaluări

- Carrera de Ingeniería Electrónica Arquitectura de ComputadoresDocument25 paginiCarrera de Ingeniería Electrónica Arquitectura de ComputadoresNatalia PoloÎncă nu există evaluări

- For Each Question Use Template in Student Database System!!!Document4 paginiFor Each Question Use Template in Student Database System!!!Mehmethan Ayrım0% (1)

- Ecad Lab Manual PvpsitDocument53 paginiEcad Lab Manual PvpsitpriyankaveeramosuÎncă nu există evaluări

- Experiment No 3Document20 paginiExperiment No 3Ako C SeanÎncă nu există evaluări

- VHDL From BotrosDocument17 paginiVHDL From BotrossanjanaÎncă nu există evaluări

- Ejemplos VHDL Latch: Ieee Ieee STD - LOGIC - 1164Document6 paginiEjemplos VHDL Latch: Ieee Ieee STD - LOGIC - 1164MoriartyÎncă nu există evaluări

- Design Example 5.5Document10 paginiDesign Example 5.5MaheshÎncă nu există evaluări

- Dic File - 7 SemDocument22 paginiDic File - 7 SemShalini SharmaÎncă nu există evaluări

- Lecture 7Document27 paginiLecture 7rahulÎncă nu există evaluări

- Aplicaciones Spartan6 Ver1Document42 paginiAplicaciones Spartan6 Ver1juan mezaÎncă nu există evaluări

- Evl 104 Vlsi Design Lab-I: Ex - No:1 Modeling of Sequential Digital Systems Using VHDLDocument34 paginiEvl 104 Vlsi Design Lab-I: Ex - No:1 Modeling of Sequential Digital Systems Using VHDLvijithacvijayanÎncă nu există evaluări

- Tugas 3 Achmad Mauludin 165060301111002Document7 paginiTugas 3 Achmad Mauludin 165060301111002Mauudin BRgÎncă nu există evaluări

- Digital Lab Cs 6211 VHDL ProgramsDocument13 paginiDigital Lab Cs 6211 VHDL ProgramsMurugan GÎncă nu există evaluări

- VHDL in An HourDocument28 paginiVHDL in An HouranjugaduÎncă nu există evaluări

- Sequential Code: ProcessDocument10 paginiSequential Code: ProcessChutiyaÎncă nu există evaluări

- L10 Ex RegisterDocument36 paginiL10 Ex RegisterusitggsipuÎncă nu există evaluări

- DDCA Ch4 VHDLDocument35 paginiDDCA Ch4 VHDLYerhard Lalangui FernándezÎncă nu există evaluări

- VHDL SynthesisDocument16 paginiVHDL SynthesisNickos PopoviciÎncă nu există evaluări

- V HDL SampleDocument5 paginiV HDL Sampleppat2006Încă nu există evaluări

- Digital Circuits and Stystems: Lab FileDocument14 paginiDigital Circuits and Stystems: Lab FileAnurag AroraÎncă nu există evaluări

- Asynchronous Down Counter OBJECTIVE: To Design and Simulate The Asynchronous Down CounterDocument20 paginiAsynchronous Down Counter OBJECTIVE: To Design and Simulate The Asynchronous Down CounterKalagadda BikshaluÎncă nu există evaluări

- Lab 6Document4 paginiLab 6marwa abdelrazikÎncă nu există evaluări

- Programme No.10 AIM-To Design A D - Flip Flop CODE - Following Is The VHDL Code For Simulation of D Flip FlopDocument8 paginiProgramme No.10 AIM-To Design A D - Flip Flop CODE - Following Is The VHDL Code For Simulation of D Flip FlopAnkit GoelÎncă nu există evaluări

- VHDL Code For Updown CNTDocument3 paginiVHDL Code For Updown CNTmeaow88100% (2)

- VHDL PgmsDocument2 paginiVHDL Pgmsprabha_velÎncă nu există evaluări

- Lab 7 - COADocument3 paginiLab 7 - COAABHYANSH SHRIVASTAVAÎncă nu există evaluări

- A3 CA Fri Ankit Aman SudershanDocument16 paginiA3 CA Fri Ankit Aman SudershansrnankitÎncă nu există evaluări

- VHDL ProgramDocument5 paginiVHDL ProgramJaswanth TejaÎncă nu există evaluări

- Siddhi - E23cseu2200 - Assignment 8Document7 paginiSiddhi - E23cseu2200 - Assignment 8chipichipichapachapa2121Încă nu există evaluări

- VHDL Code For Parallel in Parallel Out Shift RegisterDocument4 paginiVHDL Code For Parallel in Parallel Out Shift RegisterPRITY KUMARI 20BEC0773Încă nu există evaluări

- VHDL For FPGA Design - 4-Bit Binary Counter With Parallel Load - Wikibooks, Open Books For An Open World PDFDocument5 paginiVHDL For FPGA Design - 4-Bit Binary Counter With Parallel Load - Wikibooks, Open Books For An Open World PDFpavani kutalaÎncă nu există evaluări

- VHDLDocument13 paginiVHDLSrijeeta SenÎncă nu există evaluări

- ASIC Va VHDL Toan TapDocument76 paginiASIC Va VHDL Toan TapCường VũÎncă nu există evaluări

- 4 Bit Counter With Test BenchDocument3 pagini4 Bit Counter With Test BenchJaya Balakrishnan100% (1)

- VHDL Code For 4-Bit Updown CounterDocument4 paginiVHDL Code For 4-Bit Updown CounterVinod ParabÎncă nu există evaluări

- DSD PPT Usr and CN and Odd DividerDocument22 paginiDSD PPT Usr and CN and Odd Dividerece19637ec003Încă nu există evaluări

- VHDL Programs LabDocument20 paginiVHDL Programs LabVasu SiriÎncă nu există evaluări

- VHDL Code For 4-Bit SisoDocument2 paginiVHDL Code For 4-Bit SisoAju JohnÎncă nu există evaluări

- Digital Integrated Circuits Lab: Practical FILEDocument55 paginiDigital Integrated Circuits Lab: Practical FILELakshayÎncă nu există evaluări

- Exp-6 20pec005Document8 paginiExp-6 20pec005ajay nareshÎncă nu există evaluări

- DSD Unit-5Document43 paginiDSD Unit-5R.c.Raghavendra ReddyÎncă nu există evaluări

- Chapter8 - VHDL - Sequential CircuitsDocument64 paginiChapter8 - VHDL - Sequential CircuitsRagheb IbrahimÎncă nu există evaluări

- Chapter9 - VHDL - Sequential Circuits - PracticeDocument37 paginiChapter9 - VHDL - Sequential Circuits - PracticeRagheb IbrahimÎncă nu există evaluări

- Chandigarh University, GharuanDocument5 paginiChandigarh University, GharuanAnkit KumarÎncă nu există evaluări

- Ieee Ieee STD - LOGIC - 1164: Library Use ALLDocument1 paginăIeee Ieee STD - LOGIC - 1164: Library Use ALLdineshvhavalÎncă nu există evaluări

- VHDL FileDocument25 paginiVHDL Filenitin_280890Încă nu există evaluări

- Example6.1: DFF With Asynchronous Reset #1Document7 paginiExample6.1: DFF With Asynchronous Reset #1ChutiyaÎncă nu există evaluări

- FSM Melay Using 1011Document3 paginiFSM Melay Using 1011dineshvhavalÎncă nu există evaluări

- VHDL 3 - Sequential Logic Circuits: Reference: Roth/John Text: Chapter 2Document29 paginiVHDL 3 - Sequential Logic Circuits: Reference: Roth/John Text: Chapter 2Soni NsitÎncă nu există evaluări

- Part 6Document5 paginiPart 6bmbsnpÎncă nu există evaluări

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.De la EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Încă nu există evaluări

- National Federation of RRB EmployeesDocument3 paginiNational Federation of RRB EmployeesSAKETSHOURAVÎncă nu există evaluări

- Regional Rural Bank (Employees') : Pension Scheme, 2018Document8 paginiRegional Rural Bank (Employees') : Pension Scheme, 2018SAKETSHOURAVÎncă nu există evaluări

- Certificate of RephasementDocument1 paginăCertificate of RephasementSAKETSHOURAVÎncă nu există evaluări

- All India Bank Employees' Association: "Prabhat Nivas"Document3 paginiAll India Bank Employees' Association: "Prabhat Nivas"SAKETSHOURAVÎncă nu există evaluări

- Judgment D.B. CIVIL SPECIAL APPEAL (W) NO.2021/2011Document11 paginiJudgment D.B. CIVIL SPECIAL APPEAL (W) NO.2021/2011SAKETSHOURAVÎncă nu există evaluări

- The Long March.: P. S. SundaresanDocument5 paginiThe Long March.: P. S. SundaresanSAKETSHOURAVÎncă nu există evaluări

- ,RDL-Q, QFR.&F: Baroda BankDocument9 pagini,RDL-Q, QFR.&F: Baroda BankSAKETSHOURAVÎncă nu există evaluări

- Ib Acio Ii 2013Document4 paginiIb Acio Ii 2013SAKETSHOURAVÎncă nu există evaluări

- Women Empowerment in IndiaDocument3 paginiWomen Empowerment in IndiaSAKETSHOURAVÎncă nu există evaluări

- PM Test Schedule 2017 PDFDocument2 paginiPM Test Schedule 2017 PDFSAKETSHOURAVÎncă nu există evaluări

- Final Result 53 To 55 CCEDocument7 paginiFinal Result 53 To 55 CCESAKETSHOURAVÎncă nu există evaluări

- Syllogism 2 1 PDFDocument3 paginiSyllogism 2 1 PDFSAKETSHOURAVÎncă nu există evaluări

- IDM 6.15 Serial KeysDocument1 paginăIDM 6.15 Serial KeysZheroelObedozaLaguitÎncă nu există evaluări

- Synchronous Positive Edge T FlipDocument12 paginiSynchronous Positive Edge T FlipSAKETSHOURAVÎncă nu există evaluări

- Admin: Mobile Showroom Management SystemDocument1 paginăAdmin: Mobile Showroom Management SystemSAKETSHOURAVÎncă nu există evaluări

- DFD 2Document1 paginăDFD 2SAKETSHOURAVÎncă nu există evaluări

- 1-5 2460 System Hub PDFDocument37 pagini1-5 2460 System Hub PDFLuigi SergiÎncă nu există evaluări

- Gaming - APP 5.0 ReleaseNoteDocument5 paginiGaming - APP 5.0 ReleaseNoteAlexutza BobeicaÎncă nu există evaluări

- Your PC Inside and OutDocument79 paginiYour PC Inside and OutRizny AmeenÎncă nu există evaluări

- Smart QuillDocument9 paginiSmart QuillSrini VasuluÎncă nu există evaluări

- iDS-7200HQHI-M2/FA SERIES Turbo Acusense DVR: Key FeatureDocument4 paginiiDS-7200HQHI-M2/FA SERIES Turbo Acusense DVR: Key FeatureMetalurgica VISILUÎncă nu există evaluări

- Datasheet Chip LCD Ili9341 PDFDocument245 paginiDatasheet Chip LCD Ili9341 PDFframqzÎncă nu există evaluări

- Release Note Qfle3f 1.0.68.0-1OEM.670.0.0.8169922Document22 paginiRelease Note Qfle3f 1.0.68.0-1OEM.670.0.0.8169922Tech On Demand Solution ProvidersÎncă nu există evaluări

- MCQ Unit 2Document3 paginiMCQ Unit 2Darshana KodamÎncă nu există evaluări

- Proxmox Cookbook - Sample ChapterDocument28 paginiProxmox Cookbook - Sample ChapterPackt Publishing0% (1)

- SF600 Specification V2.6Document24 paginiSF600 Specification V2.6L Vinoth LoganathanÎncă nu există evaluări

- Chapter!: 1.1 OverviewDocument2 paginiChapter!: 1.1 OverviewzahirsalehÎncă nu există evaluări

- H13-511 (154 Questions)Document44 paginiH13-511 (154 Questions)KashifBoota0% (1)

- Overview of RTOSDocument22 paginiOverview of RTOSveeramaniks408Încă nu există evaluări

- 0478 s19 QP 12 PDFDocument12 pagini0478 s19 QP 12 PDFSeif HeggyÎncă nu există evaluări

- Rainbow TechnologyDocument18 paginiRainbow Technologysaec08450100% (1)

- MPLAB Xpress Evaluation Board 7 - Segment DisplayDocument10 paginiMPLAB Xpress Evaluation Board 7 - Segment DisplaysivaÎncă nu există evaluări

- Ge Elect 2 ReviewerDocument6 paginiGe Elect 2 ReviewerReynalyn GalvezÎncă nu există evaluări

- Your Data of Sales File - 21june2020.xlsm 23-Jun-20 14-16-40Document10 paginiYour Data of Sales File - 21june2020.xlsm 23-Jun-20 14-16-40amitdesai92Încă nu există evaluări

- SQLDocument2 paginiSQLksenthil77Încă nu există evaluări

- CK5X Video Wall Controller User Manual-V1.3Document34 paginiCK5X Video Wall Controller User Manual-V1.3Cesar Cedano VivarÎncă nu există evaluări

- Scheme Toshiba A70 La 2301Document47 paginiScheme Toshiba A70 La 2301Жељко ГелићÎncă nu există evaluări

- Power On Self Test Beep CodesDocument5 paginiPower On Self Test Beep CodesTilak AmarghdeÎncă nu există evaluări

- E350 BrochureDocument2 paginiE350 BrochureSikandar ALiÎncă nu există evaluări

- MAXPRO® VMS Data SheetDocument4 paginiMAXPRO® VMS Data SheetjavaaidÎncă nu există evaluări

- Et STM32F103 PDFDocument25 paginiEt STM32F103 PDFabd01111100% (2)

- Wa0004.Document45 paginiWa0004.HIMANSHU DWIVEDIÎncă nu există evaluări

- HP Compaq Presario CQ62 FOXCONN Safina RevMVDocument40 paginiHP Compaq Presario CQ62 FOXCONN Safina RevMVLolitassAssÎncă nu există evaluări

- CP IpcDocument2 paginiCP IpcEko HBSÎncă nu există evaluări

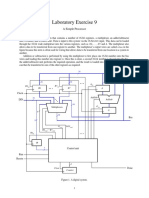

- Laboratory Exercise 9: A Simple ProcessorDocument8 paginiLaboratory Exercise 9: A Simple ProcessorhxchÎncă nu există evaluări

- CS305 Microprocessors and Microcontrollers PDFDocument2 paginiCS305 Microprocessors and Microcontrollers PDFlaraÎncă nu există evaluări