Documente Academic

Documente Profesional

Documente Cultură

Bicmos Inverter Upload

Încărcat de

HasanAlBannaBhuiyanDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Bicmos Inverter Upload

Încărcat de

HasanAlBannaBhuiyanDrepturi de autor:

Formate disponibile

Section-B

VLSI Circuit Design

Fall-2014-2015

BiCMOS INVERTER:

Made up of both Enhancement type Field Effect Transistor (MOSFET) and

T

na Fac aw

tio ul sif

na ty Ib

l U of ne

niv En Ala

er gin m

sit ee

y- rin

Ba g

ng

lad

es

(A

I

biasing resistors {collector, base and emitter} has been ignored for simplicity)

UB

)

Bipolar Junction Transistor (BJT) and hence the name BiCMOS. (The BJT

Circuit Diagram of a BiCMOS INVERTER

Characteristics of BiCMOS Inverter:

The output cannot go to VDD or Ground unlike for what we saw in the case of

In

te

r

CMOS inverter.

This lowers the noise margins of the logic.

The maximum output logic voltage is approximately VDD-0.7V.

The minimum output logic voltage is approximately 0.7V.

ica

The 0.7V drop for high and low logic comes from the base to emitter junction

Am

er

voltage drop of Q2 and Q1 Bipolar Junction Transistors.

Tawsif Ibne Alam

Faculty Engineering

American International University-Bangaldesh (AIUB)

Section-B

VLSI Circuit Design

Fall-2014-2015

Note: Caution should be exercised when working with the output of BiCMOS

gates with CMOS logic. The low output voltage of 0.7V is very close to the

UB

)

threshold voltage of the n-channel transistor. (CMOS gates with switching point

T

na Fac aw

tio ul sif

na ty Ib

l U of ne

niv En Ala

er gin m

sit ee

y- rin

Ba g

ng

lad

es

To understand the operation of the basic BiCMOS inverter;

Operating Principle:

(A

I

voltages close to the threshold voltages are susceptible to noise.)

Consider the case when the input is grounded.

Vin=0

MOSFETs M4 and M1 are in ON

state and M2 and M3 are in OFF

HIGH / 1

state.

M1 is ON due to the fact that the

static CMOS inverter output is

high. This results the base of the

LOW / 0

LOW / 0

Q1 to be at held at ground

potential

by

the

short

circuited FET, M1.

The HIGH output of the static

CMOS inverter is also holding the base of Q2 at VDD.

As a result of that Q1 is OFF and Q2 is ON, providing an output voltage

of VDD-0.7V across the load capacitor. (0.7V drop is occurring due to

Am

er

ica

In

te

r

the p-n junction voltage drop of Q2).

Tawsif Ibne Alam

Faculty Engineering

American International University-Bangaldesh (AIUB)

Section-B

VLSI Circuit Design

Fall-2014-2015

Now consider when the input is

UB

)

held @ VDD.

LOW / 0

Vin=VDD.

HIGH / 1

HIGH / 1

OFF state.

T

na Fac aw

tio ul sif

na ty Ib

l U of ne

niv En Ala

er gin m

sit ee

y- rin

Ba g

ng

lad

es

M1 is OFF due to the fact that

state while M4 and M1 are in

(A

I

MOSFETs M3 and M2 are in ON

the static CMOS inverter

output is LOW.

The LOW output of static

CMOS inverter is also holding the base of Q2 at a LOW potential,

turning Q2 OFF as well.

As M2 is ON, the base of Q1 is at a HIGH potential turning it ON,

shorting the output terminal to the ground. But due to the p-n

junction of the base-emitter in Q1, the output is held at 0.7V at pull

Am

er

ica

In

te

r

down condition.

Tawsif Ibne Alam

Faculty Engineering

American International University-Bangaldesh (AIUB)

S-ar putea să vă placă și

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Evaluare: 2.5 din 5 stele2.5/5 (3)

- L060 Push Pull (2UP)Document10 paginiL060 Push Pull (2UP)srikanthkmsÎncă nu există evaluări

- 2012 IEEE 0.6 V Class-AB CMOS Voltage Followe With Bulk-Driven Quasi Floating Gate Super Source FollowerDocument4 pagini2012 IEEE 0.6 V Class-AB CMOS Voltage Followe With Bulk-Driven Quasi Floating Gate Super Source FollowerMuhammad Sohail Asst. ProfessorÎncă nu există evaluări

- Analog Integrated Circuits & Technology (EC 305) : Differential Amplifier With Passive Load and Its Detail AnalysisDocument13 paginiAnalog Integrated Circuits & Technology (EC 305) : Differential Amplifier With Passive Load and Its Detail AnalysisAbir HoqueÎncă nu există evaluări

- Bicmos RabayeDocument19 paginiBicmos Rabayeapi-3704956Încă nu există evaluări

- Fna 41560 B 2Document16 paginiFna 41560 B 2JundiyahÎncă nu există evaluări

- MR2520 DatasheetDocument7 paginiMR2520 DatasheetOxkar YetiÎncă nu există evaluări

- Chap05 (7 5 06)Document60 paginiChap05 (7 5 06)Amar NathÎncă nu există evaluări

- Differential and Multistage AmplifiersDocument85 paginiDifferential and Multistage AmplifiersShino JosephÎncă nu există evaluări

- Nfva34065l32 D-2317928Document15 paginiNfva34065l32 D-2317928achil de troyÎncă nu există evaluări

- Ir2010 & (PBF) : High and Low Side Driver SDocument16 paginiIr2010 & (PBF) : High and Low Side Driver SManoel BonfimÎncă nu există evaluări

- 1 To 5 ManualDocument30 pagini1 To 5 ManualRoshan DodiyaÎncă nu există evaluări

- CYT1000B Specification: CYT Opto-Electronic Technology Co., LTDDocument10 paginiCYT1000B Specification: CYT Opto-Electronic Technology Co., LTDfacugomezÎncă nu există evaluări

- EC6404 UwDocument354 paginiEC6404 UwRamarao GudeÎncă nu există evaluări

- PresentationDocument44 paginiPresentationRohit chachdaÎncă nu există evaluări

- FSBF 15CH60BT F50Document17 paginiFSBF 15CH60BT F50José SilvaÎncă nu există evaluări

- FSBB30CH60CDocument17 paginiFSBB30CH60CSaul SalasÎncă nu există evaluări

- PUC EEE-311 Class-5Document14 paginiPUC EEE-311 Class-5Supreme FfÎncă nu există evaluări

- Unit 5Document6 paginiUnit 5Tarun SinghalÎncă nu există evaluări

- Inverter: Static CharacteristicsDocument57 paginiInverter: Static Characteristicsjkdas12Încă nu există evaluări

- Motion-SPM: Smart Power ModuleDocument15 paginiMotion-SPM: Smart Power ModuleAngel Suarez ZuñigaÎncă nu există evaluări

- Viper 12s Buck Boost ConverterDocument14 paginiViper 12s Buck Boost ConverterelkillyÎncă nu există evaluări

- Co-3 MaterialDocument35 paginiCo-3 MaterialMLM TELUGU GAMERSÎncă nu există evaluări

- 1008AE Specification: Specialty SummarizeDocument11 pagini1008AE Specification: Specialty Summarizenovram novÎncă nu există evaluări

- Ecler Pam2000 Pam2600 Power Amplifier Service ManualDocument107 paginiEcler Pam2000 Pam2600 Power Amplifier Service Manuallluissb92% (12)

- Design of Front-End Push-Pull Sine Wave Inverter: IOP Conference Series: Earth and Environmental ScienceDocument8 paginiDesign of Front-End Push-Pull Sine Wave Inverter: IOP Conference Series: Earth and Environmental SciencePABLO MAUROÎncă nu există evaluări

- HCPL-3150 (Single Channel), HCPL-315J (Dual Channel) : Data SheetDocument27 paginiHCPL-3150 (Single Channel), HCPL-315J (Dual Channel) : Data SheethaÎncă nu există evaluări

- CMOS Current Mirror With Enhanced Input Dynamic Range: Letter To The EditorDocument9 paginiCMOS Current Mirror With Enhanced Input Dynamic Range: Letter To The Editor15151516Încă nu există evaluări

- Analog Integrated Circuits & Technology (EC 305) : Differential Amplifier With Passive Load and Its Detail AnalysisDocument12 paginiAnalog Integrated Circuits & Technology (EC 305) : Differential Amplifier With Passive Load and Its Detail AnalysisAbir HoqueÎncă nu există evaluări

- MPM01 MPM04 Application NoteDocument16 paginiMPM01 MPM04 Application Noteprotek506Încă nu există evaluări

- FNB33060T: Motion SPM 3 SeriesDocument15 paginiFNB33060T: Motion SPM 3 Seriesphetronyo ferreira de oliveiraÎncă nu există evaluări

- BP5020 PDFDocument9 paginiBP5020 PDFCh Jameel SidhuÎncă nu există evaluări

- BicmosDocument22 paginiBicmosPrashant RamÎncă nu există evaluări

- Unit 1Document82 paginiUnit 1Shaleva SinghÎncă nu există evaluări

- ICMOSFETDocument96 paginiICMOSFETthamy_15Încă nu există evaluări

- FSBB20CH60: Smart Power ModuleDocument16 paginiFSBB20CH60: Smart Power ModuleDhaka AsasaÎncă nu există evaluări

- AN4102 (Uso 3S0680RF)Document20 paginiAN4102 (Uso 3S0680RF)Cintya CardozoÎncă nu există evaluări

- Design Principle Circuit Descripition: A) B) C) D) E) F) G) H) I)Document33 paginiDesign Principle Circuit Descripition: A) B) C) D) E) F) G) H) I)AJAY VISHNU M SÎncă nu există evaluări

- An3007 PDFDocument8 paginiAn3007 PDFJuan FelipeÎncă nu există evaluări

- Unit 4 - Fet Characteristics (2021!11!28 06-07-55 Utc)Document78 paginiUnit 4 - Fet Characteristics (2021!11!28 06-07-55 Utc)bachime13Încă nu există evaluări

- Ir2175 (S) & (PBF) : Linear Current Sensing IcDocument7 paginiIr2175 (S) & (PBF) : Linear Current Sensing IcDavid CoronadoÎncă nu există evaluări

- Function Generator With MAX038Document7 paginiFunction Generator With MAX038Laurentiu Iacob100% (1)

- Module 3 Course Material EDACDocument14 paginiModule 3 Course Material EDACNick WonkaÎncă nu există evaluări

- Linear ICDocument43 paginiLinear ICkaruppasamynagarajÎncă nu există evaluări

- Structure of Fast Power Diodes 49-53 - SemikronDocument7 paginiStructure of Fast Power Diodes 49-53 - SemikronPelotaDeTrapoÎncă nu există evaluări

- PE Lab Exp.4Document6 paginiPE Lab Exp.4sethyashis456Încă nu există evaluări

- CMOS Logic FamilyDocument6 paginiCMOS Logic FamilyAjay GeorgeÎncă nu există evaluări

- Safari 2016Document3 paginiSafari 2016Sai KishoreÎncă nu există evaluări

- Infineon-Application Note Applications For Depletion MOSFETs-AN-v01 00-ENDocument10 paginiInfineon-Application Note Applications For Depletion MOSFETs-AN-v01 00-ENvictorhugoseÎncă nu există evaluări

- Float DriveDocument24 paginiFloat DriveEdy AchalmaÎncă nu există evaluări

- New Low-Voltage Class ABDocument30 paginiNew Low-Voltage Class ABanjith2006Încă nu există evaluări

- Linear Current Sensing Ic: Product Summary FeaturesDocument6 paginiLinear Current Sensing Ic: Product Summary FeaturesBlackArnabÎncă nu există evaluări

- 2PD315 English V01Document10 pagini2PD315 English V01Narendra BholeÎncă nu există evaluări

- SSC9512SDocument2 paginiSSC9512SSamaro RodriguezÎncă nu există evaluări

- AN1585Document17 paginiAN1585DanÎncă nu există evaluări

- Power Supply Projects: A Collection of Innovative and Practical Design ProjectsDe la EverandPower Supply Projects: A Collection of Innovative and Practical Design ProjectsEvaluare: 3 din 5 stele3/5 (2)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Încă nu există evaluări

- Satellite Television Communication: Presented by Redwanul Hoque ID: 1010068Document12 paginiSatellite Television Communication: Presented by Redwanul Hoque ID: 1010068HasanAlBannaBhuiyanÎncă nu există evaluări

- Experiment Name: Top-Down Design of VLSI Circuits Using Verilog Hardware DescriptionDocument6 paginiExperiment Name: Top-Down Design of VLSI Circuits Using Verilog Hardware DescriptionHasanAlBannaBhuiyanÎncă nu există evaluări

- No 2 Power DissipationDocument28 paginiNo 2 Power DissipationHasanAlBannaBhuiyanÎncă nu există evaluări

- Vlsi Lab 8Document4 paginiVlsi Lab 8HasanAlBannaBhuiyanÎncă nu există evaluări

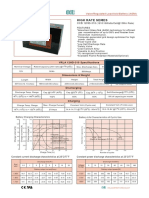

- High Rate Series: CCB 12HD-310Document1 paginăHigh Rate Series: CCB 12HD-310orunmila123Încă nu există evaluări

- SafeGrid Design ReportDocument11 paginiSafeGrid Design ReportkamilawehbeÎncă nu există evaluări

- Ni 9208Document24 paginiNi 9208Ricardo MayoralÎncă nu există evaluări

- Electronic Slot Car Controller Mysteries Revealed - JayGee RacingDocument13 paginiElectronic Slot Car Controller Mysteries Revealed - JayGee RacingBeen DeeÎncă nu există evaluări

- Epec 3606 Control Unit: Technical DocumentDocument49 paginiEpec 3606 Control Unit: Technical DocumentJoao SilvaÎncă nu există evaluări

- Slides 1, Power Electronics Circuits Devices and Applications 3ed Ed M H RashidDocument43 paginiSlides 1, Power Electronics Circuits Devices and Applications 3ed Ed M H Rashidjohnyrock07100% (2)

- 2010 Dodge Journey SXT 2010 Dodge Journey SXT: Circuit SchematicDocument32 pagini2010 Dodge Journey SXT 2010 Dodge Journey SXT: Circuit SchematicMAXIMILIANO CASTILLO ANTONIO100% (1)

- Viva-Voce Electrical MachinesDocument2 paginiViva-Voce Electrical MachinesjishnusajiÎncă nu există evaluări

- Aiml Bee Lab Manual I Yr II Sem 2023-24Document102 paginiAiml Bee Lab Manual I Yr II Sem 2023-24holagoogolÎncă nu există evaluări

- RS603MDocument3 paginiRS603Melkin_oviedoÎncă nu există evaluări

- Control IC For Single-Ended and Push-Pull Switched-Mode Power Supplies (SMPS) TDA 4700 TDA 4718Document21 paginiControl IC For Single-Ended and Push-Pull Switched-Mode Power Supplies (SMPS) TDA 4700 TDA 4718Wellison RodriguesÎncă nu există evaluări

- NPDCL New Connection Application FormDocument3 paginiNPDCL New Connection Application FormSangameshwar LabhishettyÎncă nu există evaluări

- High-Speed, High-Side MOSFET Driver With Charge Pump and Overcurrent LimitDocument24 paginiHigh-Speed, High-Side MOSFET Driver With Charge Pump and Overcurrent LimitiyanuÎncă nu există evaluări

- Em + EU R 10 EM + 7 0,025: QuestãoDocument6 paginiEm + EU R 10 EM + 7 0,025: QuestãoWilliam LeiteÎncă nu există evaluări

- Orca Share Media1535596930012Document64 paginiOrca Share Media1535596930012Julia Latawan LasilasÎncă nu există evaluări

- Electrical Experimenter - Nikola Tesla 1919 - 02Document84 paginiElectrical Experimenter - Nikola Tesla 1919 - 02Rafael Morris100% (1)

- ABB - 2CMA167801R1000 Datasheet 2023-03-06-151007Document4 paginiABB - 2CMA167801R1000 Datasheet 2023-03-06-151007Mohamed ShafeyÎncă nu există evaluări

- Final Year ProjectDocument52 paginiFinal Year ProjectMohamed A. HusseinÎncă nu există evaluări

- EC461 Microwave Devices and CircuitsDocument2 paginiEC461 Microwave Devices and Circuitsgodwinraj123Încă nu există evaluări

- Feedback Amplifiers Theory and DesignDocument279 paginiFeedback Amplifiers Theory and DesignImaginemeplayU100% (2)

- Model P4480 Kill A Watt Graphic Timer Operation Manual: Safety InstructionsDocument9 paginiModel P4480 Kill A Watt Graphic Timer Operation Manual: Safety Instructionspulse59Încă nu există evaluări

- Instruction Manual: DT-311A & DT-315A StroboscopeDocument4 paginiInstruction Manual: DT-311A & DT-315A StroboscopeAlejandro DallosÎncă nu există evaluări

- Lec 1Document17 paginiLec 1mezo4326Încă nu există evaluări

- Nikken's Magnets A BackgroundDocument3 paginiNikken's Magnets A BackgroundPeter John BellÎncă nu există evaluări

- Current Concepts in Electrical Stimulation Nov 2014Document5 paginiCurrent Concepts in Electrical Stimulation Nov 2014Israel FloresÎncă nu există evaluări

- Specification For Paging and Interconnection SystemDocument7 paginiSpecification For Paging and Interconnection SystemShibu ThomasÎncă nu există evaluări

- Radiated, RF Immunity TestDocument42 paginiRadiated, RF Immunity TestAmit SharmaÎncă nu există evaluări

- Sony D-E880, Ej815 Ver-1.0 SMDocument23 paginiSony D-E880, Ej815 Ver-1.0 SM朱子成Încă nu există evaluări

- D2300CPSDocument8 paginiD2300CPSSoham DeÎncă nu există evaluări

- Huawei Modular UPS Introduction 2020Document49 paginiHuawei Modular UPS Introduction 2020abdalla kamalÎncă nu există evaluări