Documente Academic

Documente Profesional

Documente Cultură

Surge Arrester Application of Mv-Capacitor Banks

Încărcat de

Fernando BravoDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Surge Arrester Application of Mv-Capacitor Banks

Încărcat de

Fernando BravoDrepturi de autor:

Formate disponibile

CIRED

19th International Conference on Electricity Distribution

Vienna, 21-24 May 2007

Paper 0639

SURGE ARRESTER APPLICATION OF MV-CAPACITOR BANKS TO MITIGATE

PROBLEMS OF SWITCHING RESTRIKES

Lutz GEBHARDT

ABB Switzerland

lutz.gebhardt@ch.abb.com

ABSTRACT

The paper presents the application of surge arresters as a

switching overvoltage protection of capacitor bank circuit

breakers. Based on an existing MV-Capacitor bank an

EMTP-Simulation is performed to show the effectiveness of

the surge arrester in reducing circuit breaker TRVs and in

minimizing the probability of circuit breaker restrikes.

The energy requirements of the surge arresters and the

overvoltage protection levels of the capacitors for different

surge arrester arrangements are calculated.

INTRODUCTION

Medium voltage capacitor banks are designed for industrial,

utility and commercial power systems to improve power

factor, increase system capacity, reduce harmonic distortion

and improve voltage regulation.

Capacitor bank switching is one of the most demanding

operations in MV networks, due to its associated transients.

During the opening operation the transient recovery voltage

(TRV) across the circuit breaker can rise to very high values

and that can initiate breaker restrikes which in turn generate

even higher overvoltages.

Consequently, any restrike implies additional stress for

capacitor and circuit breaker, which reduces their lifetime or

-in some extreme cases, if multiple restrikes occur- damages

the capacitor and circuit breaker immediately.

A way to prevent these overvoltages for new switchgears is

the installation of modern circuit breakers with a low

probability of restrike. For users, having old existing

switchgear not suitable for capacitor bank applications, the

question is whether the inserting of surge arresters across

the capacitor can minimize the probability of the circuit

breaker restrikes.

Based on a real existing installation of a MV-Capacitor

bank a study using the EMTP-RV Software was performed

in order to evaluate the effectiveness of the surge arrester

application in minimizing the probability of circuit breaker

restrikes.

Bernhard RICHTER

ABB Switzerland

bernhard.richter@ch.abb.com

an EMTP-Simulation for the opening operation of the

capacitor bank. A single-line diagram of the capacitor bank

is shown in Fig.1 with all the ratings marked therein. The

modelling is based on the following conditions:

The sequence of a three-phase break of capacitive load

followed by restrikes in two phases at t=8.3ms (1/2

cycle) after current interruption was identified as the

decisive case. The network with isolated neutral and a

power frequency of 60Hz was selected as the most

severe case

The circuit breaker interrupts the high frequency current

at the first current zero.

33kV, 60Hz

33/11kV

15MVA

Z=12%

Circuit

Breaker

11kV BUS

VC

1.5MVAR

CIRED2007 Session 1

Paper No 0639

Fig.1:

SA

SA

VC

1.5MVAR

1.5MVAR

C:

L:

VC

VC: Vacuum Contactor

F:

Fuse Link 180A

Capacitor 18.6uF

Detuning Reactor 15mH

SA

1.5MVAR

SA:

SA

Surge arrester POLIM-H07

Single line diagram of the capacitor bank

According Figure 2 three arrester arrangements are

investigated: phase to neutral, phase to phase and phase

to ground. The system neutral Rg was set to either zero

or infinite

As a surge arrester model a class 4 surge arrester type

with a fixed protection level of URES/UC = 2.9 (at IN =

10kA) is used

The magnitude of overvoltages is given in p.u. (per unit)

as a multiple of the peak value of the line-to-ground

voltage:

1p.u. =

1.5MVAR

MODELLING

Based on an existing installation of a 5-stage, 11kV,

7.5MVAR capacitor bank (ungrounded double wye connected), a 3-ph model of a MV-Capacitor bank

including the network components (capacitors, reactor,

circuit breaker, transformer) has been developed to perform

SA

VC

VC

2

11kVrms = 8.98kV

3

Page 1 / 4

CIRED

19th International Conference on Electricity Distribution

Vienna, 21-24 May 2007

Paper 0639

SW1a

Phase a

L3a

C4

L4a

ZnO1

SW1b

Phase b

L3b

C5

L4b

ZnO3

SW1c

ZnO2

Phase c

L3c

C6

L4c

POLIM-H

ZnO1

ZnO2

ZnO3

Rg

Fig.2:

Equivalent circuit with the arrester arrangments:

phase to ground, phase to neutral, phase to phase

DE-ENERGISATION OF CAPACITOR BANK

In order to evaluate the severity of overvoltages and to

determine the effectivness of a surge arrester application,

the step by step procedure was simulated for the following

cases:

1.

Three phase break of capacitive load

2.

Three phase break of capacitive load associated with

multiple breaker restrikes

3.

Three phase break of capacitive load associated with

multiple restrikes and using surge arresters

4.

Comparison of breaker TRVs and capacitor voltages

for the first pole-to-clear phase

1. Three phase break of capacitive load

Using the equivalent circuit according Fig.2 for a singlestage capacitor bank (S=1.5MVA) with no surge arrester

connected on the network the voltage and current

characteristics shown in Fig.3 are obtained. The first poleto-clear is phase b and the circuit breaker SW1 interrupts

the current in Phase b after t=11ms. From the moment the

current is interrupted, the charge of the capacitor is trapped

and the voltage remains constant at the value it had at zero

current. The recovery voltage across the circuit breaker for

the first pole to clear rises up to 2.5p.u.. This overvoltage is

the most severe voltage stress for the circuit breaker for all

investigated cases. As an assumption the circuit breaker is

able to withstand the voltage stress of 2.5p.u. without a

restrike.

CIRED2007 Session 1

Paper No 0639

Fig.3:

Three phase break of capacitive load

2. Three phase break of capacitive load associated

with multiple breaker restrikes

The same sequence is simulated as in case 1 but as an

assumption the circuit breaker is not able to withstand the

voltage stress of 2.5p.u. and a two phase restrike occurs at

the peak value of the recovery voltage at t=19.3ms in phase

b and c (Fig.4). A transient current with an oscillation

frequency determined by L3b/4b and C5 starts to flow and

the voltage across the capacitor C5 swings up to 3p.u. The

circuit breaker interrupts the current again at the first of its

current zeros, with the result that the voltage across the

capacitor C5 remains on the new constant value and voltage

across the circuit breaker SW1 in Phase b and c rises up to

3.7p.u. after t=28ms. In case of further restrikes

overvoltages will rise up to 6.1p.u. across the capacitors.

This process of voltage and current escalation will damage

the capacitor and breaker units

Page 2 / 4

CIRED

19th International Conference on Electricity Distribution

Vienna, 21-24 May 2007

Paper 0639

Fig.4:

Three phase break of capacitive load associated with multiple

breaker restrikes

3. Three phase break of capacitive load associated

with multiple breaker restrikes and using surge

arresters

The same sequence is simulated as in case 2 but using a

surge arrester arrangement phase to neutral. The obtained

voltage and current characteristics are shown in Fig.5. The

surge arrester limits the overvoltage across the capacitors

C5/6 at 1.9p.u.. In the case of multiple restrikes this

overvoltage level remains constant. A voltage escalation

across the capacitor and thus a capacitor failure is

prevented.

The transient recovery circuit breaker voltage across the

first pole-to-clear is limited at 2.1p.u. after the first restrike

and that mitigates the risk of further breaker restrikes. The

surge arrester not only protects the capacitor from

dangerous overvoltages but decreases the probability of

multiple restrikes of the breaker, too

CIRED2007 Session 1

Paper No 0639

Fig.5:

Three phase break of capacitive load associated with multiple

breaker restrikes and using a surge arrester phase to neutral

4. Comparison of breaker TRVs and capacitor

voltages for the first pole-to-clear phase

A detailed one-to-one comparison of the cases 2 and 3 for

the first pole-to-clear (Phase b) characteristic shows the

effectiveness of a surge arrester application (Fig.6). The

effect of the TRV-limitation across the capacitor and the

circuit breaker starts with the first restrike. There is no

voltage limitation during the opening operation without a

restrike. Therefore, the surge arrester can only reduce the

overvoltages if a restrike occurs. There is no benefit for the

circuit breaker to reduce the risk of a first restrike, but it

mitigates the risk of multiple restrikes.

Page 3 / 4

CIRED

19th International Conference on Electricity Distribution

Vienna, 21-24 May 2007

Paper 0639

has to taken into account.

PROTECTION CONSIDERATIONS

The voltages across the capacitor C5 of phase b for a singlestage capacitor bank is determined as a function of the three

phase capacitor size. The resulting voltages depending on

the arrester positioning are shown in Figure 8.

Without Arrester

With Arrester

3.5

3

Capacitor voltage C5 [p.u.]

Arrester Phase to Ground

2.5

Arrester Phase to Neutral

2

Arrester Phase to Phase

1.5

0.5

0

0

With Arrester

Fig.6:

Three phase capacitor bank size (MVAr)

Without Arrester

Fig.8:

Resulting capacitor voltages as a function of capacitor size

The same capacitor voltage is obtained for systems with

directly-grounded (Rg 0) as well as ungrounded neutral

(Rg ).

The effect of the number of parallel capacitor stages and the

number of repeated restrikes on the capacitor voltage is

negligible.

Comparison of breaker TRVs and capacitor voltages

ENERGY STRESS ON SURGE ARRESTER

The energy stresses on the surge arresters were calculated

for different arrester arrangements (Fig.2) and different

circuit parameters. The following results are obtained:

CONCLUSIONS

Energy stress as a function of the three phase capacitor

bank size

Based on the computer simulation of the capacitor bank deenergisation the following application considerations and

conclusions can be drawn:

A single-stage capacitor bank (Fig.1) is used to vary the

three-phase bank size in order to evaluate the effect on the

surge arrester energy stress.

400

Arrester energy ZnO2 [kJ]

350

300

Using a surge arrester prevents a capacitor failure at a

circuit breaker restrike by limiting the overvoltages

across the capacitors

Installation of a surge arrester mitigates the risk of

multiple restrikes by limiting the TRVs of the circuit

breaker

250

Arrester Phase to Phase

REFERENCES

200

Arrester Phase to Neutral

150

[1] Stenstrm L and Mobedjina M, April 1995,

"Guidelines for selection of surge arresters for shunt

capacitor banks", Electra, Vol. 159

Arrester Phase to Ground

100

50

0

0

Three phase capacitor bank size [MVAr]

Fig.7:

Energy stress as a function of capcitor bank size

(based on 3 successive restrikes)

Depending on the arrester arrangement, a linear increase of

the energy dissipated in the arrester is obtained.

The grounding conditions of the system neutral don`t effect

the energy stress on the surge arrester. Only in case of a

directly-grounded neutral (Rg 0) and an arrester

arrangement phase to ground a slightly higher energy of 7%

CIRED2007 Session 1

Paper No 0639

[2] ABB Publication, July 1999, "Dimensioning, testing

and application of metal oxide surge arresters in

medium voltage networks"

[3] Belanger J. and Menemenlis N., 1987, "Metal-oxide

arresters as switching overvoltage protection of

capacitor bank circuit breakers", Colloquium paper

CIGRE, SC 33 (Tokyo) 03.05.

Page 4 / 4

S-ar putea să vă placă și

- Inrush Restraint For Transformer Differential Protection With Current Waveform Analysis (Cwa) in Siprotec 4 7UT6xDocument10 paginiInrush Restraint For Transformer Differential Protection With Current Waveform Analysis (Cwa) in Siprotec 4 7UT6xsandeepmalik22Încă nu există evaluări

- 33kV - Cap - Bank-SIKAP - Spec - FY 12-13 - 30.11.11-Cesc - 20 MVARDocument9 pagini33kV - Cap - Bank-SIKAP - Spec - FY 12-13 - 30.11.11-Cesc - 20 MVARSatyajit RaiÎncă nu există evaluări

- STATCOM SpecificationDocument77 paginiSTATCOM SpecificationYinwu ZhaoÎncă nu există evaluări

- Insulation Coordination Studies and Selection of Lightning Arrester For 765kV SwitchyardDocument5 paginiInsulation Coordination Studies and Selection of Lightning Arrester For 765kV SwitchyardAnonymous BBX2E87aHÎncă nu există evaluări

- Power Line Parameters ExplainedDocument11 paginiPower Line Parameters ExplainedkamuikÎncă nu există evaluări

- Commercial Application of Arc Horns For Arc Current InterruptionDocument4 paginiCommercial Application of Arc Horns For Arc Current InterruptionramsesiÎncă nu există evaluări

- On The Problem of Shunt Reactor Tripping During Singl and Three Phase Auto ReclosingDocument6 paginiOn The Problem of Shunt Reactor Tripping During Singl and Three Phase Auto ReclosingCarlos Lino Rojas AgüeroÎncă nu există evaluări

- Technical Paper - M.Hassan Ejaz - Switching Transient of EHV Shunt ReactorDocument12 paginiTechnical Paper - M.Hassan Ejaz - Switching Transient of EHV Shunt ReactorHassan EjazÎncă nu există evaluări

- Back Up Impedance ProtectionDocument3 paginiBack Up Impedance ProtectionNeelakandan MasilamaniÎncă nu există evaluări

- In A of Of: Failure Transformer of LevelsDocument9 paginiIn A of Of: Failure Transformer of Levelseeng8124Încă nu există evaluări

- 7pg21 Solkor R RF Catalogue SheetDocument26 pagini7pg21 Solkor R RF Catalogue SheetsmcraftÎncă nu există evaluări

- Ferroresonance VT Gis v002Document4 paginiFerroresonance VT Gis v002qais652002Încă nu există evaluări

- Busbar Protection TheoryDocument13 paginiBusbar Protection TheoryDEADMANÎncă nu există evaluări

- Shunt Reactor Switching Transients at High Compensation LevelsDocument14 paginiShunt Reactor Switching Transients at High Compensation LevelsJames Ernes Llacza Carmelo100% (1)

- Interposing Current Transformers: For Use in Conjunction With Type MBCH Transformer Differential ProtectionDocument12 paginiInterposing Current Transformers: For Use in Conjunction With Type MBCH Transformer Differential ProtectionChristopher Mouly100% (1)

- Sinkrotakt Manual 5Document39 paginiSinkrotakt Manual 5Vlado RadojsolicÎncă nu există evaluări

- Ferroresonance Team PresentationDocument21 paginiFerroresonance Team PresentationPratik Ranjan100% (1)

- Arrestor Energy Calculation PDFDocument6 paginiArrestor Energy Calculation PDFpartha_gang4526Încă nu există evaluări

- Typical Surge Arrester VI Characteristic Plotting Excel WorkbookDocument12 paginiTypical Surge Arrester VI Characteristic Plotting Excel Workbookhey_frindÎncă nu există evaluări

- DC Time Constant EstimationDocument6 paginiDC Time Constant Estimationrasheed313Încă nu există evaluări

- Evaluation Methods of Limiting Switching Overvoltage During Line EnergizationDocument6 paginiEvaluation Methods of Limiting Switching Overvoltage During Line EnergizationInternational Journal of Science and Engineering InvestigationsÎncă nu există evaluări

- Backup To Busbar Protection With Numerical Distance ProtectionDocument4 paginiBackup To Busbar Protection With Numerical Distance ProtectionTran Cong ThanhÎncă nu există evaluări

- Energising Inrush Current Transients in Parallel-Connected TransformersDocument5 paginiEnergising Inrush Current Transients in Parallel-Connected TransformersagusraposobustoÎncă nu există evaluări

- Non Optimum Compensation Schemes For Single Pole Reclosing On EHV Double Circuit TLDocument9 paginiNon Optimum Compensation Schemes For Single Pole Reclosing On EHV Double Circuit TLCarlos Lino Rojas AgüeroÎncă nu există evaluări

- Short Circuit StudyDocument45 paginiShort Circuit Studymohamad arifinÎncă nu există evaluări

- Optimize Earth Fault Protection with Core Balance Current TransformersDocument3 paginiOptimize Earth Fault Protection with Core Balance Current Transformersதுரைராஜ் இலட்சுமணன்Încă nu există evaluări

- Transients in Power SystemDocument10 paginiTransients in Power SystemMATHANKUMAR.SÎncă nu există evaluări

- Power System Protection - Part 08Document16 paginiPower System Protection - Part 08Rahul MandalÎncă nu există evaluări

- What Is BIL and How Does It Apply To TransformersDocument4 paginiWhat Is BIL and How Does It Apply To TransformersAmitabhaÎncă nu există evaluări

- Switchyard Equipments & Functions: Atar SinghDocument43 paginiSwitchyard Equipments & Functions: Atar SinghbijoyÎncă nu există evaluări

- DWT-based fault detection and classification for TEED transmission systemsDocument7 paginiDWT-based fault detection and classification for TEED transmission systemsRaguramanÎncă nu există evaluări

- A Comprehensive Guide To Voltage Transformer VT Circuit Supervision TechniquesDocument24 paginiA Comprehensive Guide To Voltage Transformer VT Circuit Supervision Techniquesorgil.snoopyÎncă nu există evaluări

- Translay Commissioning Rail CorpDocument9 paginiTranslay Commissioning Rail CorpsmcraftÎncă nu există evaluări

- Negative Phase Sequence ProtectionDocument15 paginiNegative Phase Sequence ProtectionThirumalÎncă nu există evaluări

- Test Circuit ParametersDocument5 paginiTest Circuit ParametersSamsudin Ahmad100% (1)

- Metrosil Relays Datasheet PDFDocument4 paginiMetrosil Relays Datasheet PDFBaskaran Gangatharan100% (1)

- Study of Relay Protection Modeling and SimulationDocument5 paginiStudy of Relay Protection Modeling and SimulationИван ИвановÎncă nu există evaluări

- Ztr290 Testing of MCSRDocument10 paginiZtr290 Testing of MCSRFernando Lud van MeizÎncă nu există evaluări

- CT Class Very ImportantDocument6 paginiCT Class Very ImportantEngr Fahimuddin QureshiÎncă nu există evaluări

- 7kg6000 Transducer SpecificationDocument8 pagini7kg6000 Transducer SpecificationwiyatnoÎncă nu există evaluări

- Black Box Transformer ModelingDocument5 paginiBlack Box Transformer ModelingdankorankoÎncă nu există evaluări

- Floating Neutral Impact in Power DistributionDocument9 paginiFloating Neutral Impact in Power DistributionSugeng SumarnoÎncă nu există evaluări

- High Voltage Busbar ProtectionDocument45 paginiHigh Voltage Busbar ProtectionabhinavksauravÎncă nu există evaluări

- Resistance Earthed Systems: Fault CurrentsDocument25 paginiResistance Earthed Systems: Fault CurrentsRameez Ahmed100% (1)

- Cho Pap PDFDocument27 paginiCho Pap PDFrexÎncă nu există evaluări

- 7sd52 7sd62 ConfigurationDocument14 pagini7sd52 7sd62 ConfigurationWilber LucasÎncă nu există evaluări

- SPAJ 115c ManualDocument56 paginiSPAJ 115c ManualPatel AshokÎncă nu există evaluări

- Transient Analysis of Shunt Reactor SwitchingDocument4 paginiTransient Analysis of Shunt Reactor SwitchingnicesreekanthÎncă nu există evaluări

- Knowledge is "Real Power": Introduction to Power QualityDe la EverandKnowledge is "Real Power": Introduction to Power QualityÎncă nu există evaluări

- The Technology of Instrument Transformers: Current and Voltage Measurement and Insulation SystemsDe la EverandThe Technology of Instrument Transformers: Current and Voltage Measurement and Insulation SystemsÎncă nu există evaluări

- Real-Time Simulation Technology for Modern Power ElectronicsDe la EverandReal-Time Simulation Technology for Modern Power ElectronicsÎncă nu există evaluări

- Capacitor Bank Switching With Vacuum Circuit Breakers - Schneider Electric PDFDocument5 paginiCapacitor Bank Switching With Vacuum Circuit Breakers - Schneider Electric PDFpitambervermaÎncă nu există evaluări

- Vacuum Circuit Breaker Model PDFDocument6 paginiVacuum Circuit Breaker Model PDFGovernmentHookerÎncă nu există evaluări

- Mitigation of The Transient Recovery Voltage On Generator Circuit Breaker During Generator Fed FaultsDocument4 paginiMitigation of The Transient Recovery Voltage On Generator Circuit Breaker During Generator Fed FaultsryreddyÎncă nu există evaluări

- Current-Limiting Inductors' Impact on Fault InterruptionDocument7 paginiCurrent-Limiting Inductors' Impact on Fault Interruptionjm7632Încă nu există evaluări

- Surge Arrester Application of MV-capacitor Banks TDocument5 paginiSurge Arrester Application of MV-capacitor Banks Tap_venezuela100% (1)

- Generator GroundDocument5 paginiGenerator Groundanjes1Încă nu există evaluări

- Vacuum Contactor Switching Phenomena PDFDocument9 paginiVacuum Contactor Switching Phenomena PDFjulianvillajosÎncă nu există evaluări

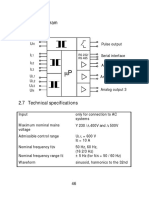

- Panelview 5510 Terminals Specifications: Technical DataDocument12 paginiPanelview 5510 Terminals Specifications: Technical DataFernando BravoÎncă nu există evaluări

- Cutout Templates For Panelview 5510 Terminals: 6.5-In. Touch Only 184 MM (7.24 In.)Document2 paginiCutout Templates For Panelview 5510 Terminals: 6.5-In. Touch Only 184 MM (7.24 In.)Fernando BravoÎncă nu există evaluări

- Technical Specifications: This Section Provides Technical Specifications For The Panelview 5510 TerminalsDocument2 paginiTechnical Specifications: This Section Provides Technical Specifications For The Panelview 5510 TerminalsFernando BravoÎncă nu există evaluări

- Panelview 5510 Terminals: User ManualDocument116 paginiPanelview 5510 Terminals: User ManualFernando BravoÎncă nu există evaluări

- MTU Dizel Generatori - Pregled Po SnagamaDocument23 paginiMTU Dizel Generatori - Pregled Po SnagamaFernando BravoÎncă nu există evaluări

- Panelview 5510 Terminals Specifications: Technical DataDocument12 paginiPanelview 5510 Terminals Specifications: Technical DataFernando BravoÎncă nu există evaluări

- Cutout Templates For Panelview 5510 Terminals: 6.5-In. Touch Only 184 MM (7.24 In.)Document2 paginiCutout Templates For Panelview 5510 Terminals: 6.5-In. Touch Only 184 MM (7.24 In.)Fernando BravoÎncă nu există evaluări

- Panelview 5000 Portfolio of Graphic Terminals: Featuring Studio 5000 View Designer SoftwareDocument6 paginiPanelview 5000 Portfolio of Graphic Terminals: Featuring Studio 5000 View Designer SoftwareFernando BravoÎncă nu există evaluări

- Panelview 5510 Terminals Specifications: Technical DataDocument12 paginiPanelview 5510 Terminals Specifications: Technical DataFernando BravoÎncă nu există evaluări

- White Paper - Systems Approach For LightingDocument6 paginiWhite Paper - Systems Approach For LightingFernando BravoÎncă nu există evaluări

- Work Breakdown Structures: White PaperDocument6 paginiWork Breakdown Structures: White PaperjmpbarrosÎncă nu există evaluări

- Study PMBOK EnoughDocument13 paginiStudy PMBOK EnoughFernando BravoÎncă nu există evaluări

- Arc Flash Hazard Analysis and Mitigation PaperDocument20 paginiArc Flash Hazard Analysis and Mitigation PapergjanitoÎncă nu există evaluări

- CBRM MV SwitchgearDocument6 paginiCBRM MV SwitchgearAleihs AyadneÎncă nu există evaluări

- Predictive Maintenance For MV SystemsDocument3 paginiPredictive Maintenance For MV SystemsFernando BravoÎncă nu există evaluări

- Electrical Installation Requirements for Hazardous & Explosives AreasDocument34 paginiElectrical Installation Requirements for Hazardous & Explosives AreasmacodarvÎncă nu există evaluări

- Ieee - C37.2-2008Document1 paginăIeee - C37.2-2008DANIEL3991Încă nu există evaluări

- VHP 7042GSI MaintenanceDocument4 paginiVHP 7042GSI MaintenanceFernando Bravo100% (2)

- 4055 EFX Quick Compliance Guide BookletDocument12 pagini4055 EFX Quick Compliance Guide BookletFernando BravoÎncă nu există evaluări

- Ansi Relay FunctionsDocument1 paginăAnsi Relay FunctionsJitendra PatilÎncă nu există evaluări

- What Is MaintenanceDocument4 paginiWhat Is MaintenanceAnman NomanÎncă nu există evaluări

- Gas Engines Oils TechPaperDocument15 paginiGas Engines Oils TechPaperZamani Mahdi100% (1)

- 50 HZ MH Series: Horizontal Multi-Stage PumpsDocument20 pagini50 HZ MH Series: Horizontal Multi-Stage PumpsJuan Pablo Moreno100% (1)

- RRB JE Syllabus OfficialDocument10 paginiRRB JE Syllabus OfficialSt.josephs MatricÎncă nu există evaluări

- ElectricidadDocument69 paginiElectricidadraul jean meza puchocÎncă nu există evaluări

- PHD Tesis ZarriDocument228 paginiPHD Tesis ZarriperathuselvanÎncă nu există evaluări

- Direct Power Control of PWM Converter Without Power Source VoltaDocument6 paginiDirect Power Control of PWM Converter Without Power Source Voltabalaji mendiÎncă nu există evaluări

- Group 7 Group Assignment Electrical InstallationDocument31 paginiGroup 7 Group Assignment Electrical InstallationLaras Dwi SenliÎncă nu există evaluări

- UCM274FDocument8 paginiUCM274F3efooÎncă nu există evaluări

- Altivars & Soft Starters - enDocument28 paginiAltivars & Soft Starters - enBudy AndikaÎncă nu există evaluări

- Motor Thermal ModelDocument15 paginiMotor Thermal ModelnagarajasarmaÎncă nu există evaluări

- Measuring and Monitoring Relays - ABBDocument76 paginiMeasuring and Monitoring Relays - ABBpevareÎncă nu există evaluări

- UCM224D - Technical Data SheetDocument8 paginiUCM224D - Technical Data Sheet3efooÎncă nu există evaluări

- EEP305 Electric Drives Laboratory PDFDocument14 paginiEEP305 Electric Drives Laboratory PDFAmit Singh100% (1)

- Transformer Kit 1Document2 paginiTransformer Kit 1Rachit KhannaÎncă nu există evaluări

- MSLC2 1,.5 ManualDocument220 paginiMSLC2 1,.5 ManualJosué Miranda da SilvaÎncă nu există evaluări

- Directional Overcurrent Relay Concepts ReviewDocument14 paginiDirectional Overcurrent Relay Concepts Reviewykh92167Încă nu există evaluări

- Active Power FilterDocument49 paginiActive Power FilterJawad Iqbal100% (1)

- Floating Neutral Impacts in Power DistributionDocument8 paginiFloating Neutral Impacts in Power DistributionMouna NjÎncă nu există evaluări

- PS 1Document37 paginiPS 1Aatif AltafÎncă nu există evaluări

- Chapter 2 - TransformersDocument25 paginiChapter 2 - TransformersYousab CreatorÎncă nu există evaluări

- Model Exam - PSGDocument2 paginiModel Exam - PSGthangalakshmiprakashÎncă nu există evaluări

- J1000 basic inverter V/f control and specificationsDocument12 paginiJ1000 basic inverter V/f control and specificationsVarga LászlóÎncă nu există evaluări

- Chamber Furnaces - High Temperature (HTC)Document16 paginiChamber Furnaces - High Temperature (HTC)Pembela KebenaranÎncă nu există evaluări

- 2CSG445010D0201 - M2M Basic - ENDocument46 pagini2CSG445010D0201 - M2M Basic - ENUlisesÎncă nu există evaluări

- GROUP-3 THREE Phase Star DeltaDocument19 paginiGROUP-3 THREE Phase Star Deltamanikanta2235789Încă nu există evaluări

- Measurement of Electrical PowerDocument2 paginiMeasurement of Electrical Powerasalasv65Încă nu există evaluări

- Clarke and Park TransfomationDocument9 paginiClarke and Park TransfomationGREATJUSTGREATÎncă nu există evaluări

- Rental: SolutionsDocument12 paginiRental: SolutionsKyle HorwarthÎncă nu există evaluări

- Sampa 1Document15 paginiSampa 1Manjula Udayanga HemapalaÎncă nu există evaluări

- Poly Phase Multifunction Energy Metering IC With Per Phase Information ADE7758Document68 paginiPoly Phase Multifunction Energy Metering IC With Per Phase Information ADE7758Kien TranÎncă nu există evaluări

- Eaton EGR 5000 Generation Protection Relay Tech DataDocument24 paginiEaton EGR 5000 Generation Protection Relay Tech DatatafseerahmedÎncă nu există evaluări