Documente Academic

Documente Profesional

Documente Cultură

Analog Electronic Circuits (ELE 209) RCS (Makeup)

Încărcat de

phdpushTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Analog Electronic Circuits (ELE 209) RCS (Makeup)

Încărcat de

phdpushDrepturi de autor:

Formate disponibile

Department of Electrical and Electronics Engineering

Reg. No. :

MANIPAL INSTITUTE OF TECHNOLOGY, MANIPAL

(A Constituent Institute of Manipal University, Manipal)

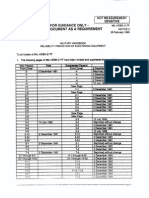

THIRD SEMESTER B.E. DEGREE MAKEUP EXAMINATION

(REVISED CREDIT SYSTEM)

08 January 2011

ANALOG ELECTRONIC CIRCUITS (ELE 209)

Time: 3 hours

Note

Max. Marks: 50

: Answer any FIVE full questions. Refer Table-1 for h-parameters.

1A

1B

1C

Write a note on construction and applications of schottky diode.

(02)

Plot the Vi, V0 with respect to time and transfer characteristics, for the circuit shown in Fig 1(B).

(03)

For the zener diode voltage regulator shown in fig 1(C) determine VL, VR, IZ ,PZ, power dissipation

in R=1K series resistance and the safe maximum input voltage that can be applied.

(05)

2A

Determine the current source current I to obtain an output voltage V0=2V in the circuit shown in

Fig 2A. Assume all the diodes are identical and =1,VT=26mV and Is=

A

(02)

Determine IBQ, ICQ, VCEQ, VCQ for the amplifier shown in fig 2(B) .Assume VBE=0.7V.

(04)

Plot the output voltage in the circuit shown in the Fig 2C for vi=10sin . Assume all diodes are

ideal diodes.

(04)

2B

2C

3A

3B

3C

4A

4B

4C

Calculate the DC component and ripple in the output signal across RL in the circuit shown in

Fig 3A. Assume V1dc=150V, V1RMS=15V and f=50HZ.

(03)

With the help of neat sketch explain the different current components of a BJT.

(03)

Using approximate h parameter circuit determine the current gain AI, Voltage gain AV and input

resistance Ri of voltage follower circuit shown in Fig 3C.

(04)

Determine VGS1, V1 and V

identical with Vt=1V,

for the MOSFET amplifier shown in Fig 4A. Both the MOSFET are

=2mA/V2. Neglect the channel length modulation effect.

(03)

With the help of neat circuit diagram explain the working of MOSFET based current mirror circuit. (03)

Draw the equivalent small signal circuit of the MOSFET amplifier shown in Fig 4C. Hence

determine the input resistance, output resistance and voltage gain. Assume

=0.25mA/V2,

Vt=1.5V and neglect channel length modulation effect.

5A

5B

5C

6A

6B

6C

(04)

With the help of neat circuit diagram explain the CMOS inverter

(02)

With the help of neat sketch derive an expression for conversion efficiency and maximum

efficiency of Class B Push pull amplifier.

(03)

A power amplifier of class A type with transformer coupling delivers a maximum of 20W to 4 ohm

load resistance. The Q point is adjusted for symmetrical clipping assuming fixed bias and VCC=20V.

Find i.) Turns ratio of transformer ii.) Slopes of AC and DC load line

iii.) Quiescent points

iv.) efficiency

(05)

Determine the VCE, output voltage output power and Zener Diode current for the circuit shown in

Fig 6A given = 100,VBE=0.7V.

(03)

From the fundamental derive an expression for the lower cut-off frequency of the amplifier due to

coupling capacitors.

(04)

Design a adujstable voltage regulato using LM317 regulator to get output voltage between 10 and

18V. Assume R1=1K,Vref=1.25V and Iadj=100 . Hence draw the circuit diagram.

(03)

Page 1 of 2

Department of Electrical and Electronics Engineering

V= 8 V

Vi

R=1K

C=1 0 F

I

10V

D1

10m s

V0

1K

D2

20m s

20V

R L= 3K

VZ = 10V

D1

2K

P ZM = 80mW

-10V

V0

D2

F ig 1 (C )

F ig 1 ( B)

D3

F ig Q 2 A

15V

4.5K

V1

120K

VL

R 1=5 0 0

Vi

500

B r idge

R e c t if ie r

50 F

R L=5K

=72

C 2= 1 5

10 F

F ull wa v e

A C in p u t

V0

10 F

10 F

C 1= 1 5

85K

F ig 3 A

F ig 2 ( B)

I= 1m A

12V

+ 15V

56K

1G

VGS 1

5K

c=

V1

ID = 2 m A

R L= 10K

c=

v0

36K

V2

1K

+

5V

_

1mA

vi

6.6K

V0

vi

F ig 4 C

5V

+

F ig . 3 C

F ig . 4 A .

Vi = 1 5 V

2 k

2 k

8V

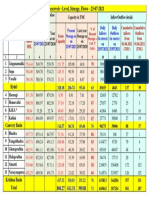

h- parameters

hi

hr

hf

h0

CE

1.1K

2.510-4

50

24mho

CB

1.1K

1

-51

25mho

CC

21.6 ohms

2.910-4

-0.98

0.49mho

Fig 6A

Page 2 of 2

S-ar putea să vă placă și

- Essence of Brahma Sutras PDFDocument335 paginiEssence of Brahma Sutras PDF23bhagaÎncă nu există evaluări

- Udupi Bengaluru: 9:35 PM 5:55 AMDocument2 paginiUdupi Bengaluru: 9:35 PM 5:55 AMphdpushÎncă nu există evaluări

- 8.corruption Prevention Measures Recommended by Kautilya: Dr. Priti PohekarDocument7 pagini8.corruption Prevention Measures Recommended by Kautilya: Dr. Priti PohekarPraveenMukatiÎncă nu există evaluări

- Fact Sheet For Vaccine Recipients & Caregivers: Restricted Use in Emergency Situation of Covid-19Document1 paginăFact Sheet For Vaccine Recipients & Caregivers: Restricted Use in Emergency Situation of Covid-19nehaalluriÎncă nu există evaluări

- 8.corruption Prevention Measures Recommended by Kautilya: Dr. Priti PohekarDocument7 pagini8.corruption Prevention Measures Recommended by Kautilya: Dr. Priti PohekarPraveenMukatiÎncă nu există evaluări

- 8.corruption Prevention Measures Recommended by Kautilya: Dr. Priti PohekarDocument7 pagini8.corruption Prevention Measures Recommended by Kautilya: Dr. Priti PohekarPraveenMukatiÎncă nu există evaluări

- Shrimadhawacharya: SRI C. KESAVA RAO, Bangalore Courtesy:Parimala Cultural MagazineDocument3 paginiShrimadhawacharya: SRI C. KESAVA RAO, Bangalore Courtesy:Parimala Cultural MagazinephdpushÎncă nu există evaluări

- Udaka Shanti - SanskritDocument111 paginiUdaka Shanti - SanskritsubrajuÎncă nu există evaluări

- Major Reservoir - Level, Storage, Flows - 25-07-2021Document1 paginăMajor Reservoir - Level, Storage, Flows - 25-07-2021phdpushÎncă nu există evaluări

- Vimanas - King Ravana Ancient Flying Matchiens (V)Document6 paginiVimanas - King Ravana Ancient Flying Matchiens (V)Mohan Perera90% (10)

- Sage VikhanasacharyaDocument2 paginiSage VikhanasacharyaphdpushÎncă nu există evaluări

- BE AssignmentDocument15 paginiBE AssignmentphdpushÎncă nu există evaluări

- PANCARATRA PradipaDocument262 paginiPANCARATRA PradipaHari Sukrawan100% (7)

- Ambhrini Sukta Part2Document2 paginiAmbhrini Sukta Part2phdpushÎncă nu există evaluări

- Mahanarayana Upanishad - With Translation PDFDocument382 paginiMahanarayana Upanishad - With Translation PDFphdpush100% (4)

- Shanti Japam KannadaDocument168 paginiShanti Japam KannadaphdpushÎncă nu există evaluări

- Angirasa SmritiDocument6 paginiAngirasa SmritiKarthikeyan RamaswamyÎncă nu există evaluări

- Narayana Upanishad PDFDocument9 paginiNarayana Upanishad PDFJeans Circuits80% (5)

- Shanti Japam KannadaDocument168 paginiShanti Japam KannadaphdpushÎncă nu există evaluări

- Narayana Upanishad PDFDocument9 paginiNarayana Upanishad PDFJeans Circuits80% (5)

- ASEE 13 Full Paper Final Submission PDFDocument7 paginiASEE 13 Full Paper Final Submission PDFphdpushÎncă nu există evaluări

- Tangents & Normal RDSADocument22 paginiTangents & Normal RDSAphdpushÎncă nu există evaluări

- Mahanarayana Upanishad - Swami Vimalananda (Sanskrit-English) C PDFDocument382 paginiMahanarayana Upanishad - Swami Vimalananda (Sanskrit-English) C PDFphdpush100% (1)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (120)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- Microbiol Incubators 6000 ImlabDocument11 paginiMicrobiol Incubators 6000 ImlabTatit Aji WijayaÎncă nu există evaluări

- Fundamental, Technology and Manufacturing in Indonesia: HV Power TransformerDocument82 paginiFundamental, Technology and Manufacturing in Indonesia: HV Power TransformerAriÎncă nu există evaluări

- Final Year Project Report EditedDocument31 paginiFinal Year Project Report Editedvijaya karthegha.RÎncă nu există evaluări

- st-200 ProDocument132 paginist-200 ProAndres TapiaÎncă nu există evaluări

- Circuito Integrado TA8207KDocument11 paginiCircuito Integrado TA8207KIberê CamposÎncă nu există evaluări

- 5124 Science (Physics and Chemistry)Document4 pagini5124 Science (Physics and Chemistry)mstudy123456Încă nu există evaluări

- 07 Eldor SodaDocument9 pagini07 Eldor SodaDeepthiÎncă nu există evaluări

- LNCTGroup Data Login IDs - For DisplayDocument18 paginiLNCTGroup Data Login IDs - For DisplaySiddharth NagayachÎncă nu există evaluări

- GOOLOO GE1200 - User ManualDocument1 paginăGOOLOO GE1200 - User ManualzoltanpolyakÎncă nu există evaluări

- GCS VCSEL DO188 - VCSEL Datasheet Preliminary Ver. 2Document2 paginiGCS VCSEL DO188 - VCSEL Datasheet Preliminary Ver. 2bobÎncă nu există evaluări

- Instructional MaterialsDocument50 paginiInstructional Materialsanir100% (1)

- TVSS (Transient Voltage Surge Suppression) What Is It and Why All of A Sudden Do We Need It?Document12 paginiTVSS (Transient Voltage Surge Suppression) What Is It and Why All of A Sudden Do We Need It?Jecer Casipong NuruddinÎncă nu există evaluări

- Product End of Life Instructions: Mixed I/O Module, With Mixed Technologies (Analog, Digital and Hart)Document3 paginiProduct End of Life Instructions: Mixed I/O Module, With Mixed Technologies (Analog, Digital and Hart)Mohd JannahÎncă nu există evaluări

- Gekko DSDocument2 paginiGekko DSAnte NekicÎncă nu există evaluări

- Military HandbookDocument80 paginiMilitary HandbookLuthfyatma HardyÎncă nu există evaluări

- Ampeg SVT450H SchematicDocument3 paginiAmpeg SVT450H SchematicJuanGuajardoÎncă nu există evaluări

- Presentasi MultimeterDocument41 paginiPresentasi MultimetermdÎncă nu există evaluări

- HBM P3 Top ClassDocument10 paginiHBM P3 Top ClasslgustavolucaÎncă nu există evaluări

- Argus LCX: Convenient Vital Data Patient MonitoringDocument4 paginiArgus LCX: Convenient Vital Data Patient MonitoringAzhari DasrilÎncă nu există evaluări

- How Satellite TV WorksDocument6 paginiHow Satellite TV WorksAlpesh ThesiyaÎncă nu există evaluări

- Pressure Controller Application Guide: ModelDocument2 paginiPressure Controller Application Guide: ModelSIVAM81Încă nu există evaluări

- COA 2013 Application and SyllabusDocument7 paginiCOA 2013 Application and SyllabusLohanathan VkÎncă nu există evaluări

- A2 38+thermal+modellingDocument57 paginiA2 38+thermal+modellingblem_0075Încă nu există evaluări

- PHYSICS Test No. 10 Chapter. 14, 16 - KEYDocument2 paginiPHYSICS Test No. 10 Chapter. 14, 16 - KEYAhmed SaudÎncă nu există evaluări

- Xcortech XT301 Compact Airsoft Tracer Unit Manual: Setup ProcessDocument3 paginiXcortech XT301 Compact Airsoft Tracer Unit Manual: Setup ProcessrobertoÎncă nu există evaluări

- Deep Bar and Double Cage 010223Document20 paginiDeep Bar and Double Cage 010223Debankan ChatterjeeÎncă nu există evaluări

- Renoise User ManualDocument244 paginiRenoise User ManualStephen DaviesÎncă nu există evaluări

- Evaluating Potential Failures of Power Transformer Using Failure Mode and Effects Analysis (Fmea)Document6 paginiEvaluating Potential Failures of Power Transformer Using Failure Mode and Effects Analysis (Fmea)Dante FilhoÎncă nu există evaluări

- Mesa Boogie Mark II-BDocument10 paginiMesa Boogie Mark II-BscheisshandyÎncă nu există evaluări

- Solution Manual For Principles and AppliDocument64 paginiSolution Manual For Principles and AppliWellin Sambo100% (1)