Documente Academic

Documente Profesional

Documente Cultură

1373697227-2. Electronics - IJECE - Real Time - Manthan S. Manavadaria PDF

Încărcat de

Vishal TankDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

1373697227-2. Electronics - IJECE - Real Time - Manthan S. Manavadaria PDF

Încărcat de

Vishal TankDrepturi de autor:

Formate disponibile

International Journal of Electronics and

Communication Engineering (IJECE)

ISSN 2278-9901

Vol. 2, Issue 3, July 2013, 7-12

IASET

REAL TIME IMPLEMENTATION AND VERIFICATION OF EBERS-MOLL MODEL

MANTHAN S. MANAVADARIA1 & VISHAL P. TANK2

1

Research Scholar, Electronics & Communication Department, CSPIT-Changa, Gujarat, India

Assistant Professor, Electronics & Communication Department, CSPIT-Changa, Gujarat, India

ABSTRACT

Todays in any electronic circuit diode and transistor are essential components. It is too much difficult to design or

implement a circuit without these two silicon made devices. From the point of fabrication and atomic structure, diode is

single junction component whereas transistor is double junction. As per this simple construction a normal though can arise

from any human mind, why a transistor cannot make by simply connecting two diodes? The answer for this question is

very well explained by Ebers Moll model in theoretical way. By this article we have tried to demonstrate the same concept

practically. By performing various experiments like i/p-o/p characteristics, DC-AC analysis, etc. for both, one is single

transistor and later one is two back to back diode combinations, it is easy to answer mentioned question.

KEYWORDS: Ebers Moll Model, Diode 1N4007, Transistor BC547, Saturation Condition

INTRODUCTION

In Figure 1 we see the Ebers Moll model for pn-p transistor. It involves two ideal diodes placed back to back

with reverse saturation current IEO and - ICO and two dependent current controlled sources shunting the ideal diodes.

Figure 1: The Ebers-Moll Model for PNP Transistor

Let us see the equations of Ic and IE from Ebers moll model. Applying KCL to the collector node, we get

N I E IC 1

IC I N I E

I C N I E I O (eVC / VT 1)

IO I CO

I C N I E I CO (eVC / VT )

The general expression for collector current IC of a transistor for any voltage across collector junction Vc and

emitter current IE is

Manthan S. Manavadaria & Vishal P. Tank

Figure 2: The Ebers-Moll Model for PNP Transistor

I C N I N I CO (eVC / VT 1)

Here, subscript N to indicates that we are using transistor in a normal manner. When we interchange the role of

emitter and collector we operate transistor in a inverted function. In such case current and junction voltage relationship for

transistor is given by

I E I I C I EO (eVE / VT 1)

Here, subscript I to indicates that we are using transistor in a inverted manner, I is the inverted common base

current Gain.

IEO The emitter junction reverse saturation current.

VE The voltage drop from p side to N side at the emitter junction.

Similarly applying KCL to emitter node we get

I E I IC I

I E I I IC

I E I I C IO (eVE / VT 1)

I C I I C I EO (eVC / VT )

This model is valid for both forward & reverse static voltages applied across the transistor junction. In the above

model, by making the base width much large than the diffusion length of minority carriers in the base, all mining carriers

will recombine in the base and none will survive to reach the collector [1].

IMPLEMENTATION

For this research paper two different circuits have been implemented practically on the bread board, one is for

transistor and second is for back to back diodes. During implementation Transistor BC547 (NPN) and diode (1N4007) has

been used. Initially we have started with DC analysis and then AC analysis also carried out.

In table 1 the dc analysis of transistor has been shown. We have shown i/p and o/p characteristics. During analysis

the saturation point has been highlighted.

Real Time Implementation and Verification of Ebers-Moll Model

Table 1: Transistor Characteristics Analysis at Vcc=5V

Vbb

(Volts)

0

1

2

3

4

5

6

I/P Characteristics

Vbe (Volts) Ib(mA)

0

0

0.76

1.349

0.82

7.3

0.84

14.2

0.87

22.1

0.88

28.9

0.90

38.5

O/P Characteristics

Vce (Volts) Ic(mA)

0

0

0.02

4.8

0.02

4.8

0.03

4.8

0.03

4.8

0.04

4.8

0.04

4.8

Table 2: Diode Characteristics Analysis at Vcc=5V

Vbb

(Volts)

0

1

2

3

4

5

6

I/P Characteristics

Vbe (Volts) Ib(mA)

0

0

0.61

2.7

0.66

8.7

0.70

17.3

0.72

28.2

0.73

36.2

0.74

46

O/P Characteristics

Vce (Volts) Ic(mA)

0

0

4.98

0

4.98

0

4.98

0

4.98

0

4.98

0

4.98

0

Table 3: Diode Characteristics Analysis at Vcc=5V

Vbb

(Volts)

0

1

2

3

4

5

6

I/P Characteristics

Vbe (Volts) Ib(mA)

0

0

0.27

4.8

0.63

9.4

0.68

17.5

0.71

26.8

0.72

36.4

0.73

46

O/P Characteristics

Vce (Volts) Ic(mA)

0

0

-0.07

4.7

-0.11

4.9

-0.13

4.9

-0.15

4.9

-0.16

4.9

-0.18

4.9

In table no.2 two back to back diode circuit analysis carried out with vcc=5v and vcc=-5v. in figure 1 we have

compare the characteristics graphically.

Figure 3: Input Characteristics Comparison for Transistor and Back to Back Diode

10

Manthan S. Manavadaria & Vishal P. Tank

Figure 4: DSO O/P for Back to Back Diode Case Input Character

Figure 5: DSO O/P for Transistor Case

In Figure 4 and Figure 5 AC analysis has been shown by using DSO 5025-A. In figure 4 it has been clearly shown

that we are getting phase shift in transistor case but in Figure 5 we are not getting any type of result in back to back diode

scenario.

CONCLUSIONS

As per the Ebers moll mode condition, transistor action ceases, and we simply have two diodes placed back to

back diodes. The result of DC analysis clearly indicates th difference between characteristics of a transistor and back to

back diodes combination. Not only in the DC analysis but by observing waveform result for AC analysis we can

differentiate both the cases. Therefore it is impossible to construct a transistor by simply connecting two separate diodes

back to back. Simply,

Transistor Diode + Diode

Real Time Implementation and Verification of Ebers-Moll Model

11

REFERENCES

1.

Jacob millman, christos C. Halkias, Electronic devices & Circuits Tata McGraw hill ISBN 0-07-462243-9

pp.247-249

2.

Debhasish De, Electronic devices & Circuits Pearson ISBN 978-81-317-1068-5 pp.201-202

3.

Juan M. Lopez, Dave M. Keogh, Peter M. Asbeck, An Ebers-Moll model for Heteostructure bipolar

transistors with tunnel junctions ,IEEEv. ISBN-0-7803-7478-, vol. 2, no. 1, pp. 240-244, Month, 2002.

4.

Kuntman, H. , Application of modified Ebers Loll model to non linera distortion analysis of transistor

amplifiers, IEEE Trans Elctronics letters, ISSN 0013- 5194, vol. 19, no. 1, pp. 126127, Feb. 1983.

AUTHORS DETAILS

Manthan S. Manavadaria has obtained his master degree in Communication System Engineering, from

CHARUSAT-Changa, Gujarat, INDIA. And bachelor degree in EC field from DDU, Nadiad, Gujarat. Currently he is

working as an Research scholar and Assi.Prof. in E.C.Dept. in CHARUSAT- Changa , Gujarat, India. His main interested

areas are Bioelectronics and Networking

Vishal P. Tank has obtained his master degree in Communication System Engineering, from L.D. college of

Engineering, Gujarat, INDIA. And bachelor degree in EC field from DDU, Nadiad, Gujarat. Currently he is working as an

Assi.Prof. in E.C.Dept. in CHARUSAT- Changa, Gujarat, India. His main interested areas are DSP and Networking

S-ar putea să vă placă și

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Analog vs Digital TransmissionDocument5 paginiAnalog vs Digital TransmissionVishal TankÎncă nu există evaluări

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (587)

- API Score GuidelineDocument9 paginiAPI Score GuidelineVishal TankÎncă nu există evaluări

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (894)

- Govt Exam Previous Year Model Question Papers With Answer Key PDF 09Document31 paginiGovt Exam Previous Year Model Question Papers With Answer Key PDF 09NagarajuRaginaboyinaÎncă nu există evaluări

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- All All: CLC Clear CloseDocument1 paginăAll All: CLC Clear CloseVishal TankÎncă nu există evaluări

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- Advt 25oct2013 1Document5 paginiAdvt 25oct2013 1Vishal TankÎncă nu există evaluări

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (73)

- Settings For UetfwwDocument2 paginiSettings For UetfwwVishal TankÎncă nu există evaluări

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- Revision For UPS (Physics Matriculation)Document6 paginiRevision For UPS (Physics Matriculation)Erina PhantomhiveÎncă nu există evaluări

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Rosendal1943 SkinDocument22 paginiRosendal1943 SkinEdwin CallejasÎncă nu există evaluări

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

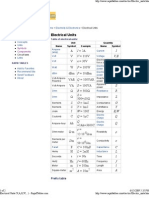

- Electrical Units Guide (V, A, Ω, WDocument2 paginiElectrical Units Guide (V, A, Ω, Wevtoma100% (1)

- Led Matrix DisplayDocument14 paginiLed Matrix DisplayAkshay KaushikÎncă nu există evaluări

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Renewable Energy: How Photovoltaic Modules and Arrays WorkDocument33 paginiRenewable Energy: How Photovoltaic Modules and Arrays Workcharbel jabbourÎncă nu există evaluări

- Trouble Shooting-Diagram Tank Level Measuring system-EL-TDocument5 paginiTrouble Shooting-Diagram Tank Level Measuring system-EL-TEtl OdessaÎncă nu există evaluări

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- BS 4533-102.1-1990, en 60598-2-1-1989Document12 paginiBS 4533-102.1-1990, en 60598-2-1-1989sumanÎncă nu există evaluări

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- Measurement and Simulation of Grounding Resistance With Two and Four Mesh GridsDocument6 paginiMeasurement and Simulation of Grounding Resistance With Two and Four Mesh GridscphcricriÎncă nu există evaluări

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2219)

- NTMP2014 1Document1 paginăNTMP2014 1HannOtto StoreÎncă nu există evaluări

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- Pinza Scully - 67206 - Desc PDFDocument2 paginiPinza Scully - 67206 - Desc PDFYilhennys RegaladoÎncă nu există evaluări

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- WF101GTYAPLNG0Document7 paginiWF101GTYAPLNG0Jorge ArijaÎncă nu există evaluări

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (265)

- QuickSilver Controls QCI-DS019 QCI-D2-IGDocument13 paginiQuickSilver Controls QCI-DS019 QCI-D2-IGElectromateÎncă nu există evaluări

- 800kVGIS Spec Rev1Document51 pagini800kVGIS Spec Rev1JayadevDamodaranÎncă nu există evaluări

- Cable Accessories GuideDocument2 paginiCable Accessories Guideeleon07Încă nu există evaluări

- FBR211 Miniature Relay Data SheetDocument6 paginiFBR211 Miniature Relay Data SheetSaikat HasanÎncă nu există evaluări

- DYNC-10202 & DYNC-10502 linear actuatorsDocument4 paginiDYNC-10202 & DYNC-10502 linear actuatorsAsif MehmoodÎncă nu există evaluări

- Tank Gauge Servicemanual Ed2 308012enDocument154 paginiTank Gauge Servicemanual Ed2 308012enRam KumarÎncă nu există evaluări

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- Durosite Series Led High Bay: For Industrial & Commercial ApplicationsDocument8 paginiDurosite Series Led High Bay: For Industrial & Commercial ApplicationsTiagohowpy RamosÎncă nu există evaluări

- Catalogo INGESCO ENGDocument32 paginiCatalogo INGESCO ENGBogdan MondocÎncă nu există evaluări

- Blowers: Blower Motors, Wheels & FansDocument27 paginiBlowers: Blower Motors, Wheels & FansAndrey GyrychÎncă nu există evaluări

- Saw Filter (Siemens)Document350 paginiSaw Filter (Siemens)Luiz059100% (1)

- Lab 3 TheveninDocument2 paginiLab 3 TheveninLê MinhÎncă nu există evaluări

- Ammeter N VoltmeterDocument56 paginiAmmeter N VoltmeterPrerna AgrawalÎncă nu există evaluări

- BS Standard For Cable LayingDocument2 paginiBS Standard For Cable Layingmurali50% (2)

- Nac ExtenderDocument8 paginiNac ExtenderharrisonaqpÎncă nu există evaluări

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (119)

- Power Electronics - Chapter 4 - Rectifiers AnalysisDocument40 paginiPower Electronics - Chapter 4 - Rectifiers Analysiskennedy kipsangÎncă nu există evaluări

- BL2000 Elevator Control System Wiring DiagramDocument28 paginiBL2000 Elevator Control System Wiring DiagramAnderley Quintero100% (1)

- Using The Power MOSFET As A SwitchDocument5 paginiUsing The Power MOSFET As A SwitchNgoc Nguyen HaÎncă nu există evaluări

- Arnu07gm1a4.Encbleu Listeb de PiecesDocument2 paginiArnu07gm1a4.Encbleu Listeb de PiecesDimitris ThanasopoulosÎncă nu există evaluări

- UPS-MR Data SheetDocument8 paginiUPS-MR Data SheetLast Juan StandingÎncă nu există evaluări

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)