Documente Academic

Documente Profesional

Documente Cultură

Jerarquía Digital Plesiócrona - Wikipedia, La Enciclopedia Libre

Încărcat de

JosHerreraDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Jerarquía Digital Plesiócrona - Wikipedia, La Enciclopedia Libre

Încărcat de

JosHerreraDrepturi de autor:

Formate disponibile

13/9/2014

Jerarqua digital plesicrona - Wikipedia, la enciclopedia libre

Jerarqua digital plesicrona

De Wikipedia, la enciclopedia libre

La jerarqua digital plesicrona1 abreviada como PDH, del ingls Plesiochronous Digital Hierarchy1 es

una tecnologa usada en telecomunicacin tradicionalmente para telefona que permite enviar varios canales

telefnicos sobre un mismo medio (ya sea cable coaxial, radio o microondas) usando tcnicas de multiplexacin

por divisin de tiempo y equipos digitales de transmisin. Tambin puede enviarse sobre fibra ptica, aunque no

est diseado para ello y a veces se suele usar en este caso SDH Sinchronous Digital Hierarchy.

La jerarqua usada en

Latinoamrica es la misma

de Europa que agrupa

30+2 canales de 64Kb/s

para obtener 2048 kbit/s

(E1). Luego multiplexado

por 4 sucesivamente se

obtiene jerarquas de nivel

superior

con

las

velocidades de 8 Mbit/s

(E2), 34 Mbit/s (E3) y

139 Mbit/s (E4).

Fig. 1 Niveles de PDH

ndice

1 Introduccin

2 Principios de entramado y multiplexacin PDH

3 Jerarquas europea (E1), norteamericana (T1) y japonesa (J1)

4 Jerarqua Europea (E1)

4.1 Canal de Administracin TS0

4.2 Proceso de alineamiento de trama

4.3 Canal de Sealizacin TS16

5 rdenes jerrquicos superiores (E2,E3,E4)

5.1 Nivel jerrquico E2

http://es.wikipedia.org/wiki/Jerarqu%C3%ADa_digital_plesi%C3%B3crona

1/10

13/9/2014

Jerarqua digital plesicrona - Wikipedia, la enciclopedia libre

5.1 Nivel jerrquico E2

5.2 rdenes jerrquicossuperiores

6 Propiedades fsicas y elctricas

6.1 Interfaces de Conexin

6.2 Interfaces elctricas

7 Codificacin

8 Deteccin de errores y alarmas

8.1 Deteccin de errores

8.2 Alarmas PDH

8.2.1 Prdida de trama (LOS)

8.2.2 Seal indicadora de alarma (AIS)

8.2.3 Remote Defect Indication (RDI)

9 Limitaciones de PDH

10 Vase tambin

11 Referencias

12 Enlaces externos

Introduccin

El trmino plesicrono se deriva del griego plesio, cercano y chronos, tiempo, y se refiere al hecho de que las

redes PDH funcionan en un estado donde las diferentes partes de la red estn casi, pero no completamente

sincronizadas. La tecnologa PDH, por ello, permite la transmisin de flujos de datos que, nominalmente, estn

funcionando a la misma velocidad (bit rate), pero permitiendo una cierta variacin alrededor de la velocidad

nominal gracias a la forma en la que se construyen las tramas. Un ejemplo clarifica el concepto: Tenemos dos

relojes que, nominalmente, funcionan a la misma velocidad, sealando 60 segundos cada minuto. Sin embargo, al

no existir enlace alguno entre los dos relojes que garantice que ambos van exactamente a la misma velocidad, es

muy probable que uno de ellos vaya ligeramente ms rpido que el otro.

Principios de entramado y multiplexacin PDH

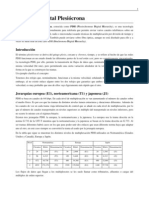

En el sistema europeo, se tiene hasta cinco jerarquas, como se puede observar en la siguiente tabla.

Jerarqua

Velocidad

Canales

Trama

E1

2048 Kbit/s

30

256 bits = 125 us

E2

8448 Kbit/s

120

848 bits = 100.38 us

E3

34368 Kbit/s 480

1536 bits = 44,7 us

E4

139268 Kbit/s 1920

2904 bits = 20.85 us

E5

564992 Kbit/s 7680

2688 bits = 4.7 us

Un equipo multiplicador digital recibe un nmero N de seales numricas, llamadas tributarios, que se presentan a

su entrada en paralelo y produciendo una seal digital de mayor velocidad de informacin como mnimo N veces

superior a la de los tributarios.

http://es.wikipedia.org/wiki/Jerarqu%C3%ADa_digital_plesi%C3%B3crona

2/10

13/9/2014

Jerarqua digital plesicrona - Wikipedia, la enciclopedia libre

fm >= N ft

fm = frecuencia mltiplo.

ft = frecuencia de tributario.

Los tributarios de entrada debern estar en fase y en igualdad de frecuencia entre s, pero en realidad no es as sino

que tienen distinta fase entre s y variacin de las frecuencias.

ft< = ft ft

fm = fm fm

A cada seal tributaria se le aaden unos bits que se llaman de relleno o de justificacin, y unos bits que se llaman

de control de justificacin, para que el extremo receptor pueda distinguir los bits que son de informacin y los que

son de relleno. Este proceso es conocido como justificacin, y tiene por objeto absorber las ligeras diferencias de

frecuencia que pueden presentar los distintos tributarios, ya que pueden haberse constituido con fuentes de reloj

diferentes. De esta forma, a los tributarios ms lentos es necesario aadirles ms bits de relleno que a los tributarios

ms rpidos. En el extremo receptor, los bits de relleno son oportunamente reconocidos y cancelados gracias a la

informacin que transportan consigo los bits de control de la justificacin. En consecuencia, la velocidad de la seal

agregada es mayor que la suma de las velocidades de las seales tributarias.

fm > N ft ---> fm = (N ft) + fr

fr = frecuencia de los bits de redundancia.

Jerarquas europea (E1), norteamericana (T1) y japonesa (J1)

PDH se basa en canales de 64 kbps. En cada nivel de multiplexacin se van aumentando el nmero de canales

sobre el medio fsico. Es por eso que las tramas de distintos niveles tienen estructuras y duraciones diferentes.

Adems de los canales de voz en cada trama viaja informacin de control que se aade en cada nivel de

multiplexacin, por lo que el nmero de canales transportados en niveles superiores es mltiplo del transportado en

niveles inferiores, pero no ocurre lo mismo con el rgimen binario.

Existen tres jerarquas PDH: la europea, la norteamericana y la japonesa. La europea usa la trama descrita en la

norma G.732 de la UIT-T mientras que la norteamericana y la japonesa se basan en la trama descrita en G.733. Al

ser tramas diferentes habr casos en los que para poder unir dos enlaces que usan diferente norma haya que

adaptar uno al otro, en este caso siempre se convertir la trama al usado por la jerarqua europea.

En la tabla que sigue se muestran los distintos niveles de multiplexacin PDH utilizados en Norteamrica (Estados

Unidos y Canad), Europa y Japn.

Nivel

Norteamrica

Europa

Japn

Circuitos kbit/s

Denominacin Circuitos kbit/s

Denominacin Circuitos kbit/s

Denominacin

24

1544

(T1)

30

2048

(E1)

24

1544

(J1)

96

6312

(T2)

120

8448

(E2)

96

6312

(J2)

672

44 736 (T3)

480

34 368 (E3)

480

32 064 (J3)

4032

274 176 (T4)

1920

139 264 (E4)

1440

97 728 (J4)

http://es.wikipedia.org/wiki/Jerarqu%C3%ADa_digital_plesi%C3%B3crona

3/10

13/9/2014

Jerarqua digital plesicrona - Wikipedia, la enciclopedia libre

Los flujos de datos que llegan a los multiplexores se les suele llamar como tributarios, afluentes o cargas del

mltiplex de orden superior la mayora de las veces.

Jerarqua Europea (E1)

- Definida por el sistema G.732 del CCITT

Define

un

conjunto de 32

slots de tiempo de

8 bits, cada uno a

una velocidad de

64 kbit/s.

- Slot 0 y slot 16

reservados para

administracin y

sealizacin del

canal, esto se

puede ver en la

Fig. 2

- Cada trama

tiene una duracin

de 125 us.

- Los primeros 8

bits (TS0) de

cada trama es un

Fig. 2 Estructura de Multitrama E1

encabezado H, el

cual lleva

el

protocolo G.704.

- Los otros 248 bits pueden ser usados para la transmisin de datos. (datos de usuario), tienen una tasa de bits

disponible de 1984 kbit/s 31*64 kbit/s.

- La ley de codificacin utilizada es la ley A (alaw) especificada en la Recomendacin G.711 que proporciona un

flujo de datos de 64 kbit/s. G.711 es un estndar para representar seales de audio con frecuencias de la voz

humana, con 256 niveles de cuantizacin y una tasa de muestreo de 8000 muestras por segundo.

- Se permite una variacin, alrededor de la velocidad exacta de 2,048 Mbit/s, de 50 ppm (partes por milln). Esto significa que dos flujos diferentes de 2 megas pueden estar funcionando a velocidades ligeramente diferentes

uno de otro.

Canal de Administracin TS0

- Contiene los bits del encabezado de G.704.

- Se utiliza para enviar:

Sincronizacin

Alineamiento de trama (FAS)

Informacin de supervisin del enlace.

http://es.wikipedia.org/wiki/Jerarqu%C3%ADa_digital_plesi%C3%B3crona

4/10

13/9/2014

Jerarqua digital plesicrona - Wikipedia, la enciclopedia libre

Indicador

de

alarma remota

Verificacin

de

Redundancia cclica

(CRC)

Proceso

alineamiento

trama

de

de

Fig. 3 FAS (Palabra de alineacin de trama)

- El alineamiento de la trama consiste en 10 bits que permiten el sincronismo del receptor.

- Cuando se detectan con error 4 palabras consecutivas se produce la perdida el alineamiento de trama LOF; para

recuperar el alineamiento de la trama se deben leer correctamente 3 palabras consecutivas.

- En tanto dura la falta de alineamiento, la seal de los tributarios se remplaza por una seal de indicacin de alarma

AIS consistente en una secuencia de bits 1.

Canal de Sealizacin TS16

Existen dos formas genricas de enviar la sealizacin de los canales de telefona en el multiplexor E1:

1. Sealizacin por Canal Asociado (CAS): Es una sealizacin que requiere la disponibilidad de un canal

exclusivo para tareas de sealizacin. Define los protocolos que deben establecerse entre usuarios para los

siguientes casos:

Cuando el usuario levanta el telfono.

Cuando uno de los usuarios empieza a marcar el nmero.

Cuando el usuario llama, etc.

1. Sealizacin por Canal Comn CCS o SSNo7: Es un conjunto de protocolos de sealizacin telefnica

empleado en la mayor parte de redes telefnicas mundiales. Su principal propsito es el establecimiento y

finalizacin de llamadas, no requiere la disposicin de un canal exclusivo, liberando el TS16 en el caso del

E1.

rdenes jerrquicos superiores (E2,E3,E4)

Nivel jerrquico E2

El nivel E2 generalmente es llamado G.742.

El uso de este orden fue en un principio para caminos digitales entre pases.

La tasa de bit nominal debe ser de 8448 kbit/s.

La trama consiste en 848 bits, 4 subtramas de 212 bit. Cada subtrama se divide en 53 grupos de 4 bits.

Tiene 206 bits por cada tributario (E1) y se puede apreciar en la Fig. 4.

Entrelaza 4 tributarios de distinta velocidad (funcionamiento plesicrono) dentro de la tolerancia de 50 ppm,

asignando a cada afluente una capacidad levemente superior a la real y rellenar el exceso con bits de

justificacin (stuffing ) que se eliminan en el proceso de demultiplexacin.

http://es.wikipedia.org/wiki/Jerarqu%C3%ADa_digital_plesi%C3%B3crona

5/10

13/9/2014

Jerarqua digital plesicrona - Wikipedia, la enciclopedia libre

Entrelazado de 4 afluentes de entrada cuya velocidad puede no ser exactamente igual (funcionamiento

plesicrono) requiere entonces de la aplicacin del proceso de Justificacin Positiva. El mismo consiste en

asignar a cada afluente una capacidad levemente superior a la real y rellenar el exceso con bits de

justificacin que se eliminan en el proceso de demultiplexacin.

rdenes jerrquicossuperiores

El tercer y cuarto orden

jerrquico

son

una

extensin del segundo

orden, debido a la similitud

de tramas.

Se disponen de palabras de

alineamiento de trama al

inicio de cada organizacin

de iguales caractersticas.

Se cuenta con una alarma

para informar al terminal

remoto de la falta de

alineamiento local.

En resumen:

Equipo Mltiplex digital

Fig. 4 Estructura de trama PDH a 8448 kbit/s

plesicrono de 2/8 Mbit/s:

Equipo que en transmisin

combina 4 seales tributarias a 2,048 Mbit/s, de forma que a la salida se obtiene una seal mltiplex de

8,448 Mbit/s. En recepcin lleva a cabo la funcin complementaria.

Equipo Mltiplex digital plesicrono de 8/34 Mbit/s: Equipo que en transmisin combina 4 tributarios de

8,448 Mbit/s, de forma que a la salida se obtiene una seal mltiplex de 34,368 Mbit/s. En recepcin lleva a

cabo la funcin complementaria.

Equipo Mltiplex digital plesicrono de 34/140 Mbit/s: Equipo que en transmisin combina 4 tributarios de

34,368 Mbit/s, de forma que a la salida se obtiene una seal mltiplex de 139,264 Mbit/s. En recepcin

lleva a cabo la funcin complementaria.

Equipo Mltiplex digital plesicrono de 140/565 Mbit/s: Equipo que en transmisin combina 4 tributarios de

139,264 Mbit/s, de forma que a la salida se obtiene una seal mltiplex de 564,992 Mbit/s. En recepcin

lleva a cabo la funcin complementaria. No est normalizado por la ITU-T. Tambin se denomina mltiplex

digital 4 x 140 Mbit/s.

Propiedades fsicas y elctricas

Interfaces de Conexin

Las especificaciones elctricas para las conexiones E1, E2, E3, etc, son distintas, partiendo por las condiciones

elctricas, tipo de codificacin, tipo de interfaz entre otros detalles.

http://es.wikipedia.org/wiki/Jerarqu%C3%ADa_digital_plesi%C3%B3crona

6/10

13/9/2014

Jerarqua digital plesicrona - Wikipedia, la enciclopedia libre

Protocolo Capacidad

Interfaz

E1

2 Mbit/s

V.35, DB15

E2

8 Mbit/s

No se comercializan(se utilizan enlaces E1 en paralelo)

E3

34 Mbit/s

HSSI(High Speed Serial Interfaz)

Interfaz V.35: Es una combinacin de la norma V.35 y la EIA 232. Todos los pines de datos y de temporizacin

se aaden a la especificacin V.35 que son circuitos balanceados y de bajo voltaje. Utilizado para enlaces

troncales E1 entre equipos de conmutacin.

Interfaz DB15 a BNC: Diseada para trabajar con equipos Cisco, proporciona una interfaz de conexin E1.

Interfaz HSSI: La interfaz serial de alta velocidad (HSSI, High-Speed Serial Interface) admite velocidades de

transmisin de hasta 52 Mbps. La interfaz HSSI se usa para conectar routers en las LAN con las WAN mediante

lneas de alta velocidad como las lneas T3 E3.

Interfaces elctricas

Interfaz E1 A 2048 Kbps - En los puertos de entrada, se

presentar una impedancia de 75 Ohms para conexiones

coaxiales y de 120 Ohms para conexiones de pares

simtricos.

- Un margen de 12-18 dB en prdidas por retorno

@3KHz.

- El conductor exterior al par coaxial deber conectarse a

la red de tierra.

Interfaces E2, E3, E4 - En los puertos de entrada

presenta un impedancia de 75 Ohms.

- Un margen de 6-8 dB en prdidas por retorno @12Khz

(E2), @51KHz (E3).

Fig. 5 Interfaces PDH a) DB15 a BNC, b) V.35, c)

HSSI

Codificacin

Se presentan varios esquemas de codificacin, sin embargo, para el caso del estndar Europeo, el nico esquema

de codificacin empleado para todos los niveles de jerarqua es el HDB3 a excepcin del E4 que usa CMI.

Cdigo de Lnea HDB3

- Alta Densidad Bipolar 3 Ceros.

- Admite hasta 3 ceros consecutivos, invierte la polaridad en un 4. cero. Alternan las polaridades para evitar la

componente continua.

- Adecuado para transmisin a altas velocidades.

Cdigo CMI

- Coded mark inversin.

- Permite una mnima componente contnua y un mximo nmero de cambios de nivel.

- Diseado para velocidades de 140 Mbps de la jerarqua digital plesiocrona.

Deteccin de errores y alarmas

Deteccin de errores

http://es.wikipedia.org/wiki/Jerarqu%C3%ADa_digital_plesi%C3%B3crona

7/10

13/9/2014

Jerarqua digital plesicrona - Wikipedia, la enciclopedia libre

La deteccin de errores se ejecuta sobre la secuencia de alineamiento de trama (TS0 de las tramas pares), de

forma que el receptor que ejecuta la medida compara la secuencia recibida en este octeto con el patrn.

Este mtodo es poco exhaustivo, pues testea nicamente 8 bits de cada 512, pero es el que se utiliza en ausencia

de implementacin de CRC.

La CRC por sus siglas en ingles, es un mtodo de control de errores y una de sus finalidades es el monitoreo de

errores, donde controla el BER de un enlace digital de extremo a extremo, el cdigo CRC se coloca al crear la

trama y se mantiene con ella hasta el final donde el receptor la analiza para ver si ocurri un error. El CRC no es

ms que un conjunto de bits de paridad usados para el control de la tasa de error.

Alarmas PDH

Prdida de trama (LOS)

La alarma en PDH denominada LOS (Lost of frame), se dispara cuando el nivel de la seal se encuentra por

debajo de un BER de 1 en 10, esto puede ocurrir cuando se corta el cable de transmisin o existe mucha

atenuacin en la seal. La alarma ser retirada cuando se detecten dos tramas PDH y no nuevas seales de LOS.

Algunos criterios para la deteccin y desaparicin de la seal de LOS segn la norma G.775 son:

Se detecta una seal de LOS en una interfaz de 64 kbps cuando se tiene una ausencia de seal por un

periodo de 31 us a 30 ms.

Se detecta una seal de LOS en una interfaz de 2048 Kbps cuando se tiene una ausencia de seal por un

periodo de 5 us a 1 ms.

Se detecta una seal de LOS en una interfaz de 8448 Kbps cuando se tiene una ausencia de seal por un

periodo de 1.2us a 1 ms.

Se detecta una seal de LOS en una interfaz de 34368 Kbps cuando se tiene una ausencia de seal por un

periodo de 0.3us a 1 ms.

Se detecta una seal de LOS en una interfaz de 139264 Kbps cuando se tiene una ausencia de seal por un

periodo de 36ns a 1 ms.

En todos los casos la alarma desaparecer cuando se detecte la transmisin de seales, el trmino de las alarmas

debe ser comunicado casi en el mismo periodo sealado en la aparicin de la alarma.

Seal indicadora de alarma (AIS)

La alarma denominada AIS (Alarm Indication Signal) es una seal de informacin caracterstica que poseen todas

las jerarquas SDH. Es generada para remplazar el trfico normal cuando este contiene una condicin defectuosa

para poder prevenir fallos.

Algunos criterios para la deteccin y desaparicin de la seal de AIS segn la norma G.775 son:

Dos criterios diferentes para la deteccin de AIS en una interfaz de 64 kbps:

La seal de 64 kbps contiene 5 o menos ceros en una secuencia de 128 unos.

La seal de 64 kbps de unos sin trama con una duracin de 15.6 ms no debe contener ms de

0.20.1% ceros.

Dos criterios diferentes para la deteccin de AIS en una interfaz de 2048 kbps:

La seal de 2048 kbps contiene 2 o menos ceros en una secuencia de 512 bits (250 us).

http://es.wikipedia.org/wiki/Jerarqu%C3%ADa_digital_plesi%C3%B3crona

8/10

13/9/2014

Jerarqua digital plesicrona - Wikipedia, la enciclopedia libre

La seal de 64 kbps de unos sin trama con una duracin de 0.5 ms no debe contener ms de

0.20.1% ceros.

La seal de entrada tiene 1 o menos ceros en cada una de dos periodos de tramas consecutivas (512

bits por doble trama).

En todos los casos la alarma desaparece cuando dos o menos zeros son detectados en una secuencia de 3156 bits.

Remote Defect Indication (RDI)

La alarma denominada RDI (RemoteDefectIndication) es una seal que se enva al equipo transmisor cuando se

detectan alarmas como Lost of Frame, Lost of Signal o AIS. Algunos criterios para la deteccin y desaparicin de

la seal de RDI segn la norma G.775 son:

- Criterio para la deteccin de una alarma RDI en un nivel TS-16:

La alarma se activa con un solo bit y se configura como un 1 binario durante un perodo de muestreo de

5ms. La alarma desaparece cuando el bit y se configura como un binario 0 durante un periodo de

muestreo de 5 ms.

- Criterio para la deteccin de una alarma RDI en una interfaz de 2048 kbps:

La alarma se activa con un solo bit A se configura como un 1 binario durante un periodo de muestreo de 5

ms. La alarma desaparece cuando el bit A se configura como un binario 0 durante un periodo de muestreo

de 5 ms.

Limitaciones de PDH

El proceso de justificacin por una parte, y por otra el hecho de que la temporizacin vaya ligada a cada nivel

jerrquico, hacen que en la prctica sea imposible identificar una seal de orden inferior dentro de un flujo de orden

superior sin demultiplexar completamente la seal de lnea.

Uno de los mayores inconvenientes de la demultiplexacin plesicrona es que una vez formada la seal mltiplex,

no es posible extraer un tributario concreto sin demultiplexar completamente la seal.

Supongamos por ejemplo que tenemos un flujo de 140 Mbit/s, y que en un punto intermedio deseamos extraer un

canal a 2 Mbit/s; es necesario para ello recurrir a las voluminosas y rgidas cadenas de multiplexacin.

Las diferentes jerarquas plesicronas existentes: Americana, Europea y Japonesa, hacen muy difcil el

interfuncionamiento. La escasa normalizacin ha conducido a que los cdigos de lnea, la modulacin o las

funciones de supervisin, sean especficas de cada suministrador, de forma que equipos de diferentes fabricantes

son incompatibles entre s.

Vase tambin

Jerarqua digital sncrona (SDH)

Referencias

http://es.wikipedia.org/wiki/Jerarqu%C3%ADa_digital_plesi%C3%B3crona

9/10

13/9/2014

Jerarqua digital plesicrona - Wikipedia, la enciclopedia libre

a

b

1.

jerarqua

digital

plesicrona

(http://diccionario.raing.es/es/lema/jerarqu%C3%ADa-digitalplesi%C3%B3crona), Diccionario Espaol de Ingeniera (1.0 edicin), Real Academia de Ingeniera de Espaa,

2014, http://diccionario.raing.es/es/lema/jerarqu%C3%ADa-digital-plesi%C3%B3crona, consultado el 21 de mayo

de 2014

Enlaces externos

Sitio ITU (http://www.itu.int/net/home/index-es.aspx)

Estndar ITU G.732 (http://www.itu.int/rec/T-REC-G.732-198811-I/es) Caractersticas del equipo

mltiplex MIC primario que funciona a 2048 kbit/s

Estndar ITU G.733 (http://www.itu.int/rec/T-REC-G.733-198811-I/es) Caractersticas del equipo

mltiplex MIC primario que funciona a 1544 kbit/s

Obtenido de http://es.wikipedia.org/w/index.php?title=Jerarqua_digital_plesicrona&oldid=76561008

Categoras: Telecomunicaciones Trminos de telecomunicaciones Estndares de telecomunicaciones

Esta pgina fue modificada por ltima vez el 24 ago 2014 a las 22:23.

El texto est disponible bajo la Licencia Creative Commons Atribucin Compartir Igual 3.0; podran ser

aplicables clusulas adicionales. Lanse los trminos de uso para ms informacin.

Wikipedia es una marca registrada de la Fundacin Wikimedia, Inc., una organizacin sin nimo de lucro.

http://es.wikipedia.org/wiki/Jerarqu%C3%ADa_digital_plesi%C3%B3crona

10/10

S-ar putea să vă placă și

- Jerarquía Digital PlesiócronaDocument11 paginiJerarquía Digital PlesiócronaEberSantaCruzBerriosÎncă nu există evaluări

- Jerarquía Digital PlesiócronaDocument7 paginiJerarquía Digital PlesiócronaedgarfransÎncă nu există evaluări

- Jerarquía Digital Plesiócrona: ÍndiceDocument9 paginiJerarquía Digital Plesiócrona: ÍndiceNeycerAnchundiaÎncă nu există evaluări

- Jerarquía Digital PlesiócronaDocument40 paginiJerarquía Digital PlesiócronaWilson RodriguezÎncă nu există evaluări

- PDHDocument18 paginiPDHkiyipi123100% (1)

- PDH y SDHDocument4 paginiPDH y SDHDavid AvilaÎncă nu există evaluări

- Tecnología de Transporte PDH, SDH, OTNDocument12 paginiTecnología de Transporte PDH, SDH, OTNGrace Romualdo LazaroÎncă nu există evaluări

- SDH y PDHDocument44 paginiSDH y PDHJuan Carlos G HÎncă nu există evaluări

- Jerarquia Digital PlesiocronaDocument4 paginiJerarquia Digital PlesiocronaJaime Humberto Pech CarmonaÎncă nu există evaluări

- Consulta 1 PDHDocument21 paginiConsulta 1 PDHMontes Silva EryÎncă nu există evaluări

- Trabajo de Investigacion de AuxiliaturaDocument41 paginiTrabajo de Investigacion de AuxiliaturaJimenez Meneces BrianÎncă nu există evaluări

- Jerarquía Digital Plesiócrona - PDHDocument4 paginiJerarquía Digital Plesiócrona - PDHChristian Silva Arrieta100% (1)

- PDHDocument24 paginiPDHDeiviÎncă nu există evaluări

- La Jerarquía Digital PlesiócronaDocument11 paginiLa Jerarquía Digital PlesiócronaMarcos HerreraÎncă nu există evaluări

- PDH DefinicionDocument13 paginiPDH DefinicionAndres Felipe Sierra CorreaÎncă nu există evaluări

- Jerarquias Digitales de TransmisiónDocument29 paginiJerarquias Digitales de TransmisiónSagitta LyraeÎncă nu există evaluări

- Jerarquias de ComunicacionDocument10 paginiJerarquias de ComunicaciondennisÎncă nu există evaluări

- Telefonia SDHDocument16 paginiTelefonia SDHAngel SczÎncă nu există evaluări

- PDH SDH TDMDocument6 paginiPDH SDH TDMdarr3Încă nu există evaluări

- Descripción Del Protocolo PDHDocument7 paginiDescripción Del Protocolo PDHManuel Alberto Segobia MuñozÎncă nu există evaluări

- PDH - SDHDocument11 paginiPDH - SDHSantiago RodriguezÎncă nu există evaluări

- Redes Conmutadas Por CircuitoDocument12 paginiRedes Conmutadas Por Circuitofabiola97Încă nu există evaluări

- PDH Jerarquía Digital PlesiócronaDocument5 paginiPDH Jerarquía Digital PlesiócronaEugenio Puche SánchezÎncă nu există evaluări

- SDHDocument0 paginiSDHJuanPabloAAÎncă nu există evaluări

- Jerarquía Digital PlesiócronaDocument18 paginiJerarquía Digital PlesiócronaRivasandreeeaÎncă nu există evaluări

- Jerarquía Digital PlesiócronaDocument4 paginiJerarquía Digital PlesiócronaEddy AyalaÎncă nu există evaluări

- Inf 3742 (Redes de Banda Ancha) : JDP O PDH (Jerarquía Digital Plesiocrona)Document17 paginiInf 3742 (Redes de Banda Ancha) : JDP O PDH (Jerarquía Digital Plesiocrona)Jhamil VillegasÎncă nu există evaluări

- PDH SDH PCM Ss7Document6 paginiPDH SDH PCM Ss7Lenin Antonio Juela TorresÎncă nu există evaluări

- PDH - SDH V1 - 1Document52 paginiPDH - SDH V1 - 1Camilo ManriqueÎncă nu există evaluări

- E1 Trama de TXDocument19 paginiE1 Trama de TXHeidi SharpeÎncă nu există evaluări

- Trama E1Document19 paginiTrama E1Jaime Garcia De Paredes100% (1)

- Monografía PDH y SDHDocument32 paginiMonografía PDH y SDHwilliamolivares_Încă nu există evaluări

- Jerarquia Digital PlesiocronaDocument6 paginiJerarquia Digital PlesiocronaKarlita M.Încă nu există evaluări

- Técnica de SupermercadoDocument7 paginiTécnica de SupermercadoLuis LópezÎncă nu există evaluări

- Tema 6Document20 paginiTema 6lagarto_dÎncă nu există evaluări

- SONETDocument4 paginiSONETJhonatan EspinozaÎncă nu există evaluări

- SDHDocument15 paginiSDHginethalexandraÎncă nu există evaluări

- Exposicion PDH SDHDocument30 paginiExposicion PDH SDHJuan Soto Hernández100% (1)

- Capitulo IVDocument9 paginiCapitulo IVGeovanny GabrielÎncă nu există evaluări

- Ensayo 1Document6 paginiEnsayo 1STEPHANYE JAZMIN ACUTA MORATAYAÎncă nu există evaluări

- Jerarquía Digital SíncronaDocument11 paginiJerarquía Digital SíncronaRoberto VásquezÎncă nu există evaluări

- Jerarquias de TransmisionDocument6 paginiJerarquias de TransmisionAlfredo De Luis100% (1)

- Ensayo Sobre Comunicacion SerialDocument10 paginiEnsayo Sobre Comunicacion SerialMark PamplonÎncă nu există evaluări

- Jerarquía Digital Plesiócrona (PDH) : Web SiteDocument9 paginiJerarquía Digital Plesiócrona (PDH) : Web Sitevvd1011Încă nu există evaluări

- SDH II 2010 Examen 2012Document178 paginiSDH II 2010 Examen 2012Michael Punguil75% (4)

- SDHDocument46 paginiSDHJairo Saavedra SaavedraÎncă nu există evaluări

- Protocolo ss7Document11 paginiProtocolo ss7judabacaÎncă nu există evaluări

- PDH SDHDocument8 paginiPDH SDHrodiaz65Încă nu există evaluări

- PDH y SDHDocument53 paginiPDH y SDHGlendaCernaÎncă nu există evaluări

- Desarrollo de La Tarea1 - ConmutacionDocument9 paginiDesarrollo de La Tarea1 - ConmutacionJames Mora MosqueraÎncă nu există evaluări

- Desarrollo de La Tarea1 - ConmutacionDocument15 paginiDesarrollo de La Tarea1 - ConmutacionJames Mora MosqueraÎncă nu există evaluări

- Marco Teórico PASANTIAS (En Ejecución)Document14 paginiMarco Teórico PASANTIAS (En Ejecución)Alfredo Guánchez VillegasÎncă nu există evaluări

- CLASE6Document5 paginiCLASE6Alvakito Flower'sÎncă nu există evaluări

- Fisica Aplicada TelecomunicacionesDocument255 paginiFisica Aplicada TelecomunicacionesPatricio Pé50% (2)

- Jerarquia Digital Plesiocrona PDHDocument11 paginiJerarquia Digital Plesiocrona PDHTacoMedinaOscarÎncă nu există evaluări

- Redes Conmutadas Por CircuitoDocument27 paginiRedes Conmutadas Por CircuitoZulay RomeroÎncă nu există evaluări

- Prácticas de redes de datos e industrialesDe la EverandPrácticas de redes de datos e industrialesEvaluare: 4 din 5 stele4/5 (5)

- UF1874 - Mantenimiento de la infraestructura de la red de comunicacionesDe la EverandUF1874 - Mantenimiento de la infraestructura de la red de comunicacionesÎncă nu există evaluări

- UF1869 - Análisis del mercado de productos de comunicacionesDe la EverandUF1869 - Análisis del mercado de productos de comunicacionesÎncă nu există evaluări

- UF1872 - Implantación y configuración de pasarelasDe la EverandUF1872 - Implantación y configuración de pasarelasEvaluare: 5 din 5 stele5/5 (1)

- Calculo DifeDocument17 paginiCalculo DifeJosHerreraÎncă nu există evaluări

- JereciciosDocument2 paginiJereciciosJosHerrera100% (1)

- Nota08 PDFDocument72 paginiNota08 PDFJosHerreraÎncă nu există evaluări

- Traduccion de Capitulos Del Libro de Aris Spanos PDFDocument549 paginiTraduccion de Capitulos Del Libro de Aris Spanos PDFJosHerreraÎncă nu există evaluări

- 02defrebreo2011 120708191144 Phpapp01Document58 pagini02defrebreo2011 120708191144 Phpapp01JosHerreraÎncă nu există evaluări

- Problemes Nous PDFDocument55 paginiProblemes Nous PDFJosHerreraÎncă nu există evaluări

- Probab PDFDocument22 paginiProbab PDFJosHerreraÎncă nu există evaluări

- Tecnología Álbum 2Document9 paginiTecnología Álbum 2Daissy Sofia Melgar ArdonÎncă nu există evaluări

- Cronología de Florinda Donner-Grau, Parte IDocument7 paginiCronología de Florinda Donner-Grau, Parte IcarolinafasioÎncă nu există evaluări

- Indicadores de Gestión EjemploDocument2 paginiIndicadores de Gestión EjemploAdry MuñozÎncă nu există evaluări

- Práctica 3Document7 paginiPráctica 3Luis Herrador CruzÎncă nu există evaluări

- Acta de Entrega Huacahuasi DerechoDocument2 paginiActa de Entrega Huacahuasi DerechoIvan Mamani MermaÎncă nu există evaluări

- Contrato de Arrendamiento de Bodega A AlmavivaDocument16 paginiContrato de Arrendamiento de Bodega A AlmavivakountluigiÎncă nu există evaluări

- MSDS Cherteston 274Document8 paginiMSDS Cherteston 274Italo JaureguiÎncă nu există evaluări

- Analisis Situacional EntelDocument19 paginiAnalisis Situacional EntelAndrea RojasÎncă nu există evaluări

- FQ2-2021.1 Tarea 01Document1 paginăFQ2-2021.1 Tarea 01salma de la rosaÎncă nu există evaluări

- Certf. CosmosDocument1 paginăCertf. CosmosIrvin ChapilliquenÎncă nu există evaluări

- 1er Parcial Compensadores ControladoresDocument14 pagini1er Parcial Compensadores ControladoresFabiola MejiasÎncă nu există evaluări

- Consigna TP2-FINAL-TexturasN5A-ScuffiDocument3 paginiConsigna TP2-FINAL-TexturasN5A-ScuffiJulian OLIVEROÎncă nu există evaluări

- Unidad Ii - Algebra LinealDocument19 paginiUnidad Ii - Algebra LinealJuan Rios DavilaÎncă nu există evaluări

- Modelo Presentación Pitch de Emprendimiento ACTUALDocument15 paginiModelo Presentación Pitch de Emprendimiento ACTUALSantiago Arturo Rodriguez SalcedoÎncă nu există evaluări

- Riesgos Higienicos en El Sector de La JoyeriaDocument14 paginiRiesgos Higienicos en El Sector de La JoyeriaKaren Zugeidi Buitrago GarciaÎncă nu există evaluări

- Evidencia 3.Document2 paginiEvidencia 3.Fernando Mueses100% (6)

- Desarrollo Territorial - Repensar El Poder Desde Los Gobiernos LocalesDocument45 paginiDesarrollo Territorial - Repensar El Poder Desde Los Gobiernos Localescposso1Încă nu există evaluări

- Ecopetrol CIIUDocument10 paginiEcopetrol CIIUmaii_toloza0% (1)

- Desistimiento Civil ActualizadoDocument4 paginiDesistimiento Civil ActualizadoCony Barrios MarteÎncă nu există evaluări

- Practica 5Document14 paginiPractica 5Daniel S. NavaÎncă nu există evaluări

- Actividad 1 Los Principales Sistemas OperativosDocument8 paginiActividad 1 Los Principales Sistemas OperativosDark Angel26Încă nu există evaluări

- Santa LuciaDocument71 paginiSanta LuciaJohnMhijailViianuevaArevalhoÎncă nu există evaluări

- Proyecto Final v1Document14 paginiProyecto Final v1Oswaldo Dareel Soto100% (1)

- Dia Positi VasDocument28 paginiDia Positi VasIsrael Nazareth Chaparro CruzÎncă nu există evaluări

- Capitulo 5 MicroeconomiaDocument4 paginiCapitulo 5 MicroeconomiaSabino GarciaÎncă nu există evaluări

- El Sistema de Producción Justo A TiempoDocument4 paginiEl Sistema de Producción Justo A TiempoMariana Martinez HernandezÎncă nu există evaluări

- Acción de Inconstitucionalidad (Objeto)Document5 paginiAcción de Inconstitucionalidad (Objeto)Lesly LópezÎncă nu există evaluări

- Datos Centros de Acopio y AlamacenamientoDocument8 paginiDatos Centros de Acopio y AlamacenamientoIsabella Cardona SernaÎncă nu există evaluări

- Pasaje - MarthaDocument1 paginăPasaje - MarthaElvis Vargas AsenciosÎncă nu există evaluări

- Copia de Cuaderno Profesor (Asignatura) v3Document57 paginiCopia de Cuaderno Profesor (Asignatura) v3natalia_bÎncă nu există evaluări