Documente Academic

Documente Profesional

Documente Cultură

An-Leakage Power Evaluation in Microwind

Încărcat de

Lean MiñonDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

An-Leakage Power Evaluation in Microwind

Încărcat de

Lean MiñonDrepturi de autor:

Formate disponibile

MICROWIND APPLICATION NOTE

Leakage

Leakage Power Consumption Evaluation in

Microwind31

Etienne SICARD

Professor

INSA-Dgei, 135 Av de Rangueil

31077 Toulouse France

email: Etienne.sicard@insa-toulouse.fr

This paper describes the leakage current effect appearing in MOS devices, presents low-leakage

device options, and gives a rapid overview of the current leakage modeling in LEVEL1, LEVEL3 and

BSIM4. The recent trends in leakage current reduction are also recalled for 45-nm technology. Finally,

a case study serves as an illustration of the low-leakage MOS device benefits versus high-speed MOS

devices.

1. Leakage Current in MOS devices

The leakage current is the current that flows between Drain and Source when no channel is present.

The expected behavior of the n-channel MOS device is summarized in figure 1. The 0 on the gate

should leave the drain floating. No current is expected to flow between drain and source. Howevere, a

leakage current enables nA range current to flow although the gate voltage is 0. In contrats, the 1 on

the gate should link the drain to the source, via a resistive path and enable mA range current to flow

between drain and source.

Drain floating

Drain connected to

source

Leakage

current

Pass 0

Pass 1

Figure 1: Ioff current when the channel is off (nMOS)

For the pMOS device, the 1 on the gate should leave the drain floating. In that situation again, a nArange current called leakage current may flow between source and drai.

Page 1/13

MICROWIND APPLICATION NOTE

Leakage

Leakage current

Figure 2: Ioff current when the channel is off (pMOS)

2. Low-Leakage vs. High-Speed Mos

The main objective of the low leakage MOS is to reduce the Ioff current significantly, that is the small

current that flows between drain and source with a zero gate voltage. The price to pay is a reduced Ion

current. The designer has the possibility to use high speed MOS devices, which have high Ioff

leakages but large Ion drive currents. The symbols of the low leakage MOS and the high speed MOS

are given in figure 3. The size correspond to the 0.12m technology.

Figure 3: The low leakage MOS symbol (left) and the high speed MOS symbol (right)

Page 2/13

MICROWIND APPLICATION NOTE

Leakage

Ion=550A

Ion=800A

Ioff around 100nA

Ioff around 1nA

Fig. 4: The low leakage MOS offers a low Ioff current (1nA) but a reduced Ion current (550A)

as compared to the high speed MOS, in 0.12m technology [Sicard2005a]

In figure 4, the low leakage MOS device (left side) has an Ioff current reduced nearly by a factor 100,

thanks to a higher threshold voltage (0.4V rather than 0.3V) and larger effective channel length

(120nm) compared to the high speed MOS (100nm, see figure 5). By default, the MOS device is in

low leakage option, to encourage low power design. The Ion difference is around 30%. This means

that an high speed MOS device is 30% faster than the low leakage MOS. Its use is justified in circuits

where speed is critical.

20

gate

oxide

N+

diffusion

High substrate

doping

Effective channel

0.10m

High speed MOS

20

gate

oxide

N+

diffusion

Low substrate

doping

Effective channel

0.12m

Low leakage MOS

Fig. 5: Process section of the high speed (left) and low leakage (right) MOS devices

High speed MOS devices may be found in clock trees, data bus interfaces, central processing units,

while low leakage MOS are used whenever possible, for all nodes where a maximum switching speed

is not mandatory.

Page 3/13

MICROWIND APPLICATION NOTE

Leakage

3. Ioff Current Modelling

Ioff Modelling using LEVEL1

Using LEVEL1, the Ioff current is always 0 below the threshold voltage VTO. If Vgs<VTO, the device

is in cut-off mode.

Ids = 0

Ioff Modelling using LEVEL3

In sub-threshold mode (gate voltage less than the threshold voltage VTO), an exponential dependence

of the current with Vgs is introduced by using the equation 1. See [Weste] for a detailed analysis of

MOS LEVEL3. Notice the temperature effect introduced in the denominator nkT. Without any voltage

applied to the gate, the current is not equal to zero. The current of Ids for Vgs=0 is called the Ioff

current (Figure 6). Its value in 0.12m is around 10-10 A. In contrast, for Vgs=VDD, the maximum

current Ion is of the order of several mA (10-3 A).

Ids = Ids(Von,Vds)exp(

q(Vgs - Von)

)

nkT

(Equ. 1)

Ids (log)

10-3

-5

10

Subthreshold

(Vgs<VTO)

Von

model 3,

BSIM do this

Above threshold

(Vgs>VTO)

Model 1 would do this

10-7

10-9

Ion

Vgs

Ioff

VTO

VDD

Figure 6: An exponential law is introduced to the MOS device model to account for the subthreshold behavior of the current

Mos Model 3 parameters

Parameter

Definition

NSS

Page 4/13

Substhreshold factor

Typical Value 0.12m

NMOS

pMOS

0.07 V-1

0.07 V-1

MICROWIND APPLICATION NOTE

Leakage

Ioff Modelling using BSIM4

Amoung many other effects, the Ioff modeling in BSIM4 has been handled with care. The parameter

Vgsteff is a mathematical smoothing function [Liu 2001] to ensure continuity between the subthreshold

region and the linear region.

(Vgs Vth)

)

n.vt

) (Equ. 2)

Vgst eff = max( VOFF,

(Vgs Vth)

1 + n.exp(

)

n.vt

n = 1 + NFACTOR

(Equ. 3)

n.vt.ln(1 + exp(

A specific parameter VOFF is introduced to account for a specific effect appearing in short-channel

device when Vgs is negative. Conventional models predict that the current decrease with an

exponential law down to zero with decreasing Vgs. For Vgs<0, Ids is supposed to be 0. In

Microwind31, both VOFF and NFACTOR are user-accessible.

Ids (Log)

Measurements

10-3

Ids above VTO

Ids below

VTO

10-6

With VOFF,

current keeps

above a limit

10-9

VOFF

VTO

Vgs

Without VOFF, the

current would continue

to decrease

Figure 7: Illustration of the subthreshold current for Vgs below the threshold voltage VTO

In real-case measurements, Ids stops decreasing near zero Vgs, and then tends to increase with

negative Vgs (Figure 7). This effect is called gate-induced drain leakage (GIDL). Consequently, the

leakage current Ioff can be significant when Vgs is negative (Quite frequent in logic cells). The VOFF

parameter stops the Ids at a certain value, a simplified version of the BSIM4 modeling of the so-called

gate-induced leakage current (More info may be found in [Liu]).

Page 5/13

MICROWIND APPLICATION NOTE

IOFF stops the

current decrease

Leakage

NFACTOR acts on

the slope

Figure 8: Illustration of the effects of IOFF and NFACTOR in sub-threshold mode

The parameter NFACTOR is usually close to 1, meaning that n is close from 2 (Equation 3). The effect

on NFACTOR is illustrated in the display mode Id. vs. Vg, in logarithmic scale, as illustrated in figure

8.

Parameter

NFACTOR

VOFF

Description

NMOS value NMOS value

in 0.12m

in 0.12m

1

Sub-threshold turn-on swing 1

factor. Controls the exponential

increase of current with Vgs.

Offset voltage in subthreshold -0.08V

-0.08V

region.

Name in RUL

file

B4NFACTOR

B4VOFF

Table 1: List of user-accessible parameters in the BSIM4 implementation in Microwind.

Page 6/13

MICROWIND APPLICATION NOTE

Leakage

4. Trends in Ioff Current

Limiting the Leakage Current

The recent introduction of metal gate (See application note on 45-nm technology [Sicard07]) has

induced a drastic reduction of the parasitic leakage current Ioff, while increasing the Ion current, as

shown in Fig. 9.

Drain current (A/m)

Ion current

increase

Traditionnal

process

10-3

10-4

10-5

Metal-gate

process

10-6

10-7

Ioff current

decrease

10-8

10-9

10-10

0.0

0.5

1.0

Gate voltage (V)

Figure 9: The metal gate combined with High-K oxide material enhances the Ion current and drastically reduces

the Ioff current.

Leakage Current in 45-nm Technology

Parameter

Drawn length (nm)

Effective length (nm)

Threshold voltage (V)

Ion (mA/m) at VDD=1.0V

Ioff (nA/m)

NMOS

Low leakage

40

35

0.20

0.9

7

NMOS

High speed

40

30

0.18

1.2

200

Table 2: nMOS parameters featured in the CMOS 45-nm technology provided in Microwind31

The device I/V characteristics of the low-leakage and high-speed MOS in 45-nm technology devices

are obtained using the MOS model BSIM4 (See [Sicard2005a] for more information about this

model). Concerning the low-leakage MOS, the I/V characteristics reported in Fig. 10 demonstrate a

drive current capability of around 0.9 mA/m for W=1.0m at a voltage supply of 1.0 V. For the high

Page 7/13

MICROWIND APPLICATION NOTE

Leakage

speed MOS, the effective channel length is slightly reduced as well as the threshold voltage, to achieve

a drive current around 1.2 mA/m.

High-speed Ion

25% increase of the

maximum current

Imax=0.9 mA

Low-leakage Ion

(a) Low leakage W=1m, Leff= 35nm

(b) High speed W=1m, Leff= 30nm

Figure 10: Id/Vd characteristics of the low leakage and high speed nMOS devices

Id/Vg for Vb=0, Vds=1 V

Ioff=7 nA

Vt=0.2 V

(a) low leakage MOS (Leff=35 nm)

Ioff=200 nA

Vt=0.2 V

(b) high speed MOS (W=1 m, Leff=30 nm)

Figure 11: Id/Vg characteristics (log scale) of the low leakage and high-speed nMOS devices

The drawback of the high-speed MOS current drive is the leakage current which rises from 7 nA/m

(low leakage) to 200 nA/m (high speed), as seen in the Id/Vg curve at the X axis location

corresponding to Vg= 0 V (Fig. 11-b).

Temperature effects

Note that in the sub-threshold region, the impact of temperature is extremely important, as

demonstrated in figure 12. At low temperature the current Ids decreased rapidly down to 10nA,

corresponding to a small off leakage current. In contrast, at high temperature, not only the threshold

voltage is reduced but the sub-threshold slope is flattened, which means an exponential increase of the

Ioff leakage current (figure 12).

Page 8/13

MICROWIND APPLICATION NOTE

Leakage

100C

27C

-20C

Figure 12: The effect of temperature on the MOS characteristics.

Leakage effects not handled by Microwind31

Note that several other leakage current effects exist in nano-scale MOS devices, such as the drain/gate

and source/gate leakage. More information about these effects may be found in [Liu].

The diode leakage is modelized in Microwind31 under specific conditions, such as presented in the

I/O structures.

Page 9/13

MICROWIND APPLICATION NOTE

Leakage

5. Simulation of Leakage Current

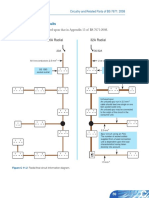

Let us consider the ring oscillator with an enable circuit, where one inverter has been replaced by a

NAND gate to enable or disable oscillation (Inv5Enable.MSK). The schematic diagram of the

oscillator and its layout implementation are shown in Fig. 13. We analyze its switching performances,

in the high speed and low leakage modes.

Figure 13: The schematic diagram and layout of the ring oscillator used to compare the analog performances in

high speed and low leakage mode (INV5Enable.MSK)

Page 10/13

MICROWIND APPLICATION NOTE

Leakage

Reduced

consumption

(100 A max)

Strong consumption

(170 A max)

Low standby

current

High standby

current

Fast oscillation

(37 GHz)

Slower

oscillation

(28 GHz)

Figure 14: Simulation of the ring oscillator in high speed mode (left) and low leakage mode (right). The

oscillating frequency is faster in the case of high-speed mode but the standby current is high (Inv5Enable.MSK)

The tick in front of "Scale I in log" must be asserted to display the current in logarithmic scale. The

option layer which surrounds all the oscillator devices is set to high speed mode first by a double click

inside that box, and by selecting high speed (Fig. 14). The analog performances of both options are

summarized in Fig. 14. In the high speed mode, the circuit works fast (37 GHz) but consumes a

significant standby current when off (around 200 nA).

(1) Double click in

the option box

(2) Modify the MOS

option as low

leakage

Figure 15: Changing the MOS option into low leakage mode

Once the option layer is set to low leakage (Fig. 15), the simulation is performed again. The lowleakage mode features a little slower oscillation (29 GHz that is approximately a 30 % speed

reduction) and more than one decade less standby current when off (5 nA). In summary, low leakage

MOS devices should be used as default devices whenever possible. High speed MOS should be used

only when switching speed is critical.

Page 11/13

MICROWIND APPLICATION NOTE

Leakage

6. Modifying Microwind31 Leakage Parameters

The easiest way to modify the leakage parameters is to change directly the RUL file.

Mos Level3

The parameter l3nss may be changed to modify the subthreshold slope and therefore the Ioff current.

PARAMETER

KEYWORD

DEFINITION

NSS

l3nss

Sub-threshold factor

TYPICAL VALUE 0.25m

NMOS

pMOS

0.07 V-1

0.07 V-1

In the RUL file, the parameters l3nss in the NMOS section and l3nss in the PMOS section may be

modified. The following NSS values are provided for CMOS 45-nm technology.

* Nmos Model 3 parameters

*

NMOS

l3vto = 0.34

l3nss = 0.045

*

* Pmos Model 3

*

PMOS

l3vto = -0.32

l3nss = 0.045

Mos BSMI4

The parameters Nfactor and Voff may be changed to modify the sub threshold slope and minimum

value, with direct impact on the Ioff current.

Parameter Keyword

Description

NFACTOR B4nf

Sub-threshold turn-on swing factor.

Controls the exponential increase of

current with Vgs.

Offset voltage in subthreshold region.

VOFF

b4voff

NMOS

value in

0.12m

1

PMOS

value in

0.12m

1

-0.08V

-0.08V

In the RUL file, the parameters b4nfact and b4voff in the NMOS and PMOS sections may

be modified. The following b4nfact and b4voff values are provided for CMOS 45-nm

technology.

* BSIM4 parameters

*

NMOS

Page 12/13

MICROWIND APPLICATION NOTE

Leakage

b4vtho = 0.35

b4nfact = 1.02

b4voff = 0.01

*

PMOS

b4vtho = 0.36

b4nfact = 1.05

b4voff = 0.01

7. Conclusions

This application note has detailed the leakage current effect and its modeling, with illustration of the

MOS options, the different available models in Microwind31 and one illustration in the case of a ring

oscillator.

References

[Bsim4] BSIM4 web site www-device.eecs.berkeley.edu

[Weste] N. Weste, K. Eshraghian "Principles of CMOS VLSI design", Addison Wesley, ISBN 0-20153376-6, 1993

[Liu] W. Liu "Mosfet Models for SPICE simulation including Bsim3v3 and BSIM4", Wiley & Sons,

2001, ISBN 0-471-39697-4

[Sicard2005a] E. Sicard, S. Ben Dhia Basic CMOS cell design, McGraw Hill India, 450 pages,

ISBN 0-07-0599335, June 2005, international edition 2007.

[Sicard2005b] E. Sicard Introducing 90-nm technology in Microwind3, application note, July 2005,

www.microwind.org

[Sicard2006a] E. Sicard Microwind Users Manual, lite version 3.1, www.microwind.org, INSA

editor, 2006

[Sicard2006b] E. Sicard Introducing 65-nm technology in Microwind3, application note, July 2006,

www.microwind.org

[Sicard2007] E. Sicard Introducing 45-nm technology in Microwind3, application note, July 2007,

www.microwind.org

Page 13/13

S-ar putea să vă placă și

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- Radio and TV BroadcastingDocument13 paginiRadio and TV BroadcastingLean MiñonÎncă nu există evaluări

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Seven Layers of OSI ModelDocument9 paginiSeven Layers of OSI ModelLean MiñonÎncă nu există evaluări

- What Is Intellectual Property Law?: Miñon, Leandro B. 10-22855Document10 paginiWhat Is Intellectual Property Law?: Miñon, Leandro B. 10-22855Lean MiñonÎncă nu există evaluări

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Addressing: The What' and Where' of CommunicationDocument24 paginiAddressing: The What' and Where' of CommunicationLean MiñonÎncă nu există evaluări

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- Chapter6 7thDocument14 paginiChapter6 7thMuhammad RidwanÎncă nu există evaluări

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- Amplitude Modulation (Am)Document7 paginiAmplitude Modulation (Am)Lean MiñonÎncă nu există evaluări

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- Erich Einen Final ReportDocument21 paginiErich Einen Final ReportLean MiñonÎncă nu există evaluări

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- Radio and TV BroadcastingDocument13 paginiRadio and TV BroadcastingLean MiñonÎncă nu există evaluări

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- SPI Master Controller Implementation On FPGA Using VHDLDocument14 paginiSPI Master Controller Implementation On FPGA Using VHDLAnand Cool100% (1)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- Signalin1 ExactDocument16 paginiSignalin1 ExactLean MiñonÎncă nu există evaluări

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Prelim-Ethics With KEYpointsDocument8 paginiPrelim-Ethics With KEYpointsLean MiñonÎncă nu există evaluări

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Book ReportDocument3 paginiBook ReportLean MiñonÎncă nu există evaluări

- Experiment ResultsDocument6 paginiExperiment ResultsLean MiñonÎncă nu există evaluări

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (73)

- Arithmetic Logic UnitDocument63 paginiArithmetic Logic UnitLean MiñonÎncă nu există evaluări

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Amplitude Modulation (Am)Document7 paginiAmplitude Modulation (Am)Lean MiñonÎncă nu există evaluări

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- PLC Repeater and TimersDocument7 paginiPLC Repeater and TimersLean MiñonÎncă nu există evaluări

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- Transmission Line ExperimentDocument2 paginiTransmission Line ExperimentLean MiñonÎncă nu există evaluări

- Pneumatic SymbolsDocument23 paginiPneumatic SymbolsPirate_KillerÎncă nu există evaluări

- EETPaperIIIYR2 PDFDocument109 paginiEETPaperIIIYR2 PDFpsychic_jason0071319Încă nu există evaluări

- Horizontal Section Fault TipsDocument2 paginiHorizontal Section Fault Tipshemendra06@yahoo.com100% (2)

- Pspice ZenerwDocument4 paginiPspice ZenerwVinsen Teubun LetsoinÎncă nu există evaluări

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- Structure Elucidation From XRD 1Document34 paginiStructure Elucidation From XRD 1Meissha Ayu ArdiniÎncă nu există evaluări

- SocketDocument1 paginăSocketEngr Zain Ul AbaidinÎncă nu există evaluări

- Short-Circuit CaculationsDocument10 paginiShort-Circuit CaculationsYousif_AbdalhalimÎncă nu există evaluări

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- Gelatin Direct CompressionDocument4 paginiGelatin Direct CompressionYuuki93Încă nu există evaluări

- SCR Power Control (Watlow)Document28 paginiSCR Power Control (Watlow)nealmalm100% (1)

- SBL2030CT - SBL2060CT: 20A Schottky Barrier RectifierDocument2 paginiSBL2030CT - SBL2060CT: 20A Schottky Barrier RectifiertutulkarÎncă nu există evaluări

- Design and Implementation of An Automatic Power Supply From Four Different Source Using MicrocontrollerDocument8 paginiDesign and Implementation of An Automatic Power Supply From Four Different Source Using MicrocontrollerPradeep KÎncă nu există evaluări

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (120)

- 5200 Service Bulletin Z152Document4 pagini5200 Service Bulletin Z152www_acswinÎncă nu există evaluări

- KUPDF - Free Document Sharing Platform - Upload and ShareDocument2 paginiKUPDF - Free Document Sharing Platform - Upload and Sharemmm89% (9)

- Growth and Characterization of L-Alanine Potassium Nitrate Single Crystals For Nonlinear Optical ApplicationsDocument5 paginiGrowth and Characterization of L-Alanine Potassium Nitrate Single Crystals For Nonlinear Optical ApplicationsPalaniswamy SankariahÎncă nu există evaluări

- Seminar Report: Microstrip Patch Antenna and Its ApplicationsDocument26 paginiSeminar Report: Microstrip Patch Antenna and Its ApplicationsDebdeep Sarkar100% (1)

- JBL GTO1004 SMDocument27 paginiJBL GTO1004 SMautreraÎncă nu există evaluări

- STK4211V: 2-Channel 70 W Min AF Power Amplifier (Split Power Supply)Document3 paginiSTK4211V: 2-Channel 70 W Min AF Power Amplifier (Split Power Supply)mundomusicalmeriaÎncă nu există evaluări

- TBS2000 Digital Storage Oscilloscope Service Manual en USDocument52 paginiTBS2000 Digital Storage Oscilloscope Service Manual en USTushar PatilÎncă nu există evaluări

- Airtel Intelligent Power Management Unit (Ipmu)Document8 paginiAirtel Intelligent Power Management Unit (Ipmu)Masaba Denis MadenÎncă nu există evaluări

- Obsolescence Management The Impact OnDocument8 paginiObsolescence Management The Impact OnZia Ul BasithÎncă nu există evaluări

- 74LCX125Document13 pagini74LCX125ed251Încă nu există evaluări

- Arduino Based Underground Cable Fault Distance LocatorDocument60 paginiArduino Based Underground Cable Fault Distance Locatornabil tijjani100% (3)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- Super FinishingDocument8 paginiSuper FinishingUttara GargÎncă nu există evaluări

- 16MB1A0 Gems Sensors Datasheet 8557295Document4 pagini16MB1A0 Gems Sensors Datasheet 8557295GUZMANÎncă nu există evaluări

- Diffusion in SiliconDocument71 paginiDiffusion in Silicontb770% (1)

- Scier Entechllearning: Logic GatesDocument1 paginăScier Entechllearning: Logic GatesTarangÎncă nu există evaluări

- UL Standard Revisions and Proposals, Tri-National Standard Harmonization ActivitiesDocument31 paginiUL Standard Revisions and Proposals, Tri-National Standard Harmonization Activitiesjigmaster100% (1)

- Id Connected PV Wind Battery Based Multi InputDocument3 paginiId Connected PV Wind Battery Based Multi InputPidikiti Surendra BabuÎncă nu există evaluări

- RF To DC Converter 2.4GHzDocument12 paginiRF To DC Converter 2.4GHzViswa GopalÎncă nu există evaluări

- 830 Series: Silicon 28V Hyperabrupt Varactor DiodesDocument7 pagini830 Series: Silicon 28V Hyperabrupt Varactor DiodesBILAL KIYANIÎncă nu există evaluări

- Lightning Overvoltages in HV-EHV "Mixed" Overhead-Cable LinesDocument6 paginiLightning Overvoltages in HV-EHV "Mixed" Overhead-Cable LinesEmina FehratovicÎncă nu există evaluări

- Hacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxDe la EverandHacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxÎncă nu există evaluări

- Chip War: The Quest to Dominate the World's Most Critical TechnologyDe la EverandChip War: The Quest to Dominate the World's Most Critical TechnologyEvaluare: 4.5 din 5 stele4.5/5 (227)

- Computer Science: A Concise IntroductionDe la EverandComputer Science: A Concise IntroductionEvaluare: 4.5 din 5 stele4.5/5 (14)