Documente Academic

Documente Profesional

Documente Cultură

ATSC 8-VSB Demodulator and Decoder TDA8960: Philips Semiconductors Preliminary Specification

Încărcat de

abbasdfDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

ATSC 8-VSB Demodulator and Decoder TDA8960: Philips Semiconductors Preliminary Specification

Încărcat de

abbasdfDrepturi de autor:

Formate disponibile

Philips Semiconductors

Preliminary specification

ATSC 8-VSB Demodulator and Decoder

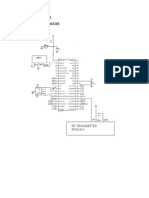

PINNING

Feed forward including a decision feedback structure (DFE)

Range of -2.3 s to +10.5 s

Rate 2/3 (Rate 1/2 Ungerboeck code based)

Reed-Solomon decoder

Internal convolutional de-interleaving

External indication of uncorrectable error (Transport Error Indicator bit

in MPEG packet header is also set)

Followed by de-randomizer based on ATSC standard

I2C interface

I2C-bus interface to initialize and monitor the demodulator and FEC

decoder. An operation without I 2C (default) is possible.

Applications

Digital ATSC compliant TV receivers

Personal computers with digital television capabilities

Set top boxes

52

53

54

55

56

57

43

XXX

TDA8960

10

42

11

41

12

40

13

39

14

38

15

37

16

36

17

35

18

34

32

33

31

19

MXXxxx

Fig.1 Pin configuration.

Adaptation based on ATSC field sync (trained) and/or 8-VSB data

(blind)

Trellis (Viterbi) decoder

58

44

NC

NC

VSSD3

NC

NC

NC

VDDD3

NC

NC

VSSD7

VDDD7

DATA0

DATA1

VSSD2

DATA2

DATA3

DATA4

VDDD2

DATA5

TRST

TDO

ERROR

VDDD1

SOP

DATAVALID

VDDD6

RST_AN

VSSD6

DATACLK

VSSD1

DATA7

DATA6

Adaptive Equalizer

Capability to read and write taps via I2C-bus

59

45

20

External indication of demodulator lock

46

30

Mostly internal clock recovery and AGC loops with programmable loop

filters

47

29

Fully internal carrier recovery loop with programmable loop filter

48

28

Square-Root Raised-Cosine filter with 11.5% roll-off factor

27

On-chip digital circuitry for tuner AGC control

49

26

8-VSB demodulator

50

25

Output format: 8-bit wide MPEG-2 transport stream

51

24

Boundary Scan Test

23

ADIN0

ADIN1

ADIN2

ADIN3

ADIN4

ADIN5

ADIN6

ADIN7

VDDD5

VSSD5

ADIN8

ADIN9

A0

SCL

SDA

A1

TDI

TMS

TCK

60

handbook, full pagewidth

64 lead QFP64 package

22

3.3V device

64

One chip ATSC compliant 8-VSB demodulator and concatenated Trellis

(Viterbi)/Reed-Solomon decoder with deinterleaver and de-randomizer

61

General features

62

TR_LD

TR_CS

TR_STB

TR_SDO

VDDD8

CLK

VSSD8

VDDD4

AGCOUT

VSSD4

EQLOCK_INDIC

LOCK_INDIC

NC

63

FEATURES

21

TDA8960

GENERAL DESCRIPTION

The TDA8960 is an ATSC compliant demodulator and forward error

correction decoder for reception of 8-VSB modulated signals for terrestrial

and cable applications:

Most of the loop components needed to recover the data from the received

symbols are internal. The only required external loop components are a

low-speed serial D/A converter and VCXO for the symbol timing recovery

and an OPAMP integrator for the AGC. Loop parameters of the clock and

carrier recovery can be controlled by I2C.

A tuner converts the incoming RF frequency to a fixed IF frequency

centred at 44 MHz. The output of the tuner is filtered, followed by a down

conversion in an IF block to a low IF centred at 1/2 the VSB symbol rate or

approximately 5.38 MHz. The low IF signal is connected to the A/D

converter.

The A/D converter is located within what is typically a fine AGC loop that

includes a variable gain stage at the output of the IF block. However, it is

also possible to apply the VSB IC AGC control output directly to the tuner.

The detector for the VSB IC AGC output is located just after the A/D and

determines the peak level of the incoming signals. After gain control, the

low IF signal is sampled at a nominal rate of twice the VSB symbol frequency, or approximately 21.5 MHz.

The carrier recovery is performed completely internally. This function

consists of a digital frequency and frequency and phase-locked loop

(FPLL).

Data shaping is performed with a square root raised cosine (half Nyquist)

filter with roll-off factor of 11.5%.

Purchase of Philips I2C components conveys a license under the

Philips' I 2C patent to use the components in the I2C system provided

the system conforms to the I2C specification defined by Philips. This

specification can be ordered using the code 9398 393 40011.

7001002

Philips Semiconductors

Preliminary specification

ATSC 8-VSB Demodulator and Decoder

TDA8960

AGC

Terrestial/cable

UHF/VHF

IF downconverter

TDA9819/9829T

Tuner

A/D

TDA8763

MPEG transport stream

VSB IC

21.52 MHz

I2C controller

D/A

VCXO

I2C-bus

Fig.2 Front end unit for reception of 8-VSB signals.

Symbol timing recovery is performed mostly within the VSB IC, except that

a low cost D/A converter and VCXO are required externally to generate

the nominal 21.52 MHz clock for the A/D converter and VSB IC.

After carrier recovery, half Nyquist filtering, and symbol timing recovery,

adaptive equalization is performed based on the use of the ATSC field

sync (trained equalization) and/or the 8-VSB data itself (blind

equalization). The adaptive equalizer uses a decision feedback equalizer

(DFE) structure.

After trellis decoding, the stream is de-interleaved with a convolutional

de-interleaver (interleaving depth 52). The memory for de-interleaving is

on-chip. The Reed-Solomon decoder is ATSC-compliant, has a length 207

LOCK_INDIC EQLOCK_INDIC

LOCK

DECTECTORS

AGCOUT

and can correct up to 10 bytes. Next the decoded stream is de-randomized

using a pseudo-random binary sequence (PRBS).. Finally the data is

passed to a FIFO that prevents the appearance of irregular gaps in the

output data.

The output of the VSB IC is an ATSC compliant MPEG-2 transport stream

together with a clock. Furthermore some signal flags are provided to

indicate the sync bytes and the valid data bytes. Uncorrected blocks are

also indicated.

The 8-bit wide MPEG-2 stream can be provided to an MPEG-2 transport

stream demultiplexer.

ADIN[9:0]

DIGITAL FRONTEND:

RESET

RST_AN

FINE AGC

CARRIER RECOVERY

SERIAL

DAC

INTERACE

HALF-NYQUIST FILTERING

SYMBOL TIMING RECOVERY

SYNC RECOVERY AND PILOT

REMOVAL

TR_SDO

TR_STB

TR_CS

TR_LD

ADAPTIVE EQUALIZATION

SYNCHRONIZATION

TDI

VETERBI DECODER

BOUNDARY

SCAN TEST

DE-INTERLEAVER

REED-SOLOMON DECODER

DE-RANDOMIZER

I2C

FIFO

CLK

DATACLK DATA[7:0] ERROR SOP

DATAVALID

Fig.3 Block diagram of the TDA8960.

Philips Electronics N.V. 1998

TDO

TRST

TMS

TCK

A0

A1

SCL

SDA

S-ar putea să vă placă și

- Tda 10021 DatasheetDocument17 paginiTda 10021 DatasheetWilly DacoÎncă nu există evaluări

- Tda 1548Document20 paginiTda 1548Jennifer NealÎncă nu există evaluări

- Design of Digital TV Receive System Based On DVB-TDocument4 paginiDesign of Digital TV Receive System Based On DVB-Tdesconoc9Încă nu există evaluări

- TDA8822TDocument29 paginiTDA8822TDaniel Hernandez SanchezÎncă nu există evaluări

- Codec ChipDocument11 paginiCodec Chipbalachandra1234Încă nu există evaluări

- An 11.1Gbps Analog PRML Receiver For EDC of Up To 400km-Reach WDM Fiber-Optic LinksDocument4 paginiAn 11.1Gbps Analog PRML Receiver For EDC of Up To 400km-Reach WDM Fiber-Optic LinksGbarbarÎncă nu există evaluări

- GP3 - Complete GuideDocument31 paginiGP3 - Complete GuideAndres AlegriaÎncă nu există evaluări

- Vestel dvd7500 Orion dvd-2705 5.1ch SMDocument25 paginiVestel dvd7500 Orion dvd-2705 5.1ch SMgondifÎncă nu există evaluări

- Experiment 08 Interfacing Codec TLV320AIC23, and Use of DAC and ADCDocument6 paginiExperiment 08 Interfacing Codec TLV320AIC23, and Use of DAC and ADCOmar JanjuaÎncă nu există evaluări

- DSB-B350S Training ManualDocument46 paginiDSB-B350S Training Manualax63naÎncă nu există evaluări

- 73K324L CCITT V.22bis, V.22, V.21, V.23, Bell 212A Single-Chip ModemDocument32 pagini73K324L CCITT V.22bis, V.22, V.21, V.23, Bell 212A Single-Chip ModemRicardo MercadoÎncă nu există evaluări

- Tda 10045Document21 paginiTda 10045tatarmisiÎncă nu există evaluări

- CounterDocument11 paginiCounterDatpmÎncă nu există evaluări

- WTM Microwave DigitalDocument16 paginiWTM Microwave DigitalrrohuuÎncă nu există evaluări

- Ti I2cDocument13 paginiTi I2crajkumar_jain4855100% (1)

- RM0090 Analog-To-Digital Converter (ADC)Document66 paginiRM0090 Analog-To-Digital Converter (ADC)Hieu PhamÎncă nu există evaluări

- T.D.A 10021HTDocument16 paginiT.D.A 10021HTJose M PeresÎncă nu există evaluări

- The Design and Construction of A DDS Based Waveform GeneratorDocument12 paginiThe Design and Construction of A DDS Based Waveform GeneratorWilson Fernando Rodríguez RodríguezÎncă nu există evaluări

- 74 HC 94Document8 pagini74 HC 94Ravi RathodÎncă nu există evaluări

- MC44BS374T1Document34 paginiMC44BS374T1Aydın DoganÎncă nu există evaluări

- DV29 Service Manual Issue 1 PDFDocument48 paginiDV29 Service Manual Issue 1 PDFZbigniew SzaryczÎncă nu există evaluări

- Vestel 17MB230 FullDocument78 paginiVestel 17MB230 FullCornel Pislaru100% (1)

- 11AK37 Chassis: General InformationDocument65 pagini11AK37 Chassis: General InformationBenjamin MaxwellÎncă nu există evaluări

- Circuit Diagram Wireless TransmitterDocument17 paginiCircuit Diagram Wireless Transmitterumaiya1990100% (2)

- T.D.A 10023HTDocument20 paginiT.D.A 10023HTJose M PeresÎncă nu există evaluări

- Saf 7113 HTDocument80 paginiSaf 7113 HTgheo23Încă nu există evaluări

- Surya - First PhasereportDocument10 paginiSurya - First PhasereportSuribabuIppiliÎncă nu există evaluări

- 14-Bit, 160 Msps 2 Interpolating Dual Txdac+: Ⴛ/4Ⴛ/8Ⴛ D/A ConverterDocument52 pagini14-Bit, 160 Msps 2 Interpolating Dual Txdac+: Ⴛ/4Ⴛ/8Ⴛ D/A Convertercbernal73Încă nu există evaluări

- Tda 7449Document18 paginiTda 7449Ariel NavarreteÎncă nu există evaluări

- Pic 18 F 4520Document51 paginiPic 18 F 4520sitizarina78100% (1)

- MC44817Document8 paginiMC44817felipefreeÎncă nu există evaluări

- SAA7708H DatasheetDocument60 paginiSAA7708H Datasheetchitz852100% (1)

- China Ve01 With Tda93xx An17821 Stv9302a La78040 Ka5q0765-SmDocument40 paginiChina Ve01 With Tda93xx An17821 Stv9302a La78040 Ka5q0765-SmAmadou Fall100% (1)

- Adc Lab Pic18Document23 paginiAdc Lab Pic18Bolarinwa Joseph100% (1)

- Data Sheet: Device SpecificationDocument101 paginiData Sheet: Device SpecificationvmalvicaÎncă nu există evaluări

- Vehicle Speed Control System Using RF CommunicationDocument20 paginiVehicle Speed Control System Using RF CommunicationRaina John100% (2)

- TDA8366Document48 paginiTDA8366Rigoberto Martinez LopezÎncă nu există evaluări

- Cdma Reverselink Waveform Generator Fpga For Production Transmit Path TestsDocument9 paginiCdma Reverselink Waveform Generator Fpga For Production Transmit Path Testsxiao zhanÎncă nu există evaluări

- Vestel 17mb36 Chassis Mb36 Training-ManualDocument59 paginiVestel 17mb36 Chassis Mb36 Training-Manualdaniel1964Încă nu există evaluări

- Data Sheet: Radio Tuning PLL Frequency SynthesizerDocument13 paginiData Sheet: Radio Tuning PLL Frequency SynthesizerElchat InternacionalÎncă nu există evaluări

- Data SheetDocument108 paginiData SheetBrowserÎncă nu există evaluări

- A 6.1 GS/S 52.8 MW 43 DB DR 80 MHZ Bandwidth 2.4 GHZ RF Bandpass Adc in 40 NM CmosDocument4 paginiA 6.1 GS/S 52.8 MW 43 DB DR 80 MHZ Bandwidth 2.4 GHZ RF Bandpass Adc in 40 NM Cmossohailasghar_tÎncă nu există evaluări

- Data Sheet: 1.3 GHZ Bidirectional I C-Bus Controlled SynthesizerDocument19 paginiData Sheet: 1.3 GHZ Bidirectional I C-Bus Controlled Synthesizerlu1agpÎncă nu există evaluări

- Analog-to-Digital Conversion: Industrial Embedded SystemsDocument14 paginiAnalog-to-Digital Conversion: Industrial Embedded Systemschandramohan muruganÎncă nu există evaluări

- Bell 202Document30 paginiBell 202danxyÎncă nu există evaluări

- Digital IF Subsampling Using The HI5702, HSP45116 and HSP43220Document6 paginiDigital IF Subsampling Using The HI5702, HSP45116 and HSP43220Farhan BabarÎncă nu există evaluări

- National Institute of Technology, Rourkela: Embedded Systems LaboratoryDocument13 paginiNational Institute of Technology, Rourkela: Embedded Systems Laboratoryprateekkumardash2002Încă nu există evaluări

- Tsa5512 CNV 3Document21 paginiTsa5512 CNV 3soft4gsmÎncă nu există evaluări

- 11AK20M6Document16 pagini11AK20M6goncalojpvÎncă nu există evaluări

- M123SP Service ManualDocument57 paginiM123SP Service ManualJhonatan Diaz100% (1)

- Tda 9875Document93 paginiTda 9875FxprimeÎncă nu există evaluări

- PIC16F18855 ModDocument662 paginiPIC16F18855 Modwhynot05Încă nu există evaluări

- Saa7708h PDFDocument60 paginiSaa7708h PDFPamela Ramos SánchezÎncă nu există evaluări

- LTE Signaling: Troubleshooting and Performance MeasurementDe la EverandLTE Signaling: Troubleshooting and Performance MeasurementÎncă nu există evaluări

- Radio Frequency Identification and Sensors: From RFID to Chipless RFIDDe la EverandRadio Frequency Identification and Sensors: From RFID to Chipless RFIDÎncă nu există evaluări

- Chipless Radio Frequency Identification Reader Signal ProcessingDe la EverandChipless Radio Frequency Identification Reader Signal ProcessingÎncă nu există evaluări

- Digital Signal Processing Using the ARM Cortex M4De la EverandDigital Signal Processing Using the ARM Cortex M4Evaluare: 1 din 5 stele1/5 (1)

- Crack Lectra Diamino Fashion V5r3 Checked PDFDocument3 paginiCrack Lectra Diamino Fashion V5r3 Checked PDFTiffany0% (1)

- XBR-55X900F Specsheet 221217Document4 paginiXBR-55X900F Specsheet 221217rolringarÎncă nu există evaluări

- 3-The Session Initiation ProtocolDocument42 pagini3-The Session Initiation ProtocolRaytheeshMonÎncă nu există evaluări

- Omnia SST: Audio Processing SoftwareDocument3 paginiOmnia SST: Audio Processing SoftwareFelipe QuindeÎncă nu există evaluări

- Computer Laboratory Manual: Fundamental of ICT Lab ManualDocument133 paginiComputer Laboratory Manual: Fundamental of ICT Lab Manualanon_510855877Încă nu există evaluări

- Sample Layer 3 - SFO - LTE - SC3B - Part3 - GoodZone - 01.2 Qualcomm - IPERFDocument1.411 paginiSample Layer 3 - SFO - LTE - SC3B - Part3 - GoodZone - 01.2 Qualcomm - IPERFVijay VasaÎncă nu există evaluări

- DP TV Others 14060 DriversDocument347 paginiDP TV Others 14060 DriversLenin KumarÎncă nu există evaluări

- Huawei: H31-611 ExamDocument3 paginiHuawei: H31-611 ExamVidusheeÎncă nu există evaluări

- GY-HM890U / GY-HM850U Operation ManualDocument220 paginiGY-HM890U / GY-HM850U Operation ManualProduccion TAMÎncă nu există evaluări

- XM-15B Comandos ATDocument28 paginiXM-15B Comandos ATRed JonhÎncă nu există evaluări

- Chapter 1 Introduction To Internet ProgrammingDocument4 paginiChapter 1 Introduction To Internet ProgrammingchetraTEP100% (1)

- Photography Websites For All PhotographersDocument2 paginiPhotography Websites For All PhotographersantcaraÎncă nu există evaluări

- DAEWO Igual A TCL-DW50-LEDHDDocument38 paginiDAEWO Igual A TCL-DW50-LEDHDRaul Lopez ReinaÎncă nu există evaluări

- DynaFlex DB4 DB4XDocument2 paginiDynaFlex DB4 DB4XRikyÎncă nu există evaluări

- Welcome: W1100/W1200 Digital Projector User ManualDocument65 paginiWelcome: W1100/W1200 Digital Projector User ManualJoao Jose Santos NetoÎncă nu există evaluări

- DCN Multimedia Comme Commercial Brochure EnUS 13234400395Document12 paginiDCN Multimedia Comme Commercial Brochure EnUS 13234400395fgfsdg fdgÎncă nu există evaluări

- Fax Machine Phone PDFDocument3 paginiFax Machine Phone PDFVilasak ItptÎncă nu există evaluări

- Lh70yr Monitor TV LGDocument144 paginiLh70yr Monitor TV LGJTELLO857Încă nu există evaluări

- MPVDocument177 paginiMPVcrazydmanÎncă nu există evaluări

- DSL 2730EUser ManualDocument93 paginiDSL 2730EUser Manualdillamirl100% (1)

- LectraDocument3 paginiLectraJinsu JangÎncă nu există evaluări

- Vonage RTP300Document98 paginiVonage RTP300Berks HomesÎncă nu există evaluări

- Hdmi + Optical Zoom Amazing Clarity: Portable Flexarm Document CameraDocument2 paginiHdmi + Optical Zoom Amazing Clarity: Portable Flexarm Document CameraEmily MagrishÎncă nu există evaluări

- HP ActualTests HP2-H08 v2011-06-14 by NowerdaysDocument39 paginiHP ActualTests HP2-H08 v2011-06-14 by NowerdaysLai Jack0% (2)

- Computers Main IdeaDocument1 paginăComputers Main IdeaMaria Del Carmen GagliardiÎncă nu există evaluări

- Philco Pm1414 Chasis La5-ADocument26 paginiPhilco Pm1414 Chasis La5-Abinsakluis1808Încă nu există evaluări

- Picoscope PC OscilloscopesDocument3 paginiPicoscope PC Oscilloscopespsihocognitie1Încă nu există evaluări

- Speedport w701v SetupDocument4 paginiSpeedport w701v Setupgalijas93Încă nu există evaluări

- Universal Asynchronous Receiver Transmitter (Uart) PDFDocument56 paginiUniversal Asynchronous Receiver Transmitter (Uart) PDFG30nyÎncă nu există evaluări

- UNIT 3 Format of APA Style PDFDocument1 paginăUNIT 3 Format of APA Style PDFJohn Lester M. Dela CruzÎncă nu există evaluări